Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Multiple Input Switch Monitor LSI for Automotive

# BD3375MUV-M

#### **General Description**

BD3375MUV-M is a 22-channel Multiple Input Switch Monitor IC that detects the opening and closing of mechanical switches. Once it senses a change in the status of a switch, it sends an interrupt signal to the MCU via a serial peripheral interface (SPI).

The 22 switch inputs have two types of power supply, VPUB and VPUA. The VPUB and the VPUA power supplies can either be from a battery or from another power supply system. VPUB is the supply for the INB inputs while VPUA is for the INZ and INA inputs.

BD3375MUV-M has two modes of operation, Normal and Sleep. In both modes, the internal registers can be set to make the device perform either intermittent or continuous monitoring of the switches.

In intermittent monitoring, the switch status is monitored at regular time intervals, allowing the IC to operate with low power consumption. Also, operation with reduced noise can be achieved by enabling uniform sequential monitoring of all switches or sequential monitoring by power supply system.

# **Application**

■ Body Control Module

#### **Key Specifications**

■ Fully Functional Voltage Range: 8V to 26V

■ Switch Input Voltage Range: -14V to +40V

■ Selectable Wetting Current (Min):

1mA, 3mA, 5mA, 10mA, 15mA

# **Specifications**

- AEC-Q100 Qualified (Note 1)

- Operational Voltage Range: 3.9V to 8V

- Uses 3.3/5.0V SPI protocol in communicating with the MCU

- Serial communication error checking through 8bit-CRC

- Thermal Shutdown Protection (TSD)

- Power on Reset (POR)

- Selectable source/sink current levels through register settings

- Wetting current timer capability

- 8 source or sink input terminals

- 14 source input terminals

- Separable Power Supply

VPUA: 16ch (INA&INZ), VPUB: 6ch (INB)

- Interrupt notification upon switch status change

- 1 to 6 times matched LPF that eliminates input terminal noise

- Low current consumption (Intermittent monitoring)

- Status display of selected terminal at DMUX terminal (Note 1) Grade 1

# **Package**

VQFN48MCV070 (48 pin QFN) W(Typ) x D(Typ) x H(Max)

7.00mm x 7.00mm x 1.00mm

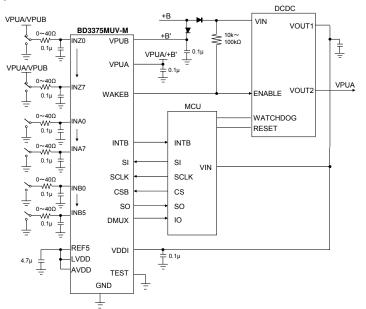

# **Typical Application Circuit**

Figure 1. Typical Application Circuit

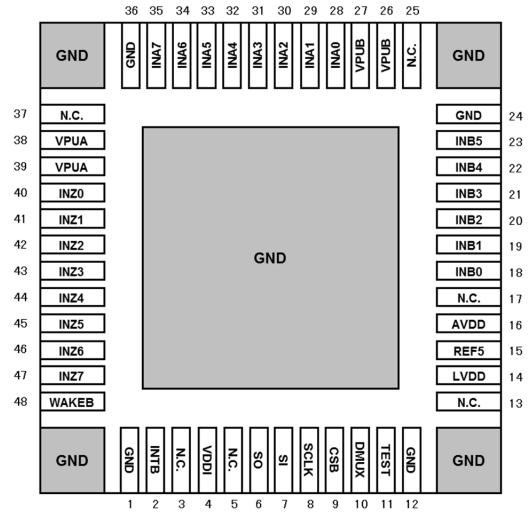

# **Pin Configuration**

Figure 2. Pin Configuration (Top View)

# **Pin Description**

Table 1. Pin Description (1)

| Pin<br>No. | Pin<br>Name | Function | Description                                                                                 | Equivalent<br>Circuit<br>Diagram<br>(Note 2) |

|------------|-------------|----------|---------------------------------------------------------------------------------------------|----------------------------------------------|

| 1          | GND         | Ground   | Ground pin                                                                                  |                                              |

| 2          | INTB        | Output   | Open-drain interrupt output pin to the MCU (with an internal pull-up resistor)              | С                                            |

| 3          | N.C.        | -        | No Connection                                                                               |                                              |

| 4          | VDDI        | Input    | Power supply pin for CSB, SI, SCLK, SO, INTB and DMUX                                       |                                              |

| 5          | N.C.        | -        | No Connection                                                                               |                                              |

| 6          | SO          | Output   | SPI data output pin to the MCU                                                              | Н                                            |

| 7          | SI          | Input    | SPI control data input pin from the MCU (with an internal pull-down resistor)               | A                                            |

| 8          | SCLK        | Input    | SPI control clock input pin from the MCU (with an internal pull-down resistor)              | А                                            |

| 9          | CSB         | Input    | SPI control chip select input pin from the MCU (with internal pull-up current source)       | В                                            |

| 10         | DMUX        | Output   | Digital multiplexer for switch input output pin                                             | G                                            |

| 11         | TEST        | Input    | Test mode control pin <sup>(Note 3)</sup>                                                   | J                                            |

| 12         | GND         | Ground   | Ground                                                                                      |                                              |

| 13         | N.C.        | -        | No Connection                                                                               |                                              |

| 14         | LVDD        | Input    | Power supply input pin for the logic block (Note 4)                                         |                                              |

| 15         | REF5        | Output   | Power supply input pin for the logic block (Note 4)  5V power supply output pin (Note 4)    | I                                            |

| 16         | AVDD        | Input    | Power supply input pin for the analog block (Note 4)                                        |                                              |

| 17         | N.C.        | -        | No Connection                                                                               |                                              |

| 18         | INB0        | Input    | Switch input pin 0 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 19         | INB1        | Input    | Switch input pin 1 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 20         | INB2        | Input    | Switch input pin 2 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 21         | INB3        | Input    | Switch input pin 3 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 22         | INB4        | Input    | Switch input pin 4 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 23         | INB5        | Input    | Switch input pin 5 under VPUB power supply system (with an internal pull-up current source) | F                                            |

| 24         | GND         | Ground   | Ground                                                                                      |                                              |

|            | 1           |          | I .                                                                                         |                                              |

<sup>(</sup>Note 2) Ref. Page 66 and Page 67 IO Equivalent Circuit.

(Note 3) Short TEST pin to ground when mounted.

(Note 4) Short REF5 pin to AVDD pin and LVDD pin, and connect a 4.7µF capacitor between it and ground. Do not use it as voltage source to another IC.

Table 2. Pin Description (2)

|            |             |          | Table 2. Pin Description (2)                                                                     |                                              |

|------------|-------------|----------|--------------------------------------------------------------------------------------------------|----------------------------------------------|

| Pin<br>No. | Pin<br>Name | Function | Description                                                                                      | Equivalent<br>Circuit<br>Diagram<br>(Note 2) |

| 25         | GND         | -        | No Connection                                                                                    |                                              |

| 26         | VPUB        | Input    | Power supply input pin for the main system and INB switches                                      |                                              |

| 27         | VPUB        | Input    | Power supply input pin for the main system and INB switches                                      |                                              |

| 28         | INA0        | Input    | Switch input pin 0 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 29         | INA1        | Input    | Switch input pin 1 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 30         | INA2        | Input    | Switch input pin 2 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 31         | INA3        | Input    | Switch input pin 3 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 32         | INA4        | Input    | Switch input pin 4 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 33         | INA5        | Input    | Switch input pin 5 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 34         | INA6        | Input    | Switch input pin 6 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 35         | INA7        | Input    | Switch input pin 7 under VPUA power supply system (with an internal pull-up current source)      | F                                            |

| 36         | GND         | Ground   | Ground                                                                                           |                                              |

| 37         | N.C.        | -        | No Connection                                                                                    |                                              |

| 38         | VPUA        | Input    | Power supply input pin for INA and INZ switches                                                  |                                              |

| 39         | VPUA        | Input    | Power supply input pin for INA and INZ switches                                                  |                                              |

| 40         | INZ0        | Input    | Switch input pin 0 under VPUA power supply system (with an internal pull-up/down current source) | Е                                            |

| 41         | INZ1        | Input    | Switch input pin 1 under VPUA power supply system (with an internal pull-up/down current source) | Е                                            |

| 42         | INZ2        | Input    | Switch input pin 2under VPUA power supply system (with an internal pull-up/down current source)  | E                                            |

| 43         | INZ3        | Input    | Switch input pin 3 under VPUA power supply system (with an internal pull-up/down current source) | Е                                            |

| 44         | INZ4        | Input    | Switch input pin 4 under VPUA power supply system (with an internal pull-up/down current source) | E                                            |

| 45         | INZ5        | Input    | Switch input pin 5 under VPUA power supply system (with an internal pull-up/down current source) | E                                            |

| 46         | INZ6        | Input    | Switch input pin 6 under VPUA power supply system (with an internal pull-up/down current source) | E                                            |

| 47         | INZ7        | Input    | Switch input pin 7 under VPUA power supply system (with an internal pull-up/down current source) | E                                            |

| 48         | WAKEB       | Output   | Open-drain output pin to monitor the mode of operation (Note 5)                                  | D                                            |

(Note 5) In the application circuit, WAKEB should be pulled-up by an external resistor.

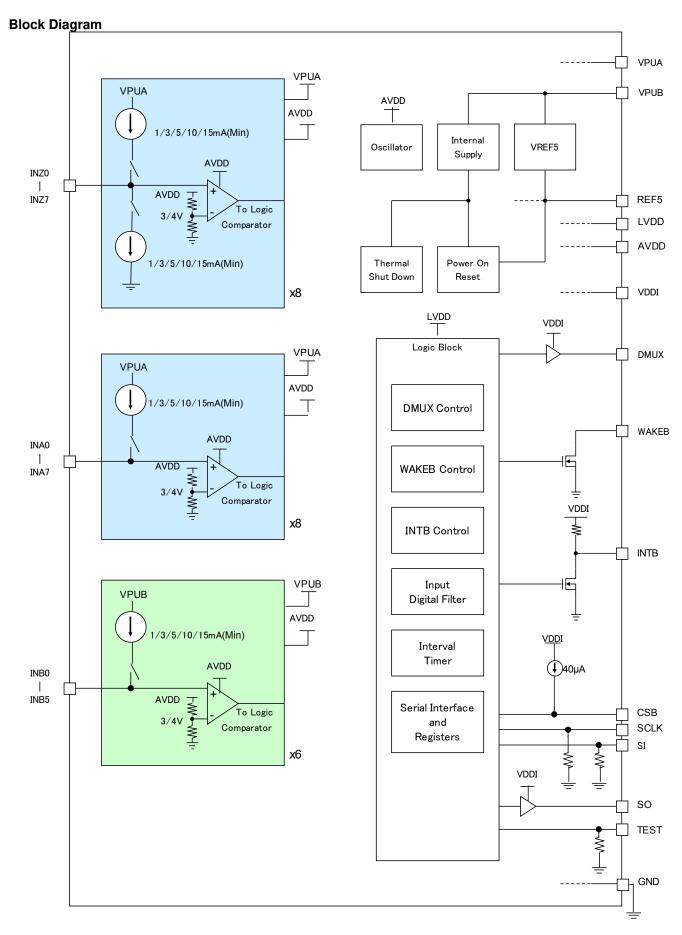

Figure 3. Block Diagram

# **Absolute Maximum Ratings**

Table 3. Pin Description

| Table 6.1 in Beschilden                                                                                                                      |                  |              |      |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|--------------|------|--|--|--|--|

| Parameter                                                                                                                                    | Symbol           | Ratings      | Unit |  |  |  |  |

| Supply Voltage Range on Pin VDDI, AVDD, LVDD Input Voltage Range on Pin CSB, SI, SCLK, TEST Output Voltage Range at Pin SO, INTB, DMUX, REF5 | -                | -0.3 to +7.0 | V    |  |  |  |  |

| Supply Voltage Range on Pin VPUA, VPUB Voltage Range on Pin WAKEB                                                                            | -                | -0.3 to +40  | V    |  |  |  |  |

| Input Current at Pin WAKEB                                                                                                                   | -                | 10           | mA   |  |  |  |  |

| Input Voltage on Switch Pin (INB0-INB5, INA0-INA7,INZ0-INZ7)                                                                                 | -                | -14 to +40   | V    |  |  |  |  |

| Operating Temperature Range                                                                                                                  | $T_{OPR}$        | -40 to +125  | °C   |  |  |  |  |

| Storage Temperature Range                                                                                                                    | T <sub>STR</sub> | -55 to +150  | °C   |  |  |  |  |

| Maximum Junction Temperature                                                                                                                 | Tj               | -40 to +150  | °C   |  |  |  |  |

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

# Thermal Resistance (Note 6)

Table 4. Thermal Resistance

| Table 1: Thermal Reciciance                         |               |             |               |       |  |  |  |

|-----------------------------------------------------|---------------|-------------|---------------|-------|--|--|--|

| Parameter                                           | Symbol        | Thermal Res | Unit          |       |  |  |  |

| Faiametei                                           | Symbol        | 1s (Note 8) | 2s2p (Note 9) | Offic |  |  |  |

| VQFN48MCV070                                        |               |             |               |       |  |  |  |

| Junction to Ambient                                 | $\theta_{JA}$ | 83.3        | 24.5          | °C/W  |  |  |  |

| Junction to Top Characterization Parameter (Note 7) | $\Psi_{JT}$   | 8           | 5             | °C/W  |  |  |  |

(Note 6) Based on JESD51-2A(Still-Air)

(Note 7) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 8) Using a PCB board based on JESD51-3 (Table 5).

(Note 9) Using a PCB board based on JESD51-5, 7 (Table 6).

Table 5. 1s

| Layer Number of<br>Measurement Board | Material  | Board Size                 |

|--------------------------------------|-----------|----------------------------|

| Single                               | FR-4      | 114.3mm x 76.2mm x 1.57mmt |

| Тор                                  |           |                            |

| Copper Pattern                       | Thickness |                            |

| Footprints and Traces                | 70µm      |                            |

Table 6. 2s2p

| Layer Number of            | Material  | Board Size                |           | Thermal Via (Note 10) |           |       |          |

|----------------------------|-----------|---------------------------|-----------|-----------------------|-----------|-------|----------|

| Measurement Board          | Material  | Board Size                |           | Board Size            |           | Pitch | Diameter |

| 4 Layers                   | FR-4      | 114.3mm x 76.2mm x 1.6mmt |           | 1.20mm                | Ф0.30mm   |       |          |

| Тор                        |           | 2 Internal Laye           | ers       | Bottom                |           |       |          |

| Copper Pattern             | Thickness | Copper Pattern            | Thickness | Copper Pattern        | Thickness |       |          |

| Footprints and Traces 70µm |           | 74.2mm x 74.2mm 35μm      |           | 74.2mm x 74.2m        | m 70µm    |       |          |

(Note 10) This thermal via connects with the copper pattern of all layers.

# **Recommended Operating Conditions**

Table 7. Recommended Operating Conditions

| Parameter                                 | Cymbol            | Rati | Unit |      |  |

|-------------------------------------------|-------------------|------|------|------|--|

| raidilletei                               | Symbol            | Min  | Max  | John |  |

| Operating Temperature                     | T <sub>OPR</sub>  | -40  | +125 | °C   |  |

| VPUA/VPUB Supply Voltage                  | V <sub>VPUX</sub> | 8.0  | 26   | V    |  |

| VDDI Supply Voltage                       | $V_{VDDI}$        | 3.1  | 5.25 | V    |  |

| Capacitance for REF5 <sup>(Note 11)</sup> | C <sub>REF</sub>  | 4.7  | -    | μF   |  |

(Note 11) Recommend a ceramic capacitance. Please consider variation of capacitance.

# **Electrical Characteristics**

Spec conditions: 8.0V≤VPUA/VPUB≤26V, 3.1V≤VDDI≤5.25V, -40°C≤T<sub>OPR</sub>≤+125°C VPUA/VPUB/INZ/INA/INB terminal: resistors and capacitors are not connected

REF5 terminal: 4.7µF

Unless otherwise specified, the typical condition is VPUA/VPUB=13V, VDDI=5.00V, T<sub>OPR</sub>=25°C.

Table 8. Recommended Operating Conditions

| Parameter                                          | Symbol/Name            | Min  | Тур  | Max  | Unit |

|----------------------------------------------------|------------------------|------|------|------|------|

| VPUA/VPUB Supply Voltage                           |                        |      |      |      |      |

| Low -voltage Operating Range (Note 12)             | $V_{VPUX(QFL)}$        | 3.9  | -    | 8.0  | .,   |

| Fully Operational Voltage Range                    | V <sub>VPUX(FO)</sub>  | 8.0  | -    | 26   | V    |

| High-voltage Operating Range (Note 13)             | V <sub>VPUX(QFH)</sub> | 26   | -    | 40   |      |

| POR(Power on Reset) Activation Voltage (Note 14)   | V <sub>POR(LOW)</sub>  | 3.9  | 4.2  | 4.5  | V    |

| POR(Power on Reset) Deactivation Voltage (Note 14) | V <sub>POR(HIGH)</sub> | 4.0  | 4.3  | 4.6  | V    |

| VPUA/VPUB Operating Current                        |                        |      |      |      |      |

| Continuous Monitoring                              | I <sub>VPUX(OFF)</sub> | -    | -    | 600  | μA   |

| Current source is invalid, "Hi-Z" Status           | , ,                    |      |      |      |      |

| VPUA/VPUB Average Operating Current                |                        |      |      |      |      |

| Intermittent Monitoring                            |                        |      | 75   | 100  |      |

| Source/Sink Current Setting=1mA                    | I <sub>VPUX(SS)</sub>  | _    | 75   | 100  | μA   |

| Monitoring Period=50ms, Strobe Time=125µs          |                        |      |      |      |      |

| VDDI Operating Current                             | l                      |      | 5    | 10   |      |

| INTB="H", CSB="H"                                  | I <sub>VDDI</sub>      | _    | 3    | 10   | μA   |

| REF5 Output Voltage                                | $V_{REF5}$             | 4.75 | 5.00 | 5.25 | V    |

(Note 12) Electrical characteristics are not guaranteed though functions are operating. POR is active between 3.9V and 4.5V. (Note 13) Electrical characteristics are not guaranteed though functions are operating. (Note 14) The POR circuit monitors the REF5 voltage.

Table 9. Electrical Characteristics (Switch Input)

| Table 9. Electrical Characteristics (Switch Input) |                        |      |      |      |        |  |  |  |

|----------------------------------------------------|------------------------|------|------|------|--------|--|--|--|

| Parameter                                          | Symbol/Name            | Min  | Тур  | Max  | Unit   |  |  |  |

| Source Current 1 (Internal Pull-up Current Source) |                        |      |      |      |        |  |  |  |

| 0V external supply, VPUA/VPUB system               | I <sub>SOURCE1</sub>   | 1.0  | 1.4  | 1.8  | mA     |  |  |  |

| (1mA Setting)                                      |                        |      |      |      |        |  |  |  |

| Sink Current 1 (Internal Pull-down Current Source) | I <sub>SINK1</sub>     | 1.0  | 1.4  | 1.8  | mA     |  |  |  |

| 8V external supply, VPUA system (1mA Setting)      | ISINK1                 | 1.0  | 1.4  | 1.0  | ША     |  |  |  |

| Source Current 2 (Internal Pull-up Current Source) |                        |      |      |      |        |  |  |  |

| 0V external supply, VPUA/VPUB system               | I <sub>SOURCE3</sub>   | 3.0  | 4.2  | 5.4  | mA     |  |  |  |

| (3mA Setting)                                      |                        |      |      |      |        |  |  |  |

| Sink Current 2 (Internal Pull-down Current Source) | I <sub>SINK3</sub>     | 3.0  | 4.2  | 5.4  | mA     |  |  |  |

| 8V external supply, VPUA system (3mA Setting)      | ISINK3                 | 3.0  | 7.2  | 5.4  | ША     |  |  |  |

| Source Current 3 (Internal Pull-up Current Source) |                        |      |      |      |        |  |  |  |

| 0V external supply, VPUA/VPUB system               | I <sub>SOURCE5</sub>   | 5.0  | 7.0  | 9.0  | mA     |  |  |  |

| (5mA Setting)                                      |                        |      |      |      |        |  |  |  |

| Sink Current 3 (Internal Pull-down Current Source) | I <sub>SINK5</sub>     | 5.0  | 7.0  | 9.0  | mA     |  |  |  |

| 8V external supply, VPUA system (5mA Setting)      | ISINKS                 | 0.0  | 7.0  | 0.0  | 1117 ( |  |  |  |

| Source Current 4 (Internal Pull-up Current Source) |                        |      |      |      |        |  |  |  |

| 0V external supply, VPUA/VPUB system               | I <sub>SOURCE10</sub>  | 10.0 | 14.0 | 18.0 | mA     |  |  |  |

| (10mA Setting)                                     |                        |      |      |      |        |  |  |  |

| Sink Current 4 (Internal Pull-down Current Source) | I <sub>SINK10</sub>    | 10.0 | 14.0 | 18.0 | mA     |  |  |  |

| 8V external supply, VPUA system (10mA Setting)     | SINK10                 | 10.0 | 14.0 | 10.0 | 1117 ( |  |  |  |

| Source Current 5 (Internal Pull-up Current Source) |                        |      |      |      |        |  |  |  |

| 0V external supply, VPUA/VPUB system               | I <sub>SOURCE15</sub>  | 15.0 | 21.0 | 27.0 | mA     |  |  |  |

| (15mA Setting)                                     |                        |      |      |      |        |  |  |  |

| Sink Current 5 (Internal Pull-down Current Source) | I <sub>SINK15</sub>    | 15.0 | 21.0 | 27.0 | mA     |  |  |  |

| 8V external supply, VPUA system (15mA Setting)     | CLANIG                 | 10.0 | 21.0 | 27.0 | 1117 ( |  |  |  |

| Low to High Switch Detection Threshold Voltage     | V <sub>TH3(HIGH)</sub> | 2.7  | 3.0  | 3.3  | V      |  |  |  |

| (3.0V Setting)                                     | V TH3(HIGH)            | 2.1  | 0.0  | 0.0  | •      |  |  |  |

| High to Low Switch Detection Threshold Voltage     | V <sub>TH3(LOW)</sub>  | 2.6  | 2.9  | 3.2  | V      |  |  |  |

| (3.0V Setting)                                     | V IH3(LUVV)            | 2.0  | 2.0  | 0.2  | •      |  |  |  |

| Low to High Switch Detection Threshold Voltage     | V <sub>TH4(HIGH)</sub> | 3.7  | 4.0  | 4.3  | V      |  |  |  |

| (4.0V Setting)                                     | <b>v</b> 1П4(ПІСП)     | 0.7  | 7.0  | 7.0  | •      |  |  |  |

| High to Low Switch Detection Threshold Voltage     | V <sub>TH4(LOW)</sub>  | 3.6  | 3.9  | 4.2  | V      |  |  |  |

| (4.0V Setting)                                     | VID4(LOW)              | 0.0  | 0.0  | 1.2  | •      |  |  |  |

Table 10. Electrical Characteristics (Static Electrical Characteristics)

| Parameter                                                   | Symbol/Name                         | Min                    | Тур | Max        | Unit |

|-------------------------------------------------------------|-------------------------------------|------------------------|-----|------------|------|

| Serial Interface Threshold Voltage (Note 15)                | V <sub>INLOGIC</sub>                | 0.8                    | 1   | 2.2        | V    |

| CSB Input Current CSB=VDDI                                  | I <sub>CS(HIGH)</sub>               | -10                    | -   | +10        | μA   |

| CSB Pull-up Current<br>CSB=0V                               | Ics(Low)                            | 30                     | -   | 85         | μA   |

| SI, SCLK Pull-down Resistor                                 | R <sub>SI</sub> , R <sub>SCLK</sub> | 50                     | 100 | 150        | kΩ   |

| SI, SCLK Input Current<br>SI, SCLK=0V                       | Isi(LOW), Isclk(LOW)                | -10                    | -   | +10        | μA   |

| SO "H" Level Output Voltage<br>I <sub>SOURCE</sub> =200μA   | V <sub>SC(HIGH)</sub>               | V <sub>VDDI</sub> -0.8 | -   | $V_{VDDI}$ | V    |

| SO "L" Level Output Voltage<br>I <sub>SINK</sub> =1.6mA     | V <sub>SO(LOW)</sub>                | -                      | -   | 0.4        | V    |

| SO(Set to "Hi-Z") Input Current<br>0V to VDDI               | I <sub>SO(TRI)</sub>                | -10                    | -   | +10        | μA   |

| DMUX "H" Level Output Voltage<br>I <sub>SOURCE</sub> =200µA | V <sub>DMUX(HIGH)</sub>             | V <sub>VDDI</sub> -0.8 | -   | $V_{VDDI}$ | V    |

| DMUX "L" Level Output Voltage I <sub>SINK</sub> =1.6mA      | V <sub>DMUX(LOW)</sub>              | -                      | -   | 0.4        | V    |

| INTB Internal Pull-up Current (Note 16)                     | I <sub>INTB(PU)</sub>               | 15                     | 53  | 85         | μΑ   |

| INTB "H" Level Output Voltage INTB=OPEN                     | V <sub>INTB(HIGH)</sub>             | V <sub>VDDI</sub> -0.5 | -   | $V_{VDDI}$ | V    |

| INTB "L" Level Output Voltage I <sub>SINK</sub> =1.0mA      | V <sub>INTB(LOW)</sub>              | -                      | 0.2 | 0.4        | V    |

| WAKEB "L" Level Output Voltage WAKEB=1.0mA                  | V <sub>WAKEB(LOW)</sub>             | -                      | 0.2 | 0.4        | V    |

| WAKEB (Set to "Hi-Z") Input Current 0V to VPUB              | I <sub>WAKEB(TRI)</sub>             | -10                    | -   | +10        | μA   |

(Note 15) Applicable to SCLK, SI, CSB (Note 16) VDDI= 5.0V

Table 11. Electrical Characteristics (Dynamic Electrical Characteristics)

| Parameter                                              | Symbol/Name            | Min    | Тур                     | Max      | Unit |

|--------------------------------------------------------|------------------------|--------|-------------------------|----------|------|

| Wetting Current Timer                                  | t                      | 13     |                         | 22       | me   |

| Counting starts after n-times detection of matched LPF | t <sub>WCT</sub>       | 13     | -                       | 22       | ms   |

| Interrupt Delay Time1                                  |                        |        |                         |          |      |

| Time from switch status change to INTB output change   | t <sub>INTB_DLY1</sub> | -      | -                       | 1        | ms   |

| in continuous monitoring                               |                        |        |                         |          |      |

| Interrupt Delay Time 2                                 |                        |        |                         | [Monitor |      |

| Time from switch status change to INTB output change   | t <sub>INTB DLY2</sub> | _      | _                       | cycle] x | ms   |

| in intermittent monitoring                             | UNTB_DLY2              | _      | _                       | n+1      | 1113 |

| n: Setting time of LPF matched n times                 |                        |        |                         | 11.1     |      |

| Interrupt Clear Time                                   | t <sub>INTB_CLR</sub>  | _      | _                       | 150      | μs   |

| Time from CSB rising edge to INTB output change        | UNTB_CLR               | _      | _                       | 130      | μο   |

| Command Set Time                                       | t <sub>REG EN</sub>    | _      | _                       | 150      | μs   |

| Time from CSB rising edge to setting of register       | REG_EN                 |        |                         | 100      | μο   |

| Transition Time to Normal Mode                         | twakeb dly1            | _      | _                       | 1        | ms   |

| Time from CSB rising edge to WAKEB output change       | WAKEB_DLY I            |        |                         | •        | 1110 |

| Transition Time to Sleep Mode                          | twakeb dly2            | _      | _                       | 1        | ms   |

| Time from CSB rising edge to WAKEB output change       | WANEB_DL12             |        |                         | -        | 1110 |

| Switch Strobe Time (93.75µs Setting) (Note 17)         | t <sub>SCAN 94</sub>   | 84.375 | 93.75                   | 103.125  | μs   |

| Switch Strobe Time (125us Setting) (Note 17)           | t <sub>SCAN_125</sub>  | 112.5  | 125                     | 137.5    | μs   |

| Switch Strobe Time (187.5µs Setting) (Note 17)         | t <sub>SCAN 188</sub>  | 168.75 | 187.5                   | 206.25   | μs   |

| Switch Strobe Time (250µs Setting) (Note 17)           | t <sub>SCAN 250</sub>  | 225    | 250                     | 275      | μs   |

| Source/Sink Current Rise Time                          |                        |        | 41 ( 40)                |          |      |

| FSQ="0", FSQZ/A/B="0", 10mA Setting                    | t <sub>SR_R</sub>      | -      | 20 <sup>(Note 18)</sup> | -        | μs   |

| Load Resistance 100Ω                                   |                        |        |                         |          |      |

| Source/Sink Current Fall Time                          |                        |        | (NI=4= 40)              |          |      |

| FSQ="0", FSQZ/A/B="0", 10mA Setting                    | t <sub>SR_F</sub>      | -      | 15 <sup>(Note 18)</sup> | -        | μs   |

| Load Resistance 100Ω                                   | _                      |        |                         |          |      |

| Internal Clock Accuracy                                | t <sub>TIMER</sub>     | -10    | -                       | +10      | %    |

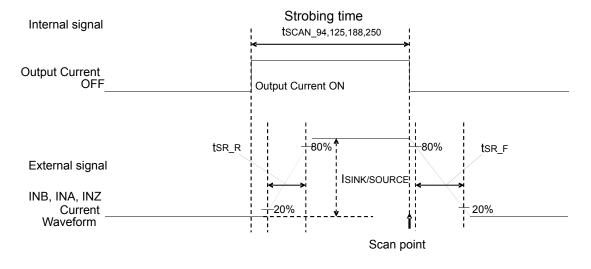

(Note 17) "H" width of internal signal (Ref. Page 12 Figure 6). (Note 18) Reference value.

Table 12. Electrical Characteristics (Digital Interface Characteristics)

| Parameter                                        | Symbol/Name           | Min | Тур                      | Max  | Unit |

|--------------------------------------------------|-----------------------|-----|--------------------------|------|------|

| SCLK Frequency                                   | f <sub>SCLK</sub>     | -   | -                        | 4.4  | MHz  |

| Setup Time from CSB Fall to SCLK Rise            | t <sub>LEAD</sub>     | 100 | -                        | 1000 | ns   |

| Setup Time from SCLK Fall to CSB Rise            | t <sub>LAG</sub>      | 50  | -                        | 500  | ns   |

| Setup Time from SI to SCLK Fall                  | t <sub>SI(SU)</sub>   | 16  | -                        | -    | ns   |

| Hold Time from SCLK Fall to SI                   | t <sub>SI(HOLD)</sub> | 20  | -                        | -    | ns   |

| SI, CSB, SCLK Rise Time                          | t <sub>R(SI)</sub>    | -   | 5.0 <sup>(Note 19)</sup> | -    | ns   |

| SI, CSB, SCLK Fall Time                          | t <sub>F(SI)</sub>    | -   | 5.0 <sup>(Note 19)</sup> | -    | ns   |

| Time from CSB Fall to SO Output Low Impedance    | t <sub>SO(EN)</sub>   | -   | -                        | 55   | ns   |

| Time from CSB Rising to SO Output High Impedance | t <sub>SO(DIS)</sub>  | -   | -                        | 55   | ns   |

| SCLK "H" Level Width                             | t <sub>SCLKH</sub>    | 75  | -                        | -    | ns   |

| SCLK "L" Level Width                             | t <sub>SCLKL</sub>    | 75  | -                        | -    | ns   |

| Time from SCLK Rise to Stable SO Data Output     | t                     |     | 25                       | 55   | ne   |

| SO CL=20pF                                       | t <sub>VALID</sub>    | -   | 25                       | ນວ   | ns   |

| CSB "H" Level Time                               | t <sub>CSBH</sub>     | 150 | -                        | -    | μs   |

(Note 19) Reference value.

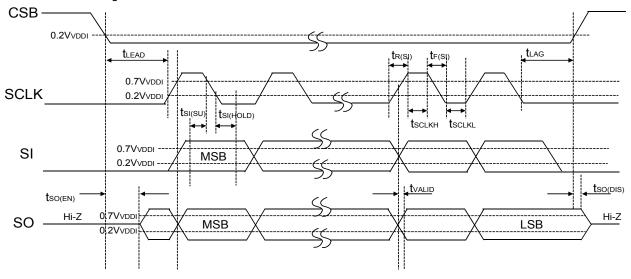

# **Timing Chart**

Serial Access Timing

Figure 4. Serial Access Timing

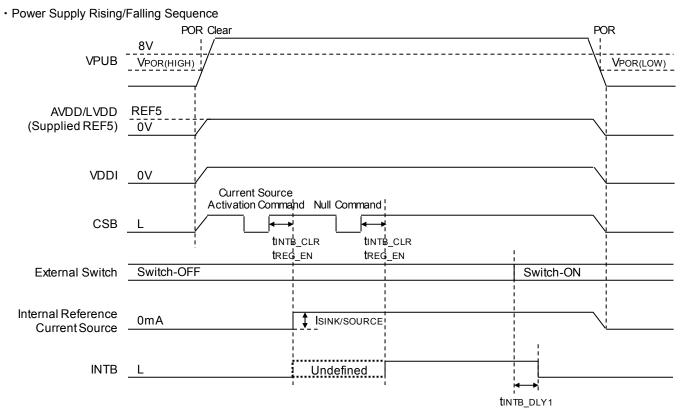

Figure 5. Power Supply Rising/Falling Sequence

· Source/Sink Current Rise and Fall Time

Figure 6. Intermittent Monitoring Enabled (FSQ=0, FSQZ/A/B=0, CMB/A/Z=1), Source/Sink Current Rise and Fall Time

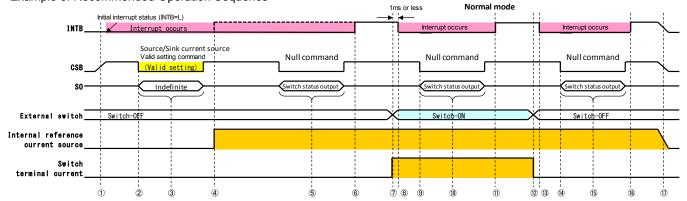

## [Basic Operation 1] Detection of Switch Status Change (Continuous Monitoring)

Upon detection of a change in switch status, interrupt (INTB="H"→"L") occurs and the IC requests serial communication with the MCU.

Figure 7. Basic Operation 1

- ①After power is turned on, interrupt (INTB="L") occurs.

- ②By serial communication, the switch status is obtained by the MCU at CSB falling edge.

- 3Since the current source is OFF, the switch terminal is "Hi-Z", and the output of SO is undefined.

- 4)Internal reference current source is activated

- 5 Switch status is output by SO.

- ⑥Interrupt is cleared (INTB="L"→ "H") by CSB rising edge and prepares for switch change.

- ⑦Switch change occurs (OFF→ON) and IC detects switch status change.

- ®Interrupt (INTB="H"→"L") is notified to MCU, and serial communication is requested

- 9By serial communication, switch status is obtained by the MCU at CSB falling edge.

- **®**Switch status is output by SO.

- ①Interrupt is cleared (INTB="L"→ "H") by CSB rising edge and prepares for switch change.

- <sup>®</sup>Switch change occurs (ON→OFF) and IC detects switch status change.

- ③Interrupt (INTB="H"→"L") is notified to MCU, and serial communication is requested

- (4) By serial communication, the switch status is obtained by the MCU at CSB falling edge.

- 15 Switch status is output by SO.

- bInterrupt is cleared (INTB="L" $\rightarrow$ "H") by CSB rising edge and prepares for switch change.

- ①Power is turned off.

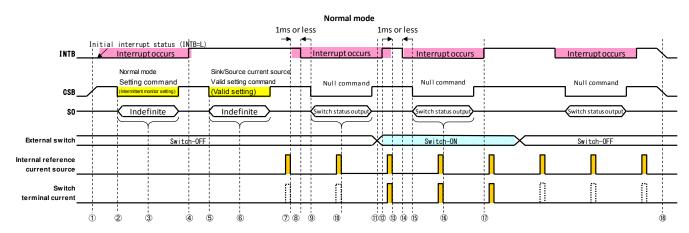

#### [Basic Operation 2] Detection of Switch Status Change (Intermittent Monitoring)

When Intermittent Monitoring is enabled, switch status is monitored by periodically turning the current source on and off. Intermittent monitoring allows low power consumption.

Figure 8. Basic Operation 2

- ①After power is turned on, interrupt (INTB="L") occurs.

- ②By serial communication, the switch status is obtained by the MCU at CSB falling edge.

- 3Since the current source is OFF, the switch terminal is "Hi-Z", and the output of SO is undefined.

- ⊕Interrupt is cleared (INTB="L"→ "H") by CSB rising edge and prepares for switch change.

- ⑤By serial communication, switch status is obtained by the MCU at CSB falling edge.

- ⑤Since the current source is OFF, the switch terminal is "Hi-Z", and the output of SO is undefined.

- TIC gets the switch status when the current source is ON.

- ®Interrupt (INTB="H"→"L") is notified to MCU, and serial communication is requested

- (9) By serial communication, switch status is obtained by the MCU at CSB falling edge.

- ①IC detects switch status change.

- 1Interrupt is cleared (INTB="L" $\rightarrow$  "H") by CSB rising edge and prepares for switch change.

- <sup>(3)</sup>IC detects switch status change.

- ♠Interrupt (INTB="H"→"L") is notified to MCU, and serial communication is requested

- (5) By serial communication, switch status is obtained by the MCU at CSB falling edge.

- 16 Switch status is output by SO.

- $\widehat{\mathbb{I}}$ Interrupt is cleared (INTB="L" $\rightarrow$  "H") by CSB rising edge and prepares for switch change.

- ®Power is turned off.

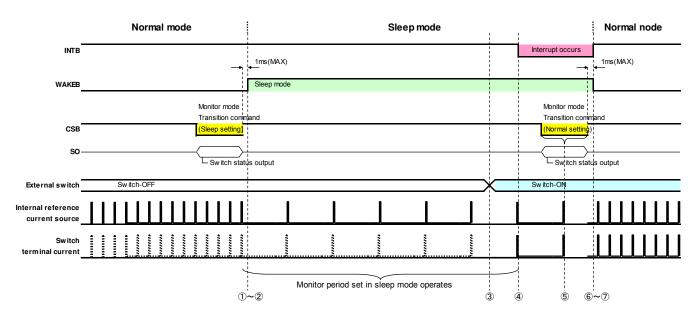

#### [Basic Operation 3] Sleep Mode Operation (Manual Transition)

When MDC register of Monitor Mode Transition Command is set to "1", mode is changed to sleep. When MDC register of Monitor Mode Transition Command is set to "0", mode is changed to normal. During sleep mode, WAKEB is in "Hi-Z" state and its voltage level is the level of the external pull-up.

Figure 9. Basic Operation 3

- ①Monitor mode transition command (Sleep mode setting) is received from MCU.

- 2Transition to sleep mode.

- $\begin{tabular}{ll} \hline \end{tabular} \begin{tabular}{ll} \hline \end{$

- 4IC detects switch status change.

- 5IC informs MCU the interrupt (INTB="H" $\rightarrow$ "L") and switch status is output by SO.

- 6 Monitor mode transition command (Normal mode setting) is received from MCU.

- 7)Transition to normal mode.

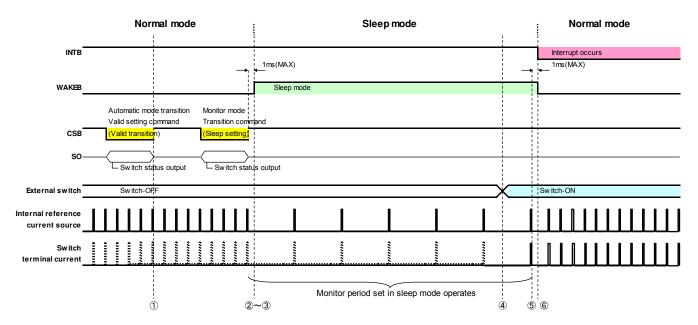

#### [Basic Operation 4] Sleep Mode Operation (Automatic Transition to Normal Mode)

Automatic transition from sleep mode to normal mode when a switch status changes is possible when the automatic mode transition setting is enabled.

During sleep mode, WAKEB is in "Hi-Z" state and its voltage level is the level of the external pull-up.

Figure 10. Basic Operation 4

- 1) Automatic transition of mode is enable.

- ②Monitor mode transition command (sleep mode setting) is received from MCU.

- 3 Transition to sleep mode.

- 4Switch change occurs (OFF $\rightarrow$ ON).

- 5IC detects switch status change.

- ⑥IC informs the interruption to MCU with INTB("H" →"L") and changes to Normal mode automatically.

# **Description of Functions**

#### 1. Power on Reset (POR)

Upon the application of an external voltage to VPUB, REF5 output is generated by the LDO inside the IC.

When REF5  $\leq$  4.2(Typ), POR is activated.

When REF5  $\geq$  4.3(Typ), POR is deactivated.

#### 2. Serial Interface

Communication between BD3375MUV-M and the MCU uses terminals chip select bar input (CSB), serial clock input (SCLK), serial data input (SI), and serial data output (SO).

CSB is internally pulled-up to VDDI. When CSB status is "0", SCLK and SI inputs are valid, and it is possible to read data from SO. When CSB status is "1", SCLK and SI inputs are invalid, and SO status is "Hi-Z".

#### · Communication Frame

The transmitted frame by the MCU is a 40-bit structure composed of the transmission and reception discrimination (2-bit), the address (6-bit), the data (24-bit), and the CRC (8-bit). The transmission and reception discrimination (2-bit) is intended to differentiate between the transmitted and the received frame. The command (6-bit) sets various settings such as the "valid interrupt setting command". The CRC (8-bit) outputs the result of a 39 to 8 bit CRC calculation. If a CRC error occurs, either when the structure of the frame is not 40-bit or when the transmission and reception discrimination bit is an error (the 33-bit of the SO frame is "H"), communication error is output and data is not recognized. As for writing, SI data is latched by internal shift register at timing of SCLK falling.

Table 13. Serial Data Input (SI)

| Communication frame | 39               | 38 | 37 | 36 | 35 | 34 | 33 | 32 | 31 | 30 | 29 | 28  | 27 | 26 | 25 | 24 |     |

|---------------------|------------------|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|-----|

| SI input bit        | Register address |    |    |    |    |    |    |    |    |    |    |     |    |    |    |    |     |

|                     | 23               | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12  | 11 | 10 | 9  | 8  | 7-0 |

| Setting data        |                  |    |    |    |    |    |    |    |    |    |    | CRC |    |    |    |    |     |

The received frame by the MCU has two types of bit alignment, "switch status output" and "register value output".

The switch status output bit alignment is a 40-bit structure composed of transmission and reception discrimination (2-bit), a fixed value (1-bit), interrupt factor output (5-bit), another fixed value (1-bit), mode status output (1-bit), switch status output (22-bit), and CRC (8-bit).

Transmission and reception discrimination (2-bit) is intended to discriminate transmit and receive frame. The interrupt factor is discussed on Page 19. When an interrupt factor occurs, the corresponding bit becomes "1". Mode status (1-bit) is "0" when set to normal mode, and it is "1" when set to sleep mode. Switch status output (22-bit) is "1" when external switch is ON, and it is "0" when external switch is OFF. The CRC (8-bit) outputs the result of a 39 to 8 bit CRC calculation.

The switch status is latched to the timing of CSB falling edge. The then in order of interrupt factor output, mode status and switch status output are output from SO by SCLK rising.

Table 14. Serial Data Output (SO-Switch Status Output)

| Output frame  | 39                          | 38 | 37 | 36 | 35      | 34       | 33                          | 32 | 31 | 30   | 29 | 28     | 27     | 26     | 25     | 24 |     |

|---------------|-----------------------------|----|----|----|---------|----------|-----------------------------|----|----|------|----|--------|--------|--------|--------|----|-----|

| SO output bit | 1                           | 0  | 0  |    | Interru | ot facto | r outpu                     |    | 0  | Mode |    | Switch | INB5-0 | status | output |    |     |

|               | 23                          | 22 | 21 | 20 | 19      | 18       | 17                          | 16 | 15 | 14   | 13 | 12     | 11     | 10     | 9      | 8  | 7-0 |

|               | Switch INA7-0 status output |    |    |    |         |          | Switch INZ7-0 status output |    |    |      |    |        |        | CRC    |        |    |     |

The register value output bit alignment is a 40-bit structure composed of transmission and reception discrimination (2-bit), a fixed value (1-bit), interrupt factor output (5-bit), register value output (24-bit), and CRC (8-bit).

The data is output by SO at SCLK's rising edge after the CSB falling edge of the command following the register value output command

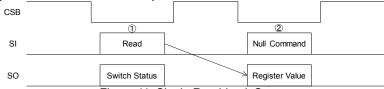

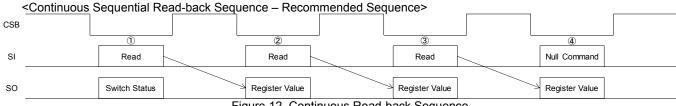

The bit alignment of the register value output is shown on Table 37. The sequence of register value output is shown in Figure 11 and Figure 12.

Table 15. Serial Data Output (SO-Register Value Output)

| Output frame  | 39                    | 38 | 37 | 36 | 35                                            | 34 | 33 | 32 | 31 | 30 | 29  | 28 | 27 | 26 | 25 | 24 |     |

|---------------|-----------------------|----|----|----|-----------------------------------------------|----|----|----|----|----|-----|----|----|----|----|----|-----|

| SO output bit | 1                     | 0  | 0  |    | Interrupt factor output Register value output |    |    |    |    |    |     |    |    |    |    |    |     |

|               | 23                    | 22 | 21 | 20 | 19                                            | 18 | 17 | 16 | 15 | 14 | 13  | 12 | 11 | 10 | 9  | 8  | 7-0 |

|               | Register value output |    |    |    |                                               |    |    |    |    |    | CRC |    |    |    |    |    |     |

The register value output command (Table 38 RIER to RMDR) is used to read-back the register value written by register write command (Table 37 IER to MDR).

Figure 11 describes the single read-back sequence. Figure 12 describes the continuous read-back sequence.

<Single Read-back Sequence - Recommended Sequence>

- Figure 11. Single Read-back Sequence

- Send the register value output command. The switch status is output by SO.

- Read the register value by sending the Null command. The result of the register value output command ① is output by SO.

- Figure 12. Continuous Read-back Sequence

- (1) Send the register value output command. The switch status is output by SO.

- Send the register value output command following ①. (The address of the register value output command does not need to be the next address.)

- (3) Send the register value output command repeatedly as needed. The SO output at each command is the result of the previous register value output command.

- **(4**) Send the Null command in the end. The register value of the previous register output command is output by SO.

# 3. Switch Status Output

Switch status can be sent through SO output.

#### 4. Interrupt (INTB operation)

There are five interrupt factors that cause the INTB terminal to output an "L". The type of interrupt factor that occurred can be checked in the SO output when CSB is "L".

INTB output will return to "H" once the interrupt factor is cleared by the rising edge of CSB. The INTB terminal is an open-drain output that is internally pulled-up to VDDI.

### Interrupt Factors

The interrupt factors are shown below:

| Interrupt Factor                                        | Interrupt flag (SO output)    | Flag name    |

|---------------------------------------------------------|-------------------------------|--------------|

| ① Test detection                                        | SO output bit [36]            | : "test_flg" |

| ② Thermal shutdown detection                            | SO output bit [35]            | : "them_flg" |

| 3 Reset detection                                       | SO output bit [34]            | : "rst_flg"  |

| Communication error detection                           | SO output bit [33]            | : "err_flg"  |

| (CRC error, 40-bit frame error, or transmission and rec | ception discrimination error) |              |

| ⑤ Switch status change detection                        | SO output bit [32]            | : "sw_flg"   |

#### 1 Test detection

The IC generates an interrupt after a transition to test mode. The TEST terminal should always be connected to ground.

#### 2 Thermal shutdown detection

Interrupt occurs when the thermal shutdown circuit detects a temperature higher than the allowable junction temperature inside IC.

#### ③ Reset detection

Interrupt occurs after the activation of Power on Reset (POR) or the transmission of the reset command. Upon POR activation, the SO output interrupt flag "rst\_flg" is reflected instantly. With reset command transmission, "rst\_flg" is reflected on the next command transmission.

#### (4) Communication error detection

Interrupt occurs due to either a CRC error, a 40-bit frame error, or a command transmission error. The interrupt flag "err flg" is triggered by the following:

CRC error : when there is a Cyclic Redundancy Check error 40-bit frame error : when the command received is not 40-bit

Transmit and receive determination error: when the first two bits of the command received is not [39:38]="01"

#### (5) Switch status change detection

Interrupt occurs when switch a status changes (switch-ON-OFF or switch-OFF-ON).

#### · Clearing of INTB output and interrupt factor

The INTB "L" output and the interrupt factor are both cleared by the CSB rising edge during command transmission. In case a new interrupt factor occurs during command transmission, the interrupt factor is not cleared. The new interrupt factor is reflected on the next command transmission.

The interrupt factor is not cleared by the register readout that follows the register value output command.

#### 5. Operating Modes

BD3375MUV-M has two types of operating mode, the normal and the sleep mode. Transition between the two modes can be done by sending the correct "Monitor Mode Transition Command". The current mode of operation can be checked through the WAKEB and the SO terminal outputs.

Monitor Mode Transition register address (0x4F): Bit [31]: 0=Normal mode, 1=Sleep mode)

#### · Normal Mode

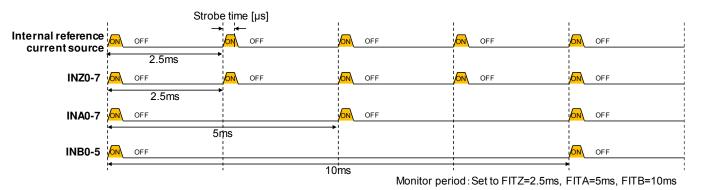

Normal mode operation can be set to continuous monitoring, wherein the switch status is checked by a continuously ON current source, or to intermittent monitoring, wherein the switch status is checked by a regularly ON/OFF current source. The period of intermittent monitoring (Note 20) can be set according to power supply system while strobe time (Note 21) is common for all switch terminals.

At normal mode, WAKEB is "L" and the 30-bit of the SO output is "0".

#### · Sleep Mode

Sleep mode operation, like in normal mode, can be set to continuous monitoring or intermittent monitoring. The monitoring period (Note 20) of intermittent monitoring can be set according to power supply system. The strobe time (Note 21) is common for all switch terminals and both modes.

The difference with normal mode is that, from sleep mode, it is possible to change to normal mode automatically when interrupt occurs. (Automatic mode transition function)

At sleep mode, WAKEB is in "Hi-Z" state and its voltage level is the level of the external pull-up. The 30-bit of SO output is "1" at sleep mode.

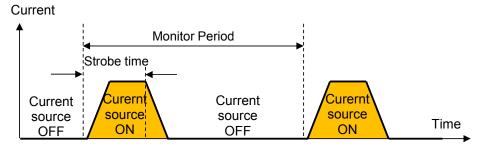

(Note 20) Monitor period (Note 21) Strobe time

Figure 13. Intermittent Monitoring

#### 6. Automatic Mode Transition Function

By sending the "Automatic Mode Transition Command" through setting the MIR register (0x4E) to "1", automatic transition from sleep to normal mode is possible. The conditions for a change in mode from sleep to normal to occur for both enabled and disabled "Automatic Mode Transition Function" are shown below:

- · Conditions for sleep to normal mode transition when "Automatic Mode Transition Function" is enabled:

- 1. Normal mode transition command is sent

- 2. POR occurs or reset command sent (Initialization)

- 3. A switch status changes (The "Switch Change Interrupt Setting" should be enabled)

- · Conditions for sleep to normal mode transition when "Automatic Mode Transition Function" is disabled:

- 1. Normal mode transition command is sent

- 2. POR occurs or reset command sent (Initialization)

[Extension Function1: Intermittent Monitoring at the Same Time (with Current Slope)]

In intermittent monitoring, it is possible to detect the status of the all switches at the same time. When all inputs are set to detect the switch status by intermittent monitoring, the wetting current has a rising and falling slope.

Normal Mode Setting Register (0x4B) : 31 to 28 bit is "0000" and intermittent monitoring setting Sleep Mode Setting Register (0x4C) : 31 to 28 bit is "0000" and intermittent monitoring setting

Figure 14. Intermittent Monitoring at the Same Time Example

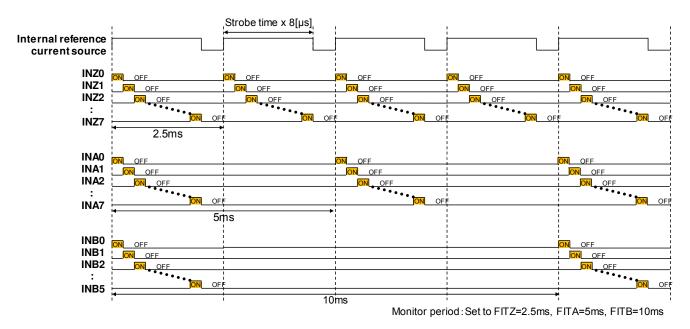

[Extension Function 2: Sequential Monitoring by Power Supply System]

In this type of sequential monitoring, the status of the switches within a power supply system is monitored one at a time. This type has no slope. Since no two or more current sources in a power supply system are ON at the same time, radiation noise is reduced.

Figure 15. Sequential Monitoring by Power Supply System Example

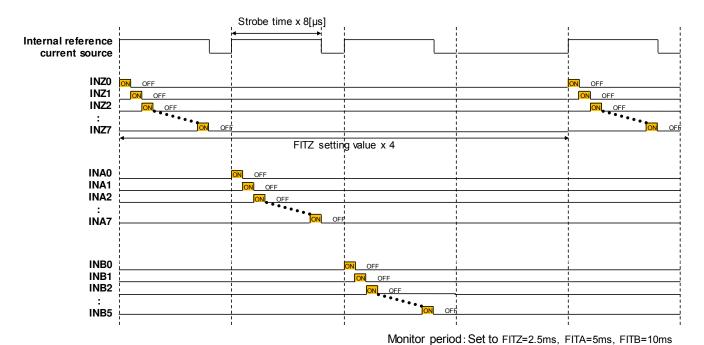

[Extension Function 3: Sequential Monitoring of All Switch Terminals]

In this type of sequential monitoring, the status of all switches is monitored one at a time.

Since no two or more current sources are ON at the same time, radiation noise is reduced. This type has no slope.

The monitoring period for all switches increases by four times the monitoring period set for the INZ channels as shown in Figure 16. Uniform sequential monitoring and sequential monitoring by power supply should not be enabled at the same time. In case the two sequential monitoring methods are activated simultaneously, the method which prevails is uniform sequential monitoring.

Figure 16. Sequential Monitoring of All Switches Terminals Example

#### 7. WAKEB Terminal

WAKEB is an open drain output pin.

In normal mode, its output is "L". In sleep mode, its output is "Hi-Z" and its voltage level is the level of the external pull-up.

# 8. Source/Sink Current Source for Switch Terminal

There are three types of switch terminal inputs with internal current source: INZ, INA, and INB. The current level can be set for each switch terminal.

- Current Source of INZ system (INZ0 INZ7)

- This current source is used to source or sink current to the external switch. The wetting current can be interchanged between pull-up and pull-down. VPUA is the power supply for the pull-up current source.

- Current Source of INA (INA0 INA7)

This current source is used to source current to the external switch. VPUA is the power supply

Current Source of INB (INB0 – INB5)

This current source is used to source current to the external switch. VPUB is the power supply.

The current source settings can be fixed by INZ current source/sink selection command, the current source setting command, and the holding current/wetting current value setting command.

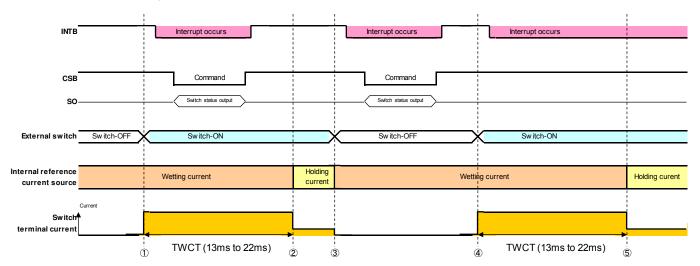

#### 9. Wetting Current Timer

The wetting current timer is 13ms to 22ms. This function can be enabled individually for each switch terminal. The timer starts after the switch has been detected as ON. After the 13ms to 22ms timer is finished, the wetting current (10mA/15mA) is switched to holding current (1mA/3mA/5mA). The timer is reset after the switch is turned OFF.

[Function operation1] Wetting Current Timer (Continuous Operation)

Figure 17. Wetting Current Timer (Continuous Operation)

- ① Switch change occurs (OFF→ON), IC detects switch status change.

- 2 When ON state of the switch continues for more than 13ms to 22ms, the holding current is output.

- ③ Switch change occurs (ON→OFF).

- ¶ Switch change occurs (OFF→ON), IC detects switch status change.

- ⑤ When ON state of the switch continues for more than 13ms to 22ms, the holding current is output.