Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Sound Processor Series for Car Audio

# Pb Free ROHM Electronic Components

# Sound processor with Built-in 2-band Equalizer

# BD37503FV

#### General Description

Sound processor which has built-in 4input selector and 2-band equalizer filter. And, loudness filter and 2nd-order anti-aliasing filter which attenuate noise occurs at output of DAC are available, either one by switching.

#### Features

- Built-in differential input selector that can make various combination of single-ended / differential input.

- Reduce switching noise by using advanced switch circuit

- Built-in ground isolation amplifier inputs, ideal for external stereo input.

- Decrease the number of external components by built-in 2nd-order anti-aliasing filter

- Decrease the number of external components by built-in 2-band equalizer filter and loudness filter.

- A PCB area can be reduced and PCB layouts become easy thanks to that signal flow is gathered to one direction by arrangement of input and output left side and right side separately.

- It is possible to control by 3.3V / 5V for I<sup>2</sup>C BUS serial controller.

### Applications

It is the optimal for the car audio. Besides, it is possible to use for the audio equipment of mini Compo, micro Compo, TV etc with all kinds.

# Key Specifications

■ Total harmonic distortion : 0.001%(Typ.) 2.2Vrms(Typ.) Maximum input voltage : ■ Common mode rejection ratio : 50dB(Min.) ■ Maximum output voltage : 2.1Vrms(Typ.) ■ Output noise voltage :  $5.8 \mu \text{ Vrms(Typ.)}$ ■ Residual output noise voltage :  $2.8 \,\mu$  Vrms (Typ.) ■ Ripple rejection: -70dB (Typ.) Operating temperature range -40°C to +85°C

● Package W(Typ.) x D(Typ.) x H(Max.) SSOP-B20 6.50mm x 6.40mm x 1.45mm

SSOP-B20

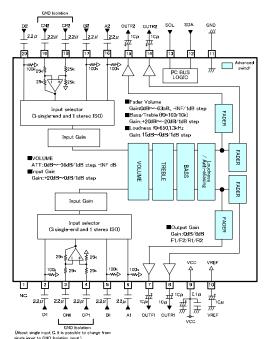

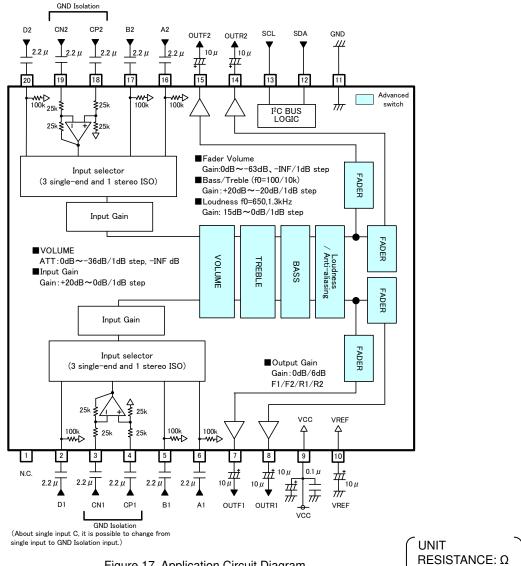

#### Typical Application Circuit

Figure 1. Application Circuit Diagram

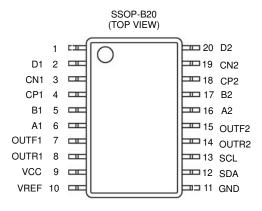

# Pin Configuration

Figure 2. Pin configuration

#### Pin Description

| Terminal<br>No. | Symbol | Description of terminals         | Terminal<br>No. | Symbol | Description of terminals                      |

|-----------------|--------|----------------------------------|-----------------|--------|-----------------------------------------------|

| 1               | N.C.   | Non connection terminal          | 11              | GND    | GND terminal                                  |

| 2               | D1     | D input terminal of 1ch          | 12              | SDA    | I <sup>2</sup> C Communication data terminal  |

| 3               | CN1    | C negative input terminal of 1ch | 13              | SCL    | I <sup>2</sup> C Communication clock terminal |

| 4               | CP1    | C positive input terminal of 1ch | 14              | OUTR2  | Rear output terminal of 2ch                   |

| 5               | B1     | B input terminal of 1ch          | 15              | OUTF2  | Front output terminal of 2ch                  |

| 6               | A1     | A input terminal of 1ch          | 16              | A2     | A input terminal of 2ch                       |

| 7               | OUTF1  | Front output terminal of 1ch     | 17              | B2     | B input terminal of 2ch                       |

| 8               | OUTR1  | Rear output terminal of 1ch      | 18              | CP2    | C positive input terminal of 2ch              |

| 9               | VCC    | Power supply terminal            | 19              | CN2    | C negative input terminal of 2ch              |

| 10              | VREF   | BIAS terminal                    | 20              | D2     | D input terminal of 2ch                       |

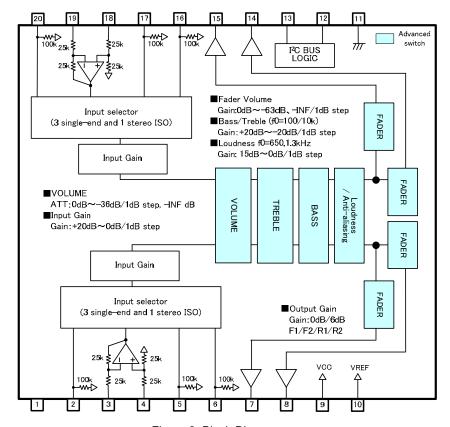

# ●Block Diagram

Figure 3. Block Diagram

#### ● Absolute Maximum Ratings (Ta=25°C)

| Item                 | Symbol | Rating                                      | Unit |

|----------------------|--------|---------------------------------------------|------|

| Power supply Voltage | VCC    | 10.0                                        | V    |

| Input voltage        | Vin    | VCC+0.3 to GND-0.3<br>SCL,SDA: 7 to GND-0.3 | V    |

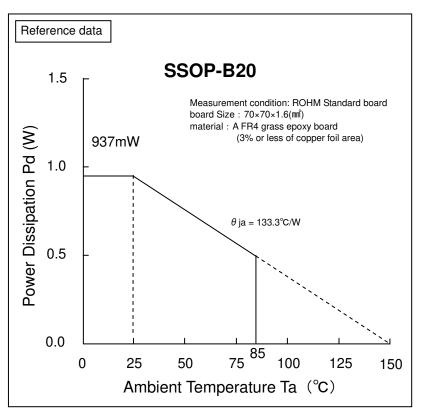

| Power Dissipation    | Pd     | 937 ※1                                      | mW   |

| Storage Temperature  | Tastg  | -55 to +150                                 | °C   |

\*1 This value decreases 7.5mW/°C for Ta=25°C or more.

ROHM standard board shall be mounted.

ROHM Standard board

\*1 Thermal resistance size : 70×70×1.6(mil)

\*2 Thermal resistance size : 70×70×1.6(mil)

size: 70×70×1.6(mil)

material: FR4 A FR4 grass epoxy board(3% or less of copper foil area)

# Recommended Operating Rating

| Item                 | Symbol | MIN. | TYP. | MAX. | Unit |

|----------------------|--------|------|------|------|------|

| Power supply Voltage | VCC    | 7.0  | 8.5  | 9.5  | ٧    |

| Temperature          | Topr   | -40  | -    | +85  | ပ    |

# Electrical Characteristic

Unless specified particularly, Ta=25°C, VCC=8.5V, f=1kHz, Vin=1Vrms, Rg=600 $\Omega$ , RL=10k $\Omega$ , A input, Input gain 0dB, Volume 0dB, Tone control 0dB, Loudness 0dB, Fader 0dB, Output Gain 0dB

|                | /olume 0dB, Tone control 0dB, Loudnes | ss oub, raue        | i uub, U | uipui Gai | II UUD |       |                                                                               |

|----------------|---------------------------------------|---------------------|----------|-----------|--------|-------|-------------------------------------------------------------------------------|

| S              | ltem                                  | Symbol              |          | Limit     |        | Unit  | Condition                                                                     |

| BLOCK          | пеш                                   | Symbol              | MIN.     | TYP.      | MAX.   | Offic | Condition                                                                     |

|                | Current upon no signal                | IQ                  | _        | 20        | 27     | mA    | No signal                                                                     |

|                | Voltage gain                          | G∨                  | -1.5     | 0         | 1.5    | dB    | Gv=20log(VOUT/VIN)                                                            |

|                | Channel balance                       | СВ                  | -1.5     | 0         | 1.5    | dB    | $CB = G_V 1 - G_V 2$                                                          |

|                | Total harmonic distortion             | THD+N1              | _        | 0.001     | 0.05   | %     | VOUT=1Vrms<br>BW=400-30KHz                                                    |

| 3AL            | Output noise voltage *                | V <sub>NO</sub>     | _        | 5.8       | 18     | μVrms | $Rg = 0\Omega$<br>BW = IHF-A                                                  |

| GENERAL        | Residual output noise voltage *       | $V_{NOR}$           | _        | 2.8       | 9      | μVrms | Fader = $-\infty dB$<br>Rg = $0\Omega$<br>BW = IHF-A                          |

|                | Cross-talk between channels *         | СТС                 | _        | -100      | -90    | dB    | Rg = 0Ω<br>CTC=20log(VOUT/VIN)<br>BW = IHF-A                                  |

|                | Ripple rejection                      | RR                  | _        | -70       | -40    | dB    | f=1kHz<br>VRR=100mVrms<br>RR=20log(VCC IN/VOUT)                               |

|                | Input impedance(A, B, D)              | R <sub>IN S</sub>   | 70       | 100       | 130    | kΩ    |                                                                               |

|                | Input impedance(CP,CN)                | R <sub>IN D</sub>   | 35       | 50        | 65     | kΩ    |                                                                               |

| TOR            | Maximum input voltage                 | V <sub>IM</sub>     | 2        | 2.2       | _      | Vrms  | V <sub>IM</sub> at THD+N(VOUT)=1%<br>BW=400-30KHz                             |

| INPUT SELECTOR | Cross-talk between selectors *        | CTS                 | _        | -100      | -90    | dB    | $Rg = 0\Omega$<br>CTS=20log(VOUT/VIN)<br>BW = IHF-A                           |

| INPU.          | Common mode rejection ratio           | CMRR                | 50       | 60        | _      | dB    | CP1 and CN1 input<br>CP2 and CN2 input<br>CMRR=20log(VIN/VOUT)<br>BW = IHF-A, |

| GAIN           | Minimum input gain                    | G <sub>IN MIN</sub> | -2       | 0         | 2      | dB    | Input gain 0dB<br>VIN=100mVrms<br>G <sub>IN</sub> =20log(VOUT/VIN)            |

| INPUT GAIN     | Maximum input gain                    | G <sub>IN MAX</sub> | 18       | 20        | 22     | dB    | Input gain 20dB<br>VIN=100mVrms<br>G <sub>IN</sub> =20log(VOUT/VIN)           |

|                | Gain set error                        | G <sub>IN ERR</sub> | -2       | 0         | 2      | dB    | GAIN=+1 to +20dB                                                              |

| X              |                         | 0 1 1                   |      | Limit |      |      | Q IV                                                                                                                                                       |

|----------------|-------------------------|-------------------------|------|-------|------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BLOCK          | Item                    | Symbol                  | MIN. | TYP.  | MAX. | Unit | Condition                                                                                                                                                  |

| IME            | Maximum gain            | G <sub>V MAX</sub>      | -1.5 | 0     | 1.5  | dB   | Volume = 0dB<br>VIN=100mVrms<br>Gv=20log(VOUT/VIN)                                                                                                         |

| VOLUME         | Maximum attenuation *   | G <sub>V MIN</sub>      | _    | -100  | -85  | dB   | Volume = -∞dB<br>Gv=20log(VOUT/VIN)<br>BW = IHF-A                                                                                                          |

|                | Attenuation set error   | G <sub>V ERR1</sub>     | -2   | 0     | 2    | dB   | ATT=0dB to -36dB                                                                                                                                           |

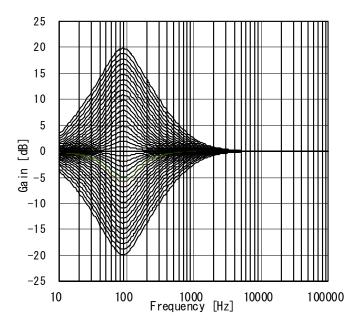

| S              | Maximum boost gain      | G <sub>B BST</sub>      | 18   | 20    | 22   | dB   | Gain=+20dB f=100Hz<br>VIN=100mVrms<br>G <sub>B</sub> =20log (VOUT/VIN)                                                                                     |

| BASS           | Maximum cut gain        | G <sub>B CUT</sub>      | -22  | -20   | -18  | dB   | Gain=-20dB f=100Hz<br>VIN=2Vrms<br>G <sub>B</sub> =20log (VOUT/VIN)                                                                                        |

|                | Gain set error          | G <sub>B ERR</sub>      | -2   | 0     | 2    | dB   | Gain=+20 to -20dB f=100Hz                                                                                                                                  |

| 3LE            | Maximum boost gain      | G <sub>T BST</sub>      | 18   | 20    | 22   | dB   | Gain=+20dB f=10kHz<br>VIN=100mVrms<br>G <sub>T</sub> =20log (VOUT/VIN)                                                                                     |

| TREBLE         | Maximum cut gain        | G <sub>T CUT</sub>      | -22  | -20   | -18  | dB   | Gain=-20dB f=10kHz<br>VIN=2Vrms<br>G <sub>T</sub> =20log (VOUT/VIN)                                                                                        |

|                | Gain set error          | G <sub>T ERR</sub>      | -2   | 0     | 2    | dB   | Gain=+20 to -20dB f=10kHz                                                                                                                                  |

|                | Maximum gain            | G <sub>F BST</sub>      | -2   | 0     | 2    | dB   | Gain=0dB<br>G <sub>F</sub> =20log(VOUT/VIN)                                                                                                                |

| FADER          | Maximum attenuation *   | G <sub>F MIN</sub>      | _    | -100  | -90  | dB   | $\begin{aligned} & \text{Fader} = -\infty \text{dB} \\ & \text{G}_{\text{F}} = 20 \text{log}(\text{VOUT/VIN}) \\ & \text{BW} = \text{IHF-A} \end{aligned}$ |

| DE             | Attenuation set error 1 | G <sub>F ERR1</sub>     | -2   | 0     | 2    | dB   | ATT=-1 to -15dB                                                                                                                                            |

| FA             | Attenuation set error 2 | G <sub>F ERR2</sub>     | -3   | 0     | 3    | dB   | ATT=-16 to -47dB                                                                                                                                           |

|                | Attenuation set error 3 | G <sub>F ERR3</sub>     | -4   | 0     | 4    | dB   | ATT=-48 to -63dB                                                                                                                                           |

|                | Output impedance        | R <sub>O FAD</sub>      | -    | _     | 50   | Ω    | VIN=100mVrms                                                                                                                                               |

|                | Maximum output voltage  | V <sub>OM F</sub>       | 2    | 2.1   | _    | Vrms | THD+N=1%<br>BW=400-30KHz                                                                                                                                   |

| LOUDNESS       | Maximum gain            | G <sub>LD MAX</sub>     | 13   | 15    | 17   | dB   | Gain=15dB<br>G <sub>LD</sub> =20log(VOUT/VIN)<br>BW=IHF-A                                                                                                  |

| LOUD           | Gain set error          | G <sub>LD ERR</sub>     | -2   | 0     | 2    | dB   | Gain=0dB to -15dB<br>G <sub>LD</sub> =20log(VOUT/VIN)                                                                                                      |

| OUTPUT<br>GAIN | Maximum gain            | G <sub>OUT</sub>        | 4    | 6     | 8    | dB   | Gain +6dB<br>VIN=100mVrms<br>G <sub>OUT</sub> =20log(VOUT/VIN)                                                                                             |

|                | Gain set error          | G <sub>OUT</sub><br>ERR | -2   | 0     | 2    | dB   | Gain=0dB, +6dB                                                                                                                                             |

<sup>%</sup>VP-9690A(Average value detection, effective value display) filter by Matsushita Communication is used for \* measurement. %Phase between input / output is same.

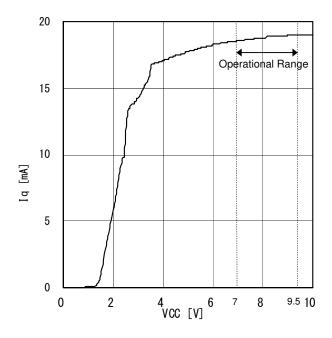

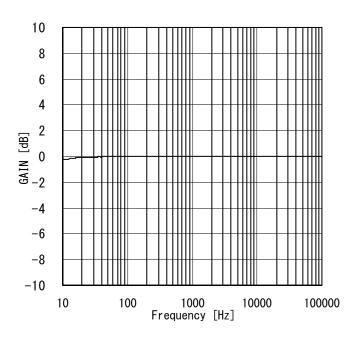

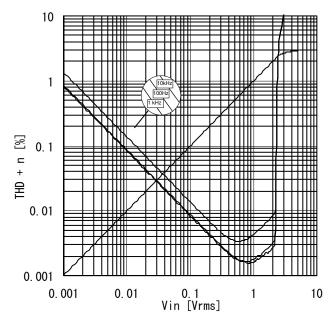

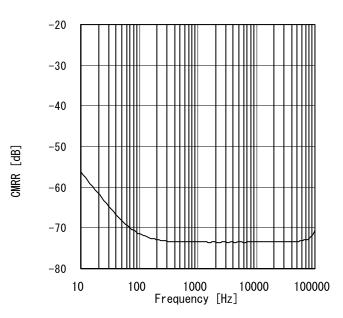

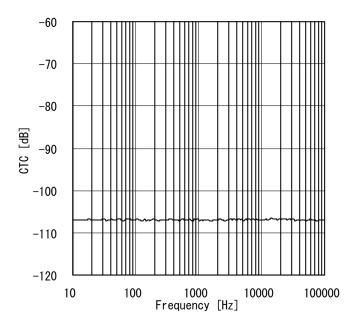

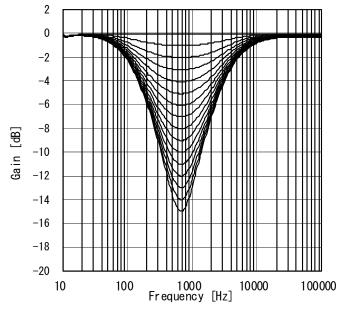

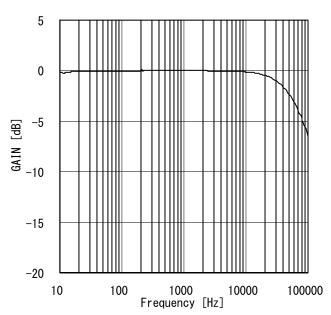

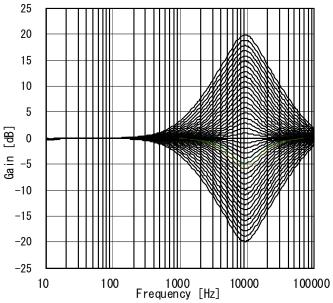

#### ● Typical Performance Curve (reference data)

Figure 4. Iq vs VCC

Figure 5. Gain vs Frequency

Figure 6. THD+n vs Input Voltage

Figure 7. CMRR vs Frequency

Figure 8. PSRR vs Frequency

Figure 9. Cross-talk between channels vs Frequency

Figure 10. Loudness Gain vs Frequency

Figure 11. Antifilter Gain vs Frequency

Figure 13. Treble Gain vs Frequency

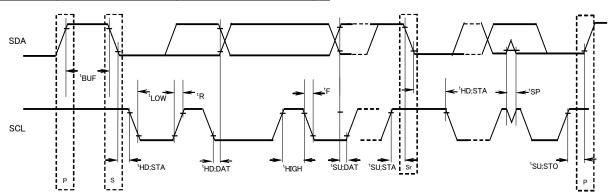

#### **●**CONTROL SIGNAL SPECIFICATION

#### (1) Electrical specifications and timing for bus lines and I/O stages

Figure 14. Definition of timing on the I<sup>2</sup>C-bus

Table 1 Characteristics of the SDA and SCL bus lines for I<sup>2</sup>C-bus devices

|   | Parameter                                                                                   | Symbol   | Fast-mode l <sup>2</sup> | 1    | Unit  |

|---|---------------------------------------------------------------------------------------------|----------|--------------------------|------|-------|

|   | T diamotoi                                                                                  | Cymbol   | MIN.                     | MAX. | Offic |

| 1 | SCL clock frequency                                                                         | fSCL     | 0                        | 400  | kHz   |

| 2 | Bus free time between a STOP and START condition                                            | tBUF     | 1.3                      | _    | μS    |

| 3 | Hold time (repeated) START condition. After this period, the first clock pulse is generated | tHD;STA  | 0.6                      | _    | μS    |

| 4 | LOW period of the SCL clock                                                                 | tLOW     | 1.3                      | _    | μS    |

| 5 | HIGH period of the SCL clock                                                                | tHIGH    | 0.6                      | _    | μS    |

| 6 | Set-up time for a repeated START condition                                                  | tSU;STA  | 0.6                      | _    | μS    |

| 7 | Data hold time                                                                              | tHD;DAT  | 0                        | _    | μS    |

| 8 | Data set-up time                                                                            | tSU; DAT | 100                      | _    | ns    |

| 9 | Set-up time for STOP condition                                                              | tSU;STO  | 0.6                      | _    | μS    |

All values referred to VIH min. and VIL max. Levels (see Table 2). About 7(tHD;DAT), 8(tSU;DAT), please make setup which has enough margin.

Table 2 Characteristics of the SDA and SCL I/O stages for I<sup>2</sup>C-bus devices

|    | Item                                                                        | Symbol | Fast-mode l | C-bus | Unit        |

|----|-----------------------------------------------------------------------------|--------|-------------|-------|-------------|

|    | Item                                                                        | Symbol | MIN.        | MAX.  | Offic       |

| 10 | LOW level input voltage: In case an input level is fixed                    | VIL    | -0.5        | 1     | V           |

| 11 | HIGH level input voltage: In case an input level is fixed                   | VIH    | 2.3         | -     | V           |

| 12 | Pulse width of spikes which must be suppressed by the input filter.         | tSP    | 0           | 50    | ns          |

| 13 | LOW level output voltage(open drain or open collector): at 3mA sink current | VOL1   | 0           | 0.4   | <b>&gt;</b> |

| 14 | Input current each I/O pin with an input voltage between 0.4V and 0.9V.     | li     | -10         | 10    | μΑ          |

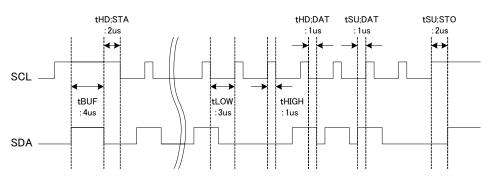

SCL clock frequency: 250kHz

Figure 15. A command timing example in the I2C data transmission

# (2) I<sup>2</sup>C BUS FORMAT

| _ |      | MSB  | LSB          |                                                    | MSB                                                                 | LSB |      | MSB | LSB  |      |      |  |  |

|---|------|------|--------------|----------------------------------------------------|---------------------------------------------------------------------|-----|------|-----|------|------|------|--|--|

|   | S    | Slav | e Address    | Α                                                  | A Select Address                                                    |     | Α    | [   | Data |      | Р    |  |  |

|   | 1bit | 8bit |              | 1bit                                               | 8bit                                                                |     | 1bit |     | 8bit | 1bit | 1bit |  |  |

|   |      | S    |              | = Sta                                              | = Start conditions (Recognition of start bit)                       |     |      |     |      |      |      |  |  |

|   |      | Sla  | ve Address   | = Re                                               | = Recognition of slave address. 7 bits in upper order are voluntary |     |      |     |      |      |      |  |  |

|   |      |      |              | The least significant bit is "L" due to writing.   |                                                                     |     |      |     |      |      |      |  |  |

|   |      | Α    |              | = ACKNOWLEDGE bit (Recognition of acknowledgement) |                                                                     |     |      |     |      |      |      |  |  |

|   |      | Se   | lect Address | = Select every of volume, bass and treble.         |                                                                     |     |      |     |      |      |      |  |  |

|   |      | Da   | ta           | = Data on every volume and tone.                   |                                                                     |     |      |     |      |      |      |  |  |

|   |      | Р    |              | = Stop condition (Recognition of stop bit)         |                                                                     |     |      |     |      |      |      |  |  |

# (3) I<sup>2</sup>C BUS Interface Protocol

1) Basic form

| / |              |     |   |                |     |   |     |     |   |   |

|---|--------------|-----|---|----------------|-----|---|-----|-----|---|---|

| S | Slave Addres | ss  | Α | Select Address |     |   | Dat | а   | Α | Р |

|   | MSB          | LSB |   | MSB            | LSB | М | SB  | LSE | } |   |

2) Automatic increment (Select Address increases (+1) according to the number of data.)

|   | S | Slave Addr | ess | Α | Select Add | ress | Α | Data1 | Α   | Data2 | Α  | <br>DataN | Α | Р   |  |

|---|---|------------|-----|---|------------|------|---|-------|-----|-------|----|-----------|---|-----|--|

| _ |   | MSB _      | LSB |   | MSB        | LSB  |   | MSB   | LSB | MSB I | SB | MSB       | L | .SB |  |

- (Example) ① Data1 shall be set as data of address specified by Select Address.

- 2 Data2 shall be set as data of address specified by Select Address +1.

- ③ DataN shall be set as data of address specified by Select Address +N-1.

3) Configuration unavailable for transmission (In this case, only Select Address1 is set.

| S | Slave Addr | ess A | Select A | ddress1 | Α | Data   | Α | Select Add | ress 2 | Α | Dat | ta  | Α | Р |

|---|------------|-------|----------|---------|---|--------|---|------------|--------|---|-----|-----|---|---|

|   | MSB        | LSB   | MSB      | LSB     | М | SB LSE | 3 | MSB        | LSB    | М | SB  | LSB | } |   |

(Note) If any data is transmitted as Select Address 2 next to data, it is recognized as data, not as Select Address 2.

# (4) Slave address

| MSB |            |    |    |    |    |    | LSB | _   |

|-----|------------|----|----|----|----|----|-----|-----|

| A6  | <b>A</b> 5 | A4 | A3 | A2 | A1 | A0 | R/W |     |

| 1   | 0          | 0  | 0  | 0  | 0  | 0  | 0   | 80H |

#### (5) Select Address & Data

| lance           | Select           | MSB                 |                      |               | Da         | ata             |           |    | LSB            |

|-----------------|------------------|---------------------|----------------------|---------------|------------|-----------------|-----------|----|----------------|

| Items           | Address<br>(hex) | D7                  | D6                   | D5            | D4         | D3              | D2        | D1 | D0             |

| Initial setup 1 | 01               | 1                   | 0                    | 1             | 0          | 0               | 0         | 0  | 0              |

| Initial setup 2 | 03               | Output<br>Gain      | 0                    | 0             | 0          | Loudness select | 0         | 0  | Loudness<br>fo |

| Input selector  | 05               | 0                   | 0 0 0 Input selector |               |            |                 |           | or |                |

| Input gain      | 06               | 0                   | 0 0 0 Input Gain     |               |            |                 |           |    |                |

| Volume gain     | 20               |                     | Volume Attenuation   |               |            |                 |           |    |                |

| Fader 1ch Front | 28               |                     | Fader Attenuation F1 |               |            |                 |           |    |                |

| Fader 2ch Front | 29               |                     |                      |               | Fader Atte | nuation F2      |           |    |                |

| Fader 1ch Rear  | 2A               |                     |                      |               | Fader Atte | nuation R1      |           |    |                |

| Fader 2ch Rear  | 2B               |                     |                      |               | Fader Atte | nuation R2      |           |    |                |

| Bass gain       | 51               | Bass<br>Boost/Cut   | 0                    | 0             |            |                 | Bass Gain |    |                |

| Treble gain     | 57               | Treble<br>Boost/Cut | 0                    | 0 Treble Gain |            |                 |           |    |                |

| Loudness Gain   | 75               | 0                   | 0 0 Loudness Gain    |               |            |                 |           |    |                |

| System Reset    | FE               | 1                   | 0                    | 0             | 0          | 0               | 0         | 0  | 1              |

| Advanced    | switch   |

|-------------|----------|

| / lavarioca | CAALCOLL |

#### Note

- 1. In function changing of the hatching part, it works Advanced switch.

- 2. Upon continuous data transfer, the Select Address is circulated by the automatic increment function, as shown below.

3. For the function of input selector, input gain and output gain etc, it is not corresponded for advanced switch. Therefore, please apply mute on the side of a set when changes these setting.

Select address 03(hex)

| _, | noot addition |        |    |                |   |          |   |   |   |  |

|----|---------------|--------|----|----------------|---|----------|---|---|---|--|

|    | fo            | MSB    |    | Loudness fo    |   |          |   |   |   |  |

|    | 10            | D7     | D6 | D5 D4 D3 D2 D1 |   |          |   |   |   |  |

|    | 650 Hz        | Output | 0  | 0              | 0 | Loudness | 0 | 0 | 0 |  |

| Ī  | 1.3k Hz       | Gain   | U  | U              | U | select   | U | U | 1 |  |

| Mode                 | MSB    |    | Loudness select |    |    |    |    |          |  |  |  |

|----------------------|--------|----|-----------------|----|----|----|----|----------|--|--|--|

|                      | D7     | D6 | D5              | D4 | D3 | D2 | D1 | D0       |  |  |  |

| Loudness             | Output | 0  | 0               | 0  | 0  | 0  | 0  | Loudness |  |  |  |

| Anti-aliasing filter | Gain   | U  | U               | U  | 1  | U  | U  | fo       |  |  |  |

| Coin | MSB |    | Output Gain       |   |          |   |   |          |  |  |

|------|-----|----|-------------------|---|----------|---|---|----------|--|--|

| Gain | D7  | D6 | D6 D5 D4 D3 D2 D1 |   |          |   |   |          |  |  |

| 0dB  | 0   | 0  | 0                 | 0 | Loudness | 0 | 0 | Loudness |  |  |

| +6dB | 1   | U  | U                 | U | select   | U | U | fo       |  |  |

Select address 05(hex)

| Mode        | MSB |    | Input Selector |    |    |    |    |    |  |  |

|-------------|-----|----|----------------|----|----|----|----|----|--|--|

| Mode        | D7  | D6 | D5             | D4 | D3 | D2 | D1 | D0 |  |  |

| A single    |     |    |                |    |    | 0  | 0  | 0  |  |  |

| B single    |     |    |                |    |    | 0  | 0  | 1  |  |  |

| C single    |     |    |                |    |    | 0  | 1  | 0  |  |  |

| D single    |     |    |                |    |    | 0  | 1  | 1  |  |  |

| C diff      | 0   | 0  | 0              | 0  | 0  | 1  | 0  | 0  |  |  |

| Input SHORT |     |    |                |    |    | 1  | 0  | 1  |  |  |

|             |     |    |                |    |    | 0  | 1  | 1  |  |  |

| Prohibition |     |    |                |    |    | 1  | 1  | 0  |  |  |

|             |     |    |                |    |    | 1  | 1  | 1  |  |  |

Input SHORT : The input impedance of each input terminal is lowered from  $100k\Omega(TYP)$  to  $1~k\Omega(TYP)$ .(For quick charge of coupling capacitor)

: Initial condition

The list of terminals that is active when each mode of input selector is selected

| Mode     | 1ch+Input Terminal | 1ch-Input Terminal | 2ch+Input Terminal | 2ch-Input Terminal |

|----------|--------------------|--------------------|--------------------|--------------------|

| A single | 6pin(A1)           | -                  | 16pin(A2)          | -                  |

| B single | 5pin(B1)           | -                  | 17pin(B2)          | -                  |

| C single | 4pin(CP1)          | -                  | 18pin(CP2)         | -                  |

| D single | 2pin(D1)           | -                  | 20pin(D2)          | -                  |

| C diff   | 4pin(CP1)          | 3pin(CN1)          | 18pin(CP2)         | 19pin(CN2)         |

Select address 06 (hex)

| Coin        | MSB |    |    | Input | t Gain |    |    | LSB |

|-------------|-----|----|----|-------|--------|----|----|-----|

| Gain        | D7  | D6 | D5 | D4    | D3     | D2 | D1 | D0  |

| 0dB         |     |    |    | 0     | 0      | 0  | 0  | 0   |

| 1dB         |     |    |    | 0     | 0      | 0  | 0  | 1   |

| 2dB         |     |    |    | 0     | 0      | 0  | 1  | 0   |

| 3dB         |     |    |    | 0     | 0      | 0  | 1  | 1   |

| 4dB         |     |    |    | 0     | 0      | 1  | 0  | 0   |

| 5dB         |     |    | 0  | 0     | 1      | 0  | 1  |     |

| 6dB         |     |    |    | 0     | 0      | 1  | 1  | 0   |

| 7dB         |     |    |    | 0     | 0      | 1  | 1  | 1   |

| 8dB         |     |    |    | 0     | 1      | 0  | 0  | 0   |

| 9dB         |     |    |    | 0     | 1      | 0  | 0  | 1   |

| 10dB        |     |    |    | 0     | 1      | 0  | 1  | 0   |

| 11dB        | 0   | 0  | 0  | 0     | 1      | 0  | 1  | 1   |

| 12dB        | 0   | 0  |    | 0     | 1      | 1  | 0  | 0   |

| 13dB        |     |    |    | 0     | 1      | 1  | 0  | 1   |

| 14dB        |     |    |    | 0     | 1      | 1  | 1  | 0   |

| 15dB        |     |    |    | 0     | 1      | 1  | 1  | 1   |

| 16dB        |     |    |    | 1     | 0      | 0  | 0  | 0   |

| 17dB        |     |    |    | 1     | 0      | 0  | 0  | 1   |

| 18dB        |     |    |    | 1     | 0      | 0  | 1  | 0   |

| 19dB        |     |    |    | 1     | 0      | 0  | 1  | 1   |

| 20dB        |     |    |    | 1     | 0      | 1  | 0  | 0   |

|             |     |    |    | 1     | 0      | 1  | 0  | 1   |

| Prohibition |     |    |    | :     | :      | :  | :  | :   |

|             |     |    |    | 1     | 1      | 1  | 1  | 1   |

Select address 20 (hex)

| Delect address 20 (Hex) |     |    |    |          |            |    |    |     |

|-------------------------|-----|----|----|----------|------------|----|----|-----|

| ATT                     | MSB |    |    | Volume A | ttenuation |    |    | LSB |

| All                     | D7  | D6 | D5 | D4       | D3         | D2 | D1 | D0  |

|                         | 0   | 0  | 0  | 0        | 0          | 0  | 0  | 0   |

| Dualailaitian           | 0   | 0  | 0  | 0        | 0          | 0  | 0  | 1   |

| Prohibition             | :   | :  | :  | :        | :          | :  | :  | :   |

|                         | 0   | 1  | 1  | 1        | 1          | 1  | 1  | 1   |

| 0dB                     | 1   | 0  | 0  | 0        | 0          | 0  | 0  | 0   |

| -1dB                    | 1   | 0  | 0  | 0        | 0          | 0  | 0  | 1   |

| -2dB                    | 1   | 0  | 0  | 0        | 0          | 0  | 1  | 0   |

| :                       | :   | :  | :  | :        | :          | :  | :  | :   |

| -35dB                   | 1   | 0  | 1  | 0        | 0          | 0  | 1  | 1   |

| -36dB                   | 1   | 0  | 1  | 0        | 0          | 1  | 0  | 0   |

|                         | 1   | 0  | 1  | 0        | 0          | 1  | 0  | 1   |

| Prohibition             | :   | :  | :  | :        | :          | :  | :  | :   |

|                         | 1   | 1  | 1  | 1        | 1          | 1  | 1  | 0   |

| -∞dB                    | 1   | 1  | 1  | 1        | 1          | 1  | 1  | 1   |

: Initial condition

Select address 28, 29, 2A, 2B (hex)

| 201001 addi 000 20, 20, 2 | -, LD (110A) |    |    |           |           |    |    |     |

|---------------------------|--------------|----|----|-----------|-----------|----|----|-----|

| ATT                       | MSB          |    |    | Fader Att | tenuation |    |    | LSB |

| AII                       | D7           | D6 | D5 | D4        | D3        | D2 | D1 | D0  |

|                           | 0            | 0  | 0  | 0         | 0         | 0  | 0  | 0   |

| Duahihitian               | 0            | 0  | 0  | 0         | 0         | 0  | 0  | 1   |

| Prohibition               | :            | :  | :  | :         | :         | :  | :  | :   |

|                           | 0            | 1  | 1  | 1         | 1         | 1  | 1  | 1   |

| 0dB                       | 1            | 0  | 0  | 0         | 0         | 0  | 0  | 0   |

| -1dB                      | 1            | 0  | 0  | 0         | 0         | 0  | 0  | 1   |

| -2dB                      | 1            | 0  | 0  | 0         | 0         | 0  | 1  | 0   |

| :                         | :            | :  | :  | :         | :         | :  | :  | :   |

| -62dB                     | 1            | 0  | 1  | 1         | 1         | 1  | 1  | 0   |

| -63dB                     | 1            | 0  | 1  | 1         | 1         | 1  | 1  | 1   |

|                           | 1            | 1  | 0  | 0         | 0         | 0  | 0  | 0   |

| Prohibition               | :            | :  | :  | :         | :         | :  | :  | :   |

|                           | 1            | 1  | 1  | 1         | 1         | 1  | 1  | 0   |

| -∞dB                      | 1            | 1  | 1  | 1         | 1         | 1  | 1  | 1   |

Select address 51, 57 (hex)

| Select address 51, 57 ( | nex)   |    |    |          |          |    |    |     |

|-------------------------|--------|----|----|----------|----------|----|----|-----|

| Gain                    | MSB    |    |    | Bass/Tre | ble Gain |    |    | LSB |

| Gain                    | D7     | D6 | D5 | D4       | D3       | D2 | D1 | D0  |

| 0dB                     |        |    |    | 0        | 0        | 0  | 0  | 0   |

| 1dB                     |        |    |    | 0        | 0        | 0  | 0  | 1   |

| 2dB                     |        |    |    | 0        | 0        | 0  | 1  | 0   |

| 3dB                     |        |    |    | 0        | 0        | 0  | 1  | 1   |

| 4dB                     |        |    |    | 0        | 0        | 1  | 0  | 0   |

| 5dB                     |        |    |    | 0        | 0        | 1  | 0  | 1   |

| 6dB                     |        |    |    | 0        | 0        | 1  | 1  | 0   |

| 7dB                     |        |    |    | 0        | 0        | 1  | 1  | 1   |

| 8dB                     |        |    |    | 0        | 1        | 0  | 0  | 0   |

| 9dB                     |        |    |    | 0        | 1        | 0  | 0  | 1   |

| 10dB                    | Bass/  |    |    | 0        | 1        | 0  | 1  | 0   |

| 11dB                    | Treble | 0  | 0  | 0        | 1        | 0  | 1  | 1   |

| 12dB                    | Boost  | 0  | 0  | 0        | 1        | 1  | 0  | 0   |

| 13dB                    | /cut   |    |    | 0        | 1        | 1  | 0  | 1   |

| 14dB                    |        |    |    | 0        | 1        | 1  | 1  | 0   |

| 15dB                    |        |    |    | 0        | 1        | 1  | 1  | 1   |

| 16dB                    |        |    |    | 1        | 0        | 0  | 0  | 0   |

| 17dB                    |        |    |    | 1        | 0        | 0  | 0  | 1   |

| 18dB                    |        |    |    | 1        | 0        | 0  | 1  | 0   |

| 19dB                    |        |    |    | 1        | 0        | 0  | 1  | 1   |

| 20dB                    |        |    |    | 1        | 0        | 1  | 0  | 0   |

|                         |        |    |    | 1        | 0        | 1  | 0  | 1   |

| Prohibition             |        |    |    | :        | :        | :  | :  | :   |

|                         |        |    |    | 1        | 1        | 1  | 1  | 1   |

Select address 51, 57 (hex)

| $\mathbf{c}$ | ilect address 51, 57 (i | 167) |     |                    |             |           |             |     |     |  |  |  |

|--------------|-------------------------|------|-----|--------------------|-------------|-----------|-------------|-----|-----|--|--|--|

|              | Mode                    | MSB  |     |                    | Bass/Treble | Boost/Cut | t           |     | LSB |  |  |  |

|              | Mode                    | D7   | D6  | D5                 | D4          | D3        | D2          | D1  | D0  |  |  |  |

|              | Boost                   | 0    | 0   | 0                  |             | Ba        | cc/Troble G | ain |     |  |  |  |

|              | Cut                     | 1    | ] 0 | 0 Bass/Treble Gain |             |           |             |     |     |  |  |  |

: Initial condition

Select address 75 (hex)

| select address 75 (nex) |     |    |               |    |    |    |    | LSB |  |  |  |  |

|-------------------------|-----|----|---------------|----|----|----|----|-----|--|--|--|--|

| Coin                    | MSB |    | Loudness Gain |    |    |    |    |     |  |  |  |  |

| Gain                    | D7  | D6 | D5            | D4 | D3 | D2 | D1 | D0  |  |  |  |  |

| 0dB                     |     |    |               |    | 0  | 0  | 0  | 0   |  |  |  |  |

| 1dB                     |     |    |               |    | 0  | 0  | 0  | 1   |  |  |  |  |

| 2dB                     |     | 0  | 0             | 0  | 0  | 0  | 1  | 0   |  |  |  |  |

| 3dB                     |     |    |               |    | 0  | 0  | 1  | 1   |  |  |  |  |

| 4dB                     |     |    |               |    | 0  | 1  | 0  | 0   |  |  |  |  |

| 5dB                     |     |    |               |    | 0  | 1  | 0  | 1   |  |  |  |  |

| 6dB                     |     |    |               |    | 0  | 1  | 1  | 0   |  |  |  |  |

| 7dB                     | 0   |    |               |    | 0  | 1  | 1  | 1   |  |  |  |  |

| 8dB                     |     |    |               |    | 1  | 0  | 0  | 0   |  |  |  |  |

| 9dB                     |     |    |               |    | 1  | 0  | 0  | 1   |  |  |  |  |

| 10dB                    |     |    |               |    | 1  | 0  | 1  | 0   |  |  |  |  |

| 11dB                    |     |    |               |    | 1  | 0  | 1  | 1   |  |  |  |  |

| 12dB                    |     |    |               |    | 1  | 1  | 0  | 0   |  |  |  |  |

| 13dB                    |     |    |               |    | 1  | 1  | 0  | 1   |  |  |  |  |

| 14dB                    |     |    |               |    | 1  | 1  | 1  | 0   |  |  |  |  |

| 15dB                    |     |    |               |    | 1  | 1  | 1  | 1   |  |  |  |  |

: Initial condition

#### ● Volume / Fader volume attenuation of the details

Volume attenuation is 0dB to -36dB/Fader volume is 0dB to -63dB

| (dB) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (dB) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|----|

| 0    | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | -33  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 1  |

| -1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | -34  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 0  |

| -2   | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  | -35  | 1  | 0  | 1  | 0  | 0  | 0  | 1  | 1  |

| -3   | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | -36  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 0  |

| -4   | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 0  | -37  | 1  | 0  | 1  | 0  | 0  | 1  | 0  | 1  |

| -5   | 1  | 0  | 0  | 0  | 0  | 1  | 0  | 1  | -38  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 0  |

| -6   | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 0  | -39  | 1  | 0  | 1  | 0  | 0  | 1  | 1  | 1  |

| -7   | 1  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | -40  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 0  |

| -8   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  | -41  | 1  | 0  | 1  | 0  | 1  | 0  | 0  | 1  |

| -9   | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  | -42  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 0  |

| -10  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0  | -43  | 1  | 0  | 1  | 0  | 1  | 0  | 1  | 1  |

| -11  | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1  | -44  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 0  |

| -12  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 0  | -45  | 1  | 0  | 1  | 0  | 1  | 1  | 0  | 1  |

| -13  | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | -46  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 0  |

| -14  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | -47  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  |

| -15  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | -48  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0  |

| -16  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  | -49  | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 1  |

| -17  | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  | -50  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 0  |

| -18  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | -51  | 1  | 0  | 1  | 1  | 0  | 0  | 1  | 1  |

| -19  | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  | -52  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 0  |

| -20  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 0  | -53  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 1  |

| -21  | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | -54  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 0  |

| -22  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 0  | -55  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 1  |

| -23  | 1  | 0  | 0  | 1  | 0  | 1  | 1  | 1  | -56  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 0  |

| -24  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  | -57  | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 1  |

| -25  | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  | -58  | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 0  |

| -26  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  | -59  | 1  | 0  | 1  | 1  | 1  | 0  | 1  | 1  |

| -27  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  | -60  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 0  |

| -28  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | -61  | 1  | 0  | 1  | 1  | 1  | 1  | 0  | 1  |

| -29  | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | -62  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 0  |

| -30  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 0  | -63  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  |

| -31  | 1  | 0  | 0  | 1  | 1  | 1  | 1  | 1  | -∞   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

| -32  | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | -    | -  | -  | -  | -  | -  | -  | -  | -  |

: Initial condition

# (6) About power on reset

At ON of supply voltage circuit made initialization inside IC is built-in. Please send data to all address as initial data at supply voltage on. And please supply mute at set side until this initial data is sent.

| ltom |                                          | Cumbal | Limit |      |      | Lloit | Condition                   |

|------|------------------------------------------|--------|-------|------|------|-------|-----------------------------|

|      | Item                                     | Symbol | Min.  | Тур. | Max. | Unit  | Condition                   |

| R    | ise time of VCC                          | Trise  | 20    | _    | _    | usec  | VCC rise time from 0V to 5V |

| re   | CC voltage of<br>elease power on<br>eset | Vpor   | _     | 5.0  | _    | V     |                             |

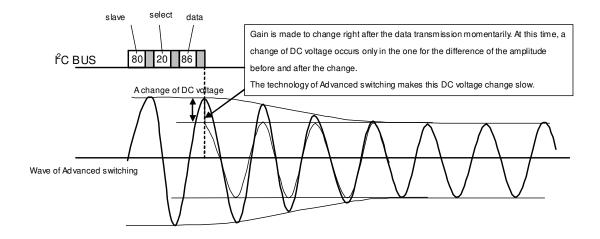

#### About Advanced switching circuit

#### [1] About Advanced switch

#### 1-1. Effect of Advanced switch

It is the ROHM original technology for prevention of switching noise. When gain switching such as volume and tone control is done momentarily, a music signal isn't continuous, and unpleasant shock noise is made. Advanced switch can reduce shock noise with the technology which signal wave shape is complemented so that a music signal may not continue drastically.

Advanced switch starts switching after the control data from a microcomputer are received. It takes one fixed time, and wave shape transits as the above figure. The data transmitted by a microcomputer are processed inside, and the most suitable movement is done inside the IC so that switching shock noise may not be made.

But, it presumes by the transmitting timing when it doesn't become intended switching wave shape because it is the function which needs time. The example in which there are relation with the switching time of the data transmitting timing and the reality are shown in the following. It asks for design when it is confirmed well.

#### 1-2. About a kind of transmission method

- A data setup except for the item for advanced switch (p11/27 select address and the data format, the thing which isn't indicated by gray)

There is no regulation in transmission specially.

- The data setup of the item for advanced switch

(p11/27 select address and the data format,, the thing which is indicated by gray)

Though there is no regulation in data transmission, the switching order when data are transmitted to several blocks follows the next 2.

#### [2] About transmission DATA of advanced switching item

#### 2-1. About switching time of advanced switch

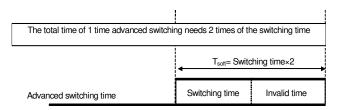

Advanced switching time are equivalent to the switching time and invalid time(effect-less time) inside the IC, and switching time and invalid time is equal to 11.2msec x ( $1\pm0.4$ (dispersion margin))

Therefore, actual Advanced switching time (T<sub>soft</sub>) is defined as follows.

Advanced switching time  $T_{soft}$  is,  $T_{soft}$  = switching time and invalid time(= switching time x 2).

#### 2-2. About the data transmitting timing in same block state and the switching movement

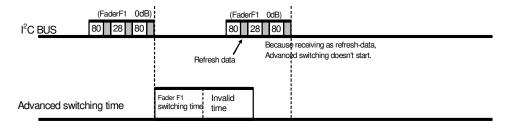

#### ■ Transmitting example 1

A time chart to the start of switching from the data transmission is as following.

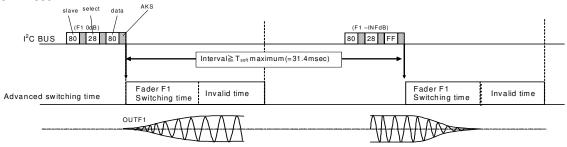

At first, the example are shown as below when the interval time is sufficient in which transmission of the same blocks.

(Sufficient interval means time which is more than  $T_{\text{soft}}$  maximum value, 11.2msec x 1.4(dispersion margin) x 2 = 31.4msec

#### ■ Transmitting example 2

Next, when a transmitting interval isn't sufficient (when it is shorter than the above interval), the example is shown. In case data are transmitted during the first switching movement, the next switching movement is started in succession after the first switching movement is finished.

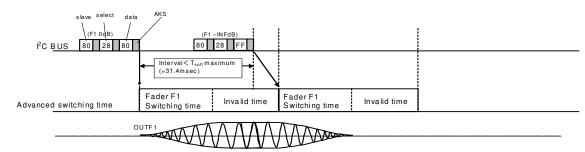

#### ■ Transmitting example 3

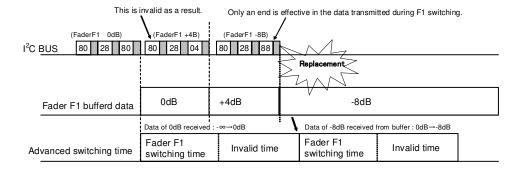

Next, the example of the switching movement when a transmitting interval was shortened more is shown. Inside the IC, It has the buffer which memorizes data, and a buffer always does transmitting data. But, data of +4dB which transmitted to the second become invalid with this example because the buffer holds only the latest data.

#### ■ Transmitting example 4

At first, transmitting data are stored in the maintenance data, and next it is written in the setup data in which gain is set up to. But, in case there is no difference between the transmitting data and the setup data as a refresh data, Advanced switch movement isn't started.

#### 2-3. About the data transmitting timing and the switching movement in several block state

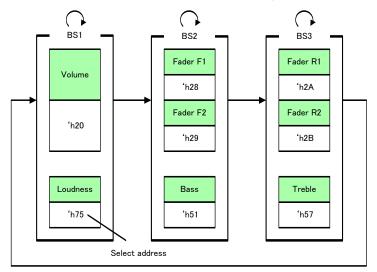

When data are transmitted to several blocks, treatment in the BS (block state) unit is carried out inside the IC. The order of advanced switch movement start is decided in advance dependent on BS.

#### The order of advanced switch start

XIt is possible that blocks in the same BS start switching at the same timing.

Figure 16. The example of the timing of command of in I<sup>2</sup>Cdata transmitting

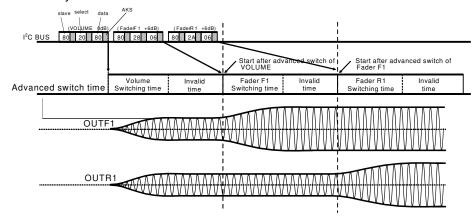

#### ■ Transmitting example 5

About the transmission to several blocks also, as explained in the previous section, though there is no restriction of the I2C BUS data transmitting timing, the start timing of switching follows the figure of previous page, figure 16.

Therefore, it isn't based on the data transmitting order, and an actual switching order becomes as the figure 16 (Transmitting example 6).

Each block data is being transmitted separately in the transmitting example 5, but it becomes the same result even if data are transmitted by automatic increment.

# ■ Transmitting example 6

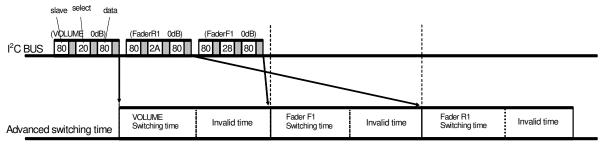

When an actual switching order is different from the transmitting order or data except for the same BS are transmitted at the timing when advanced switch movement isn't finished, switching of the next BS is done after the present switching completion .

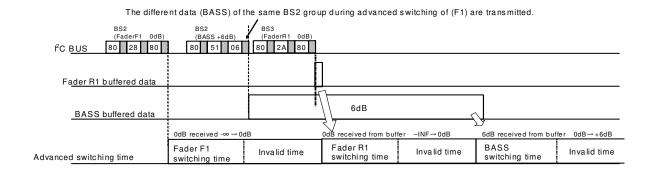

#### ■ Transmitting example 7

In this example, data of BS2 and BS3 are transmitted during Advances switching of BS2(same BS2 group) .

#### 2-4. About gain switching of TONE(Bass/ Treble)

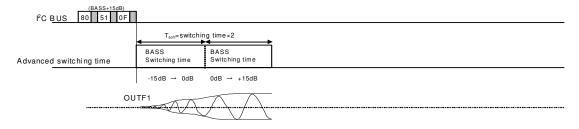

When gain is changed from boost to cut (or, from cut to boost), advanced switching is two-step transition movement that it go through 0dB to prevent the occurrence of the switching noise. And when boost/cut doesn't change between before switching and after switching, advanced switching is the same as 2-2, 2-3. About advanced switching time, it is same time length as other switching time length.

#### ■ Transmitting example 8

In case changing Bass gain +15dB from -15dB

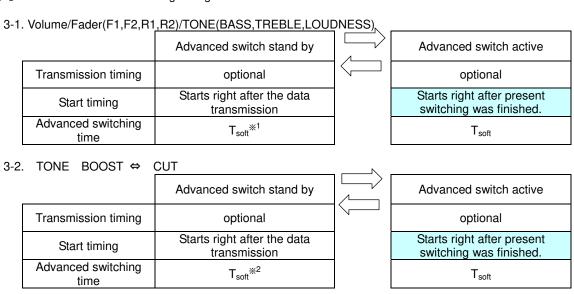

# [3] Advanced switch transmitting timing list

- X1 Advanced switching time  $T_{soft}$  equalls to 2 times of swithcing time.

- ※2 About T<sub>soft</sub> of TONE BOOST⇔CUT, the time length until gain switching finishes is equal to 2times of switching time, because it go through 0dB when switching from initial gain to requested gain. In this case, Advanced switching time is same as ※1 above.

# Application Circuit Diagram

Figure 17. Application Circuit Diagram

#### Notes on wiring

- ①Please connect the decoupling capacitor of a power supply in the shortest distance as much as possible to GND.

- 2Lines of GND shall be one-point connected.

- 3Wiring pattern of Digital shall be away from that of analog unit and cross-talk shall not be acceptable.

- (4) Lines of SCL and SDA of I<sup>2</sup>C BUS shall not be parallel if possible.

- The lines shall be shielded, if they are adjacent to each other.

- ⑤Lines of analog input shall not be parallel if possible. The lines shall be shielded, if they are adjacent to each other.

CAPACITANCE: F

#### ●Thermal Derating Curve

About the thermal design by the IC

Characteristics of an IC have a great deal to do with the temperature at which it is used, and exceeding absolute maximum ratings may degrade and destroy elements. Careful consideration must be given to the heat of the IC from the two standpoints of immediate damage and long-term reliability of operation.

Figure 18. Temperature Derating Curve

Note) Values are actual measurements and are not guaranteed.

Power dissipation values vary according to the board on which the IC is mounted.

| Terminal Equiva                  | lent Circuit and    | Description        |                                                                         |

|----------------------------------|---------------------|--------------------|-------------------------------------------------------------------------|

| Terminal Name                    | Terminal<br>Voltage | Equivalent Circuit | Terminal Description                                                    |

| A1<br>A2<br>B1<br>B2<br>D1<br>D2 | 4.2                 | VCC DE 100kΩ       | A terminal for signal input. The input impedance is $100k\Omega(typ)$ . |

| CP1<br>CP2                       | 4.2                 | VCC 25k S          | A terminal for positive input of ground isolation amplifier.            |

| CN1<br>CN2                       | 4.2                 | GND 25k 25k        | A terminal for negative input of ground isolation amplifier.            |

| SCL                              | -                   | VCC<br>B<br>1.65V  | A terminal for clock input of I <sup>2</sup> C BUS communication.       |

| SDA                              | -                   | VCC<br>O<br>I.65V  | A terminal for data input of I <sup>2</sup> C BUS communication.        |

| Terminal<br>Name                 | Terminal<br>Voltage | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Terminal Description                                                                                                                                                   |  |  |  |  |

|----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| OUTF1<br>OUTR1<br>OUTR2<br>OUTF2 | 4.2                 | VCC<br>A<br>GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A terminal for fader output.                                                                                                                                           |  |  |  |  |

| N.C.                             | -                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Non connect terminal                                                                                                                                                   |  |  |  |  |

| VCC                              | 8.5                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power supply terminal.                                                                                                                                                 |  |  |  |  |

| GND                              | 0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground terminal.                                                                                                                                                       |  |  |  |  |

| VREF                             | 4.2                 | VCC OF THE STATE O | BIAS terminal.  Voltage for reference bias of analog signal system. The simple pre-charge circuit and simple discharge circuit for an external capacitor are built in. |  |  |  |  |

<sup>\*\*</sup>The figure in the pin explanation and input/output equivalent circuit is reference value, it doesn't guarantee the value.