Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# **Sound Processor with Built-in 2-band Equalizer**

#### **General Description**

BD37511FS is a sound processor with built-in 2-band equalizer for car audio. The functions are 3ch stereo input selector, input-gain control, main volume and 4ch fader volume. Moreover, its "Advanced switch circuit", which is an original ROHM technology, can reduce various switching noise (ex. No-signal, low frequency like 20Hz & large signal inputs). "Advanced switch" makes control of microcomputer easier, supporting the construction of a high quality car audio system.

#### **Features**

- Reduce switching noise of mute, main volume, fader volume, bass, trebles by using advanced switch circuit

- Built-in 3 single-ended input selectors

- Decrease the number of external components due to built-in 2-band equalizer filter.

- It is possible to adjust the gain of the bass and treble up to ±20dB with 1 dB step gain adjustment.

- Energy-saving design resulting in low current consumption, by utilizing the Bi-CMOS process. It has the advantage in quality over scaling down the power heat control of the internal regulators.

- Input terminals and output terminals are organized and separately laid out to keep the signal flow in one direction which results in simpler and smaller PCB layout.

- It is possible to control the I<sup>2</sup>C BUS by 3.3V / 5V.

# **Applications**

It is optimal for use in car audio systems. It can also be used for audio equipment of mini Compo, micro Compo, TV. etc.

# **Key Specifications**

Power Supply Voltage Range: 7.0V to 9.5V Circuit Current (No Signal): 15mA(Typ) Total Harmonic Distortion: 0.005%(Typ) Maximum Input Voltage: 2.3Vrms (Typ) -100dB(Typ) Cross-talk Between Selectors: Volume Control Range: +0dB to -40dB Output Noise Voltage: 6μVrms(Typ) 2μVrms(Typ) Residual Output Noise Voltage: Operating Temperature Range: -40°C to +85°C

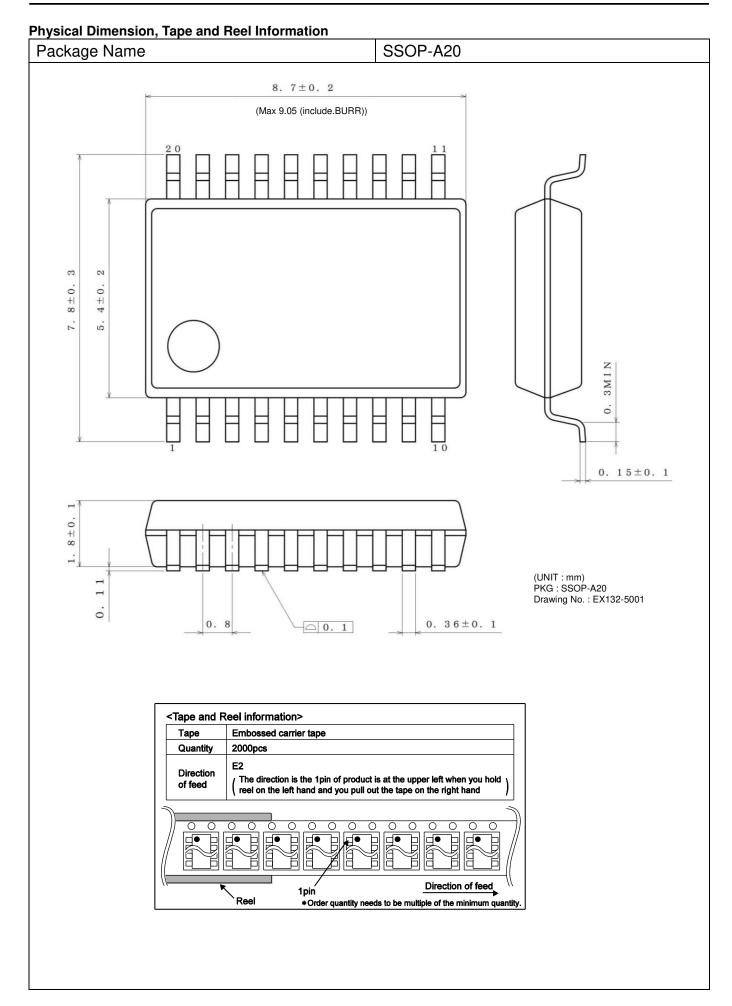

#### **Package**

$W(Typ) \times D(Typ) \times H(Max)$

**SSOP-A20** 8.70mm x 7.80mm x 2.01mm

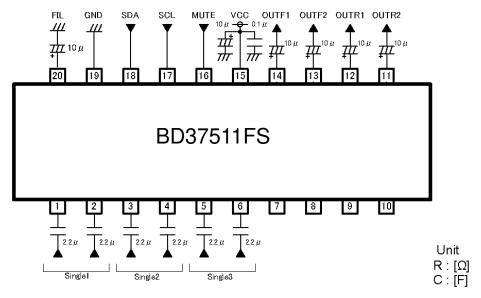

# **Typical Application Circuit**

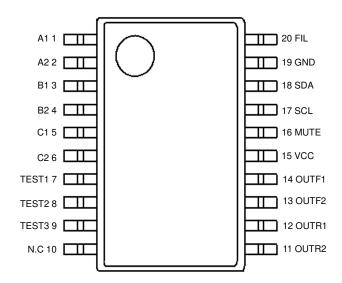

# **Pin Configuration**

Pin Descriptions

| in Descript | ions        |                         |         |             |                                               |

|-------------|-------------|-------------------------|---------|-------------|-----------------------------------------------|

| Pin No.     | Pin<br>Name | Description             | Pin No. | Pin<br>Name | Description                                   |

| 1           | A1          | A input terminal of 1ch | 11      | OUTR2       | Rear output terminal of 2ch                   |

| 2           | A2          | A input terminal of 2ch | 12      | OUTR1       | Rear output terminal of 1ch                   |

| 3           | B1          | B input terminal of 1ch | 13      | OUTF2       | Front output terminal of 2ch                  |

| 4           | B2          | B input terminal of 2ch | 14      | OUTF1       | Front output terminal of 1ch                  |

| 5           | C1          | C input terminal of 1ch | 15      | VCC         | Power supply terminal                         |

| 6           | C2          | C input terminal of 2ch | 16      | MUTE        | External compulsory mute terminal             |

| 7           | TEST1       | Test Pin                | 17      | SCL         | I <sup>2</sup> C Communication clock terminal |

| 8           | TEST2       | Test Pin                | 18      | SDA         | I <sup>2</sup> C Communication data terminal  |

| 9           | TEST3       | Test Pin                | 19      | GND         | GND terminal                                  |

| 10          | N.C.        | No Connection           | 20      | FIL         | VCC/2 terminal                                |

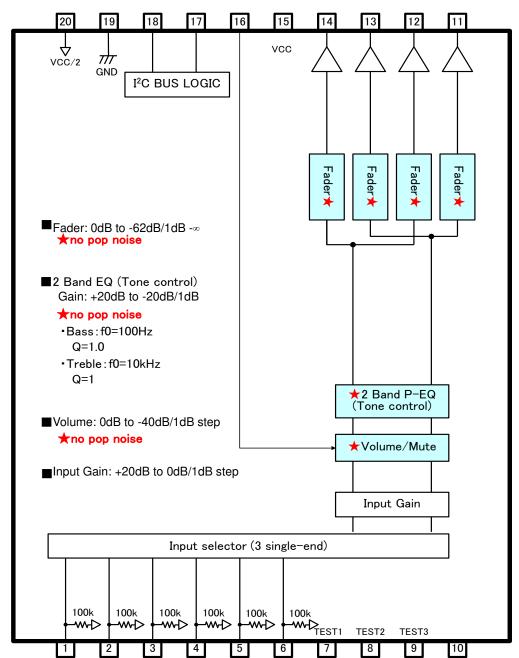

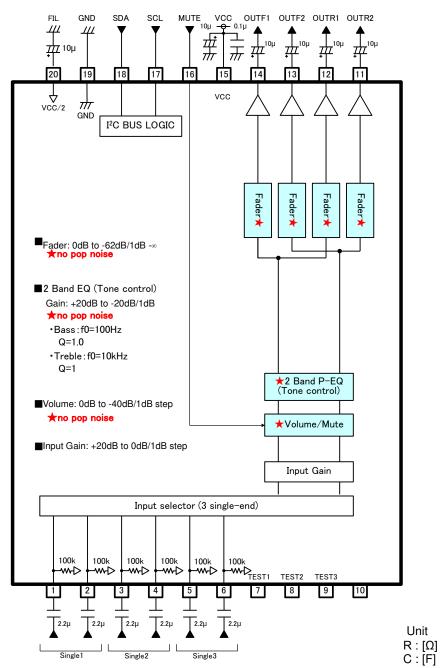

# **Block Diagram**

**Absolute Maximum Ratings** (Ta=25°C)

| Parameter            | Symbol          | Rating                          | Unit |

|----------------------|-----------------|---------------------------------|------|

| Power Supply Voltage | Vcc             | 10.0                            | V    |

| Input Voltage        | V <sub>IN</sub> | V <sub>CC</sub> +0.3 to GND-0.3 | V    |

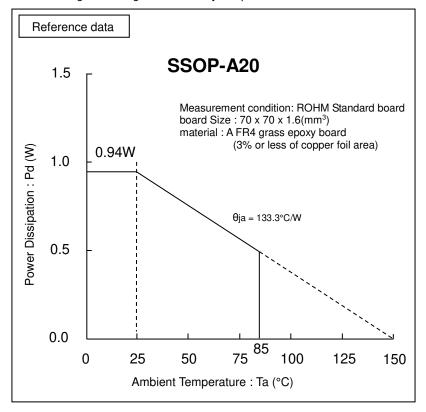

| Power Dissipation    | Pd              | 0.94 <sup>(Note 1)</sup>        | W    |

| Storage Temperature  | Tstg            | -55 to +150                     | °C   |

(Note 1) This value derates by 7.5mW/°C for Ta=25°C or more when ROHM standard board is used. Thermal resistance θja = 133.3(°C/W) ROHM Standard board

Size: 70 x 70 x 1.6(mm<sup>3</sup>)

Material : A FR4 grass epoxy board(3% or less of copper foil area)

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

**Recommended Operating Conditions**

| Parameter            | Symbol | Min | Тур | Max | Unit |

|----------------------|--------|-----|-----|-----|------|

| Power Supply Voltage | Vcc    | 7.0 | -   | 9.5 | V    |

| Temperature          | Topr   | -40 | -   | +85 | °C   |

#### **Electrical Characteristics**

(Unless specified otherwise, Ta=25°C, V<sub>CC</sub>=8.5V, f=1kHz, V<sub>IN</sub> =1Vrms, Rg=600Ω, R<sub>L</sub>=10kΩ, A input, Input gain 0dB, Mute OFF, Volume 0dB, Tone control 0dB, Loudness 0dB, Fader 0dB)

| X          | ,                               |                     | ·    | Limit |      |       |                                                                                                            |

|------------|---------------------------------|---------------------|------|-------|------|-------|------------------------------------------------------------------------------------------------------------|

| BLOCK      | Parameter                       | Symbol              | Min  | Тур   | Max  | Unit  | Conditions                                                                                                 |

|            | Circuit Current                 | IQ                  | 1    | 15    | 30   | mA    | No signal                                                                                                  |

|            | Voltage Gain                    | Gv                  | -1.5 | 0     | +1.5 | dB    | G <sub>V</sub> =20log(V <sub>OUT</sub> /V <sub>IN</sub> )                                                  |

|            | Channel Balance                 | СВ                  | -1.5 | 0     | +1.5 | dB    | CB = G <sub>V1</sub> -G <sub>V2</sub>                                                                      |

|            | Total Harmonic Distortion       | THD+N1              | ı    | 0.005 | 0.05 | %     | V <sub>OUT</sub> =1Vrms<br>BW=400Hz-30KHz                                                                  |

| 3AL        | Output Noise Voltage *          | V <sub>NO1</sub>    | -    | 6     | 25   | μVrms | $Rg = 0\Omega$<br>BW = IHF-A                                                                               |

| GENERAL    | Residual Output Noise Voltage * | V <sub>NOR</sub>    | -    | 2     | 10   | μVrms | Fader = -∞dB<br>Rg = 0Ω<br>BW = IHF-A                                                                      |

|            | Cross-talk Between Channels *   | СТС                 | -    | -100  | -90  | dB    | $Rg = 0\Omega$ $CTC=20log(V_{OUT}/V_{IN})$ $BW = IHF-A$                                                    |

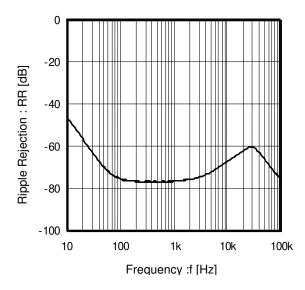

|            | Ripple Rejection                | RR                  | -    | -70   | -40  | dB    | f=1KHz<br>V <sub>RR</sub> =100mVrms<br>RR=20log(V <sub>CC</sub> IN/V <sub>OUT</sub> )                      |

| Ж          | Input Impedance(A, B, C)        | R <sub>IN_s</sub>   | 70   | 100   | 130  | kΩ    |                                                                                                            |

| SELECTOR   | Maximum Input Voltage           | V <sub>IM</sub>     | 2.1  | 2.3   | ı    | Vrms  | V <sub>IM</sub> at THD+N(V <sub>OUT</sub> )=1%<br>BW=400Hz-30KHz                                           |

| INPUT SEI  | Cross-talk Between Selectors *  | стѕ                 | -    | -100  | -90  | dB    | $Rg = 0\Omega$ $CTS=20log(V_{OUT}/V_{IN})$ $BW = IHF-A$                                                    |

| Z          | Minimum Input Gain              | G <sub>IN_MIN</sub> | -2   | 0     | +2   | dB    | Input gain 0dB<br>V <sub>IN</sub> =100mVrms<br>G <sub>IN</sub> =20log(V <sub>OUT</sub> /V <sub>IN</sub> )  |

| INPUT GAIN | Maximum Input Gain              | GIN_MAX             | 18   | 20    | 22   | dB    | Input gain 20dB<br>V <sub>IN</sub> =100mVrms<br>G <sub>IN</sub> =20log(V <sub>OUT</sub> /V <sub>IN</sub> ) |

|            | Gain Set Error                  | G <sub>IN_ERR</sub> | -2   | 0     | +2   | dB    | GAIN=+1dB to +20dB                                                                                         |

#### **Electrical Characteristics - continued**

|        | ar Characteristics - continued |                     |     | Limit |     |      |                                                                                                               |

|--------|--------------------------------|---------------------|-----|-------|-----|------|---------------------------------------------------------------------------------------------------------------|

| BLOCK  | Parameter                      | Symbol              | Min | Тур   | Max | Unit | Conditions                                                                                                    |

| MUTE   | Mute Attenuation *             | G <sub>MUTE</sub>   | -   | -105  | -85 | dB   | Mute ON<br>G <sub>MUTE</sub> =20log(V <sub>OUT</sub> /V <sub>IN</sub> )<br>BW = IHF-A                         |

| VOLUME | Maximum Attenuation            | Gv_мім              | -43 | -40   | -37 | dB   | Volume = -40dB<br>Gv=20log(V <sub>OUT</sub> /V <sub>IN</sub> )                                                |

|        | Attenuation Set Error 1        | G <sub>V_ERR1</sub> | -2  | 0     | +2  | dB   | GAIN & ATT=0dB to -15dB                                                                                       |

| ×      | Attenuation Set Error 2        | G <sub>V_ERR2</sub> | -3  | 0     | +3  | dB   | ATT=-16dB to -40dB                                                                                            |

|        | Maximum Boost Gain             | Gв_вѕт              | 18  | 20    | 22  | dB   | Gain=+20dB f=100Hz<br>V <sub>IN</sub> =100mVrms<br>G <sub>B</sub> =20log (V <sub>OUT</sub> /V <sub>IN</sub> ) |

| BASS   | Maximum Cut Gain               | G <sub>В_СUТ</sub>  | -22 | -20   | -18 | dB   | Gain=-20dB f=100Hz<br>V <sub>IN</sub> =2Vrms<br>G <sub>B</sub> =20log (V <sub>OUT</sub> /V <sub>IN</sub> )    |

|        | Gain Set Error                 | G <sub>B_ERR</sub>  | -2  | 0     | +2  | dB   | Gain=-20dB to +20dB f=100Hz                                                                                   |

| ш      | Maximum Boost Gain             | Gт_вѕт              | 18  | 20    | 22  | dB   | Gain=+20dB f=10kHz<br>V <sub>IN</sub> =100mVrms<br>G <sub>T</sub> =20log (V <sub>OUT</sub> /V <sub>IN</sub> ) |

| TREBLE | Maximum Cut Gain               | Gт_сит              | -22 | -20   | -18 | dB   | Gain=-20dB f=10kHz<br>V <sub>IN</sub> =2Vrms<br>G <sub>T</sub> =20log (V <sub>OUT</sub> /V <sub>IN</sub> )    |

|        | Gain Set Error                 | GT_ERR              | -2  | 0     | +2  | dB   | Gain=-20dB to +20dB<br>f=10kHz                                                                                |

|        | Maximum Attenuation *          | G <sub>F_MIN</sub>  | -   | -100  | -90 | dB   | Fader = -∞dB<br>G <sub>F</sub> =20log(V <sub>OUT</sub> /V <sub>IN</sub> )<br>BW = IHF-A                       |

|        | Attenuation Set Error 1        | GF_ERR1             | -2  | 0     | +2  | dB   | ATT=0dB to -15dB                                                                                              |

| FADER  | Attenuation Set Error 2        | GF_ERR2             | -3  | 0     | +3  | dB   | ATT=-16dB to -47dB                                                                                            |

| FAI    | Attenuation Set Error 3        | GF_ERR3             | -4  | 0     | +4  | dB   | ATT=-48dB to -62dB                                                                                            |

|        | Output Impedance               | Rout                | -   | -     | 50  | Ω    | V <sub>IN</sub> =100mVrms                                                                                     |

|        | Maximum Output Voltage         | V <sub>ОМ</sub>     | 2   | 2.2   | -   | Vrms | THD+N=1 %<br>BW=400Hz-30KHz                                                                                   |

$<sup>\</sup>label{lem:possible} \mbox{VP-9690A (Average value detection, effective value display) filter by Matsushita Communication is used for $^*$ measurement. Phase between input / output is same.}$

# **Typical Performance Curves**

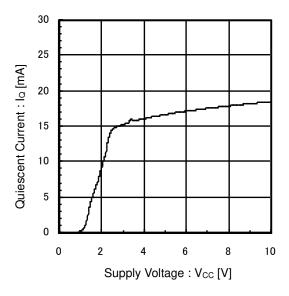

Figure 1. Quiescent Current vs Supply Voltage

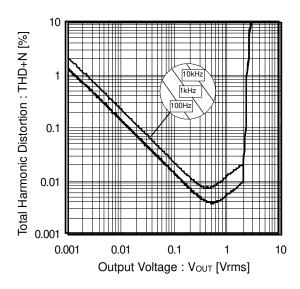

Figure 2. Total Harmonic Distortion vs Output Voltage

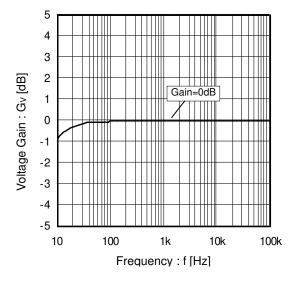

Figure 3. Voltage Gain vs Frequency

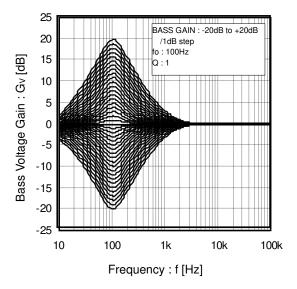

Figure 4. Bass Voltage Gain vs Frequency

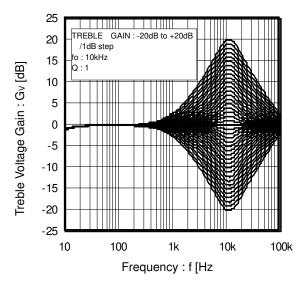

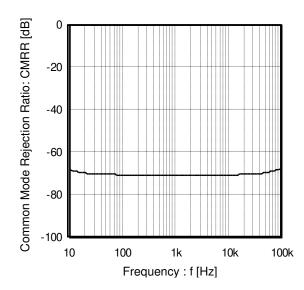

# **Typical Performance Curves - continued**

Figure 5. Treble Voltage Gain vs Frequency

Figure 6. Common Mode Rejection Ratio vs Frequency

Figure 7. Cross-Talk Between Channels vs Frequency

Figure 8. Ripple Rejection Ratio vs Frequency

# **Typical Performance Curves - continued**

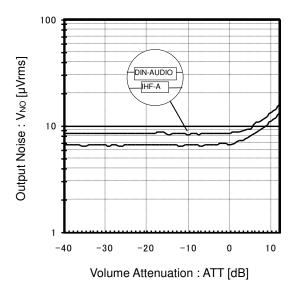

Figure 9. Output Noise vs Volume Attenuation

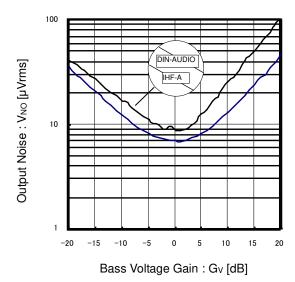

Figure 10. Output Noise vs Bass Voltage Gain

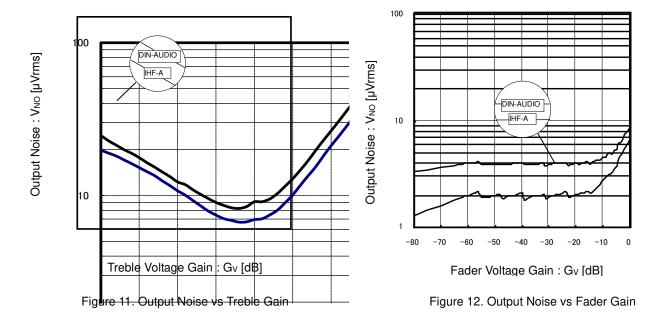

# **Typical Performance Curves - continued**

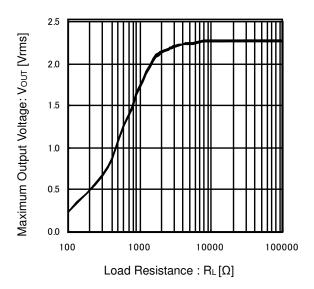

Figure 13. Maximum Output Voltage vs Load Resistance

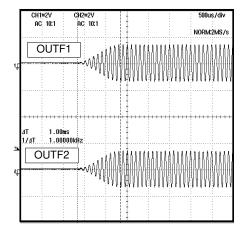

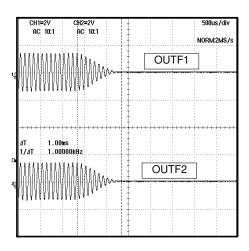

Figure 14. Advanced Switch 1

Figure 15. Advanced Switch 2

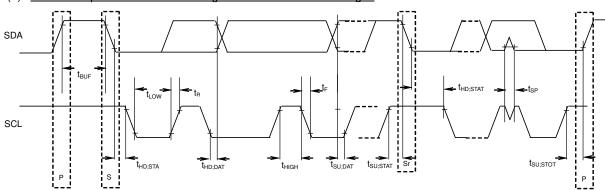

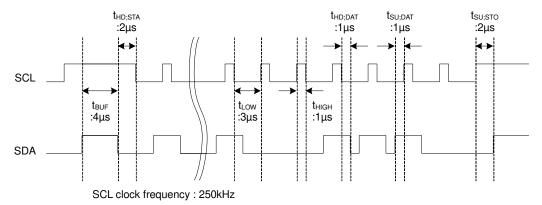

# **Timing Chart**

# **Control Signal Specification**

(1) Electrical Specifications and Timing for Bus Lines and I/O Stages

Figure 16. I<sup>2</sup>C-bus Signal Timing Diagram

Table 1 Characteristics of the SDA and SCL bus lines for I<sup>2</sup>C-bus devices

|   | Parameter                                                                | Cumbal  | Fast-mod   | e I <sup>2</sup> C-bus | Unit  |

|---|--------------------------------------------------------------------------|---------|------------|------------------------|-------|

|   | Farameter                                                                | Symbol  | Min        | Max                    | Utill |

| 1 | SCL clock frequency                                                      | fscL    | 0          | 400                    | kHz   |

| 2 | Bus free time between a STOP and START condition                         | tbur    | 1.3        | -                      | μS    |

| 3 | Hold time (repeated) START condition. After this period, the first clock | tupora  | 0.6        |                        | μS    |

| 3 | pulse is generated                                                       | thd;sta | 0.0        |                        | μΟ    |

| 4 | LOW period of the SCL clock                                              | tLOW    | 1.3        | -                      | μS    |

| 5 | HIGH period of the SCL clock                                             | thigh   | 0.6        | -                      | μS    |

| 6 | Set-up time for a repeated START condition                               | tsu;sta | 0.6        | -                      | μS    |

| 7 | Data hold time:                                                          | thd;dat | 0.7 (Note) | -                      | μS    |

| 8 | Data set-up time                                                         | tsu;dat | 700        | -                      | ns    |

| 9 | Set-up time for STOP condition                                           | tsu;sto | 0.6        | -                      | μS    |

All values referred to VIH Min and VIL Max Levels (see Table 2).

(Note) To avoid sending right after the fall-edge of SCL (VIHmin of the SCL signal), the transmitting device should set a hold time of 300ns or more for the SDA signal.

For  $7(t_{HD;DAT})$ ,  $8(t_{SU;DAT})$ , make the setup in which the margin is fully in.

Table 2 Characteristics of the SDA and SCL I/O stages for I<sup>2</sup>C-bus devices

|    | Parameter                                                                  | Cumbal           | Fast-mode | e devices | Unit  |

|----|----------------------------------------------------------------------------|------------------|-----------|-----------|-------|

|    | raiaiiielei                                                                | Symbol           | Min       | Max       | Ufill |

| 10 | LOW level input voltage:                                                   | $V_{IL}$         | -0.3      | +1        | V     |

| 11 | HIGH level input voltage:                                                  | V <sub>IH</sub>  | 2.3       | 5         | V     |

| 12 | Pulse width of spikes which must be suppressed by the input filter.        | t <sub>SP</sub>  | 0         | 50        | ns    |

| 13 | LOW level output voltage: at 3mA sink current                              | V <sub>OL1</sub> | 0         | 0.4       | V     |

| 14 | Input current of each I/O pin with an input voltage between 0.4V and 4.5V. | I <sub>I</sub>   | -10       | +10       | μA    |

Figure 17. I<sup>2</sup>C Data Transmission Command Timing Diagram

#### (2) <u>I<sup>2</sup>C BUS FORMAT</u>

|      | MSB LSB        | MSB               | LSB               |        | MSB               | LSB           |          |            |

|------|----------------|-------------------|-------------------|--------|-------------------|---------------|----------|------------|

| S    | Slave Address  | A Selec           | t Address         | Α      | Data              |               | A P      |            |

| 1bit | 8bit           | 1bit              | 8bit              | 1bit   | 8bit              | 11            | bit 1bit |            |

|      | S              | = Start condition |                   |        |                   |               |          |            |

|      | Slave Address  | = Recognition     | of slave addre    | ess. 7 | he first 7 bits c | orrespond to  | the slav | e address. |

|      |                | The least sig     | nificant bit is ' | "L" wl | nich correspond   | ds to write m | ode.     |            |

|      | Α              |                   |                   |        | ion of acknowle   |               |          |            |

|      | Select Address |                   |                   |        | o volume, bass    | or treble.    |          |            |

|      | Data           | = Data on eve     |                   |        |                   |               |          |            |

|      | Р              | = Stop condition  | on (Recognitio    | n of s | stop bit)         |               |          |            |

#### (3) I<sup>2</sup>C BUS Interface Protocol

| (a) l | Basic Format  |   |                |    |       |   |   |

|-------|---------------|---|----------------|----|-------|---|---|

| S     | Slave Address | Α | Select Address | Α  | Data  | Α | F |

|       | MSB IS        | 2 | MSR ISB        | MS | R ISI | 2 |   |

(b) Automatic Increment (Select Address increases (+1) according to the number of data.)

S Slave Address A Select Address A Data1 A Data2 A ···· DataN A F MSB LSB MSB LSB MSB LSB MSB LSB MSB LSB

(Example) ①Data1 shall be set as data of address specified by Select Address.

- ②Data2 shall be set as data of address specified by Select Address +1.

- ③DataN shall be set as data of address specified by Select Address +N-1.

(c) Configuration Unavailable for Transmission (In this case, only Select Address1 is set.)

| S | Slave A | ddress    | Α    | Select     | Address1     | Α    | Data      | Α     | Select Ac   | ddress 2     | Α   | Dat | a   | Α | Р |

|---|---------|-----------|------|------------|--------------|------|-----------|-------|-------------|--------------|-----|-----|-----|---|---|

|   | MSB     | LSB       | Ν    | 1SB        | LSB          | Ν    | ISB LSB   |       | MSB         | LSB          | Ν   | 1SB | LSE | } |   |

|   | (Note   | e) If any | data | a is trans | mitted as Se | elec | t Address | s 2 r | ext to data | , it is reco | gni | zed |     |   |   |

|   |         | as        | data | , not as   | Select Addre | ess  | 2.        |       |             |              |     |     |     |   |   |

#### (4) Slave Address

|   | MSB |    |    |    |    |    |    | LSB |     |

|---|-----|----|----|----|----|----|----|-----|-----|

| Γ | A6  | A5 | A4 | A3 | A2 | A1 | A0 | R/W |     |

|   | 1   | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 80H |

#### (5) Select Address & Data

|                 | Select           | MSB                           |    |                                                                | Da | ıta        |            |    | LSB |  |

|-----------------|------------------|-------------------------------|----|----------------------------------------------------------------|----|------------|------------|----|-----|--|

| Items           | Address<br>(hex) | D7                            | D6 | D5                                                             | D4 | D3         | D2         | D1 | D0  |  |

| Initial setup 1 | 01               | Advance<br>d switch<br>ON/OFF | 0  | Advanced switch time of 0 0 Advanced some of Nolume/Tone/Fader |    |            |            |    |     |  |

| Input Selector  | 04               | 0                             | 0  | 0 0 0 Input selector                                           |    |            |            |    |     |  |

| Input gain      | 06               | Mute<br>ON/OFF                | 0  | 0 Input Gain                                                   |    |            |            |    |     |  |

| Volume gain     | 20               | 1                             | 0  |                                                                |    | Volume Att | enuation   |    |     |  |

| Fader 1ch Front | 28               | 1                             | 0  |                                                                |    | Fader Atte | nuation    |    |     |  |

| Fader 2ch Front | 29               | 1                             | 0  |                                                                |    | Fader Atte | nuation    |    |     |  |

| Fader 1ch Rear  | 2A               | 1                             | 0  |                                                                |    | Fader Atte | nuation    |    |     |  |

| Fader 2ch Rear  | 2B               | 1                             | 0  |                                                                |    | Fader Atte | nuation    |    |     |  |

| Bass gain       | 51               | Bass<br>Boost/<br>Cut         | 0  | 0                                                              |    | ı          | Bass Gain  |    |     |  |

| Treble gain     | 57               | Treble<br>Boost/<br>Cut       | 0  | 0                                                              |    | Т          | reble Gain |    |     |  |

| System Reset    | FE               | 1                             | 0  | 0                                                              | 0  | 0          | 0          | 0  | 1   |  |

Advanced switch

#### Note

- 1. The Advanced Switch works in the latch part while changing from one function to another.

- When changing a tone into the cut from the boost, or the cut and the boost, always go via the condition of the tone 0dB.

- 3. Upon continuous data transfer, the Select Address rolls over because of the automatic increment function, as shown below.

$$\longrightarrow 01 \rightarrow 04 \rightarrow 06 \rightarrow 20 \rightarrow 28 \rightarrow 29 \rightarrow 2A \rightarrow 2B \rightarrow 51 \rightarrow 57$$

- 4. For the function of Input Selector etc, Advanced Switch is not used. Therefore, please apply mute on the set side when changing these settings.

- 5. When using mute function of this IC at the time of changing input selector, please switch mute ON/OFF while waiting for advanced-mute time.

Select address 01 (hex)

| Ociobi addica | 3 0 1 (11CA) |                     |    |            |             |              |              |    |     |

|---------------|--------------|---------------------|----|------------|-------------|--------------|--------------|----|-----|

| Mod           | 40           | MSB                 |    | Ad         | vanced swit | ch time of N | <b>l</b> ute |    | LSB |

| IVIO          | ae           | D7                  | D6 | D5         | D4          | D3           | D2           | D1 | D0  |

| 0.6m          | sec          | A al. (a ) a a a al |    |            |             |              |              | 0  | 0   |

| 1.2m          | sec          | Advanced            | 0  | Advanced   | switch time | 0            |              | 0  | 1   |

| 2.4m          | sec          | Switch ON/OFF       | U  | of Volume/ | Tone/Fader  | U            | 0            | 1  | 0   |

| 4.8m          | sec          | ON/OFF              |    |            |             |              |              | 1  | 1   |

| Mode      | MSB                |    | ,  | Advanced so<br>Volume/To | witch time o<br>one/Fader | of |         | LSB       |

|-----------|--------------------|----|----|--------------------------|---------------------------|----|---------|-----------|

|           | D7                 | D6 | D5 | D4                       | D3                        | D2 | D1      | D0        |

| 4.6 msec  | A di (a (a a a a d |    | 0  | 0                        |                           |    |         |           |

| 9.3 msec  | Advanced<br>Switch | 0  | 0  | 1                        | 0                         | 0  | Advance | ed switch |

| 18.6 msec | ON/OFF             | U  | 1  | 0                        | U                         | U  | Time o  | of Mute   |

| 37.2 msec | OIN/OI I           |    | 1  | 1                        |                           |    |         |           |

| Mode   | MSB |    |            | Advanced sv | vitch ON/OF | F  |         | LSB       |

|--------|-----|----|------------|-------------|-------------|----|---------|-----------|

| iviode | D7  | D6 | D5         | D4          | D3          | D2 | D1      | D0        |

| OFF    | 0   | 0  | Advanced   | switch time | 0           | 0  | Advance | ed switch |

| ON     | 1   | U  | of Volume/ | Tone/Fader  |             |    | Time o  | of Mute   |

Select address 04(hex)

| Made        | MSB Input Selector LSB |    |    |    |    |    |    |    |  |  |

|-------------|------------------------|----|----|----|----|----|----|----|--|--|

| Mode        | D7                     | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |  |

| Α           |                        |    |    |    |    | 0  | 0  | 0  |  |  |

| В           |                        |    |    |    |    | 0  | 0  | 1  |  |  |

| С           | 0                      | 0  | 0  | 0  | 0  | 0  | 1  | 0  |  |  |

| SHORT       | U                      | U  | 0  | 0  | U  | 1  | 0  | 1  |  |  |

| INPUT MUTE  |                        |    |    |    |    | 1  | 1  | 0  |  |  |

| INPUT WILLE |                        |    |    |    |    | 1  | 1  | 1  |  |  |

:Initial condition

SHORT : The input impedance of each input terminal is lowered from  $100k\Omega(TYP)$  to  $6~k\Omega(TYP)$ . (For quick charge of coupling capacitor)

INPUT MUTE: Mute is done at the input signal in the part of Input Selector.

Select address 06 (hex)

| Coin        | MSB    |    |    | Inpu | t Gain |    |    | LSB |

|-------------|--------|----|----|------|--------|----|----|-----|

| Gain        | D7     | D6 | D5 | D4   | D3     | D2 | D1 | D0  |

| 0dB         |        |    |    | 0    | 0      | 0  | 0  | 0   |

| 1dB         |        |    |    | 0    | 0      | 0  | 0  | 1   |

| 2dB         |        |    |    | 0    | 0      | 0  | 1  | 0   |

| 3dB         |        |    |    | 0    | 0      | 0  | 1  | 1   |

| 4dB         |        |    |    | 0    | 0      | 1  | 0  | 0   |

| 5dB         |        |    |    | 0    | 0      | 1  | 0  | 1   |

| 6dB         |        |    |    | 0    | 0      | 1  | 1  | 0   |

| 7dB         |        |    |    | 0    | 0      | 1  | 1  | 1   |

| 8dB         |        |    |    | 0    | 1      | 0  | 0  | 0   |

| 9dB         |        |    |    | 0    | 1      | 0  | 0  | 1   |

| 10dB        |        |    |    | 0    | 1      | 0  | 1  | 0   |

| 11dB        | Mute   | _  | _  | 0    | 1      | 0  | 1  | 1   |

| 12dB        | ON/OFF | 0  | 0  | 0    | 1      | 1  | 0  | 0   |

| 13dB        |        |    |    | 0    | 1      | 1  | 0  | 1   |

| 14dB        |        |    |    | 0    | 1      | 1  | 1  | 0   |

| 15dB        |        |    |    | 0    | 1      | 1  | 1  | 1   |

| 16dB        |        |    |    | 1    | 0      | 0  | 0  | 0   |

| 17dB        |        |    |    | 1    | 0      | 0  | 0  | 1   |

| 18dB        |        |    |    | 1    | 0      | 0  | 1  | 0   |

| 19dB        |        |    |    | 1    | 0      | 0  | 1  | 1   |

| 20dB        |        |    |    | 1    | 0      | 1  | 0  | 0   |

|             |        |    |    | 1    | 1      | 0  | 1  | 1   |

| Prohibition |        |    |    | :    | :      | :  | :  | :   |

|             |        |    |    | 1    | 1      | 1  | 1  | 1   |

(Note) In case sending prohibited data, 0dB is set.

| Mode | MSB |     |    | Mute | ON/OFF |            |    | LSB |

|------|-----|-----|----|------|--------|------------|----|-----|

| Mode | D7  | D6  | D5 | D4   | D3     | D2         | D1 | D0  |

| OFF  | 0   | 0   | 0  |      |        | Input Cain |    |     |

| ON   | 1   | ] " | U  |      |        | Input Gain |    |     |

:Initial condition

Select address 20 (hex)

| Coin 9 ATT     | MSB      |    | Vol Attenuation |    |    |    |    |    |  |

|----------------|----------|----|-----------------|----|----|----|----|----|--|

| Gain & ATT     | D7       | D6 | D5              | D4 | D3 | D2 | D1 | D0 |  |

| 0dB            |          |    | 0               | 0  | 0  | 0  | 0  | 0  |  |

| -1dB           |          |    | 0               | 0  | 0  | 0  | 0  | 1  |  |

| -2dB           |          |    | 0               | 0  | 0  | 0  | 1  | 0  |  |

| •              |          |    | •               | •  | •  | •  | •  | •  |  |

| •              |          |    | •               |    | •  | •  | •  | •  |  |

| •              |          |    | •               | •  | •  | •  | •  | •  |  |

| -38dB          | 1        | 0  | 1               | 0  | 0  | 1  | 1  | 0  |  |

| -39dB          |          |    | 1               | 0  | 0  | 1  | 1  | 1  |  |

| -40dB          |          |    | 1               | 0  | 1  | 0  | 0  | 0  |  |

|                |          |    | 1               | 0  | 1  | 0  | 0  | 1  |  |

| Prohibition    |          |    | :               | :  | :  | :  | :  | :  |  |

| 1 101110111011 | THORIGIT |    | 1               | 1  | 1  | 1  | 1  | 0  |  |

|                |          |    | 1               | 1  | 1  | 1  | 1  | 1  |  |

(Note) In case sending prohibited data, -40dB is set.

Select address 28, 29, 2A, 2B (hex)

| Gain & ATT | MSB |    |    | Fader At | tenuation |    |    | LSB |

|------------|-----|----|----|----------|-----------|----|----|-----|

| Gain & Air | D7  | D6 | D5 | D4       | D3        | D2 | D1 | D0  |

| 0dB        |     |    | 0  | 0        | 0         | 0  | 0  | 0   |

| -1dB       |     |    | 0  | 0        | 0         | 0  | 0  | 1   |

| -2dB       |     |    | 0  | 0        | 0         | 0  | 1  | 0   |

| •          |     |    | •  | •        | •         | •  | •  | •   |

| •          | 1   | 0  | •  | •        | •         | •  | •  | •   |

| •          |     |    | •  | •        | •         | •  | •  | •   |

| -61dB      |     |    | 1  | 1        | 1         | 1  | 0  | 1   |

| -62dB      |     |    | 1  | 1        | 1         | 1  | 1  | 0   |

| -∞dB       |     |    | 1  | 1        | 1         | 1  | 1  | 1   |

: Initial condition

Select address 51, 57 (hex)

| Goin        | MSB    |    |    | Bass/Tre | eble Gain |    |    | LSB |

|-------------|--------|----|----|----------|-----------|----|----|-----|

| Gain        | D7     | D6 | D5 | D4       | D3        | D2 | D1 | D0  |

| 0dB         |        |    |    | 0        | 0         | 0  | 0  | 0   |

| 1dB         |        |    |    | 0        | 0         | 0  | 0  | 1   |

| 2dB         |        |    |    | 0        | 0         | 0  | 1  | 0   |

| 3dB         |        |    |    | 0        | 0         | 0  | 1  | 1   |

| 4dB         |        |    |    | 0        | 0         | 1  | 0  | 0   |

| 5dB         |        |    |    | 0        | 0         | 1  | 0  | 1   |

| 6dB         |        |    |    | 0        | 0         | 1  | 1  | 0   |

| 7dB         |        |    |    | 0        | 0         | 1  | 1  | 1   |

| 8dB         |        |    |    | 0        | 1         | 0  | 0  | 0   |

| 9dB         |        |    |    | 0        | 1         | 0  | 0  | 1   |

| 10dB        |        |    |    | 0        | 1         | 0  | 1  | 0   |

| 11dB        | Bass/  |    |    | 0        | 1         | 0  | 1  | 1   |

| 12dB        | Treble | 0  | 0  | 0        | 1         | 1  | 0  | 0   |

| 13dB        | Boost  |    |    | 0        | 1         | 1  | 0  | 1   |

| 14dB        | /cut   |    |    | 0        | 1         | 1  | 1  | 0   |

| 15dB        |        |    |    | 0        | 1         | 1  | 1  | 1   |

| 16dB        |        |    |    | 1        | 0         | 0  | 0  | 0   |

| 17dB        |        |    |    | 1        | 0         | 0  | 0  | 1   |

| 18dB        |        |    |    | 1        | 0         | 0  | 1  | 0   |

| 19dB        |        |    |    | 1        | 0         | 0  | 1  | 1   |

| 20dB        |        |    |    | 1        | 0         | 1  | 0  | 0   |

|             |        |    |    | 1        | 0         | 1  | 0  | 1   |

| Prohibition |        |    |    | :        | ÷         | :  | :  | :   |

|             |        |    |    | 1        | 1         | 1  | 1  | 0   |

|             |        |    |    | 1        | 1         | 1  | 1  | 1   |

(Note) In case sending prohibited data, 0dB is set.

| Mode   | MSB |     |    | Bass/Treble | Boost/Cut |                |              | LSB |

|--------|-----|-----|----|-------------|-----------|----------------|--------------|-----|

| Iviode | D7  | D6  | D5 | D4          | D3        | D2             | D1           | D0  |

| Boost  | 0   | 0   | 0  |             | De        | ss/Treble Ga   | nin .        |     |

| Cut    | 1   | ] 0 | 0  |             | Da        | iss/ iteble Ga | <b>A</b> III |     |

:Initial condition

#### (6) About Power ON Reset

Built-in IC initialization is made during power on of the supply voltage. Please send initial data to all addresses at supply voltage on. And please turn ON mute at the set side until this initial data is sent.

| at supply voltage on. And p           | lease turri       | ON IIIule | at the se | t Side un | 111 11115 1111 | liai uala 15 Seril.                     |

|---------------------------------------|-------------------|-----------|-----------|-----------|----------------|-----------------------------------------|

|                                       |                   | Limit     |           |           |                |                                         |

| Parameter                             | Symbol            | Min       | Тур       | Max       | Unit           | Conditions                              |

| Rise Time of VCC                      | t <sub>RISE</sub> | 20        | -         | -         | μsec           | V <sub>CC</sub> rise time from 0V to 3V |

| VCC Voltage of Release Power ON Reset | V <sub>POR</sub>  | -         | 4.1       | -         | V              |                                         |

# (7) About External Compulsory Mute Terminal

It is possible to force mute externally by setting an input voltage to the MUTE terminal.

| Mute Voltage Condition  | Mode     |

|-------------------------|----------|

| GND to 1.0V             | MUTE ON  |

| 2.3V to V <sub>CC</sub> | MUTE OFF |

Establish the voltage of MUTE in the condition to be defined.

# **Application Information**

# 1. Function and Specifications

| Function       | Specifications                                                         |  |  |  |  |  |  |

|----------------|------------------------------------------------------------------------|--|--|--|--|--|--|

| Input selector | · Stereo 3 input                                                       |  |  |  |  |  |  |

| Input gain     | · 0dB to 20dB                                                          |  |  |  |  |  |  |

| Mute           | · Possible to use "Advanced switch" for prevention of switching noise. |  |  |  |  |  |  |

| Volume         | · 0dB to -40dB (1dB step)                                              |  |  |  |  |  |  |

| volume         | Possible to use "Advanced switch" for prevention of switching noise.   |  |  |  |  |  |  |

|                | · -20dB to +20dB (1dB step)                                            |  |  |  |  |  |  |

| Bass           | · Q=1                                                                  |  |  |  |  |  |  |

| Dass           | · fo=100Hz                                                             |  |  |  |  |  |  |

|                | Possible to use advanced switch at changing gain                       |  |  |  |  |  |  |

|                | · -20dB to +20dB (1dB step)                                            |  |  |  |  |  |  |

| Treble         | · Q=1                                                                  |  |  |  |  |  |  |

| Пеые           | · fo=10kHz                                                             |  |  |  |  |  |  |

|                | Possible to use advanced switch at changing gain                       |  |  |  |  |  |  |

| Fader          | · 0dB to -62dB(1dB step), -∞dB                                         |  |  |  |  |  |  |

| i adei         | Possible to use "Advanced switch" for prevention of switching noise.   |  |  |  |  |  |  |

# 2. Volume / Fader Volume Attenuation Data

| (dB) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | (dB) | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|------|----|----|----|----|----|----|----|----|------|----|----|----|----|----|----|----|----|

| 0    |    |    | 0  | 0  | 0  | 0  | 0  | 0  | -32  |    |    | 1  | 0  | 0  | 0  | 0  | 0  |

| -1   |    |    | 0  | 0  | 0  | 0  | 0  | 1  | -33  |    |    | 1  | 0  | 0  | 0  | 0  | 1  |

| -2   |    |    | 0  | 0  | 0  | 0  | 1  | 0  | -34  |    |    | 1  | 0  | 0  | 0  | 1  | 0  |

| -3   |    |    | 0  | 0  | 0  | 0  | 1  | 1  | -35  |    |    | 1  | 0  | 0  | 0  | 1  | 1  |

| -4   |    |    | 0  | 0  | 0  | 1  | 0  | 0  | -36  |    |    | 1  | 0  | 0  | 1  | 0  | 0  |

| -5   |    |    | 0  | 0  | 0  | 1  | 0  | 1  | -37  |    |    | 1  | 0  | 0  | 1  | 0  | 1  |

| -6   |    |    | 0  | 0  | 0  | 1  | 1  | 0  | -38  |    |    | 1  | 0  | 0  | 1  | 1  | 0  |

| -7   |    |    | 0  | 0  | 0  | 1  | 1  | 1  | -39  |    |    | 1  | 0  | 0  | 1  | 1  | 1  |

| -8   |    |    | 0  | 0  | 1  | 0  | 0  | 0  | -40  |    |    | 1  | 0  | 1  | 0  | 0  | 0  |

| -9   |    |    | 0  | 0  | 1  | 0  | 0  | 1  | -41  |    |    | 1  | 0  | 1  | 0  | 0  | 1  |

| -10  |    |    | 0  | 0  | 1  | 0  | 1  | 0  | -42  |    |    | 1  | 0  | 1  | 0  | 1  | 0  |

| -11  |    |    | 0  | 0  | 1  | 0  | 1  | 1  | -43  |    |    | 1  | 0  | 1  | 0  | 1  | 1  |

| -12  |    |    | 0  | 0  | 1  | 1  | 0  | 0  | -44  |    |    | 1  | 0  | 1  | 1  | 0  | 0  |

| -13  |    |    | 0  | 0  | 1  | 1  | 0  | 1  | -45  |    |    | 1  | 0  | 1  | 1  | 0  | 1  |

| -14  |    |    | 0  | 0  | 1  | 1  | 1  | 0  | -46  |    |    | 1  | 0  | 1  | 1  | 1  | 0  |

| -15  | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 1  | -47  | 1  | 0  | 1  | 0  | 1  | 1  | 1  | 1  |

| -16  | '  | U  | 0  | 1  | 0  | 0  | 0  | 0  | -48  | '  | U  | 1  | 1  | 0  | 0  | 0  | 0  |

| -17  |    |    | 0  | 1  | 0  | 0  | 0  | 1  | -49  |    |    | 1  | 1  | 0  | 0  | 0  | 1  |

| -18  |    |    | 0  | 1  | 0  | 0  | 1  | 0  | -50  |    |    | 1  | 1  | 0  | 0  | 1  | 0  |

| -19  |    |    | 0  | 1  | 0  | 0  | 1  | 1  | -51  |    |    | 1  | 1  | 0  | 0  | 1  | 1  |

| -20  |    |    | 0  | 1  | 0  | 1  | 0  | 0  | -52  |    |    | 1  | 1  | 0  | 1  | 0  | 0  |

| -21  |    |    | 0  | 1  | 0  | 1  | 0  | 1  | -53  |    |    | 1  | 1  | 0  | 1  | 0  | 1  |

| -22  |    |    | 0  | 1  | 0  | 1  | 1  | 0  | -54  |    |    | 1  | 1  | 0  | 1  | 1  | 0  |

| -23  |    |    | 0  | 1  | 0  | 1  | 1  | 1  | -55  |    |    | 1  | 1  | 0  | 1  | 1  | 1  |

| -24  |    |    | 0  | 1  | 1  | 0  | 0  | 0  | -56  |    |    | 1  | 1  | 1  | 0  | 0  | 0  |

| -25  |    |    | 0  | 1  | 1  | 0  | 0  | 1  | -57  |    |    | 1  | 1  | 1  | 0  | 0  | 1  |

| -26  |    |    | 0  | 1  | 1  | 0  | 1  | 0  | -58  |    |    | 1  | 1  | 1  | 0  | 1  | 0  |

| -27  |    |    | 0  | 1  | 1  | 0  | 1  | 1  | -59  |    |    | 1  | 1  | 1  | 0  | 1  | 1  |

| -28  |    |    | 0  | 1  | 1  | 1  | 0  | 0  | -60  |    |    | 1  | 1  | 1  | 1  | 0  | 0  |

| -29  |    |    | 0  | 1  | 1  | 1  | 0  | 1  | -61  |    |    | 1  | 1  | 1  | 1  | 0  | 1  |

| -30  |    |    | 0  | 1  | 1  | 1  | 1  | 0  | -62  |    |    | 1  | 1  | 1  | 1  | 1  | 0  |

| -31  |    |    | 0  | 1  | 1  | 1  | 1  | 1  | - 80 |    |    | 1  | 1  | 1  | 1  | 1  | 1  |

For Volume attenuation, only 0dB to -40dB are available.

: Initial condition

#### 3. Application Circuit

#### Notes on wiring

- ① Please connect the decoupling capacitor of the power supply in the shortest possible distance to GND.

- ② GND lines should be one-point connected.

- ③ Wiring pattern of Digital should be away from that of Analog unit and cross-talk should not be acceptable.

- SCL and SDA lines of I<sup>2</sup>C BUS should not be parallel if possible.

The lines should be shielded, if they are adjacent to each other.

- ⑤ Analog input lines should not be parallel if possible. The lines should be shielded, if they are adjacent to each other.

- 6 For TEST pins (Pin 7,8,9), please leave them as OPEN.

#### **Power Dissipation**

About the thermal design of the IC

Characteristics of an IC have a great deal to do with the temperature at which it is used, and exceeding absolute maximum ratings may degrade and destroy the device. Careful consideration must be given to the heat of the IC from the two standpoints of immediate damage and long-term reliability of operation.

Figure 18. Temperature Derating Curve

(Note) Values are actual measurements and are not guaranteed.

Power dissipation values vary according to the board on which the IC is mounted.

I/O Equivalent Circuits

|                      | nt Circuits                      |                 |                                            | 1                                                                                                                                                      |  |  |  |

|----------------------|----------------------------------|-----------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Terminal<br>No.      | Terminal<br>Name                 | Terminal        | Equivalent Circuit                         | Terminal Description                                                                                                                                   |  |  |  |

| 1 2 3 4 5 6          | A1<br>A2<br>B1<br>B2<br>C1<br>C2 | Voltage<br>4.25 | VCC VO | A terminal for signal input. The input impedance is 100kΩ(typ).                                                                                        |  |  |  |

| 16                   | MUTE                             | _               | VCC<br>O<br>D<br>O<br>1.65V                | A terminal for external compulsory mute. If terminal voltage is High level, the mute is off. And if the terminal voltage is Low level, the mute is on. |  |  |  |

| 11<br>12<br>13<br>14 | OUTR2<br>OUTR1<br>OUTF2<br>OUTF1 | 4.25            | VCC<br>GND<br>GND                          | A terminal for fader and Subwoofer output.                                                                                                             |  |  |  |

| 15                   | VCC                              | 8.5             |                                            | Power supply terminal.                                                                                                                                 |  |  |  |

| 17                   | SCL                              | -               | VCC<br>O<br>1.65V                          | A terminal for clock input of I <sup>2</sup> C BUS communication.                                                                                      |  |  |  |

$Values \ in \ the \ pin \ explanation \ and \ input/output \ equivalent \ circuit \ are \ reference \ values \ only \ and \ are \ not \ guaranteed.$

I/O Equivalent Circuits - continued

| Terminal | Terminal    | Terminal     | Equivalent Circuit       | Terminal Description                                                                                                                                  |

|----------|-------------|--------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| No. 18   | Name<br>SDA | Voltage<br>- | VCC<br>O<br>GND<br>I.65V | A terminal for data input of I <sup>2</sup> C BUS communication.                                                                                      |

| 19       | GND         | 0            |                          | Ground terminal.                                                                                                                                      |

| 20       | FIL         | 4.25         | VCC                      | Voltage for reference bias of analog signal system. The simple precharge circuit and simple discharge circuit for an external capacitor are built in. |

| 7        | TEST1       |              |                          | TEST terminal.                                                                                                                                        |

| 8        | TEST2       | -            |                          |                                                                                                                                                       |

| 9        | TEST3       |              |                          |                                                                                                                                                       |

Values in the pin explanation and input/output equivalent circuit are reference values only and are not guaranteed.

#### **Operational Notes**

#### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply pins.

#### 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

#### 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

#### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

#### 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the Pd rating.

#### 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

#### 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

#### 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

#### 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

#### 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

#### 11. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

# **Operational Notes - continued**

#### 12. Regarding the Input Pin of the IC

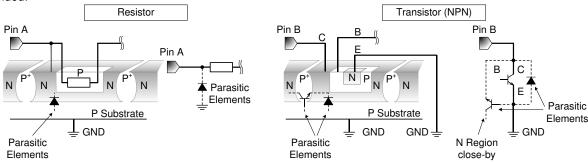

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode. When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

Figure 19. Example of monolithic IC structure

#### 13. About a Signal Input Part

#### (a) About Input Coupling Capacitor Constant Value

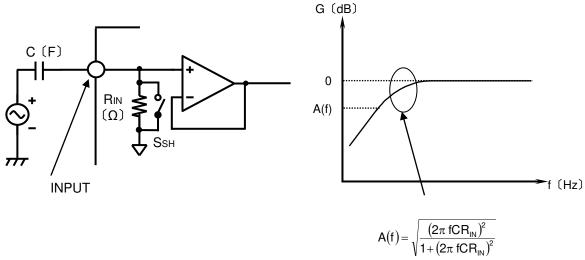

In the input signal terminal, please decide the constant value of the input coupling capacitor C(F) that would be sufficient to form an RC characterized HPF with input impedance  $R_{IN}(\Omega)$  inside the IC.

# (b) About the Input Selector SHORT

SHORT mode is the command which makes switch  $S_{SH}$  =ON of input selector part so that the input impedance  $R_{IN}$  of all terminals becomes small. Switch  $S_{SH}$  is OFF when SHORT command is not selected. The constant time brought about by the small resistance inside and the capacitor outside the LSI becomes

small when this command is used. The charge time of the capacitor becomes short. Since SHORT mode turns ON the switch of S<sub>SH</sub> and makes it low impedance, please use it at no signal condition.

#### 14. About Mute Terminal(Pin 16) when power supply is OFF

There should be no applied voltage across the Mute terminal (Pin 16) when power-supply is OFF. A resistor (about  $2.2k\Omega$ ) should be connected in series to Mute terminal in case a voltage is supplied to Mute terminal. (Please refer Application Circuit Diagram.)

# 15. About TEST Pin

TEST Pin, should be OPEN. Pin 9, 8, 7 are TEST Pins.

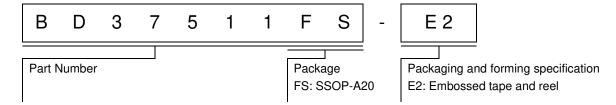

# **Ordering Information**

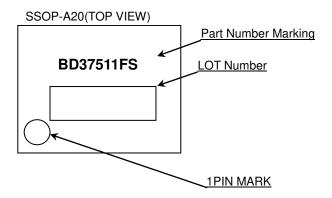

# **Marking Diagram**