# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 1.8V to 5.5V, Integrated 2.0A MOSFET 1ch **Buck-Boost Converter**

**BD8306MUV**

# **General Description**

ROHM's highly-efficient buck-boost converter BD8306MUV produces buck-boost output voltage including 3.3 V from two-cell or three-cell alkaline battery, or one-cell lithium-ion battery with just one inductor. This IC adopts the original buck-boost drive system and creates a more efficient power supply than the conventional SEPIC-system or H-bridge system switching regulators.

#### **Features**

- Highly-Efficient Buck-Boost DC/DC Converter Constructed with just one Inductor.

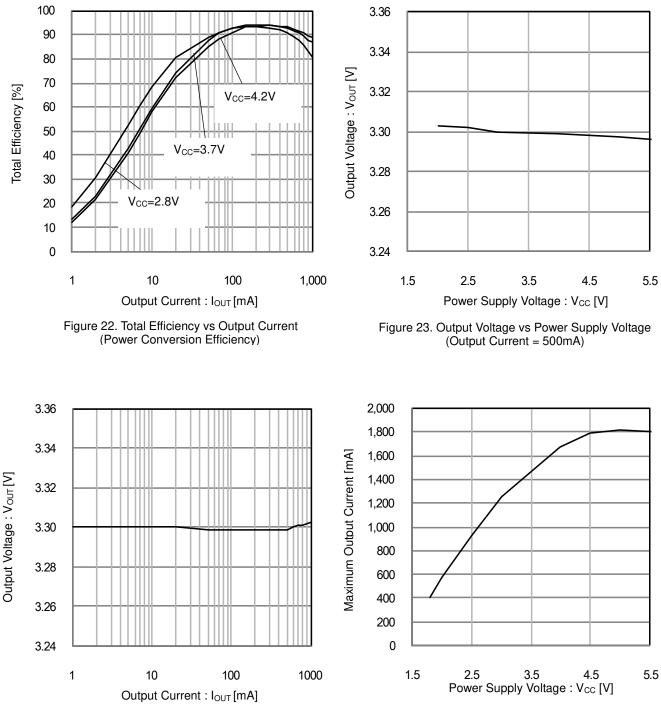

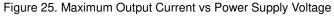

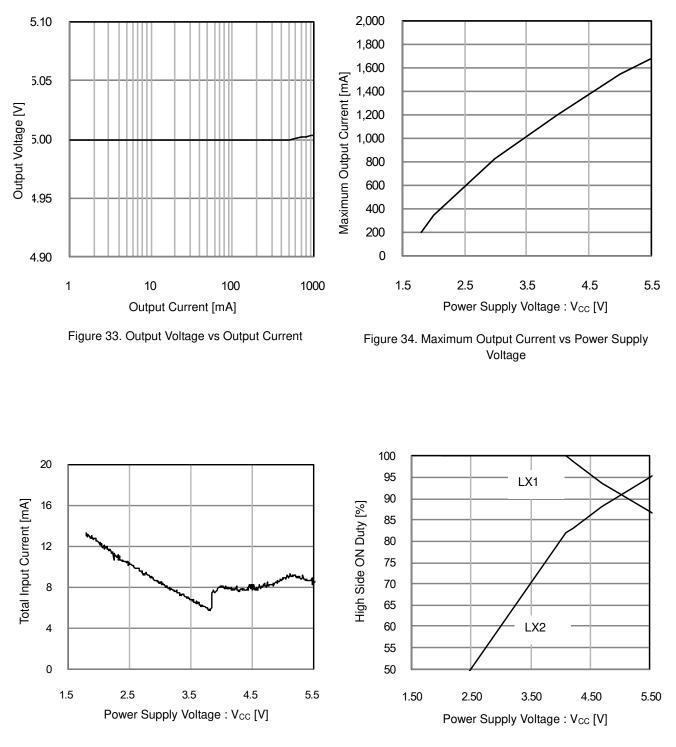

- Maximum output current changes depending on the input and output voltages. Input current for PVCC terminal should be less than 2.0A including the DC current and ripple current of the inductor. Please refer to Figure 25 and Figure 34 for details about the maximum output current at 3.3V and 5.0V output.

- Incorporates a Soft-Start Function.

- Incorporates a Timer Latch System with Short Protection Function.

# Application

- General Portable Equipment

- DSC

- DVC

- Cellular Phone

- PDA

- LED

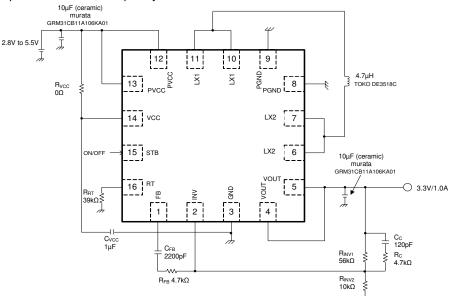

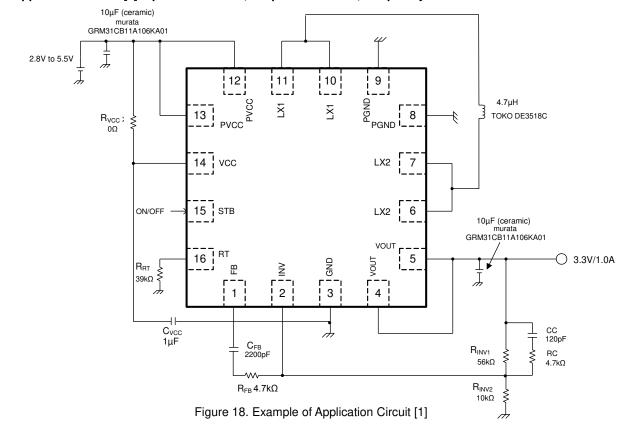

# **Typical Application Circuit**

2.8V to 5.5V, Output: 3.3V / 1.0 A, Frequency 1MHz

OProduct structure : Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays

# **Key Specifications**

- Input Voltage Range: +1.8V to +5.5V **Output Voltage Range:** +1.8V to +5.2V **Output Current:** (at 3.3V Output, +2.8V to +5.5V Input) 1.0A (at 5.0V Output, +2.8V to +5.5V Input) 0.7A Pch FET ON-Resistance: 120mΩ(Typ)

- Nch FET ON-Resistance:  $100m\Omega(Typ)$

- Standby Current: 0µA (Typ)

- **Operating Temperature Range:** -40°C to +85°C

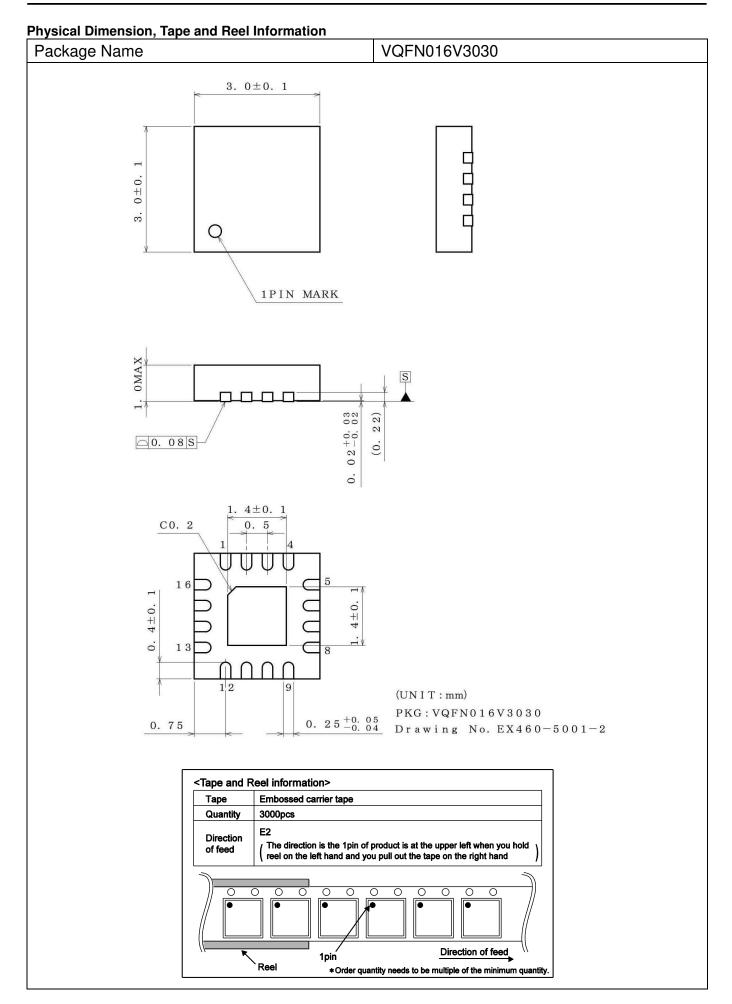

Package

W (Typ) x D (Typ) x H (Max)

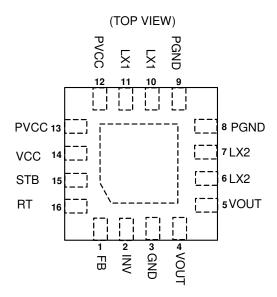

# **Pin Configuration**

# Pin Descriptions

| Pin Name | Function                                                             |  |  |  |

|----------|----------------------------------------------------------------------|--|--|--|

| FB       | Output pin of error amp                                              |  |  |  |

| INV      | Input pin of error amp                                               |  |  |  |

| GND      | Ground pin                                                           |  |  |  |

| VOUT     | Output voltage pin                                                   |  |  |  |

| LX2      | Output side pin for inductor                                         |  |  |  |

| PGND     | Ground pin for POW-MOS                                               |  |  |  |

| LX1      | Input side pin for inductor                                          |  |  |  |

| PVCC     | Voltage supply pin for DC/DC converter                               |  |  |  |

| VCC      | Voltage supply pin for control block                                 |  |  |  |

| STB      | ON/OFF pin                                                           |  |  |  |

| RT       | Pin for configuration of frequency                                   |  |  |  |

|          | FB<br>INV<br>GND<br>VOUT<br>LX2<br>PGND<br>LX1<br>PVCC<br>VCC<br>STB |  |  |  |

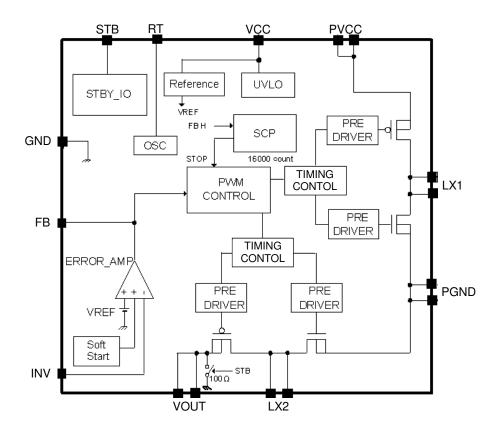

# **Block Diagram**

# **Description of Blocks**

# 1. VREF

This block generates ERROR AMP reference voltage. The reference voltage is 0.5V.

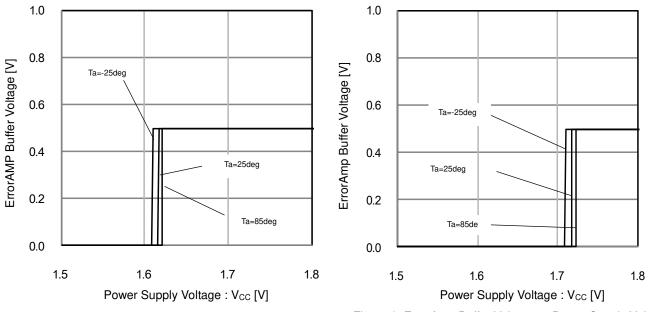

2. UVLO

Circuit for preventing malfunction at low voltage input. This circuit prevents malfunction of the internal circuit while start up of the power supply voltage or while low power supply voltage input. The circuit monitors VCC pin voltage then turns OFF all output FETs and DC/DC converter output when VCC voltage is lower than 1.6V, and reset the timer latch of the internal SCP circuit and soft-start circuit.

3. SCP

Short-circuit protection circuit based on timer latch system.

When the INV pin voltage is lower than 0.5V, the internal SCP circuit starts counting. SCP circuit detects high voltage output of Error AMP. Since internal Error AMP has highly gain as high as 80dB or more, the output voltage of Error AMP goes high and detects SCP even 1mV drop than set voltage (0.5V typ) occurs on INV pin voltage. The internal counter is in synch with OSC, the latch circuit activates after the counter counts about 16400 oscillations to turn OFF DC/DC converter output (about 16.4 msec when  $R_{RT}$  =39K $\Omega$ ). To reset the latch circuit, turn OFF the STB pin once. Then, turn it ON again or turn on the power supply voltage again.

4. OSC

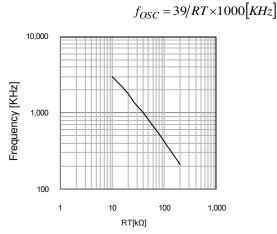

Oscillation circuit to change frequency by external resistance of the RT pin (Pin 16). When  $R_{RT}$  = 39 k $\Omega$ , operation frequency of DC/DC converter is set at 1 MHz.

5. ERROR AMP

Error amplifier for monitoring output voltage and output PWM control signals. The internal reference voltage for Error AMP is set at 0.5 V.

# 6. PWM COMP

Voltage-pulse width converter for controlling output voltage corresponding to input voltage. Comparing the internal SLOPE waveform with the ERROR AMP output voltage, PWM COMP controls the pulse width and outputs to the driver. Max Duty and Min Duty are set at the primary side (LX1) and the secondary side (LX2) of the inductor respectively, which are as follows:

| Primary side (LX1)   | Max Duty : | 100 %(LX1 High side PMOS ON Duty) |

|----------------------|------------|-----------------------------------|

|                      | Min Duty : | 0 %(LX1 High side PMOS ON Duty)   |

| Secondary side (LX2) | Max Duty : | 85 %(LX2 Low side NMOS ON Duty)   |

|                      | Min Duty : | 0 %(LX2 Low side NMOS ON Duty)    |

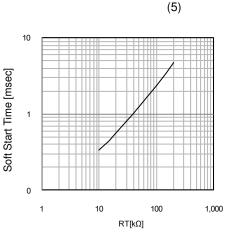

#### 7. SOFT START

Circuit for preventing in-rush current at startup by bringing the output voltage of the DC/DC converter into a soft-start. Soft-start time is in synch with the internal OSC, and the output voltage of the DC/DC converter reaches the set voltage after about 1000 oscillations (About 1 msec when  $R_{RT}$  = 39 k $\Omega$ ).

#### 8. PRE DRIVER

CMOS inverter circuit for driving the built-in Pch/Nch FET.Dead time is provided for preventing feed through during switching. The dead time is set at about 15 nsec for each individual SWs.

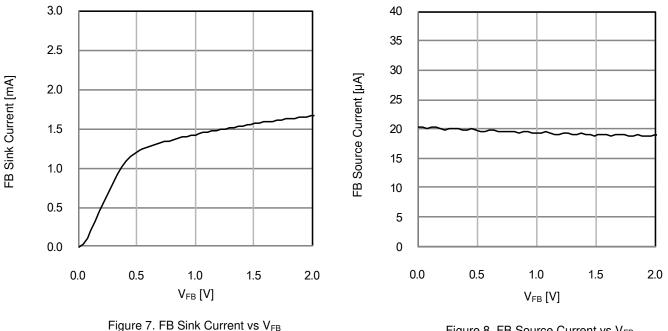

#### 9. STBY\_IO

Voltage applied on STB pin (Pin 15) to control ON/OFF of IC. Turned ON when a voltage of 1.5V or higher is applied and turned OFF when the terminal is open or 0V is applied. Incorporates approximately 400 k $\Omega$  pull-down resistance.

10. Pch/Nch FET SW

Built-in SW for switching the inductor current of the DC/DC converter. Pch FET is about  $120m\Omega$  and Nch is  $100m\Omega$ . Since the current rating of this FET is 2A, it should be used within 2A in total including the DC current and ripple current of the inductor. The peak current of the inductor can be calculated by equation (1), (2), (3).

# **Absolute Maximum Ratings**

| Parameter                    | Symbol               | Rating      | Unit |

|------------------------------|----------------------|-------------|------|

| Maximum Input Supply Voltage | $V_{CC}$ , $PV_{CC}$ | -0.3 to +7  | V    |

| Maximum Input Current        | I <sub>INMAX</sub>   | 2.0         | А    |

| Maximum Input Valtaga        | $V_{LX1}$            | 7.0         | V    |

| Maximum Input Voltage        | $V_{LX2}$            | 7.0         | V    |

| Power Dissipation (Note 1)   | Pd                   | 0.62        | W    |

| Storage Temperature          | Tstg                 | -55 to +150 | °C   |

| Junction Temperature         | Tjmax                | +150        | °C   |

(Note 1) When mounted on 74.2x74.2x1.6mm and operated over 25°C Pd reduces by 4.96mW/°C. **Caution**: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

#### Recommended Operating Conditions(Ta=25°C)

| Parameter                   | Symbol           |     | Unit |     |      |

|-----------------------------|------------------|-----|------|-----|------|

| Farameter                   |                  | Min | Тур  | Max | Unit |

| Power Supply Voltage Range  | Vcc              | 1.8 | -    | 5.5 | V    |

| Output Voltage Range        | V <sub>OUT</sub> | 1.8 | -    | 5.2 | V    |

| Operating Temperature Range | Topr             | -40 | -    | +85 | °C   |

# **Electrical Characteristics** (Unless otherwise specified Ta=25°C, V<sub>CC</sub>=3V)

| Bara                   | Parameter        |                    | Symbol |       | Limit  |      | Conditions                                                |

|------------------------|------------------|--------------------|--------|-------|--------|------|-----------------------------------------------------------|

| Parameter              |                  | Symbol             | Min    | Тур   | yp Max |      | Conditions                                                |

| [Under Voltage         | Lock Out Circuit | ]                  |        |       |        |      |                                                           |

| Reset Voltage          |                  | V <sub>UV</sub>    | -      | 1.7   | 1.8    | V    | VCC sweep up                                              |

| Hysteresis Width       |                  | $\Delta_{VUVHY}$   | 50     | 100   | 150    | mV   |                                                           |

| [Oscillator]           |                  |                    |        |       |        |      |                                                           |

| Frequency              |                  | f <sub>OSC</sub>   | 0.9    | 1.0   | 1.1    | MHz  | R <sub>RT</sub> =39KΩ                                     |

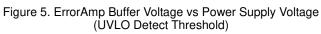

| [Error AMP]            |                  |                    |        |       |        |      |                                                           |

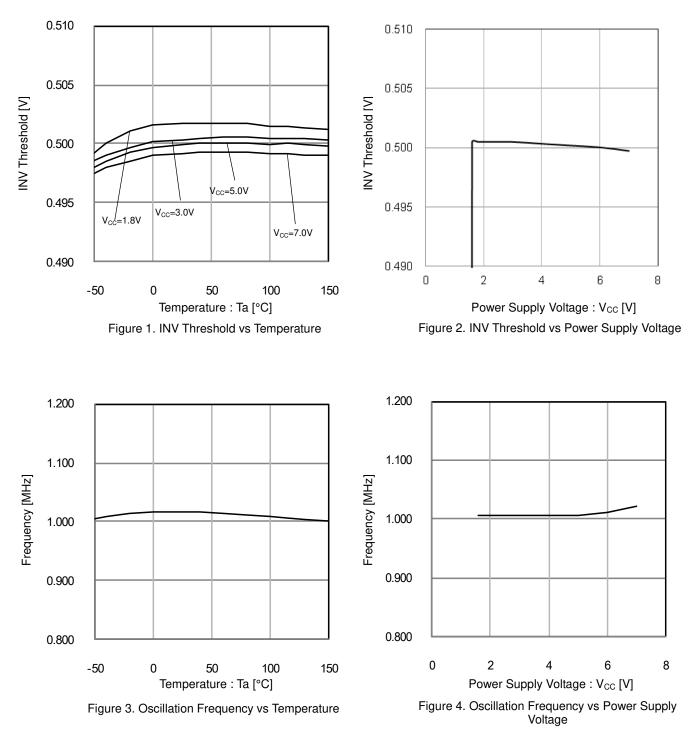

| Input Threshold        | d Voltage        | VINV               | 0.495  | 0.500 | 0.505  | V    |                                                           |

| Input Bias Curr        | ent              | l <sub>INV</sub>   | -50    | 0     | +50    | nA   | $V_{CC}{=}7.0V\;, V_{INV}{=}3.5V$                         |

| Soft Start Time        |                  | t <sub>ss</sub>    | 0.60   | 1.00  | 1.40   | msec | R <sub>RT</sub> =39kΩ                                     |

| Output Source          | Current          | I <sub>EO</sub>    | 10     | 20    | 30     | μA   | $V_{INV}$ =0.2V , $V_{FB}$ =1.5V                          |

| Output Sink Cu         | irrent           | I <sub>EI</sub>    | 0.6    | 1.2   | 2.4    | mA   | $V_{INV}$ =0.8V , $V_{FB}$ =1.5V                          |

| [PWM Compara           | ator]            |                    |        |       |        |      |                                                           |

| LX1 Max Duty           |                  | D <sub>MAX1</sub>  | -      | -     | 100    | %    | High side ON Duty                                         |

| LX2 Max Duty           |                  | D <sub>MAX2</sub>  | 77     | 85    | 93     | %    | Low side ON Duty                                          |

| [Output]               |                  |                    |        |       |        |      |                                                           |

| LX1 PMOS ON-Resistance |                  | R <sub>ON1P</sub>  | -      | 120   | 200    | mΩ   | V <sub>GS</sub> =3.0V                                     |

| LX1 NMOS ON-Resistance |                  | R <sub>ON1N</sub>  | -      | 100   | 160    | mΩ   | V <sub>GS</sub> =3.0V                                     |

| LX2 PMOS ON            | l-Resistance     | R <sub>ON2P</sub>  | -      | 120   | 200    | mΩ   | V <sub>GS</sub> =3.0V                                     |

| LX2 NMOS ON            | I-Resistance     | R <sub>ON2N</sub>  | -      | 100   | 160    | mΩ   | V <sub>GS</sub> =3.0V                                     |

| VOUT Discharç          | ge Switch        | R <sub>DVO</sub>   | -      | 100   | 160    | Ω    | $V_{GS}$ =3.0V, on at STB OFF                             |

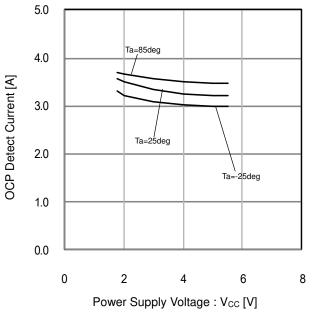

| LX1 OCP Three          | shold            | I <sub>OCP</sub>   | 2.0    | 3.0   | -      | Α    | PV <sub>CC</sub> =3.0V                                    |

| LX1 Leak Curre         | ent              | I <sub>LEAK1</sub> | -1     | 0     | +1     | μA   |                                                           |

| LX2 Leak Curre         | ent              | I <sub>LEAK2</sub> | -1     | 0     | +1     | μA   |                                                           |

| [STB]                  |                  |                    |        |       |        |      |                                                           |

| STB Pin                | Enable           | V <sub>STBH</sub>  | 1.5    | -     | 5.5    | V    |                                                           |

| Control<br>Voltage     | Disable          | V <sub>STBL</sub>  | -0.3   | -     | +0.3   | V    |                                                           |

| STB Pull Down          | Resistance       | R <sub>STB</sub>   | 250    | 400   | 700    | kΩ   |                                                           |

| [Circuit Current       | :]               | 1                  |        |       |        | 1    |                                                           |

| -<br>Stand-By          | VCC Pin          | I <sub>STB1</sub>  | -      | -     | 1      | μA   |                                                           |

| Current                | PVCC Pin         | I <sub>STB2</sub>  | -      | -     | 1      | μΑ   |                                                           |

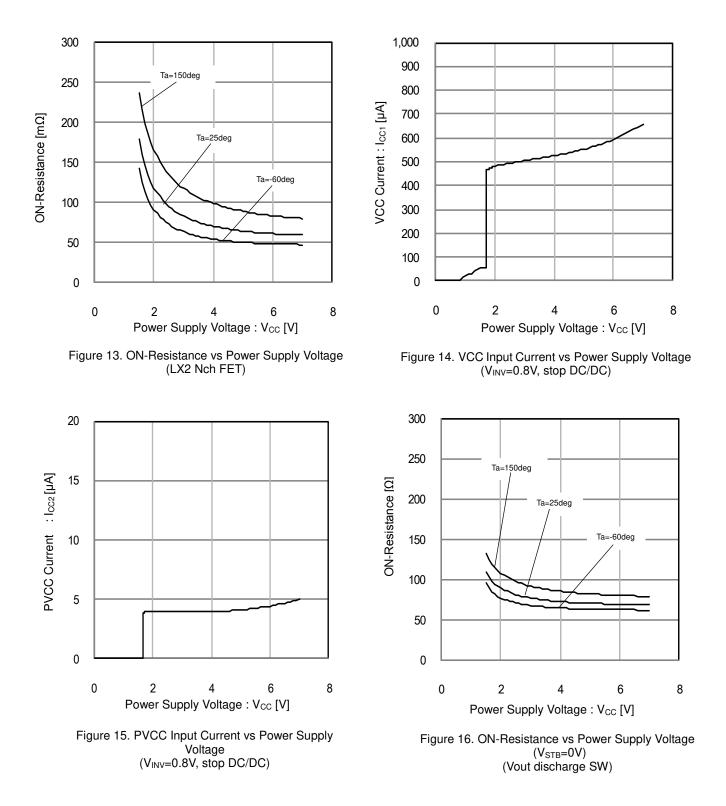

| VCC Circuit Cu         | irrent           | I <sub>CC1</sub>   | -      | 500   | 750    | μA   | <sup>(Note 2)</sup> V <sub>INV</sub> =0.8V,<br>stop_DC/DC |

| PVCC Circuit C         | Current          | I <sub>CC2</sub>   | -      | 10    | 20     | μA   | (Note 2) V <sub>INV</sub> =0.8V,<br>stop DC/DC            |

| VOUT Circuit C         | Current          | I <sub>CC3</sub>   | -      | 10    | 20     | μA   | <sup>(Note 2)</sup> V <sub>INV</sub> =0.8V,<br>stop DC/DC |

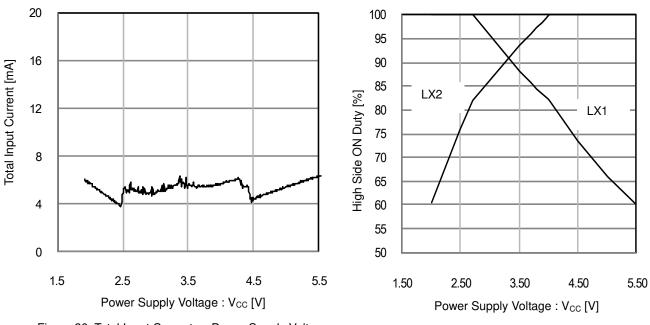

(Note 2) I<sub>CC1</sub>, I<sub>CC2</sub>, I<sub>CC3</sub> are currents flowing to VCC, PVCC, VOUT terminals. When the input voltage of INV pin is 0.8V, DC/DC converter operation stops. Total input current on DC/DC converter operation would be greater than the limit mentioned above. Please refer to Figure 26 and Figure 35 for details about the total input current under DC/DC converter operation at 3.3V and 5.0V output.

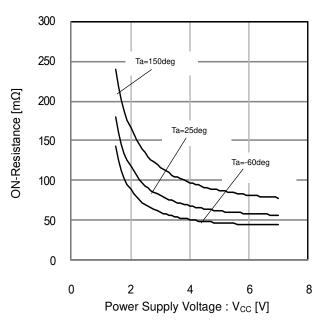

# **Typical Performance Curves**

(Unless otherwise specified, Ta =  $25^{\circ}$ C, V<sub>CC</sub> = 3.7V)

Figure 6. ErrorAmp Buffer Voltage vs Power Supply Voltage (UVLO Reset Threshold)

(V<sub>INV</sub>=0.8V)

Figure 8. FB Source Current vs  $V_{\text{FB}}$   $(V_{\text{INV}}{=}0.2\text{V})$

Figure 9. ErrorAmp Buffer Voltage vs STB Threshold Voltage

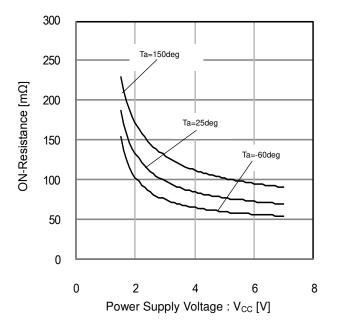

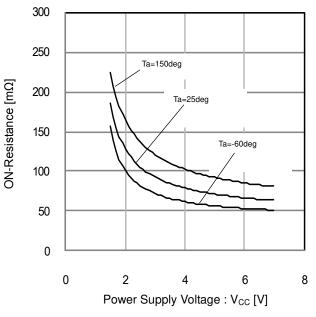

Figure 11. ON-Resistance vs Power Supply Voltage (LX1 Nch FET)

Figure 10. ON-Resistance vs Power Supply Voltage (LX1 Pch FET)

Figure 12. ON-Resistance vs Power Supply Voltage (LX2 Pch FET)

Figure 17. OCP Detect Current vs Power Supply Voltage

# **Application Information**

1. Application Circuit [1] Input: 2.8V to 5.5V, Output: 3.3V / 1.0A, Frequency 1MHz

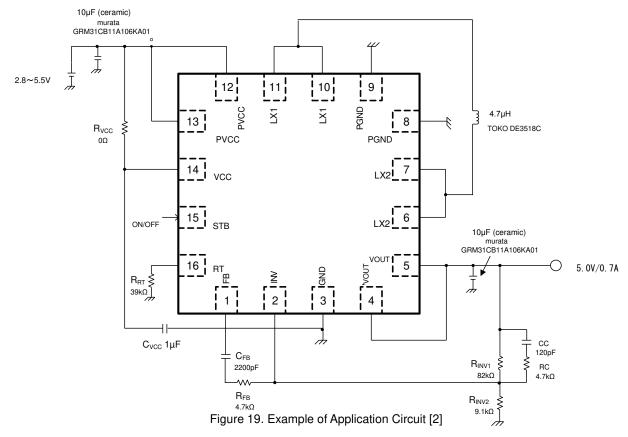

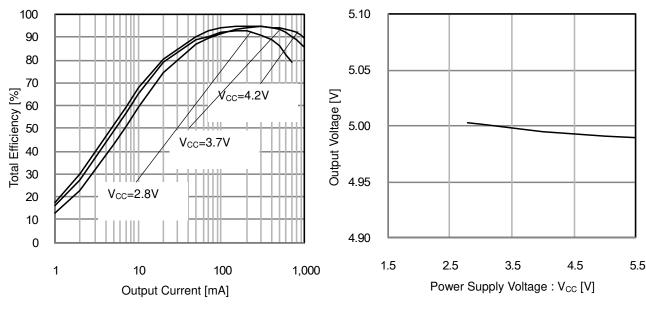

# 2. Application Circuit [2] Input: 2.8V to 5.5V, Output: 5.0V / 0.7A, Frequency 1MHz

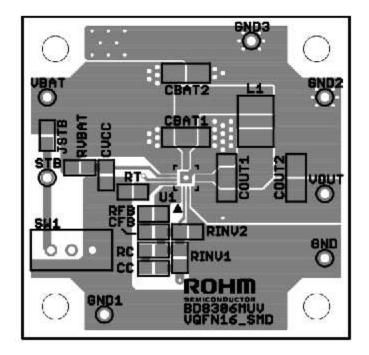

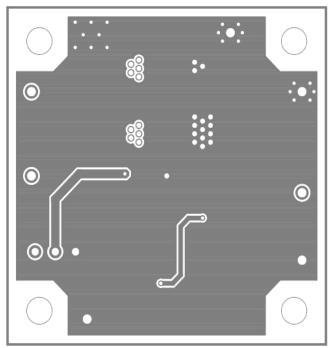

3. Sample Board Layout

Figure 20. Assembly Layer

Figure 21. Bottom Layer

4. Reference Application Data (Unless otherwise specified, Ta =  $25^{\circ}$ C, V<sub>CC</sub> = 3.7 V) Sample Application 1

Figure 24. Output Voltage vs Output Current

Figure 26. Total Input Current vs Power Supply Voltage (Output Current = 0mA)

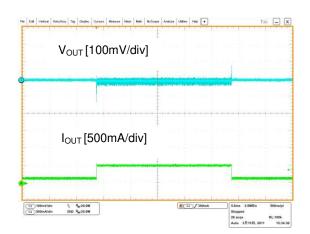

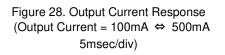

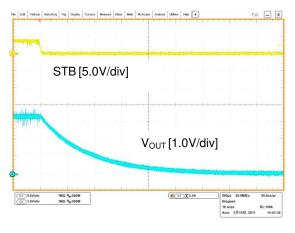

Figure 29. Soft Start Waveform (STB: Low to High 500µsec/div)

Figure 30. Discharge Waveform (STB: High to Low 500µsec/div)

Figure 32. Output Voltage vs Power Supply Voltage (Output Current = 500mA)

Figure 35. Total Input Current vs Power Supply Voltage (Output Current = 0mA)

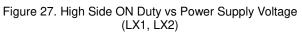

Figure 36. High Side ON Duty vs Power Supply Voltage (LX1, LX2)

# 6. Selection of Parts for Application

#### (1) Output Inductor

A shielded inductor that satisfies the current rating (current value, IPEAK as shown in the drawing below) and has a low DCR (direct current resistance component) is recommended. Inductor values affect output ripple current greatly. Ripple current can be reduced as the inductor L value becomes larger and the switching frequency becomes higher as shown in the equations below.

Figure 37. Ripple Current

(1)

; (in step-down mode)

$$I_{PEAK} = I_{OUT} + \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{2 \times L \times V_{IN} \times f} \qquad [A]$$

$$I_{PEAK} = \frac{I_{OUT} \times (V_{IN} + V_{OUT})}{2 \times Dc \times V_{IN} \times \eta} + \frac{[V_{IN} - V_{OUT}] \times V_{OUT} \times Dc}{L \times (V_{IN} + V_{OUT}) \times f} \qquad [A] \qquad ; \text{ (in buck-boost mode)} \qquad (2)$$

$$I_{PEAK} = \frac{I_{OUT} \times V_{OUT}}{V_{IN} \times \eta} + \frac{(V_{OUT} - V_{IN}) \times V_{IN}}{2 \times L \times V_{OUT} \times f} \qquad [A] \qquad \qquad ; \text{ (in step-up mode)} \qquad (3)$$

Where:

$\eta$  is the Efficiency (<0.96) Dc is the Cross Point Duty ( $\approx 0.91$ ) *f* is the Switching Frequency L is the Inductance

As a guide, output ripple current should be set at about 20% to 50% of the maximum output current.

(Note) Current flow that exceeds the coil rating brings the coil into magnetic saturation, which may lead to lower efficiency or output oscillation. Select an inductor with an adequate margin so that the peak current does not exceed the rated current of the coil.

(2) Output Capacitor

A ceramic capacitor with a low ESR is recommended at the output in order to reduce output ripple. There must be an adequate margin between the maximum rating and output voltage of the capacitor, taking the DC bias property into consideration. Output ripple voltage when ceramic capacitor is used is obtained by the following equation. Setting must be performed so that output ripple is within the allowable ripple voltage.

$$Vpp = \Delta I_L \times \frac{1}{2\pi \times f \times C_O} + \Delta I_L \times R_{ESR} \quad [V]$$

(4)

(3) Setting of Oscillation Frequency

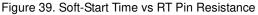

Oscillation frequency can be set using a resistance value connected to the RT pin (Pin 16). The oscillation frequency is set at 1 [MHz] when  $R_{RT}$  = 39 [KΩ], wherein frequency is inversely proportional to RT value. See Figure 38 for the relationship between RT [KΩ] and frequency. Soft-start time changes along with oscillation frequency. See Figure 39 for the relationship between RT [K $\Omega$ ] and soft-start time. Frequency is calculated by the following equation.

Figure 38. Oscillation Frequency vs RT Pin Resistance

Note: that the above example of frequency setting is just a design target value, and may differ from the actual equipment.

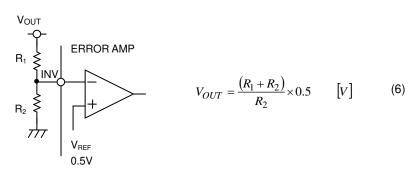

(4) Output Voltage Setting The internal reference voltage of the ERROR AMP is 0.5V. Output voltage should be obtained by referring to Equation (6) of Figure 40.

Figure 40. Setting of Feedback Resistance

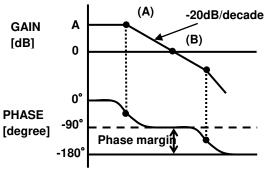

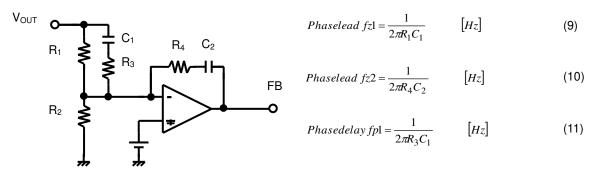

(5) Determination of Phase Compensation

The condition for feedback system stability under negative feedback is as follows:

Phase delay must be 135 °or lower when gain is 1 (0 dB) (Phase margin is 45° or higher). Since DCDC converter application is sampled according to the switching frequency, the Gain-BW of the whole system (frequency at which gain is 0dB) must be set to be equal to or lower than 1/5 of the switching frequency.

- (a) Phase delay must be 135 °or lower when gain is 1 (0 dB) (Phase margin is 45° or higher).

- (b) The Gain-BW at that time (frequency when gain is 0dB) must be equal to or lower than 1/5 of the switching frequency. For this reason, switching frequency must be increased to improve responsiveness.

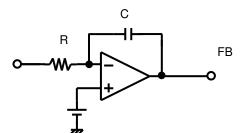

One of the points to secure stability by phase compensation is to cancel the second dimensional phase delay (-180°) generated by LC resonance of the second dimensional phase lead (i.e. put two phase leads). Since  $f_{GBW}$  is determined by the phase compensation capacitor attached to the error amplifier, the capacitor should be made larger when it is necessary to reduce  $f_{GBW}$ .

Figure 41. General Integrator

Figure 42. Frequency Property of Integrator

$$Point(A) \quad fp = \frac{1}{2\pi RCA} \qquad [Hz] \qquad (7)$$

$$Point(B) \quad f_{GBW} = \frac{1}{2\pi RC} \qquad [Hz] \qquad (8)$$

Error AMP is a low-pass filter because phase compensation by RC is performed as shown below. For DC/DC converter application, R is a parallel feedback resistance.

Phase compensation using an output capacitor with a low ESR such as ceramic capacitor is as follows:

When an output capacitor with a low ESR (several tens of  $m\Omega$ ) is used at the output, the secondary phase lead (two phase leads) must be put to cancel the secondary phase lead caused by LC. One example of phase compensation methods is as follows:

Figure 43. Example of Setting of Phase Compensation

LC resonance frequency (in step-down mode) =

$$\frac{1}{2\pi\sqrt{(LCout)}}$$

[Hz] (12)

LC resonance frequency (in step-up mode) =  $\frac{1-D}{2\pi\sqrt{(LCout)}}$  [Hz] (13)  $D:ON\frac{V_{OUT}-V_{IN}}{V_{OUT}}$

(13) Cout : OutputCapacitor

For setting of phase-lead frequency (9) and (10), both of them should be put near the LC resonance frequency (12) or (13).

When  $G_{BW}$  frequency becomes too high due to the secondary phase lead, it may be stabilized by setting the primary phase delay (11) to a frequency slightly higher than the LC resonance frequency by  $R_3$  to compensate it.

The  $f_{GBW}$  of the whole system (frequency at which gain is 0 dB) which set responsiveness of the DC/DC converter can be calculated by getting DC gain and the first dimension pole by equations below.

The responsiveness can be set high by setting the  $f_{GBW}$  to high frequency, but the whole system would be operated as bad oscillation if the  $f_{GBW}$  is set too high since there are not enough phase margin. The  $f_{GBW}$  must be equal to or lower than 1/5 of the switching frequency.

DC gain of the DC/DC converter can be expressed as below.

$$DC \ gain = \frac{A}{B} \times V_{REF} \times \frac{V_{IN}}{V_{OUT}}$$

(14)

DC gain (in step-down mode)

$$DC gain = \frac{A}{B} \times V_{REF} \times \frac{V_{OUT}}{V_{OUT} - V_{IN}}$$

(15)

$$DC gain = \frac{A}{B} \times V_{REF} \times \frac{V_{IN} + V_{OUT}}{2DC \times V_{OUT}}$$

(16)

The DC gain of the DC/DC converter declines by 20dB/decade from the first dimension pole which is as shown below.

The first dimension pole

$$fp = \frac{1}{R_1R_2}$$

[Hz]

$$fp = \frac{1}{2\pi \times A \times \frac{R_1 R_2}{R_1 + R_2} \times C_2} \qquad [H_z] \qquad (17)$$

[Hz]

(18)

where: A is the Error AMP gain= $100dB=10^5$

*B* is the oscillator amplification=0.4V

$V_{REF}$  is the reference voltage of Error AMP=0.5V

The f<sub>GBW</sub> at 0 dB under limitation of the band width of the DC gain at the first dimension pole point is as shown below.

Zero cross frequency

$$f_{GBW} = DC gain \times fp$$

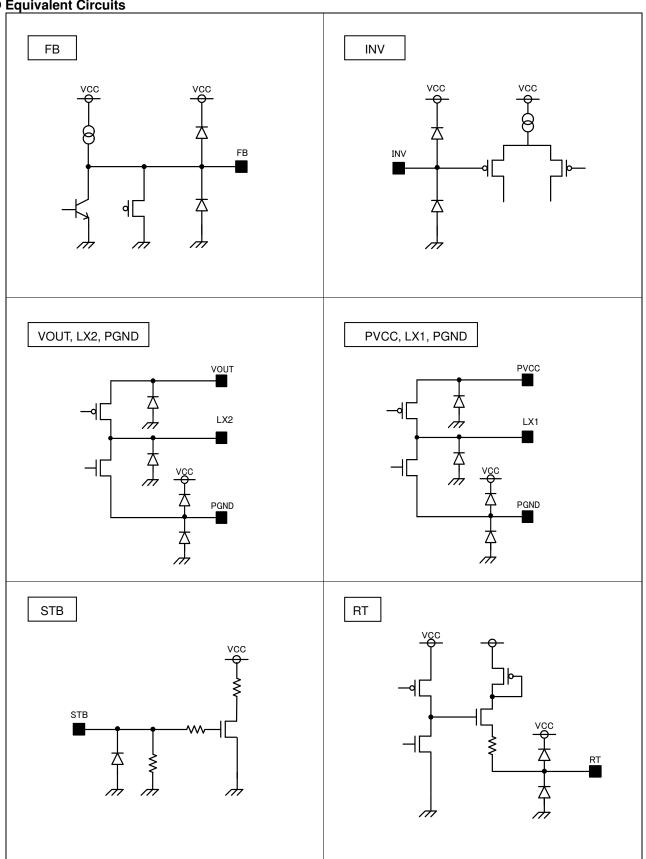

# I/O Equivalent Circuits

# **Operational Notes**

#### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply pins.

# 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

# 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

# 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

# 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the Pd rating.

# 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

#### 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

#### 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

#### 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

#### 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

# **Operational Notes – continued**

#### 11. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

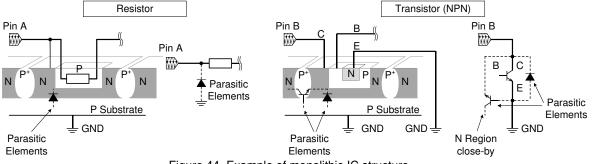

#### 12. Regarding the Input Pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode. When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

Figure 44. Example of monolithic IC structure

# 13. Thermal Shutdown Circuit(TSD)

This IC has a built-in thermal shutdown circuit that prevents heat damage to the IC. Normal operation should always be within the IC's power dissipation rating. If however the rating is exceeded for a continued period, the junction temperature (Tj) will rise which will activate the TSD circuit that will turn OFF all output pins. When the Tj falls below the TSD threshold, the circuits are automatically restored to normal operation.

Note that the TSD circuit operates in a situation that exceeds the absolute maximum ratings and therefore, under no circumstances, should the TSD circuit be used in a set design or for any purpose other than protecting the IC from heat damage.

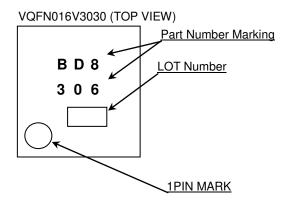

# **Marking Diagram**

# **Revision History**

| Date        | Revision | Changes                    |

|-------------|----------|----------------------------|

| 26.Nov.2014 | 001      | New Release                |

| 17.Feb.2015 | 002      | Correction of the writing. |