# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 12V to 76V input voltage range 3A output current 1ch Buck Converter Integrated FET

# BD9G341AEFJ

#### **General Description**

The BD9G341AEFJ is a buck switching regulator with integrated 150m $\Omega$  power MOSFET. Current mode architecture provides fast transient response and a simple phase compensation setup. The operating frequency is programmable from 50kHz to 750kHz. Additional protection features are included such as Over Current Protection, Thermal shutdown and Under voltage lockout. The under voltage lockout and hysteresis can be set by external resistor .

#### Features

- Wide input voltage range from 12V to 76V.

- Integrated 80V/3.5A/150mΩ NchFET.

- Current mode.

- Variable frequency from 50kHz to 750kHz.

- Accurate reference voltage.( 1.0 V±1.5 %).

- Precision ENUVLO threshold (±3%).

- Soft-start function

- OuA Standby current

Over Current Protection (OCP), Under Voltage Lockout(UVLO), Thermal-Shutdown(TSD),Over Voltage Protection (OVP) Thermally enhanced HTSOP-J8 package

#### Applications

- Industrial distributed power applications.

- Battery powered equipment.

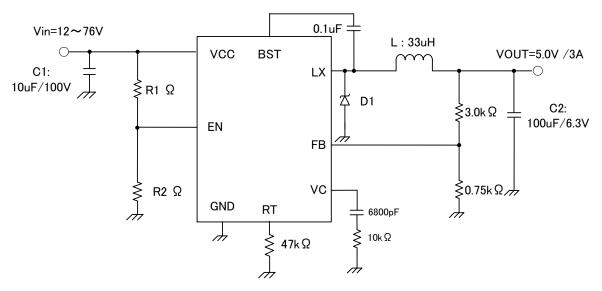

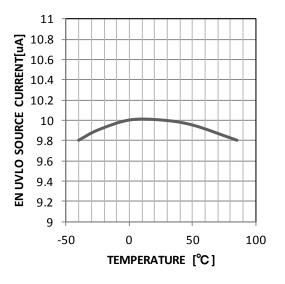

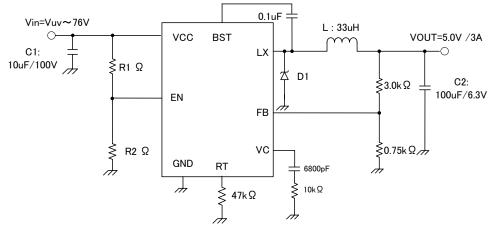

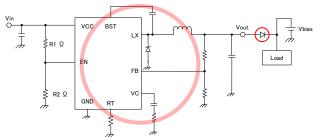

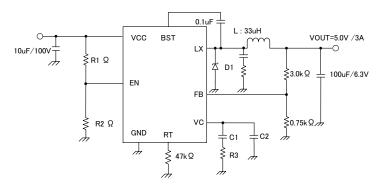

# **Typical Application Circuit**

#### Key specifications

| <br>                  |               |

|-----------------------|---------------|

| Input voltage         | 12 to 76[V]   |

| Ref voltage(Ta=25°C)  | ±1.5[%]       |

| (Ta=-40 to 85°C)      | ±2.0[%]       |

| Max output current    | 3 [A] (Max.)  |

| Operating Temperature | -40°C to 85°C |

|                       |               |

Max junction temperature

#### Package(s)

HTSOP-J8

4.90mm x 6.00mm x 1.00mm

150°C

Figure 1. Typical Application Schematic

OProduct structure : Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays

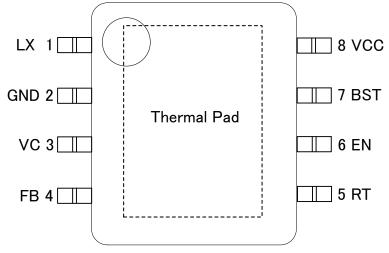

# **Pin Configuration**

Figure 2.Pin Configuration (TOP VIEW)

# **Pin Description**

| Pin No. | Pin Name    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | LX          | Switching node. It should be connected as near as possible to the schottky barrier diode, and inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2       | GND         | Ground pin. GND pattern is kept from the current line of input capacitor to output capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | VC          | The output of the internal error amplifier. The phase compensation implementation is connected between this pin to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 4       | FB          | Voltage feedback pin. This pin is the error-amp input with the DC voltage is set at 1.0V with feed-back operation.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5       | RT          | The internal oscillator frequency set pin. The internal oscillator is set with a single resistor connected between this pin and the GND pin. Recommended frequency range is 50kHz to 750kHz                                                                                                                                                                                                                                                                                                                                                             |

| 6       | EN          | Shutdown pin. If the voltage of this pin is below 1.3V,the regulator will be in a low power state. If the voltage of this pin is between 1.3V and 2.4V. The IC will be in standby mode. If the voltage of this pin is above 2.6V, the regulator is operational. An external voltage divider can be used to set under voltage threshold. If this pin is left open circuit, when converter is operating. This pin output 10uA source current. If this pin is left open circuit, a 10uA pull up current source configures the regulator fully operational. |

| 7       | BST         | Boost input for bootstrap capacitor<br>The external capacitor is required between the BST and the Lx pin.<br>A 0.1uF ceramic capacitor is recommended.                                                                                                                                                                                                                                                                                                                                                                                                  |

| 8       | VCC         | Input supply voltage pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -       | Thermal Pad | Connect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

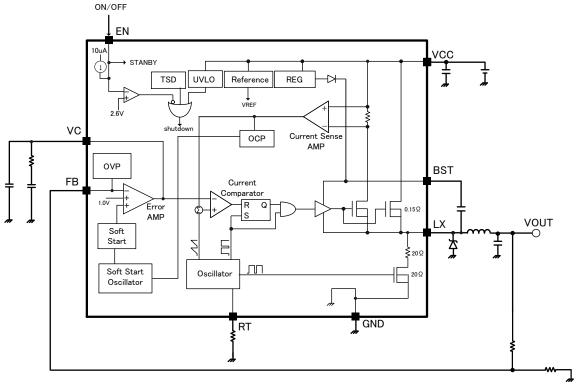

# Block Diagram

Figure 3.Block Diagram

# Description of Block(s)

- 1. Reference This block generates inner reference voltage.

- 2. REG

This block generates 8V reference voltage for bootstrap.

- 3. OSC

- This block generates inner CLK.

The internal oscillator is set with a single resistor connected between this pin and the GND pin. Recommended frequency range is 50 kHz to 750 kHz. If RT pin connect to 47kohm, frequency is set 200 kHz.

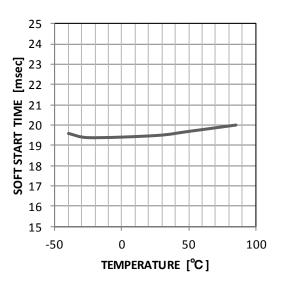

4. Soft Start

Soft Start of the output voltage of regulator prevents in-rush current during Start-up. Soft Start time is 20msec (typ)

5. ERROR AMP

This is an error amplifier what detects output signal, and outputs PWM control signal. Internal reference voltage is set to 1.0V.

6. ICOMP

This is a comparator that outputs PWM signal from current feed-back signal and error-amp output for current-mode.

7. Nch FET SW

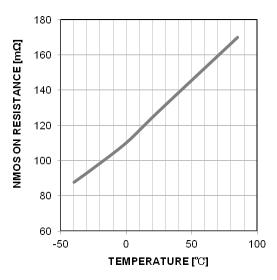

This is a  $80V/150m\Omega$ -Power Nch MOSFET SW that converts inductor current of DC/DC converter Since the current rating of this FET is 3.5A, it should be used within 3.5A including the DC current and ripple current of the coil.

8. UVLO

This is a Low Voltage Error Prevention Circuit.

This prevents internal circuit error during increase of Power supply Voltage and during decline of Power supply Voltage. It monitors VCC Pin Voltage and internal REG Voltage, When VCC Voltage becomes 11V and below, UVLO turns OFF all Output FET and turns OFF the DC/DC Comparator Output, and the Soft Start Circuit resets. Now this Threshold has Hysteresis of 200mV.

#### 9. EN

Shutdown function. If the voltage of this pin is below 1.3V, the regulator will be in a low power state. If the voltage of this pin is between 1.3V and 2.4V will be standby mode. If the voltage of this pin is above 2.6V, the regulator is operational. An external voltage divider can be used to set under voltage threshold. If this pin is left open circuit, when converter is operating. This pin output 10uA source current. If this pin is left open circuit, a 10uA pull up current source configures the regulator fully operational. When IC turn off, EN pin is pulled down by pull down resistor that sink above 10uA.

# 10. OCP

#### Over current protection

If the current of power MOSFET is over 6.0A (typ), this function reduces duty pulse –by- pulse and restricts the over current. If IC detects OCP 2 times sequentially, the device will stop and after 20 msec restart.

# 11. TSD

#### This is Thermal Shutdown Detection

When it detects an abnormal temperature exceeding Maximum Junction Temperature (Tj=150°C), it turns OFF all Output FETs, and turns OFF the DC/DC Comparator Output. When Temperature falls, and the IC automatically returns

# 12. OVP

Over voltage protection.

Output voltage is monitored with FB terminal, and output FET is turned off when it becomes 120% of set-point voltage.

# **Absolute Maximum Ratings**

| Item                  | Symbol | Ratings                 | Unit |

|-----------------------|--------|-------------------------|------|

| Maximum input voltage | VCC    | 80                      | V    |

| BST to GND            | VBST   | 85                      | V    |

| Maximum input current | Imax   | 3.5                     | А    |

| BST to LX             | ⊿VBST  | 15                      | V    |

| EN to GND             | VEN    | 80                      | V    |

| LX to GND             | VLX    | 80                      | V    |

| FB to GND             | VFB    | 7                       | V    |

| Power Dissipation     | Pd     | 3.76 <sup>(NOTE1)</sup> | W    |

| Operating Temperature | Topr   | -40 to +85              | °C   |

| Storage Temperature   | Tstg   | -55 to +150             | °C   |

| Junction Temperature  | Tjmax  | 150                     | °C   |

(NOTE1)During mounting of 70×70×1.6t mm 4layer board.Reduce by 5.4mW for every 1°C increase..(Above 25°C)

# Electrical Characteristics (Unless otherwise specified Ta=25°C, VCC=48V, Vo=5V, EN=3V, RT=47k $\Omega$ )

| Parameter                             |         | Limit  |       |         | Unit  | Q a va diiti a va |                        |

|---------------------------------------|---------|--------|-------|---------|-------|-------------------|------------------------|

|                                       |         | Symbol | Min   | Typ Max |       | Unit              | Condition              |

| [Circuit Current]                     |         |        |       | I.      | I     | 1                 | l                      |

| Stand-by current of VCC               |         | lst    | —     | 0       | 10    | μA                | VEN=0V                 |

| Circuit current of VCC                |         | lcc    | _     | 1.5     | 2.0   | mA                | FB=1.5V                |

| [Under Voltage Lock Out (UVLO         | ]       | 11     |       | 1       | 1     |                   |                        |

| Detect Voltage                        |         | Vccuv  | 10.4  | 11      | 11.6  | V                 |                        |

| Hysteresis width                      |         | Vuvhy  | _     | 200     | 300   | mV                |                        |

| [Error Amp]                           |         | 11     |       |         |       |                   |                        |

|                                       |         | VFBN   | 0.985 | 1.000   | 1.015 | V                 | Ta=25°C                |

| FB threshold voltage                  |         | VFBA   | 0.980 | 1.000   | 1.020 | V                 | Ta=-40 to 85°C         |

| FB Input bias current                 |         | IFB    | -1    | 0       | 1     | uA                | VFB=2.0V               |

| VC source current                     | Isource | 15     | 40    | 65      | uA    |                   |                        |

| VC sink current                       |         | Isink  | -65   | -40     | -15   | uA                |                        |

| Soft start time                       |         | Tsoft  | 15    | 20      | 25    | msec              |                        |

| Error amplifier DC gain               |         | AVEA   | _     | 10000   | _     | V/V               |                        |

| Trans conductance                     |         | GEA    | _     | 300     | —     | μA/V              |                        |

| [Current Sense Amp ]                  |         |        |       |         |       |                   |                        |

| VC to switch current trans conductant | Gcs     | _      | 10    | —       | A/V   |                   |                        |

| [OCP]                                 |         |        |       |         |       |                   |                        |

| Detect current                        |         | locp   | 3.5   | 6.0     | _     | Α                 |                        |

| OCP latch count                       |         | NOCP   | _     | 2       | _     | count             |                        |

| OCP latch hold time                   |         | TOCP   | 15    | 20      | 25    | msec              |                        |

| [Output]                              |         |        |       |         |       |                   |                        |

| Lx NMOS ON resistance                 |         | RonH   | _     | 150     | _     | mΩ                |                        |

| [CTL]                                 |         |        |       | 1       | 1     | 1                 | 1                      |

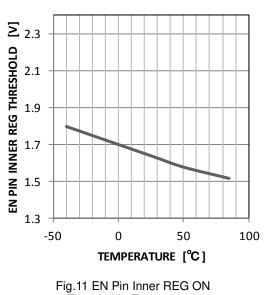

| EN Pin inner REG on voltage           | ON      | VENON  | 1.3   | _       | 2.4   | V                 |                        |

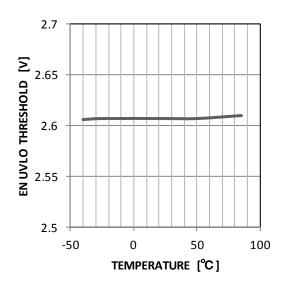

| EN Pin IC output on threshold         |         | Venuv  | 2.52  | 2.6     | 2.68  | V                 | IC on or off threshold |

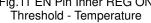

| EN pin                                |         | IEN    | 9.0   | 10.0    | 11.0  | μA                | VEN=3V                 |

| [Oscillator]                          |         | · _ ·  |       |         |       |                   |                        |

| Oscillator frequency                  |         | Fosc   | 180   | 200     | 220   | kHz               | RT:R=47kΩ              |

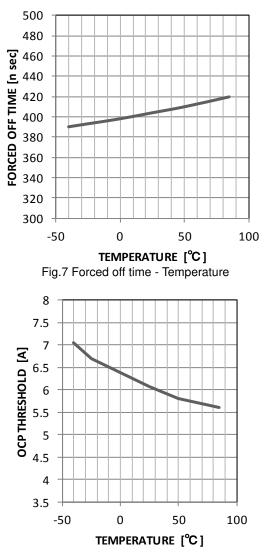

| Forced off time                       | Toff    |        |       | 500     | nsec  |                   |                        |

# Recommended Operating Ratings(Ta=25°C)

| ltem                 | Symbol | Rating                 |     |                        |      |  |

|----------------------|--------|------------------------|-----|------------------------|------|--|

| item                 | Symbol | Min                    | Тур | Max                    | Unit |  |

| Power Supply Voltage | VCC    | 12                     | _   | 76                     | V    |  |

| Output voltage       | VOUT   | 1.0 <sup>(Note2)</sup> | _   | VCC <sup>(Note3)</sup> | V    |  |

| Output current       | IOUT   | -                      | _   | 3.0                    | А    |  |

| Oscillator frequency | Fosc   | 50                     | —   | 750                    | kHz  |  |

(Note2) Restricted by minduty=f × MinOn Time (f :frequency)

If the voltage of Vcc×minduty [V] lower than 1V, this value is minimum output.

(Note3) Restricted by maxduty =1-f × forced off time

The maximum output is (Vcc- lout\*Ron) × maxduty

# **Typical Performance Characteristics**

(Unless otherwise specified, Ta=25°C, VCC=24V, VOUT=5V)

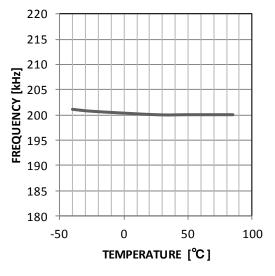

Fig.4 Oscillator Frequency - Temperature

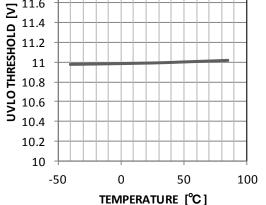

Fig.8 UVLO Threshold Voltage - Temperature

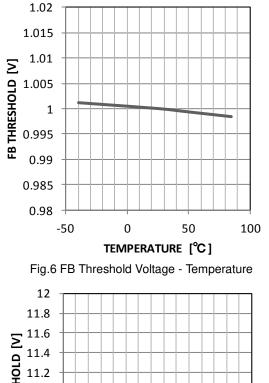

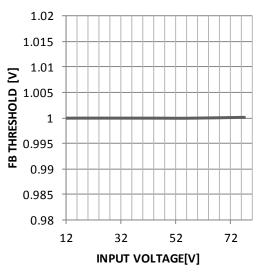

Fig.5 FB Threshold Voltage- Input Voltage

Fig.9 OCP Detect Current - Temperature

Fig.10 Soft Start Time - Temperature

Fig.12 ENUVLO Threshold - Temperature

Fig.14 NMOS ON Resistance -Temperature

Fig.13 EN Source Current - Temperature

# **Reference Characteristics of Typical Application Circuits**

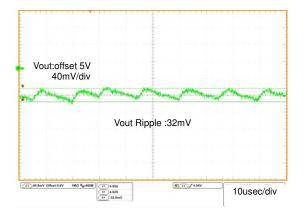

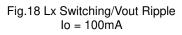

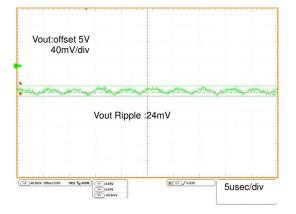

Vout=5V , f=200kHz

Fig.15 Efficiency - Output Current

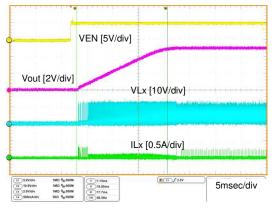

Fig.16 Start-up Characteristics

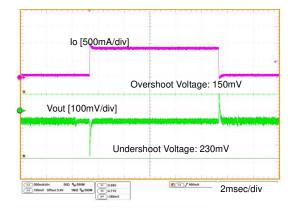

Fig.17 Load Response lout:100mA ⇔1A

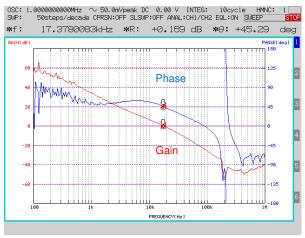

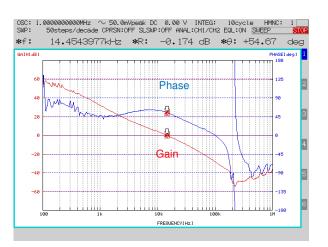

Fig.20 Frequency Response Io=100mA

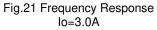

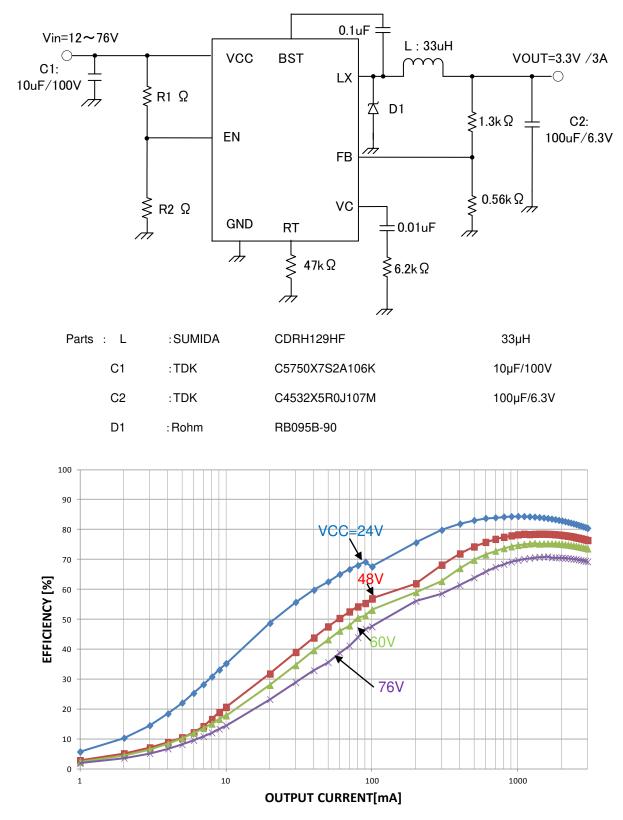

# **Reference Characteristics of Typical Application Circuits**

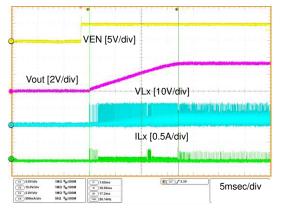

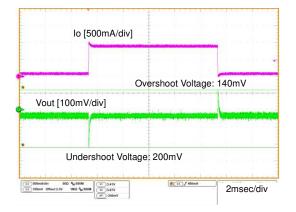

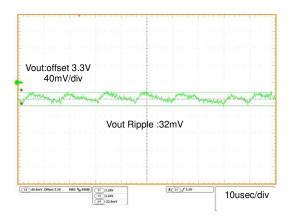

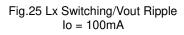

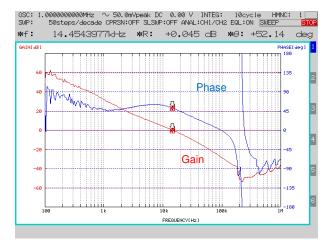

Vout=3.3V, f=200kHz

Fig.22 Efficiency – Output Current

Fig.23 Start-up Characteristics

Fig.24 Load Response lout:100mA ⇔1A

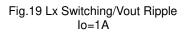

Fig.27 Frequency Response Io=100mA

Fig.28 Frequency Response Io=3A

#### **Detailed Description**

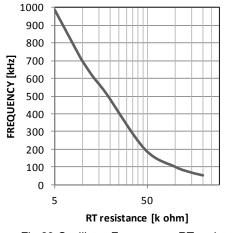

♦Frequency setting

Arbitrary internal oscillator frequency setup is possible by connecting RT resistance. Recommended frequency range is 50 kHz to 750 kHz.

For setting frequency f [Hz] , RT resistance is looked for using the following formula.

$$RT = \frac{\frac{1}{f} - 400 \times 10^{-9}}{96.48 \times 10^{-12}} [\Omega]$$

If setting frequency is 200kHz, RT is 47kΩ.

RT resistance is related to frequency as shown in Figure 26.

Fig.29 Oscillator Frequency - RT resistance

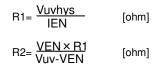

♦ External UVLO threshold

The high precision reset function is built in EN terminal of BD9G341AEFJ, and arbitrary low-voltage malfunction prevention setup is possible by connecting EN pin to resistance division of input voltage.

When you use, please set R1 and R2 to arbitrary voltage of IC turned on (Vuv) and hysteresis (Vuvhys) like below.

Fig.30 External UVLO setup

IEN:EN pin source current 10uA(typ) VEN: EN pin output on threshold 2.6V(typ) As an example in typical sample, When Vcc voltage which IC turned on 15V, Hysteresis width 1V, The resistance divider set to R1=100k $\Omega$ ,R2=20k $\Omega$ .

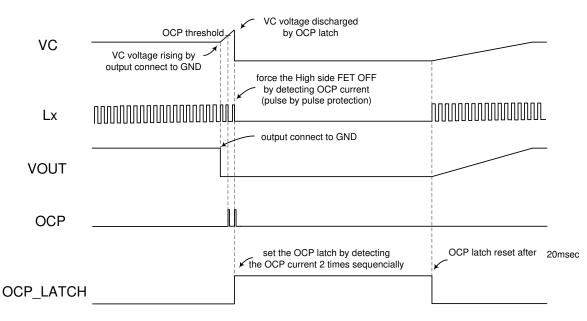

#### ♦OCP operation

The device has over current protection for protecting the FET from over current. To detect OCP 2 times sequentially, the device will stop and after 20msec restart.

Fig.31 Timing chart at OCP operation

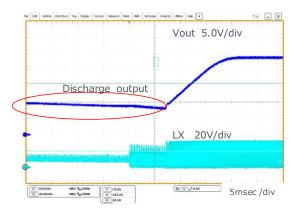

♦ start up with output pre-bias voltage

It starts in the state that the voltage remains in the output, in the cases that big capacitor is connected to output, IC discharge output voltage min 7.5V by FET ON 300nsec in period to charge bootstrap capacitor between BST to LX. When it is necessary to make a startup sequence, Please forcibly discharge the output voltage.

#### ♦ Restriction of output Bias application

The application that output connects to the other power supply is not recommended because the output voltage is not discharged in startup.

Figure 33. Output Bias NG application

When output connect to voltage supply, Please insert a diode to the IC output side.

Figure 34. Output Bias OK application

#### Application Components Selection Method

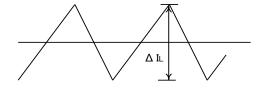

(1) Inductors

Something of the shield type that fulfills the current rating (Current value lpeak below), with low DCR is recommended. Value of Inductance influences Inductor Ripple Current and becomes the cause of Output Ripple. In the same way as the formula below, this Ripple Current can be made small for as big as the L value of Coil or as high as the Switching Frequency.

$$Ipeak = IOUT + \frac{\Delta IL}{2} \quad \cdots \quad (1)$$

$$\Delta IL = \frac{VCC - VOUT}{L} \times \frac{VOUT}{VCC} \times \frac{1}{f} \quad \cdots \quad (2)$$

<u>л тт</u>

(∠IL: Output Ripple Current, VCC: Input Voltage, VOUT: Output Voltage, f: Switching Frequency) For design value of Inductor Ripple Current, please carry out design tentatively with about 20% to 50% of Maximum Input Current.

In the BD9G341AEFJ, it is recommended the below series of  $4.7\mu$ H to  $33\mu$ H inductance value. Recommended Inductor:SUMIDA CDRH129HF Series

#### (2) Output Capacitor

In order for capacitor to be used in output to reduce output ripple, Low ceramic capacitor of ESR is recommended. Also, for capacitor rating, on top of putting into consideration DC Bias characteristics, please use something whose maximum rating has sufficient margin with respect to the Output Voltage. Output ripple voltage is looked for using the following formula.

$$\mathsf{V}_{\mathsf{PP}} = \Delta \mathsf{IL} \times \frac{1}{2\pi \times f \times COUT} + \Delta IL \times R_{ESR} \quad \cdots \quad (3)$$

Please design in a way that it is held within Capacity Ripple Voltage. In the BD9G341AEFJ, it is recommended a ceramic capacitor over  $10\mu$ F.

The maximum value of the output capacitor is limited by Start up Rush current The rush current is expressed by the following

(Rush Current )= (Current of the error amplifier reply delay) +  $\frac{C_{out} \times V_{out}}{T_{softstart_min}}$  +Ripple Current +Output Current

T T

(Out put Capacitor Charge current)

Current of the error amplifier reply delay depend on the phase compensation element and output capacitor. As output capacitor big, Rush Current grows big.

Please verify actual equipments that the Rush Current become smaller than OCP Threshold(min3.5A).

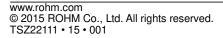

#### (3) Output voltage setting

The internal reference voltage of ERROR AMP is 1.0V. Output voltage is determined like (4) types.

$$VOUT = \frac{R1 + R2}{R2} \qquad \cdot \quad \cdot \quad (4)$$

(4) Bootstrap Capacitor

Please connect from 0.1uF (Laminate Ceramic Capacitor) between BST Pin and Lx Pins.

#### (5) Catch Diode

BD9G341AEFJ should be taken to connect external catch diode between Lx Pin and GND Pin. The diode require adherence to absolute maximum Ratings of application. Opposite direction voltage should be higher than maximum voltage of Lx Pin (VCCMAX + 0.5V). The peak current is required to be higher than IOUTMAX  $+ \angle IL$ .

#### (6) Input Capacitor

BD9G341AEFJ needs an input decoupling capacitor. It is recommended a low ceramic capacitor ESR over 4.7µF. Additionally, it should be located as close as possible.

Capacitor should be selected by maximum input voltage with input ripple voltage.

Input ripple voltage is calculated by using the following formula.

$$\Delta \text{VCC} = \frac{\text{IOUT}}{f \times \text{CVCC}} \times \frac{\text{VOUT}}{\text{VCC}} \times \left[1 - \frac{\text{VOUT}}{\text{VCC}}\right] \cdot \cdot \cdot (5)$$

#### CVCC: Input capacitor

RMS ripple current is calculated by using the following formula.

$$I_{CVCC} = IOUT \times \sqrt{\frac{VOUT}{VCC}} \times (1 - \frac{VOUT}{VCC}) \quad \cdot \cdot \cdot \quad (6)$$

If VCC=2VOUT, RMS ripple current is maximum. That is determined by (9) .

$$\mathsf{I}_{\mathsf{CVCC}_{\mathsf{max}}} = \frac{\mathsf{IOUT}}{2} \cdot \cdot \cdot (7)$$

(7) About Adjustment of DC/DC Comparator Frequency Characteristics Role of Phase compensation element C1, C2, R3

Fig.37 Feedback voltage resistance setting method

Stability and Responsiveness of Loop are controlled through VC Pin which is the output of Error Amp. The combination of zero and pole that determines Stability and Responsiveness is adjusted by the combination of resistor and capacitor that are connected in series to the VC Pin.

DC Gain of Voltage Return Loop can be calculated for using the following formula.

$$Adc = Rl \times G_{CS} \times A_{VEA} \times \frac{VFB}{VOUT} \quad \dots \quad (8)$$

Here, VFB is Feedback Voltage (1.0V).A<sub>EA</sub> is Voltage Gain of Error amplifier (typ: 80dB), Gcs is the Trans-conductance of Current Detect (typ: 10A/V), and RI is the Output Load Resistance value.

There are 2 important poles in the Control Loop of this DC/DC. The first occurs with/ through the output resistance of Phase compensation Capacitor (C1) and Error amplifier. The other one occurs with/through the Output Capacitor and Load Resistor. These poles appear in the frequency written below.

$$fp1 = \frac{G_{EA}}{2\pi \times C1 \times A_{VEA}} \quad \cdots \quad (9)$$

$$fp2 = \frac{1}{2\pi \times COUT \times Rl} \quad \cdots \quad (10)$$

Here,  $G_{EA}$  is the trans-conductance of Error amplifier (typ: 300  $\mu$ A/V).

Here, in this Control Loop, one zero becomes important. With the zero which occurs because of Phase compensation Capacitor C1 and Phase compensation Resistor R3, the Frequency below appears.

$$fz1 = \frac{1}{2\pi \times C1 \times R3} \quad \cdot \quad \cdot \quad (11)$$

Also, if Output Capacitor is big, and that ESR (RESR) is big, in this Control Loop, there are cases when it has an important, separate zero (ESR zero).

This ESR zero occurs due to ESR of Output Capacitor and Capacitance, and exists in the Frequency below.

$$fz_{ESR} = \frac{1}{2\pi \times \text{COUT} \times RESR} \cdot \cdot \cdot (12)$$

(ESR zero)

In this case, the 3<sup>rd</sup> pole determined with the 2<sup>nd</sup> Phase compensation Capacitor (C2) and Phase Correction Resistor (R3) is used in order to correct the ESR zero results in Loop Gain. This pole exists in the frequency shown below.

$$fp3 = \frac{1}{2\pi \times C2 \times R3}$$

· · · (13) (Pole that corrects ESR zero)

The target of Phase compensation design is to create a communication function in order to acquire necessary band and Phase margin.

Cross-over Frequency (band) at which Loop gain of Return Loop becomes "0" is important. When Cross-over Frequency becomes low, Power supply Fluctuation Response, Load Response, etc worsens. On the other hand, when Cross-over Frequency is too high, instability of the Loop can occur. Tentatively, Cross-over Frequency is targeted to be made 1/20 or below of Switching Frequency.

Selection method of Phase Compensation constant is shown below.

1. Phase Compensation Resistor (R3) is selected in order to set to the desired Cross-over Frequency. Calculation of RC is done using the formula below.

$$R3 = \frac{2\pi \times \text{COUT} \times \text{fc}}{G_{EA} \times G_{CS}} \times \frac{VOUT}{VFB} \quad \cdots \quad (14)$$

Here, fc is the desired Cross-over Frequency. It is made about 1/20 and below of the Normal Switching Frequency (fs).

2. Phase compensation Capacitor (C1) is selected in order to achieve the desired phase margin. In an application that has a representative Inductance value (about several 4.7µH to 33µH), by matching zero of compensation to 1/4 and below of the Cross-over Frequency, sufficient Phase margin can be acquired. C1 can be calculated using the following formula.

$$C1 > \frac{4}{2\pi \times R3 \times fc} \quad \cdots \quad (15)$$

Examination whether the second Phase compensation Capacitor C2 is necessary or not is done.

If the ESR zero of Output Capacitor exists in a place that is smaller than half of the Switching Frequency, a second Phase compensation Capacitor is necessary. In other words, it is the case wherein the formula below happens.

$$\frac{1}{2\pi \times COUT \times RESR} < \frac{fs}{2} \quad \cdots \quad (16)$$

In this case, add the second Phase compensation Capacitor C2, and match the frequency of the third pole to the Frequency fp3 of ESR zero.

$$C2 = \frac{COUT \times RESR}{R3} \quad \cdots \quad (17)$$

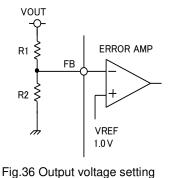

#### **PCB Layout**

Layout is a critical portion of good power supply design. There are several signals paths that conduct fast changing currents or voltages that can interact with stray inductance or parasitic capacitance to generate noise or degrade the power supplies performance. To help eliminate these problems, the VCC pin should be bypassed to ground with a low ESR ceramic bypass capacitor with B dielectric. Care should be taken to minimize the loop area formed by the bypass capacitor connections, the VCC pin, and the anode of the catch diode. See Fig.28 for a PCB layout example. The GND pin should be tied directly to the thermal pad under the IC and the thermal pad. In order to reduce the influence of the impedance and L of the parasitic, the high current line is thick and short.

Input decoupling capacitor should be located as close to the VCC pins

In order to minimize the parasitic capacitor and impedance of pattern, catch diode and inductance should be located as close to the Lx pin.

The thermal pad should be connected to any internal PCB ground planes using multiple VIAs directly under the IC.

GND feedback resistor, phase compensation element and RT resistor don't give the common impedance resistor against high current line.

# **Power Dissipation**

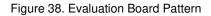

It is shown below reducing characteristics of power dissipation to mount 70mm×70mm×1.6mm<sup>t</sup> PCB Junction temperature must be designed not to exceed 150°C.

Figure 39. Power Dissipation Characteristic

#### **Power Dissipation Estimate**

The following formulas show how to estimate the device power dissipation under continuous mode operations. They should not be used if the device is working in the discontinuous conduction mode. The device power dissipation includes:

1) Conduction loss :  $Pcon = IOUT^2 \times RonH \times VOUT/VCC$

2) Switching loss :  $Psw = 16n \times VCC \times IOUT \times fsw$

3) Gate charge loss : Pgc =  $500p \times 7 \times 7 \times fsw$

4) Quiescent current loss : Pq = 1.5m × VCC

Where:

IOUT is the output current (A) , RonH is the on-resistance of the high-side MOSFET ( $\Omega$ ) , VOUT is the output voltage (V). VCC is the input voltage (V) fsw is the switching frequency (Hz).

Therefore

Power dissipation of IC is the sum of above dissipation.

Pd = Pcon + Psw + Pgc + Pq

For given Tj, Tj =Ta +  $\theta$ ja × Pd Where:

Pd is the total device power dissipation (W), Ta is the ambient temperature (°C)

Tj is the junction temperature (°C), θja is the thermal resistance of the package (°C)

# I/O Equivalent Schematic

|                  | Pin. Pin. Pin. Bin Equivalent Schematic |                          |            |      |                          |  |  |

|------------------|-----------------------------------------|--------------------------|------------|------|--------------------------|--|--|

| Pin.<br>No       | Pin.<br>Name                            | Pin Equivalent Schematic | Pin.<br>No | Name | Pin Equivalent Schematic |  |  |

| 1<br>2<br>7<br>8 | Lx<br>GND<br>BST<br>VCC                 | BST<br>VCC<br>LX<br>GND  | 5          | RT   |                          |  |  |

| 3                | vc                                      |                          | 6          | EN   |                          |  |  |

| 4                | FB                                      |                          |            |      |                          |  |  |

# **Operational Notes**

#### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply pins.

#### 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

#### 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition. OR

#### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

#### 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. The absolute maximum rating of the Pd stated in this specification is when the IC is mounted on a 70mm x 70mm x 1.6mm glass epoxy board. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the Pd rating.

#### 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

#### 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

#### 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

#### 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

#### 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

# **Operational Notes – continued**

#### 11. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

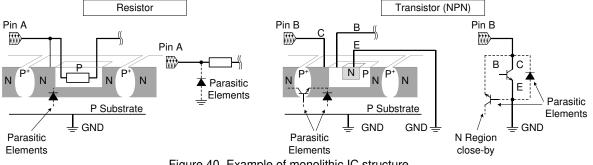

#### 12. Regarding the Input Pin of the IC

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode. When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

Figure 40. Example of monolithic IC structure

#### 13. Ceramic Capacitor

When using a ceramic capacitor, determine the dielectric constant considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

#### 14. Area of Safe Operation (ASO)

Operate the IC such that the output voltage, output current, and power dissipation are all within the Area of Safe Operation (ASO).

#### **Operational Notes – continued**

#### Thermal Shutdown Circuit(TSD)

This IC has a built-in thermal shutdown circuit that prevents heat damage to the IC. Normal operation should always be within the IC's power dissipation rating. If however the rating is exceeded for a continued period, the junction temperature (Tj) will rise which will activate the TSD circuit that will turn OFF all output pins. When the Tj falls below the TSD threshold, the circuits are automatically restored to normal operation.

Note that the TSD circuit operates in a situation that exceeds the absolute maximum ratings and therefore, under no circumstances, should the TSD circuit be used in a set design or for any purpose other than protecting the IC from heat damage.

#### 16. Over Current Protection Circuit (OCP)

This IC incorporates an integrated overcurrent protection circuit that is activated when the load is shorted. This protection circuit is effective in preventing damage due to sudden and unexpected incidents. However, the IC should not be used in applications characterized by continuous operation or transitioning of the protection circuit.

# **Ordering Information**

# **Marking Diagrams**

| HTSOP-J8                 |                                                                       |

|--------------------------|-----------------------------------------------------------------------|

| 4.90mm x 6.00mm x 1.00mm |                                                                       |

| Round                    | HTSOP-J8(TOP VIEW)       9 G 3 4 1 A       LOT Number       1PIN MARK |

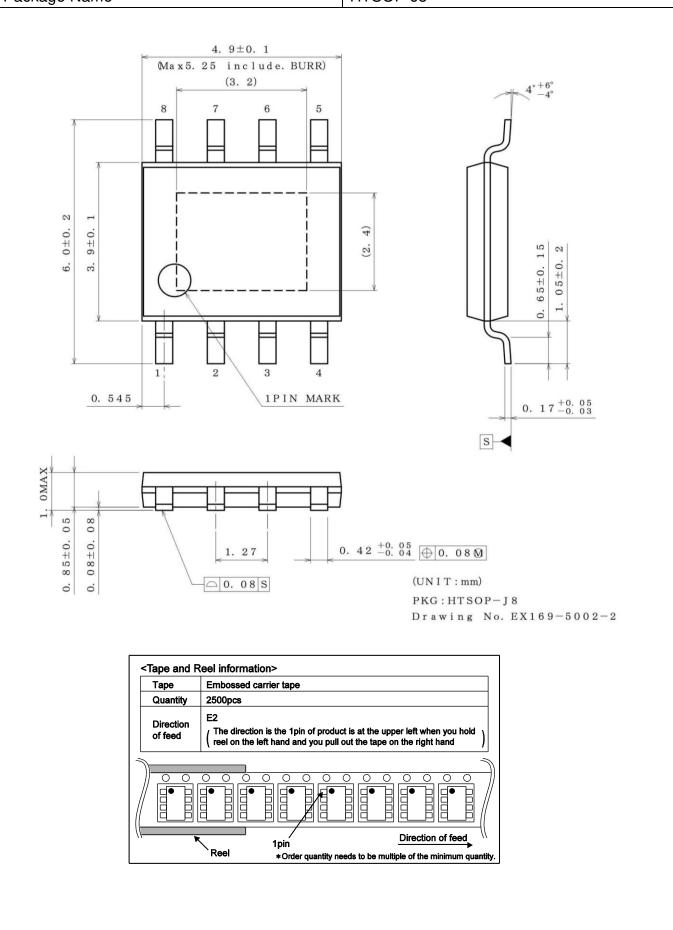

# Physical Dimension, Tape and Reel Information Package Name HTSOP-J8