Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### AC/DC Drivers

# **Quasi-Resonant Control type DC/DC Converter IC**

## **BM1Q011FJ**

#### General Description

The quasi-resonant controller typed AC/DC converter IC BM1Q011FJ provides an optimum system for all products that include an electrical outlet. Quasi-resonant operation enables soft switching and helps to keep EMI low.

With MOSFET for switching and current detection resistors as external devices, a higher degree of design freedom is achieved.

This IC built in HV starter circuit, it contributes to low consumption power and high speed start.

Because the burst mode is built-in and IC consumption current is low, stand-by power becomes very low.

Because BM1Q011FJ series built-in soft-start, burst mode, over current limiter which is cycle-by-cycle, over load protection, over voltage protection, CS Open Protection and so on, BM1Q011FJ are highly safety.

#### Key Specifications

Operating Power Supply Voltage Range:

VCC: 8.9V to 26.0V

VH: to 600V Normal: 0.60mA (Typ.)

**Operating Current:** Burst: 0.35mA(Typ.)

120kHz(Typ.) Max frequency: -40□ to +85□

Operate temperature range:

#### Features

- Quasi-resonant method

- Built-in 650V tolerate start circuit

- Low power at the light load (burst operation)

- Maximum frequency control (120kHz)

- Frequency reduction function

- AC voltage correction function

- VCC pin: under voltage protection

- VCC pin : over voltage protection

- Over-current protection (cycle-by-cycle)

- Output driver 12V clamp circuits

- Soft start function

- ZT trigger mask function

- Over Load protection [Auto-restart]

- CS pin open protection [Auto-restart]

## Package

SOP-J7S

6.00mm × 4.90mm × 1.65mm (Typ.) (Typ.) (Typ.)

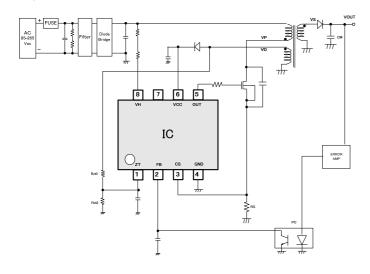

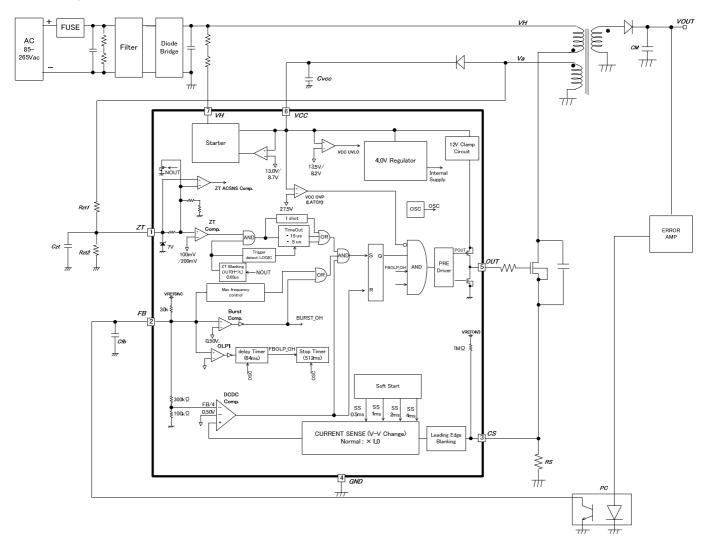

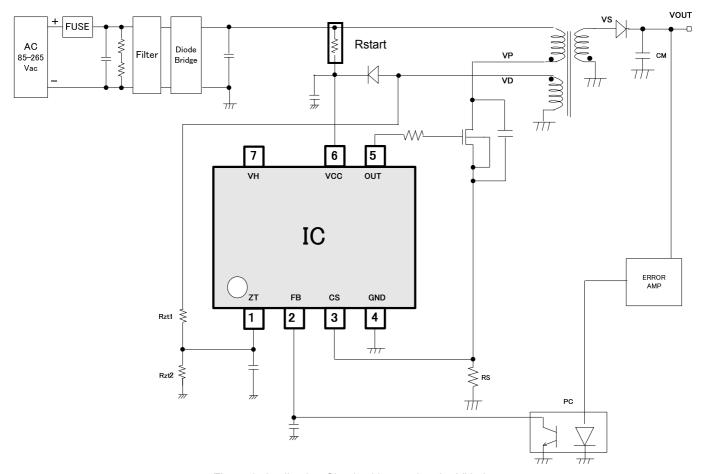

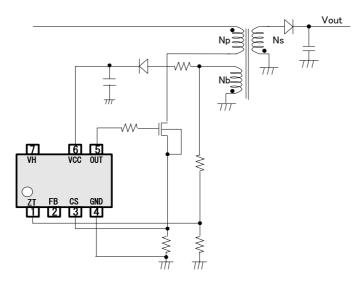

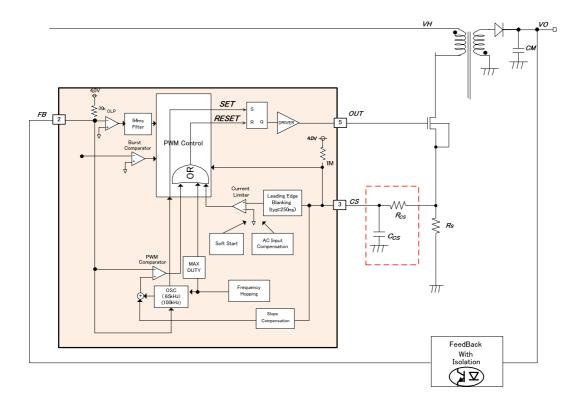

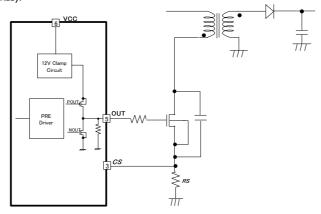

## Typical Application Circuit

Figure 1. Application Circuit

## Applications

Air conditioner, AC adapters, TV such as the products which need the outlet.

• Absolute Maximum Ratings (Ta=25°C)

| Item                      | Symbol            | Rating            | Unit | Condition    |

|---------------------------|-------------------|-------------------|------|--------------|

| Input voltage range 1     | Vmax1             | -0.3 ~ 30         | V    | VCC          |

| Input voltage range 2     | Vmax2             | -0.3 ~ 6.5        | V    | FB, CS       |

| Input voltage range 3     | Vmax3             | -0.3 ~ 7.0        | V    | ZT           |

| Input voltage range 4     | Vmax4             | -0.3 ~ 15         | V    | OUT          |

| Input voltage range 5     | Vmax5             | -0.3 ~ 650        | V    | VH           |

| OUT pin out peak current1 | I <sub>OH</sub>   | -0.5              | Α    |              |

| OUT pin out peak current2 | I <sub>OL</sub>   | 1.0               | Α    |              |

| ZT pin current1           | I <sub>SZT1</sub> | -3.0              | mA   |              |

| ZT pin current2           | I <sub>SZT2</sub> | 3.0               | mA   |              |

| CS pin current1           | I <sub>SCS1</sub> | -0.45             | mA   | Sink current |

| Allowable dissipation     | Pd                | 0.675 (Note1)     | W    |              |

| Operating temperature     | Topr              | -40 <b>~</b> +85  | °C   |              |

| Max junction temperature  | Tjmax             | 150               | °C   |              |

| Storage temperature range | Tstr              | -55 <b>∼</b> +150 | °C   |              |

(Note1) When mounted on 70 mm × 70 mm × 1.6 mm (glass epoxy on single-layer substrate).

Reduce to 5.4 mW/°C when Ta = 25°C or above.

## •Operating Conditions (Ta=25°C)

| Parameter                    | Symbol | Rating   | Unit | Conditions |

|------------------------------|--------|----------|------|------------|

| Power supply voltage range 1 | VCC    | 8.9~26.0 | V    | VCC        |

| Power supply voltage range 2 | VH     | 80~600   | V    | VH         |

•Electrical Characteristics (Unless otherwise noted, Ta = 25°C, VCC = 15 V)

| Parameter                         | Symbol              | S     | Specifications | ;     | Unit  | Conditions                                                 |

|-----------------------------------|---------------------|-------|----------------|-------|-------|------------------------------------------------------------|

| Parameter                         | Symbol              | MIN   | TYP            | MAX   | Offic | Conditions                                                 |

| [Circuit current]                 |                     |       |                |       |       |                                                            |

| Circuit current (ON)1             | I <sub>ON1</sub>    | -     | 600            | 1000  | uA    | FB=2.0V<br>(Switching operation)                           |

| Circuit current (ON)2             | I <sub>ON2</sub>    | -     | 350            | 450   | uA    | FB=0.5V<br>(Switching OFF)                                 |

| Circuit current(OFF)              | I <sub>OFF</sub>    | -     | -              | 25    | uA    | VCC=12V , VH: open<br>VCC UVLO = disable                   |

| [VH pin starter]                  |                     |       |                |       |       |                                                            |

| VH Start current 1                | I <sub>START1</sub> | 0.400 | 0.700          | 1.000 | mA    | VCC= 0V                                                    |

| VH Start current 2                | I <sub>START2</sub> | 1.00  | 3.00           | 6.00  | mA    | VCC=10V                                                    |

| VH OFF current                    | I <sub>START3</sub> | -     | 10             | 20    | uA    | After releasing VCCUVLO VH pin current                     |

| VH start current switched voltage | $V_{SC}$            | 0.400 | 0.800          | 1.400 | V     | VCC pin                                                    |

| [VCC pin protection]              |                     |       |                |       |       |                                                            |

| VCC UVLO voltage1                 | $V_{UVLO1}$         | 12.50 | 13.50          | 14.50 | V     | VCC rise                                                   |

| VCC UVLO voltage2                 | $V_{UVLO2}$         | 7.50  | 8.20           | 8.90  | V     | VCC fall                                                   |

| VCC UVLO hysteresis               | $V_{UVLO3}$         | -     | 5.30           | -     | V     | V <sub>UVLO3=</sub> V <sub>UVLO1</sub> -V <sub>UVLO2</sub> |

| VCC charge start voltage          | $V_{CHG1}$          | 7.70  | 8.70           | 9.70  | V     | Starter circuit                                            |

| VCC charge end voltage            | $V_{CHG2}$          | 12.00 | 13.00          | 14.00 | V     | Stop voltage from V <sub>CHG1</sub>                        |

| VCC OVP voltage1                  | $V_{OVP1}$          | 26.00 | 27.50          | 29.00 | V     | VCC rise                                                   |

| VCC OVP voltage2                  | $V_{\text{OVP2}}$   | -     | 23.50          | -     | V     | VCC fall                                                   |

| VCC OVP hysteresis                | $V_{OVP3}$          | •     | 4.00           | -     | V     |                                                            |

| [OUT pin]                         |                     |       |                |       |       |                                                            |

| OUT pin H voltage                 | Vouth               | 10.5  | 12.5           | 14.5  | V     | IO=-20mA, VCC=15V                                          |

| OUT pin L voltage                 | V <sub>OUTL</sub>   | -     | -              | 0.30  | V     | IO=+20mA                                                   |

| OUT pin Pull-down resistor        | R <sub>PDOUT</sub>  | 75    | 100            | 125   | kΩ    |                                                            |

•IC control unit Electrical Characteristics (Unless otherwise noted, Ta = 25°C, VCC = 15 V)

|                                           | ·                   | Specifications |        |        | Í    |                                    |

|-------------------------------------------|---------------------|----------------|--------|--------|------|------------------------------------|

| Parameter                                 | Symbol              | MIN            | TYP    | MAX    | Unit | Conditions                         |

| [ DC/DC converter unit (Turn-o            | ff\1                | 10             |        | 110.01 |      |                                    |

| =                                         |                     | 00.5           | 1 00 0 |        | 1    |                                    |

| Pull-up resistor of FB pin                | $R_{FB}$            | 22.5           | 30.0   | 37.5   | kΩ   |                                    |

| CS over current voltage 1A                | $V_{lim1A}$         | 0.475          | 0.500  | 0.525  | V    | FB=2.2V (ACSNS=L)                  |

| CS over current voltage 1B                | $V_{lim1B}$         | 0.310          | 0.350  | 0.390  | V    | FB=2.2V (ACSNS=H)                  |

| CS over current voltage 2A                | $V_{\text{lim2A}}$  | -              | 0.125  | -      | V    | FB=0.5V (ACSNS=L)                  |

| CS over current voltage 2B                | $V_{lim2B}$         | -              | 0.088  | -      | V    | FB=0.5V (ACSNS=H)                  |

| Voltage gain1 (ΔVFB/ΔVCS)                 | AV <sub>CS1</sub>   | 3.40           | 4.00   | 4.60   | V/V  | ACSNS=L                            |

| Voltage gain 2 (ΔVFB/ΔVCS)                | AV <sub>CS2</sub>   | 4.86           | 5.71   | 6.57   | V/V  | ACSNS=H                            |

| ZT current switched CS 1                  | I <sub>ZT1</sub>    | 0.93           | 1.00   | 1.07   | mΑ   |                                    |

| ZT current switched CS 2                  | I <sub>ZT2</sub>    | 0.82           | 0.90   | 0.98   | mA   |                                    |

| ZT current hysteresis switched CS voltage | I <sub>ZTHYS</sub>  | -              | 0.10   | -      | mA   |                                    |

| CS Leading Edge Blanking time             | $T_LEB$             | -              | 0.250  | -      | us   |                                    |

| Turn-off time                             | $T_{OFF}$           | -              | 0.150  | -      | us   |                                    |

| Minimum ON width                          | $T_{min}$           | -              | 0.400  | -      | us   | T <sub>LEB</sub> +T <sub>OFF</sub> |

| Maximum ON width                          | $T_{max}$           | 30.0           | 39.0   | 50.7   | us   |                                    |

| [ DC/DC converter unit (Turn-o            |                     |                |        |        |      |                                    |

| ZT input current 1                        | I <sub>ZT1</sub>    | 4              | 14     | 24     | uA   | OUT=L, ZT=4.65V                    |

| ZT input current 2                        | $I_{ZT2}$           | 6              | 16     | 26     | uA   | OUT=L, ZT=5.00V                    |

| ZT input current 3                        | $I_{ZT3}$           | 8              | 18     | 28     | uA   | OUT=L, ZT=5.35V                    |

| Max frequency 1                           | F <sub>SW1</sub>    | 108            | 120    | 132    | kHz  | FB=2.0V                            |

| Max frequency 2                           | F <sub>SW2</sub>    | -              | 30     | -      | kHz  | FB=0.5V                            |

| Frequency reduction start voltage         | $V_{FBSW1}$         | 1.10           | 1.25   | 1.40   | V    |                                    |

| Frequency reduction end voltage           | $V_{FBSW2}$         | 0.42           | 0.50   | 0.58   | V    |                                    |

| ZT comparator voltage1                    | $V_{ZT1}$           | 60             | 100    | 140    | mV   | ZT fall                            |

| ZT comparator voltage2                    | $V_{ZT2}$           | 120            | 200    | 280    | mV   | ZT rise                            |

| ZT trigger mask time                      | T <sub>ZTMASK</sub> | -              | 0.6    | -      | us   | In OUT H ->L, prevent noise        |

| ZT trigger Timeout1                       | T <sub>ZTOUT1</sub> | 10.5           | 15.0   | 19.5   | us   | Without bottom detection           |

| ZT trigger Timeout2                       | $T_{ZTOUT2}$        | 3.5            | 5.0    | 6.5    | us   | Count from final ZT trigger        |

| [DC/DC protection ]                       |                     |                |        |        |      |                                    |

| Soft start time1                          | T <sub>SS1</sub>    | 0.35           | 0.50   | 0.65   | ms   |                                    |

| Soft start time 2                         | $T_{SS2}$           | 0.70           | 1.00   | 1.30   | ms   |                                    |

| Soft start time 3                         | $T_{SS3}$           | 1.40           | 2.00   | 2.60   | ms   |                                    |

| Soft start time 4                         | $T_{SS4}$           | 2.80           | 4.00   | 5.20   | ms   |                                    |

| FB Burst voltage                          | $V_{BURST}$         | 0.42           | 0.50   | 0.58   | V    |                                    |

| FB OLP voltage a                          | $V_{FOLP1A}$        | 2.6            | 2.8    | 3.0    | V    | FBOLP detect (FB rise)             |

| FB OLP voltage b                          | $V_{FOLP1B}$        | -              | 2.6    | -      | V    | FBOLP detect (FB fall)             |

| FB OLP detection timer                    | $T_{FOLP}$          | 44.8           | 64     | 83.2   | ms   |                                    |

| FBOLP stop timer                          | T <sub>OLPST</sub>  | 358            | 512    | 666    | ms   |                                    |

| Latch mask time                           | T <sub>LATCH</sub>  | 50             | 100    | 200    | ms   |                                    |

<sup>\*</sup> Definition of ACSNS (L : ZT current < I<sub>ZT1</sub> 、H : ZT current > I<sub>ZT1</sub>)

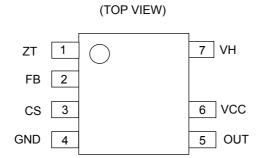

## •Pin Configuration

Table 1 Input-Output PIN Function

| NO  | Dia Marsa | 1/0 | Function                    | ESD | Diode |

|-----|-----------|-----|-----------------------------|-----|-------|

| NO. | Pin Name  | I/O | Function                    | VCC | GND   |

| 1   | ZT        | I   | Zero current detect pin     | -   | 0     |

| 2   | FB        | ı   | Feedback signal input pin   | 0   | 0     |

| 3   | CS        |     | Primary current sensing pin | 0   | 0     |

| 4   | GND       | I/O | GND pin                     | 0   | -     |

| 5   | OUT       | 0   | External MOS drive pin      | 0   | 0     |

| 6   | VCC       | I/O | Power supply pin            | -   | 0     |

| 7   | VH        | I   | Starter circuit pin         | -   | 0     |

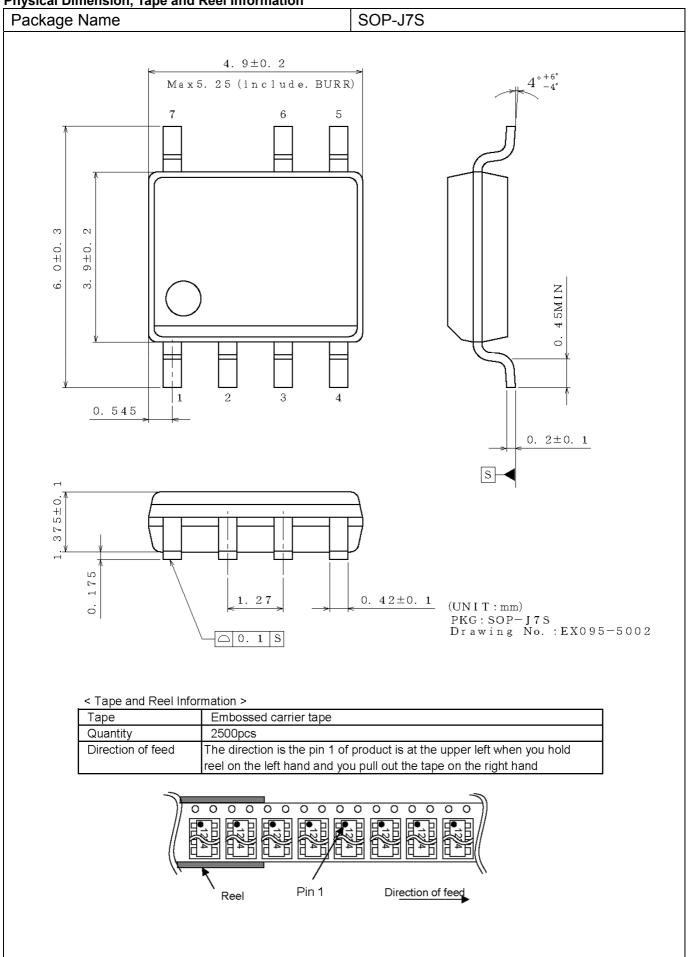

## • External Dimensions

Figure 2. SOP-J7 package external dimensions

## •I/O Equivalent Circuit Diagram

Figure 3. I/O Equivalent Circuit Diagram

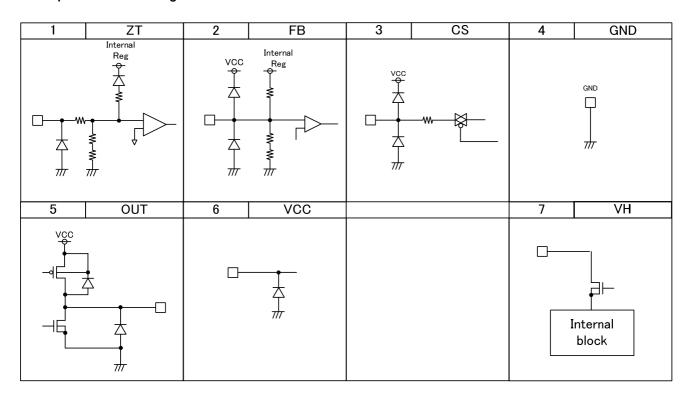

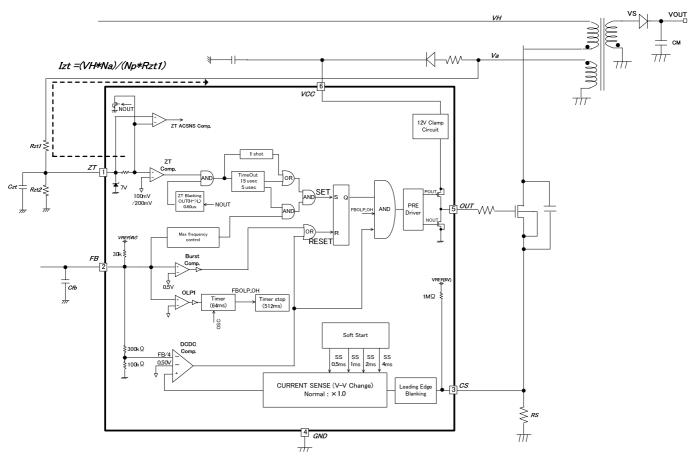

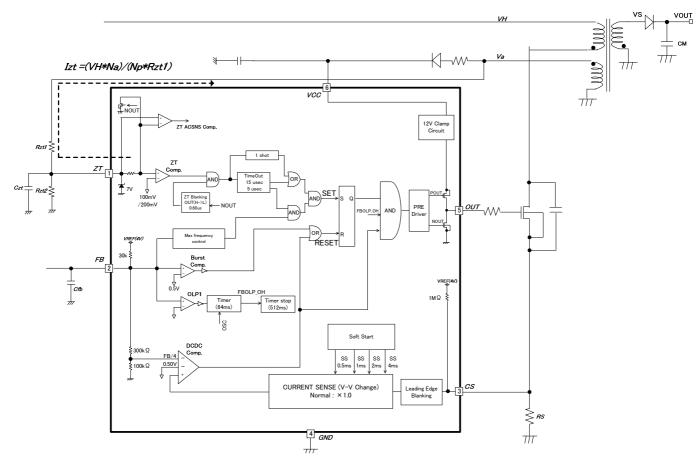

## •Block Diagram

Figure 4. Block Diagram

#### Description of Blocks

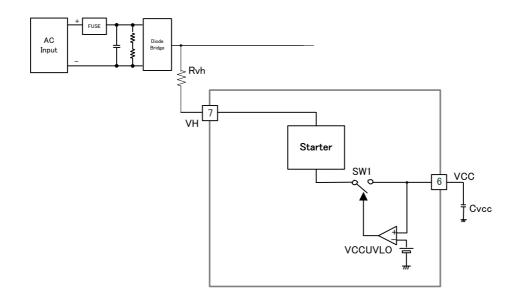

#### (1-1) Starter Circuit VH pin (7pin)

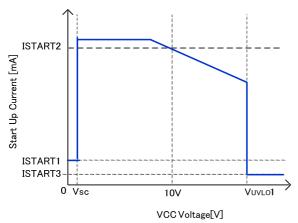

The IC builds in starter circuit (tolerates 650V) to VH pin (8pin). It enables to be low standby power and high speed starting. The operating current is shown in Figure 6. After starting the IC, the idling current I<sub>START3</sub>(typ=10uA) flows from VH voltage. The loss by the idling current is shown below.

ex) power consumption of starter circuit only

Vac=100V Power=100V\*\\sigma^210uA=1.41mW Vac=240V Power=240V\*\\sigma^210uA=3.38mW

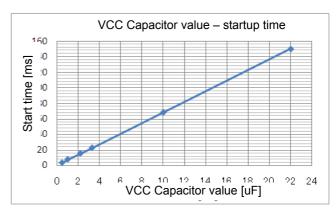

Starting time is decided by VH current and VCC pin capacitor value. The reference value of starting time is shown in Figure 7.

For example, VCC pin is charged within about 0.1 sec at  $C_{VCC}$ =10uF. When the VCC pin is shorted to GND, the current of ISTART1 flows to (shown in Figure 6). When the VH pin is shorted to GND, the large current flows from VH line to GND. To prevent this, it is needed to insert the resistor ( $5k\Omega\sim60k\Omega$ ) for limiting current between the VH line and the VH pin. When VH pin is shorted to GND, the power of VH<sup>2</sup>/R<sub>VH</sub> is applied to this resistor, so please decide the resistor value depending on specifications after having confirmed allowable electricity.

Figure 5. Starter Block Diagram

Figure 6. Start-up Current vs. VCC Voltage

\*The start up current is flown from VH pin (7Pin).

Figure 7. Start-up Time (example)

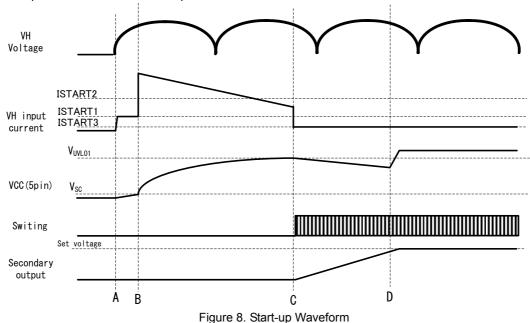

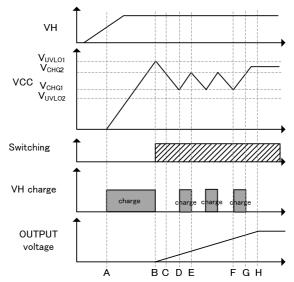

Figure 8 shows operation waveform of start-up.

protection function.

- A: By inserting to outlet, the VH voltage applies. From this moment, charging to VCC pin starts from the VH pin through starter circuit. At the time, due to VCC < V<sub>SC</sub> (typ=0.8V), VH input current is limited to ISTART1 by the VCC pin short

- B: Because of VCC voltage > V<sub>SC</sub> (typ=0.8V), VCC short protection is released and the current of the VH input current waveform flows from VH pin.

- C: Because of VCC voltage >  $V_{UVLO1}$  (typ=13.5V), the start-up circuit stops and VH input current is limited to ISTART3 (typ=10uA) only. Furthermore, for starting switching operation secondary output starts to rise however the VCC pin voltage lowers because the Secondary output is low yet. The falling rate of the VCC is determined by the VCC pin capacitance, the consumption current of the IC and the load current that flows from the VCC pin. (V/t = Cvcc/Icc)

- D: Because secondary output has risen to specific voltage, the VCC pin is applied from the auxiliary winding and VCC voltage is stabilized.

#### (1-2) a case without using VH pin

This IC is also possible to start by connecting the start-up resistor to the VCC pin in the open start-up circuit (650V breakdown voltage) of the VH pin. The structure that does not use the recharge function is shown in Figure 9.At start-up (before VCC VULO released), please be careful to set the start-up resistor Rstart shown in Figure 9, because the consumption current I<sub>OFF</sub> (Max=25uA) flows from VCC pin (6pin).

Figure 9. Application Circuit without using the VH pin

#### ·How to set the start-up resistance

Start-up resistor Rstart shown in Figure 9 is necessary for the IC to start if you do not use the VH pin. If the value of Rstart is small, the standby power is increased and the start-up time becomes shorter. Adversely, if the value of Rstart is big, the standby power is reduced and start-up time becomes longer. When the VCC voltage=12V, the standby current  $I_{OFF}$  is 25µA (max) and the VCC UVLO voltage  $V_{UVLO1}$  is 14.5V (max).

ex) The example of start-up resistor Rstart setting Rstart = (VH min -  $V_{UVLO1}(max)$ ) /  $I_{OFF}(max)$  In Vac=100V, if margin is -30%, VH min=100× $\sqrt{2}$ ×0.7=99V  $V_{UVLO1}(max)$ =14.5V, so Rstart = (99-14.5) / 25 $\mu$ A=3.38M $\Omega$

For an example, with a sufficient margin to  $3.38M\Omega$ , the Rstart is set to  $2.0M\Omega$ .In case of AC100V, Power consumption in Rstart is below.

Pd (Rstart) =  $(VH-VCC)^2/Rstart = (141V-14.5V)^2/2.0M = 8.00mW$

Pd in using start-up resistor is more than in using VH pin. However, about the value of VCC pin capacitance and VCC start-up resistor, please confirm by performing the evaluation of the actual application.

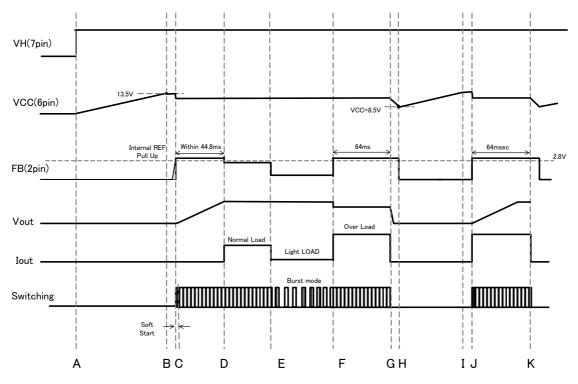

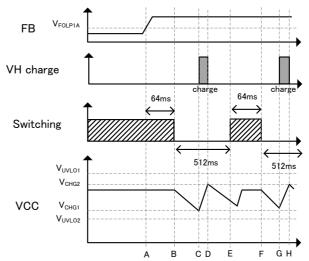

## (2) Start Sequence (Soft start, Light load operation, Auto recovery in over load protection)

The start sequence of IC is shown in Figure 10. About each detail, explain in each section.

Figure 10. Start Sequence Time Chart

- A: The voltage is applied to the Input voltage VH pin (7pin).

- B : VCC pin (6pin) voltage rise, when VCC> $V_{UVLO1}$ (typ=13.5V), IC starts operating. In the case that protection function is normal condition, the IC starts switching operation. Then the VCC pin voltage drops absolutely by the VCC pin consumption current. In case of the VCC<  $V_{CHG1}$ (typ =8.7V), the starting circuit operates and charges the VCC. After starting to charge, it lasts charging until VCC>  $V_{CHG1}$  (typ =13.0V)

- C: The IC has a soft start function which regulates the voltage level at the CS pin to prevent a rise in voltage and current.

- D: When the switching operation starts, the secondary output voltage VOUT rises. After starting switching, it is necessary to set the output voltage to stable the due output voltage within the T<sub>FOLP</sub> (typ=64ms) period.

- E: At light load condition, the burst operation starts for keeping power consumption low.

- F: When it is heavy load, FB pin voltage (2pin) is larger than V<sub>FOLP1A</sub> (typ=2.8V), because output voltage is down.G: When the condition that FB pin (2pin) voltage is more than V<sub>FOLP1A</sub> (typ=2.8V) continues for T<sub>FOLP</sub> (64ms typ), the switching is stopped by the over load protection for T<sub>OLPST</sub> (typ=512ms). When the FB pin (2pin) voltage becomes to be lower than V<sub>FOLP1B</sub>, the timer internal the IC T<sub>FOLP</sub> (64ms typ) is reset.

- H: When VCC voltage (6pin) is less than V<sub>CHG1</sub> (typ=8.7V), the starter circuit starts to operate and charge the VCC pin (6pin) .

- I: When VCC voltage (6pin) is more than V<sub>CHG2</sub> (typ =13.0V), the starter circuit stops to charge to the VCC pin (6pin).

- J: Same as F.

- K: Same as G.

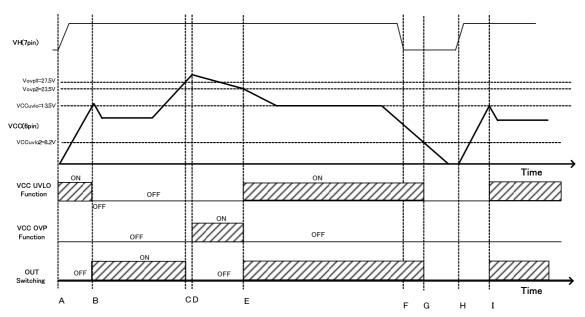

#### (3) VCC pin (6pin) Protection Function

The IC built in VCC UVLO (Under Voltage Protection) function, VCC OVP (Over Voltage Protection) function and VCC charge function which operates when the VCC voltage drops.VCC UVLO and VCC OVP are the function that prevents MOSFET for switching from destroying at the VCC voltage low or high conditions. And the VCC charge function charges in high voltage line from starting circuits and stabilize the secondary output voltage.

## (3-1) VCC UVLO / VCC OVP Function

VCC UVLO is the function monitors the VCC pin voltage and switches ON/OFF of the IC. This function has a voltage hysteresis and it is auto recovery protection type. VCC OVP is also the type. Refer to the operation figure 11. The auto recovery protection function of this IC's VCC OVP stops the switching when the condition that the VCC pin (6pin) voltage is more than  $V_{\text{OVP1}}$  (typ=27.5V) continues for more than mask time TSTOP (typ=100us). And it restarts switching when the condition that VCC pin (6pin) voltage is lower than  $V_{\text{OVP2}}$  (typ=23.5V).

Figure 11. VCC UVLO / OVP Timing Chart

- A: The VH (7pin) voltage is applied, and the VCC (6pin) voltage starts rising.

- B: The VCC pin (6pin) voltage > V<sub>UVLO1</sub>, the VCC UVLO function is released and DC/DC operation starts.

- C: The VCC pin (6pin) voltage >V<sub>OVP1</sub>, VCCOVP detects the over-voltage in the IC.

- D: When the condition that the VCC (6pin) voltage is more than  $V_{OVP1}$  continues for  $T_{STOP}$  (typ =100us), switching is stopped by the VCCOVP function.

- E: The VCC (6pin) voltage < V<sub>CHG1</sub>, the VCCOVP function is released and the operation is restarted.

- F: The high voltage line VH drops.

- G: The VCC voltage < V<sub>UVLO2</sub>, VCCUVLO function starts operation and the switching is stopped.

- H: The high voltage line VH is applied.

- I: The VCC pin (6pin) becomes more than V<sub>UVLO1</sub> and VCCUVLO function operates.

#### Regarding capacitor value of VCC pin

For stable operation of the IC, please set the capacitor value to 1uF or higher of the VCC pin. When the VCC capacitor terminal is too large, the response of the VCC pin to the Secondary output is slows down. Additionally, if the degree of the transformer coupling is low, since a large surge occurs to the VCC pin, the IC may be destroyed. In this case, it is necessary that a resistor which is from  $10\Omega$  to  $100\Omega$  is attached to the path between the capacitor and diode at the back of the auxiliary winding or the capacitor of the VCC pin is increased. And the fixed number is has to be set the VCC pin surge voltage not to exceed the absolute maximum rating of the VCC pin by evaluating the waveform of the VCC pin.

#### Regarding VCC OVP voltage protection setting method in case of rising Vout (secondary output)

The VCC pin voltage is determined by the transformer ratio (Np:Ns) and Vout (Secondary output). Therefore, when the Secondary output becomes large, it is possible to protect the IC by VCCOVP. Setting method of VCCOVP protection is shown below.

Figure 12. How to Set VCCOVP

The VCC voltage is determined by the formula below.

VCC voltage = (Vout-VFs)×Nb/Ns -VFb

(Vout: Secondary output, Nb: Number of auxiliary winding, Ns: Number of secondary winding

VFx: Secondary diode VF, VFb: auxiliary winding diode VF)

If you want to apply protection when it becomes Secondary output  $\times$  1.3, please set the number of turns to be the next formula. 1.3  $\times$  (Vout  $\times$  (Nb/Ns) - VF) > VOVP1

Because VCCOVP protection has a blanking time of  $T_{STOP}$  (typ = 100us), it is not detected for momentary surge noise of the VCC pin. However, VCCOVP is detected when the VCC voltage becomes higher than  $V_{OVP1}$  for the period of more than  $V_{STOP}$ . So it is necessary to check in application evaluation when you set VCCOVP.

#### (3-2) VCC Recharge Function

After the VCC (6pin) voltage >  $V_{UVLO1}$ , the IC start to operate. After that, when the VCC pin voltage <  $V_{CHG1}$ , VCC charge function operates. Then the IC charges the VCC pin (6pin) from the VH pin through the starting circuits. This operation prevents the IC from the VCC starting errors. After the VCC pin (6pin) is charged and rise to more than  $V_{CHG2}$ , the charging is stopped. This operation is shown to Figure 13.

Figure 13. VCC pin Charge Operation

- A: As the VH pin voltage (7pin) rises, the VCC pin (6pin) is started to charge by the VCC charge function.

- B: The VCC pin (6pin) voltage > V<sub>UVLO1</sub>, VCC UVLO function is released, VCC charge function is stopped, DC/DC operation start.

- C: The VCC pin (6pin) voltage is dropped because OUTPUT voltage is low at starting.

- D: The VCC pin (6pin) voltage < V<sub>CHG1</sub>, the VCC charge function operates and VCC pin (6pin) voltage rises.

- E: The VCC pin (6pin) voltage > V<sub>CHG2</sub>, the VCC charge function stops.

- F: The VCC pin (6pin) voltage < V<sub>CHG1</sub>, the VCC charge function operates and VCC pin (6pin) voltage rises.

- G: The VCC pin (6pin) voltage >  $V_{\text{CHG2}}$ , the VCC charge function stops.

- H: The output voltage stops stating operation and the VCC pin is charged from auxiliary winding. Then the VCC pin (6pin) becomes to be stable.

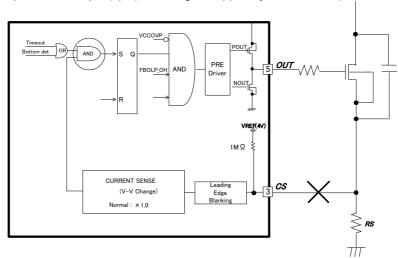

## (4) DC/DC Driver

The IC operates in PFM (Pulse Frequency Modulation) mode method. By monitoring the FB pin (2pin), ZT pin (1pin) and CS pin(3pin), the IC supply optimum system for DC/DC operation. The IC controls ON width (Turn Off) of the switching MOSFET by the FB pin (2pin) and CS pin (3pin). The IC also does OFF width (Turn ON) by the ZT pin (1pin). The detail is shown below.

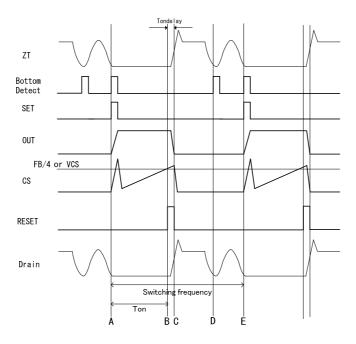

## (4-1) QR-basic Operations

The QR basic block diagram and the basic operation are shown in Figure 14 and 15.

Figure 14. DC/DC Operation Block

Figure 15. QR Basic Operation

#### **About Figure 15**

- A: The IC detects a bottom signal and outputs SET signal. Then it turns ON the MOSFET. At this moment, a noise occurs at the CS pin because the capacitor between DRAIN and SORCE of MOSFET is discharged. This noise is called Leading Edge. And this IC has an internal filter for this noise (Refer to (4-3)). This filter and delay time make the minimum pulse of the IC 400ns (typ). After that, the current flows to the MOSFET and the voltage (Vcs=Rs\*Ip) applies to the CS pin.

- B: If the CS pin voltage rises to more than the FB pin voltage / Gain (typ=4) or over current detection voltage  $V_{CS}$  (typ=0.5V), the IC outputs the RESET signal and turns OUT off.

- C: It takes delay time Tondelay until the IC turn off from point B. For this time, the maximum electric power increases depending the AC voltage. This IC has the function that restricts the increment (Refer to (4-4)).

- D: The DRAIN voltage drops because the energy stocked in transformer is discharged to secondary side and there is no energy in it. At this moment, the IC detects a bottom signal but the signal is ignored not to exceed the maximum frequency. Then the auto vibration of the transformer Lp and MOSFET Cds (the capacitor between the DRAIN and SORCE) starts.

- E: After the specific period passes from the point A and the time which determined by the maximum frequency also passes, the SET signal is outputs if the IC detects a bottom and turns MOSFET on.

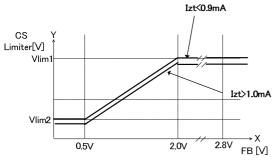

#### (4-2) Determination of ON Width (Turn OFF)

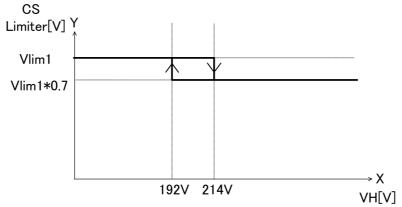

ON width is controlled by FB (2pin) and CS (3pin).By comparison between the FB pin voltage divided by AVcs (typ=4) and CS pin voltage, the IC decides ON width. Besides, by comparison with Vlim1 (typ=0.5V) voltage which is generated in the IC, the CS comparator level is changed lineally to be shown in Figure 16 (the bottom side). Then the maximum frequency also changes. The CS pin (3pin) is shared with over current limiter circuit by pulse. The IC changes the maximum blanking frequency and over current limiter level by the FB pin (2pin) voltage.

mode1: Burst operation

mode2: Frequency reduction operation (reduce max frequency)

mode3: Max frequency operation (operate at maximum frequency)

mode4: Over load operation (stop the pulse operation detecting the over load condition)

Figure 16. relation of the FB pin, over current limiter and maximum frequency

The ON width Ton is decided by the CS Limiter level (VCS).

Ton = (Lp\*Vcs) / (Vin\*RS)

Lp: primary inductance value, Vin: VH voltage (Figure 14), RS: Sense resistor (Figure 14)

To adjust over current limiter level, the IC switches the soft start function and over current protection at input voltage. In this case, the value of Vlim1 and Vlim2 is changed as below.

Table 2. Over current protection voltage Detail

| Soft start  | AC=1          | 00V          | AC=230V      |              |  |

|-------------|---------------|--------------|--------------|--------------|--|

| Soil start  | Vlim1         | Vlim2        | Vlim1        | Vlim2        |  |

| start~0.5ms | 0.063V (12%)  | 0.016V (3%)  | 0.044V (10%) | 0.011V (2%)  |  |

| 0.5ms~1ms   | 0.125V (25%)  | 0.032V (6%)  | 0.088V (20%) | 0.022V (4%)  |  |

| 1ms~2ms     | 0.250V (50%)  | 0.063V (12%) | 0.175V (40%) | 0.044V (9%)  |  |

| 2ms~4ms     | 0.375V (75%)  | 0.094V (19%) | 0.263V (60%) | 0.066V (13%) |  |

| 4ms∼        | 0.500V (100%) | 0.125V (25%) | 0.350V (70%) | 0.088V (18%) |  |

<sup>\*(</sup>percent) is shown the comparative related value with Vlim1(typ=0.5V)in normal operation.

The reason that distinguish between AC100V and AC230V is by CS over current protection voltage switch function which is shown to (4-4).

#### (4-3) LEB(Leading Edge Blanking) Function

When a MOSFET for switching is turned ON, a surge current occurs in cause of a capacitance or rush current. Therefore, when the CS (3pin) voltage rises temporarily, an over current limiter circuit may miss detections. To prevent miss detections, the IC build-in blanking function which mask for  $T_{LEB}$  (typ=250ns) from switching the OUT pin(5pin) from L to H. This blanking function enables to reduce noise filter of the CS pin (3pin). However, when the CS pin noise does not converge less than 250ns, it is needed to attach RC filter to the CS pin shown in Figure 17. Then, a delay time occurs to the CS pin detection by RC filter. Also, even if the filter in not attached, it is recommended that it is attached an Rcs resistor to the CS pin as a surge provision. Rcs recommended resistor value is about  $1k\Omega$ . If you would like to filter, please adjust in Ccs for this resistor.

Figure 17. a circuit surrounding the CS pin

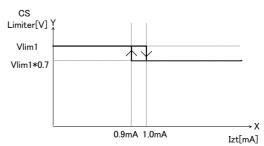

#### (4-4) CS over Current Protection Switching Function

If the input voltage (VH) becomes higher, the slope of L current raises. The switching has a constant delay time, so the maximum allowable power increases for a constant over current limiter depending AC voltage. For this countermeasure, this IC switches the internal over current protection function monitoring the input voltage. In case of high voltage (AC230V), it is needed to set the over current comparator to normal 0.7 times. The IC detects by monitoring the ZT inflow current and switching. When the MOSFET is turns ON, Va becomes minus voltage depending on the input voltage (VH). The ZT pin (1pin) cramps near 0V internal the IC. The way to determine Rzt1, Rzt2 and Czt is below. The block diagram is shown in Figure 18. The graph is also shown in Figure 19 and 20.

$$Izt1 = (Va - Vzt) / Rzt1 = Va / Rzt1 = VH * Na/Np / Rzt1 Rzt1 = Va / Izt1$$

Va: the auxiliary winding voltage (switching plus/minus) At deciding Rzt1, it should be determined from minus voltage value, and deciding Rzt2, it should be done from plus voltage value.

Izt1: the current that flows to the ZT pin Vzt: the ZT pin voltage

As the formula, Rzt1 is has to be set to the value that is divided by 1zt (typ=1mA) for the auxiliary winding Va under the AC voltage condition which the IC is going to switch the over current detection level. Secondly, the timing of turning on is has to be set by Czt to operate the ZT pin bottom detection at the moment that the Drain voltage of MOSFET is 0V. Finally, Rzt2 is also has to set the maximum ZT pin voltage is around 1 to 3V for the plus voltage of the auxiliary winding. (The noises are piled up to the ZT pin so the value of maximum voltage has been set considering a margin.) For that, Rzt2 is calculated as below. (In the case of setting in 2V)

$$VZT = Va \times Rzt2/(Rzt1 + Rzt2) < 2V$$

=>  $Rzt2 < 2 \times Rzt1 / (Va-2) = 2 \times Rzt1/(Na/Ns \times (Vout-VFs)-2)$

The auxiliary winding voltage Va has to be calculated in the plus voltage at maximum loads. In addition, the CS over current protection switching ZT current has the hysteresis of  $I_{ZTHYS}$  (typ=0.1mA).

Figure 18. CS over Current Detection Switched ZT current block diagram

Figure 19. FB pin Voltage vs. CS pin Voltage Characteristics

Figure 20 Izt Current vs Switched CS Voltage Characteristics

ex) a setting method (Switching between AC100V and AC230V)

AC100V: 141V±42V(±30% margin) AC230V: 325V±65V(±20% margin)

The winding numbers of transformer are: Np = 100, Na = 15, Ns = 20

According to above, when the IC switches the CS detection current between VH:  $182 \sim 260$ V, in case of switching the AC voltage at VH = 214V (AC150V) the minus voltage Va at MOSFET of QR turn on is calculated as below.

Rzt1 = Va /

$$I_{ZT}$$

= -32.1V/-1mA = 32.1k $\Omega$

According to this, Rzt1 is set to  $33k\Omega$ . At this time, according to Rzt2=2×33k/(20/15×19-2)=2.83k $\Omega$ , Rzt2 is also set to  $3k\Omega$ . Czt is set to the value which turns on MOSFET when the Drain voltage is minimum voltage after having checked the operation in the actual applications.

Figure 21 CS switching example VH voltage - CS voltage characteristics

## (4-5) Determination of OFF Width (Turn on)

The OFF width is controlled at the ZT pin. While the switching is OFF, the IC supplies the electric power which is stored at coils to the secondary output capacitor. After supplying, the DRAIN pin is drops because the current doesn't flow to the secondary side. For that, the voltage of auxiliary winding side also drops. The voltage divided by Rzt1 and Rzt2 applies to the ZT pin (1pin). If the voltage level drops to less than  $V_{ZT1}$  (typ =100mV), the IC turns on the OUT pin. To detection the zero current at the ZT pin (1pin), Czt, Rzt1 and Rzt2 makes time constant. However, the bottom time is adjusted by Czt because Rzt1 and Rzt2 needs to be set by the AC voltage correct function (4-3).

Toff1=Ls/(Vout+VF)\*Is (Toff1: transformer discharge time, Ls: secondary inductance, Vout: Secondary output, VF: secondary diode forward voltage, Is: secondary peak current)

For that, switching frequency is calculated below:

switching frequency=1 / {transformer charge and discharge time(Ton+Toff1) + (bottom-1/2) × resonant time } resonance time = 1 /  $(2 \times \pi \times Lp \times Cds)$

\* Lp: primary inductance, MOSFET D-S capacitor: Cds

Because a frequency reduction range in light load is restricted shown in Figure 16, bottom detection operates by the frequency which is lower than max frequency function in Figure 16.Additionally, the ZT trigger mask function (4-6) and a ZT timeout function (4-7) are built in IC.

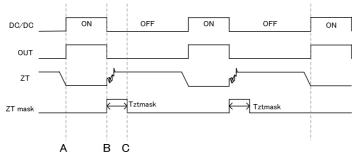

## (4-6) ZT Trigger Mask Function(Figure 22)

When switching is set from ON to OFF, superposition of noise may occur at the ZT pin. Then, the ZT comparator and ZTOVP comparator are masked for the  $T_{ZTMASK}$  time to prevent ZT comparator operation errors. In addition, taking a surge withstand pressure into consideration, the ZT voltage set by resistor divided is has to be set within 3V for the auxiliary winding voltage.

Figure 22 ZT Trigger Mask Function

- A: DC/DC OFF=>ON

- B: DC/DC ON=>OFF then the surge noise occurs to ZT pin.

- C: Since a noise occurs to ZT pin, the IC masks ZT comparator and ZTOVP comparator detection for T<sub>ZTMASK</sub> time.

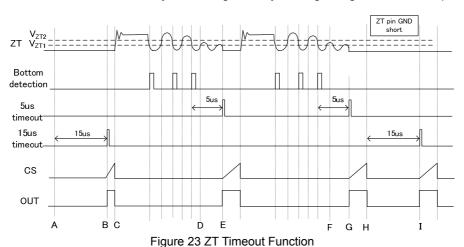

## (4-7-1) ZT Timeout Function1 (Figure 23)

When the ZT pin voltage is not higher than  $V_{ZT2}$  (typ=200mV) for  $T_{ZTOUT1}$  (typ=15us) such as start or low output voltage or ZT pin short, the IC turns on MOSFET by force.

#### (4-7-2) ZT Timeout Function2 (Figure 23)

After ZT comparator detects bottom, when the IC does not detect next bottom within  $T_{ZTOUT2}$ (typ =5us), it turns on MOSFET by force. After ZT comparator detects bottom at once, the function operates. For that, it does not operate at start or at low output voltage. When the IC is not able to detect bottom by decreasing auxiliary winding voltage, the function operates.

- A: At starting up, the IC starts to operate by ZT timeout function1 because of ZT=0V.

- B: MOSFET turns ON.

- C: MOSFET turns OFF.

- D: ZT voltage is lower than  $V_{ZT2}$  (typ=200mV) by ZT dump decreasing.

- E: MOSFET turns ON by ZT timeout fucntion2 after T<sub>ZT2</sub> (typ=5us) from D point.

- F: ZT voltage is lower than V<sub>ZT2</sub> (typ=200mV) by ZT dump decreasing.

- G: MOSFET turns ON by ZT timeout fucntion2 after T<sub>ZT2</sub> (typ=5us) from F point.

- H: ZT pin is short to GND.

- I: MOSFET turns ON by ZT timeout function1 after T<sub>ZTOUT1</sub> (typ=15us).

#### (5) Soft Start Sequence

Normally, when the AC voltage is applied, a large current flows to raise the output voltage. This IC has a built-in soft start function to prevent the output voltage and current from large change. This function is reset when the VCC pin (6pin) drops to less than  $V_{UVLO2}$  (typ=8.2V), and it performs at next applying. It operates as below after starting up. (Refer to the article of (4)-1 turn off.)

start ~ 0.5ms

0.5ms~1ms

1ms~2ms

2ms~4ms

4ms~

Set CS limiter to 12.5% of normal operation.

> Set CS limiter to 25% of normal operation.

> Set CS limiter to 50% of normal operation.

> Set CS limiter to 75% of normal operation.

> normal operation

## (6) CS (3pin) Open Protection

If the CS (3pin) is open, to prevent the OUT pin from making a error, the IC builds in the CS (3pin) open protection. When the CS (3pin) is open, the OUT pin (5pin) switching is stopped by the function. (This is auto-recovery)

Figure 24. CS Open Protection

#### (8) OUTPUT Over Load Protection (FB OLP comparator)

The over load protection is the function that monitors the condition of the secondary output current's over load and fixes the OUT pin (5pin) to Low at an over load condition. At a over load condition, there is no current in a photocoupler so the FB pin (2pin) rise to near 3.7V. When the condition continues for  $T_{FOLP}$  (typ =64ms), the IC judges this is over load state and the OUT pin (5pin) is fixed to L. If the FB pin (2pin) drops to  $V_{FOLP1B}$  (typ =2.6V) within  $T_{FOLP}$  (typ =64ms) from the moment that its voltage becomes higher  $V_{FOLP1A}$  (typ =2.8V), the over load protection timer is reset. At starting up, the FB pin starts to operate from more than  $V_{FOLP1A}$  (typ =2.8V) voltage because it is pull-up by a resistor to internal voltage. For this reason, the starting up time of the secondary output voltage is has to be set within  $T_{FOLP}$  (typ =64ms) from starting up.

After detecting the over load condition, the IC is stopped for  $T_{OLPST}$  (typ =512ms) and the IC operates auto-recovery. At this moment, the IC operates soft start. At stopping, although the VCC voltage drops, the VCC pin voltage keeps more than  $V_{UVLO2}$  because it is charged from starting circuits.

Figure 25. Over Load Protection: Auto-recovery

- A: When FB voltage is over V<sub>FOLP1A</sub>, FBOLP comparator detects an over load state.

- B: When the state A continues for T<sub>FOLP</sub> (typ=64ms), the IC stops switching by over load protection.

- C: During stopping switching by over load protection, VCC (6pin) voltage drops. When VCC (6pin) voltage is lower than V<sub>CHG</sub>, VCC re-charge function operates and the VCC (6pin) voltage is up.

- D: When the VCC (6pin) voltage is higher than V<sub>CHG2</sub> by re-charge function, VCC recharge function is stopped.

- E: It passes for T<sub>OLPST</sub> (typ =512ms) from B, the IC starts switching with soft start.

- F: When over load state continues, the FB (2pin) voltage is over V<sub>FOLP1A</sub>. When it passes for T<sub>FOLP</sub> (typ=64ms) from E, the IC stops switching.

- G: During stopping switching by over load protection, the VCC (6pin) voltage drops. When the VCC (6pin) voltage is lower than V<sub>CHG</sub>, VCC re-charge function operates and the VCC (6pin) voltage is up.

- H: When the VCC (6pin) voltage is higher than V<sub>CHG2</sub> by re-charge function, VCC recharge function is stopped.

#### (9) OUT (5pin) Voltage Clamp Function

For the purpose which protects the external MOSFET, H level of the OUT (5pin) is clamped to  $V_{OUTH}$  (typ=12.5V). It prevents gate destruction of MOSFET by raising the VCC (6pin) voltage. (Refer to Figure 23) The OUT (5pin) is pulled-down  $R_{PDOUT}$  (typ=100k $\Omega$ ).

Figure 26. OUT (5pin) Construction

## •Operation Mode of Protection Circuit

Operation mode of protection functions are shown in table3.

Table 3. Operation Mode of Protection Circuit

| Item                         | Protection mode                          |

|------------------------------|------------------------------------------|

| VCC Under Voltage Locked Out | Auto recovery                            |

| VCC Over Voltage Protection  | Auto recovery (with 100us timer)         |

| FB Over Load Protection      | Auto recovery (delay: 64ms, stop: 512ms) |

| CS Open Protection           | Auto recovery                            |

| ZT Over Voltage Protection   | -                                        |

| VCC Charge Protection        | Auto recovery                            |

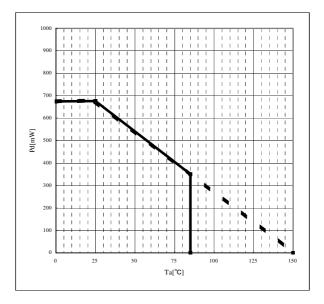

## • Power Dissipation

The thermal design should set operation for the following conditions. (Since the temperature shown below is the guaranteed temperature, be sure to take a margin into account.)

- 1. The ambient temperature Ta must be 85  $\!\!\!\square$  or less.

- 2. The IC's loss must be within the allowable dissipation Pd.

The thermal abatement characteristics are as follows. (PCB: 70 mm × 70 mm × 1.6 mm, mounted on glass epoxy substrate)

Figure 27. SOP-J8 Thermal Abatement Characteristics

#### Operational Notes

## (1) Absolute maximum ratings

Damage may occur if the absolute maximum ratings such as for applied voltage or operating temperature range are exceeded, and since the type of damage (short, open circuit, etc.) cannot be determined, in cases where a particular mode that may exceed the absolute maximum ratings is considered, use of a physical safety measure such as a fuse should be investigated.

#### (2) Power supply and ground lines

In the board pattern design, power supply and ground lines should be routed so as to achieve low impedance. If there are multiple power supply and ground lines, be careful with regard to interference caused by common impedance in the routing pattern. With regard to ground lines in particular, be careful regarding the separation of large current routes and small signal routes, including the external circuits. Also, with regard to all of the LSI's power supply pins, in addition to inserting capacitors between the power supply and ground pins, when using capacitors there can be problems such as capacitance losses at low temperature, so check thoroughly as to whether there are any problems with the characteristics of the capacitor to be used before determining constants.

#### (3) Ground potential

The ground pin's potential should be set to the minimum potential in relation to the operation mode.

#### (4) Pin shorting and attachment errors

When attaching ICs to the set board, be careful to avoid errors in the IC's orientation or position. If such attachment errors occur, the IC may become damaged. Also, damage may occur if foreign matter gets between pins, between a pin and a power supply line, or between ground lines.

#### (5) Operation in strong magnetic fields

Note with caution that these products may become damaged when used in a strong magnetic field.

#### (6) Input pins

In IC structures, parasitic elements are inevitably formed according to the relation to potential. When parasitic elements are active, they can interfere with circuit operations, can cause operation faults, and can even result in damage. Accordingly, be careful to avoid use methods that enable parasitic elements to become active, such as when a voltage that is lower than the ground voltage is applied to an input pin. Also, do not apply voltage to an input pin when there is no power supply voltage being applied to the IC. In fact, even if a power supply voltage is being applied, the voltage applied to each input pin should be either below the power supply voltage or within the guaranteed values in the electrical characteristics.

#### (7) External capacitors

When a ceramic capacitor is used as an external capacitor, consider possible reduction to below the nominal capacitance due to current bias and capacitance fluctuation due to temperature and the like before determining constants.

## (8) Thermal design

The thermal design should fully consider allowable dissipation (Pd) under actual use conditions.

Also, use these products within ranges that do not put output Tr beyond the rated voltage and ASO.

## (9) Rush current

In a CMOS IC, momentary rush current may flow if the internal logic is undefined when the power supply is turned ON, so caution is needed with regard to the power supply coupling capacitance, the width of power supply and GND pattern wires, and how they are laid out.

## (10) Handling of test pins and unused pins

Test pins and unused pins should be handled so as not to cause problems in actual use conditions, according to the descriptions in the function manual, application notes, etc. Contact us regarding pins that are not described.

## (11) Document contents

Documents such as application notes are design documents used when designing applications, and as such their contents are not guaranteed. Before finalizing an application, perform a thorough study and evaluation, including for external parts.

#### Status of this document

The Japanese version of this document is formal specification. A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document formal version takes priority

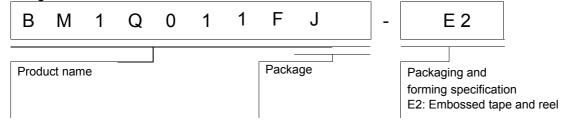

Ordering Information

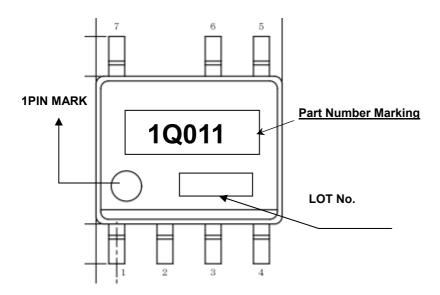

## Marking Diagram

Line-Up

| Marking Name | Package | Order name   |

|--------------|---------|--------------|

| 1Q011        | SOP-J7S | BM1Q011FJ-E2 |

Physical Dimension, Tape and Reel Information