# mail

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Middle Power Class-D Speaker Amplifier series

# 17W+17W Full Digital Speaker Amplifier with built-in DSP

# **BM28723MUV**

#### **General Description**

BM28723MUV is a 17W+17W Class D stereo Speaker Amplifier with built-in DSP designed for TVs specifically for space-saving and low-power consumption.

BM28723MUV features BCD (Bipolar, CMOS, DMOS) process technology to achieve high efficiency. In addition, BM28723MUV is packaged in a compact back surface heatsink type power package to attain low power consumption, low heat generation without external heatsink. The package Max output power is only 17W+17W (When  $R_L=8\Omega$ ) as compared to 20W+20W (When RL=8Ω) Max output power of package with external heat-sink.

The product satisfies all needs for drastic downsizing, low-profile structures and powerful high quality playback of sound systems.

### **Key Specifications**

| Supply voltage range                     | 10V to 24V     |

|------------------------------------------|----------------|

| (VCCP1,VCCP2)                            |                |

| <ul> <li>Speaker output power</li> </ul> | 17W+17W (Typ)  |

| $(V_{CCP1}, V_{CCP2}=18V,$               |                |

| R∟=8Ω)                                   |                |

| ■ THD+N                                  | 0.08 [%] (Typ) |

#### ■ THD+N **Applications**

- TVs (LCD, OLED)

- Home Audio

- Desktop PC

- Amusement equipment

- Electronic Music equipment, etc.

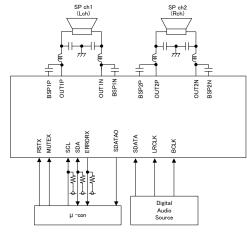

# **Typical Application Circuit**

Figure 1. Typical application circuit

#### **Features**

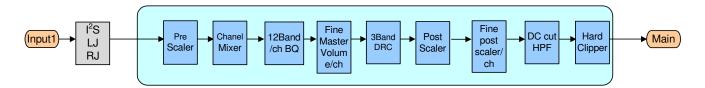

- Built-in DSP (Digital Sound Processor) for Audio Signal Processing for TVs 12-Band/ch BQ, 3-Band DRC, Pre-Scaler, Channel Mixer, Fine Master Volume, Hard Clipper, Level Meter. etc.

- Single Input System for Digital Audio Interface (No Master Clock Required)

- I2S / LJ / RJ Format

- LRCLK: 32 / 44.1 / 48kHz

- BCLK: 32 / 48 / 64fs

- SDATA: 16 / 20 / 24 bit

- Single Output System for Digital Audio Interface - I<sup>2</sup>S Format

- SDATA: 16 / 20 / 24 bit

- No Snubber Circuit Required (V<sub>CCP1</sub>, V<sub>CCP2</sub>≤22V) because of Slew Rate Control

- Output Feedback Circuit which prevents decrease of sound quality caused by change of power supply voltage, achieves low noise and low distortion, So no large electrolytic-capacitors for Vcc bypass is required.

- Wide Range of Power Supply Input Voltage

- The monaural output reduces the number of external parts needed.

- High Efficiency and Low Heat Dissipation allowing Miniaturization, Slim Design, and also Power Saving of the System

- Eliminates pop-noise generated during the power supply ON/OFF. High quality muting performance is achieved using the soft-muting technology.

- Built-in with Various Protection Functions for Highly **Reliability Design**

- High Temperature Protection

- Under Voltage Protection

- Output Short Protection

- DC Voltage Protection for speaker

- Clock Stop Protection

- Small Package, It reduces surface mount area

W(Typ) x D(Typ) x H(Max)

OProduct structure:Silicon monolithic integrated circuit OThis product has not designed protection against radioactive rays

Package

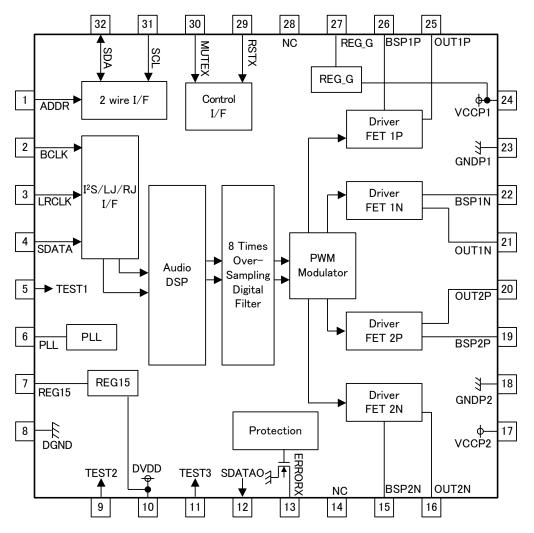

# Pin configuration and Block diagram

Figure 2. Pin configurations and Block diagram (Top View)

# **Pin Description**

| No. | Name  | I/O | No. | Name   | I/O | No. | Name  | I/O | No. | Name  | I/O |

|-----|-------|-----|-----|--------|-----|-----|-------|-----|-----|-------|-----|

| 1   | ADDR  | Ι   | 9   | TEST2  | Ι   | 17  | VCCP2 | -   | 25  | OUT1P | 0   |

| 2   | BCLK  | Ι   | 10  | DVDD   | -   | 18  | GNDP2 | -   | 26  | BSP1P | Ι   |

| 3   | LRCLK | Ι   | 11  | TEST3  | Ι   | 19  | BSP2P | Ι   | 27  | REG_G | 0   |

| 4   | SDATA | Ι   | 12  | SDATAO | 0   | 20  | OUT2P | 0   | 28  | NC    | -   |

| 5   | TEST1 | Ι   | 13  | ERRORX | 0   | 21  | OUT1N | 0   | 29  | RSTX  | -   |

| 6   | PLL   | I/O | 14  | NC     | -   | 22  | BSP1N | I   | 30  | MUTEX | Ι   |

| 7   | REG15 | 0   | 15  | BSP2N  | Ι   | 23  | GNDP1 | -   | 31  | SCL   | Ι   |

| 8   | DGND  | -   | 16  | OUT2N  | 0   | 24  | VCCP1 | -   | 32  | SDA   | I/O |

I = input; O = output; - = others

# I/O equivalence circuits

| Pin<br>No. | Pin name       | Pin<br>voltage | Pin explanation                                                                                                                                                                                              | I/O equivalence circuit |

|------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 1          | ADDR           | 0V             | 2 wire Bus control Slave address select pin                                                                                                                                                                  | 10-+                    |

|            |                |                | Select LSB data of slave address for 2 wire Bus<br>control.<br>Input High level to set LSB=1.<br>Input Low level to set LSB=0.<br>Select pull-down resistor after DVDD is applied.                           |                         |

| 2          | BCLK           | 3.3V           | Digital audio signal input pin                                                                                                                                                                               | 10 + +                  |

|            |                |                | Input bit clock of digital audio signal.<br>Select pull-up resistor after DVDD is applied.                                                                                                                   |                         |

|            |                |                |                                                                                                                                                                                                              | 8                       |

| 34         | LRCLK<br>SDATA | 3.3V           | Digital audio signal input pin<br>Input LR clock of digital audio signal to LRCLK<br>terminal.<br>Input data of digital audio signal to SDATA<br>terminal.<br>Select pull-up resistor after DVDD is applied. |                         |

| 5<br>9     | TEST1<br>TEST2 | -              | Test pin                                                                                                                                                                                                     |                         |

| 11         | TEST3          | -              | Connect to DGND.                                                                                                                                                                                             |                         |

|            |                |                |                                                                                                                                                                                                              |                         |

| 6          | PLL            | 1V             | PLL filter pin                                                                                                                                                                                               |                         |

|            |                |                | Connect filter circuit for PLL.                                                                                                                                                                              |                         |

The numerical value of I/O equivalence circuit is typical value, not guaranteed.

# I/O equivalence circuit(s) - continued

| Pin<br>No. | Pin name | Pin voltage             | Pin explanation                                                                                                                                                                                                                                                                                                                                          | I/O equivalence circuit |

|------------|----------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 7          | REG15    | 1.5V                    | Internal power supply pin for digital circuit<br>Connect capacitor.<br>(Note) The REG15 terminal of BM28723MUV should not be<br>used as an external supply and cannot support voltage load<br>from external source. Therefore, do not connect anything<br>except capacitor for stabilization.                                                            |                         |

| 8          | DGND     | 0V                      | GND pin for Digital I/O                                                                                                                                                                                                                                                                                                                                  | -                       |

| 10         | DVDD     | 3.3V                    | Power supply pin for Digital I/O.<br>Connect capacitor.                                                                                                                                                                                                                                                                                                  | -                       |

| 12         | SDATAO   | 3.3V                    | Digital audio signal output pin<br>Output data of digital audio signal.<br>Select pull-up resistor after DVDD is applied.                                                                                                                                                                                                                                |                         |

| 13         | ERRORX   | 3.3V                    | Error flag pin<br>Connect pull-up resistor.<br>High: Normal operation<br>Low: Error<br>(Note) An error flag is indicated when Output Short Protection,<br>DC Voltage Protection for speaker, and High Temperature<br>Protection are activated. The flag shows the IC condition<br>during operation.<br>Don't use for the protection except this product. |                         |

| 14<br>28   | NC       | -                       | No-Connection Pin<br>Don't connect anything                                                                                                                                                                                                                                                                                                              | -                       |

| 15         | BSP2N    | -                       | Boot strap pin, CH2 negative                                                                                                                                                                                                                                                                                                                             | (17) • •                |

| 16         | OUT2N    | V <sub>CCP2</sub> to 0V | Connect a capacitor from pin to OUT2N.<br>PWM output pin, CH2 negative<br>Connect pin to output LPF.<br>(Note) If this pin is shorted to GND, the IC may break.<br>(Note) When Reset ON or Mute ON, all output transistors are<br>OFF and output terminals are pulled down by 10kΩ (Typ).                                                                |                         |

| 17         | VCCP2    | V <sub>CCP2</sub>       | Power supply pin for CH2                                                                                                                                                                                                                                                                                                                                 |                         |

| 18         | GNDP2    | 0V                      | Power GND pin for CH2                                                                                                                                                                                                                                                                                                                                    | ★ ⊣⊢                    |

| 19         | BSP2P    | -                       | Boot strap pin, CH2 positive<br>Connect a capacitor from pin to OUT2P.                                                                                                                                                                                                                                                                                   |                         |

| 20         | OUT2P    | V <sub>CCP2</sub> to 0V | PWM output pin, CH2 positive<br>Connect pin to output LPF.<br>(Note) If this pin is shorted to GND, the IC may break.<br>(Note) When Reset ON or Mute ON, all output transistors are<br>OFF and output terminals are pulled down by 10kΩ (Typ).<br>troical value, not quaranteed                                                                         |                         |

The numerical value of I/O equivalence circuit is typical value, not guaranteed.

# I/O equivalence circuit(s) - continued

| Pin<br>No. | Pin name | Pin<br>voltage             | Pin explanation                                                                                                                                                                                                                                  | I/O equivalence circuit |

|------------|----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| 21         | OUT1N    | V <sub>CCP1</sub> to<br>0V | PWM output pin, CH1 negative<br>Connect pin to output LPF.<br>(Note) If this pin is shorted to GND, the IC may break.<br>(Note) When Reset ON or Mute ON, all output transistors are OFF<br>and output terminals are pulled down by 10kΩ (Typ).  |                         |

| 22         | BSP1N    | -                          | Boot strap pin, CH1 negative                                                                                                                                                                                                                     | 22, 26                  |

| 00         | GNDP1    | 0)/                        | Connect a capacitor from pin to OUT1N.                                                                                                                                                                                                           |                         |

| 23<br>24   | VCCP1    | 0V<br>VCCP1                | Power GND pin for ch1<br>Power supply pin for ch1                                                                                                                                                                                                |                         |

| 25         | OUT1P    | V <sub>CCP1</sub> to<br>0V | PWM output pin, CH1 positive<br>Connect to output LPF.                                                                                                                                                                                           |                         |

| 26         | BSP1P    |                            | <ul> <li>(Note) If this pin is shorted to GND, the IC may break.</li> <li>(Note) When Reset ON or Mute ON, all output transistors are OFF and output terminals are pulled down by 10kΩ (Typ).</li> <li>Boot-strap pin of ch1 positive</li> </ul> |                         |

| 20         | DOPTE    | -                          | Door-sup pin or on positive                                                                                                                                                                                                                      |                         |

|            |          |                            | Connect a capacitor from pin to OUT1P.                                                                                                                                                                                                           |                         |

| 27         | REG_G    | 5.7V                       | Internal power supply pin for gate driver<br>Connect capacitor                                                                                                                                                                                   |                         |

|            |          |                            | (Note) The REG_G terminal of BM28723MUV should not be used<br>as an external supply and cannot support voltage load from<br>external source. Therefore, do not connect anything except<br>capacitor for stabilization.                           | 27<br>350kΩ<br>23       |

| 29         | RSTX     | 0V                         | Reset pin for Digital circuit<br>High: Reset OFF<br>Low: Reset ON                                                                                                                                                                                |                         |

|            |          |                            | Select pull-down resistor after DVDD is applied.                                                                                                                                                                                                 | (2930)                  |

| 30         | MUTEX    | 0V                         | Speaker output mute control pin<br>High: Mute OFF<br>Low: Mute ON                                                                                                                                                                                |                         |

|            |          |                            | Select pull-down resistor after DVDD is applied.                                                                                                                                                                                                 |                         |

| 31         | SCL      | -                          | 2 wire Bus control transmit clock input pin                                                                                                                                                                                                      | 31                      |

|            |          |                            | Input the transmit clock to this pin for 2 wire Bus control. This pin is not corresponding to threshold tolerance of 5V.<br>Refer to:                                                                                                            |                         |

| -          |          |                            | Absolute Maximum Ratings, Input voltage 1                                                                                                                                                                                                        | 8                       |

| 32         | SDA      | -                          | 2 wire Bus control data input/output pin<br>Input the transmit data to this pin for 2 wire Bus<br>control. This pin is not corresponding to threshold<br>tolerance of 5V.                                                                        |                         |

|            |          |                            | Refer to:<br>Absolute Maximum Ratings, Input voltage 1                                                                                                                                                                                           | 8                       |

The numerical value of I/O equivalence circuit is typical value, not guaranteed.

# Absolute Maximum Ratings (Ta=25°C)

| Item                        | Symbol            | Limit                                                 | Unit | Conditions                | ;                  |

|-----------------------------|-------------------|-------------------------------------------------------|------|---------------------------|--------------------|

| Cuerty Maltage              | VCCMAX            | 30                                                    | V    | Pin 17, 24                | (Note 1) (Note 2)  |

| Supply Voltage              | VDVDDMAX          | 4.5                                                   | V    | Pin 10                    | (Note 1)           |

| Input Voltage 1             | V <sub>IN1</sub>  | -0.3 to<br>V <sub>DVDD</sub> +0.3 <sup>(Note 3)</sup> | V    | Pin 1 - 5, 9, 11, 29 - 32 | (Note 1)           |

| Terminal Voltage 1          | V <sub>PIN1</sub> | -0.3 to +7.0                                          | V    | Pin 27                    | (Note 1)           |

| Terminal Voltage 2          | VPIN2             | -0.3 to<br>+V <sub>CCMAX</sub>                        | V    | Pin 16, 20, 21, 25        | (Note 1)(Note 4-1) |

|                             |                   | -0.3 to V <sub>OUT1P</sub> +7                         |      | Pin 26                    | (Note 1)(Note 4-2) |

| Terminal Valtage 2          | V <sub>PIN3</sub> | -0.3 to Voutin+7                                      | V    | Pin 22                    | (Note 1)(Note 4-2) |

| Terminal Voltage 3          |                   | -0.3 to VOUT2P+7                                      | v    | Pin 19                    | (Note 1)(Note 4-2) |

|                             |                   | -0.3 to V <sub>OUT2N+7</sub>                          |      | Pin 15                    | (Note 1)(Note 4-2) |

| Terminal Voltage 4          | V <sub>PIN4</sub> | -0.3 to +2.1                                          | V    | Pin 7                     | (Note 1)           |

| Open-drain Terminal Voltage | VERR              | -0.3 to +7.0                                          | V    | Pin13                     | (Note 1)           |

| Operating Temperature Range | Topr              | -25 to +85                                            | °C   |                           |                    |

| Storage Temperature Range   | Tstg              | -55 to +150                                           | °C   |                           |                    |

| Junction Temperature Range  | Tj                | -40 to +150                                           | °C   |                           |                    |

(Note 1) The voltage that can be applied reference to GND (Pin 8, 18, 23). (Note 2) Do not exceed Tj=150°C.

(Note 3) Refer to Recommended Operating Ratings for VDVDD.

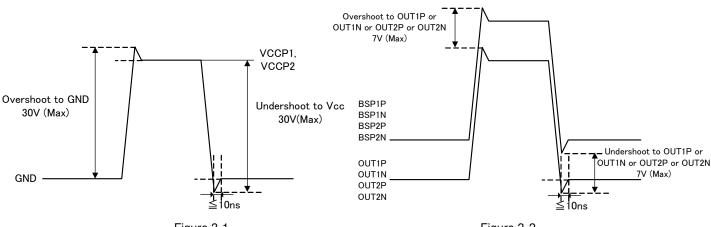

(Note 4-1) This IC should be used within AC peak limits at all conditions. Overshoot should be ≤30V with reference to GND. Undershoot should be ≤10ns and ≤30V with reference to VCCP1 and VCCP2. (Refer to figure 3-1.)

(Note 4-2) This IC should be used in lower than this rating by all means.

Undershoot should be ≤10ns and ≤( Voutip or Voutin or Voutip or Voutip)+7V. (Refer to figure 3-2.)

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

Figure 3-1

Figure 3-2

# Thermal Resistance(Note 5)

| Deremeter                                                      | Symbol      | Thermal Re             | Linit                    |      |

|----------------------------------------------------------------|-------------|------------------------|--------------------------|------|

| Parameter                                                      | Symbol      | 1s <sup>(Note 7)</sup> | 2s2p <sup>(Note 8)</sup> | Unit |

| VQFN032V5050                                                   | i           |                        |                          |      |

| Junction to Ambient                                            | θја         | 138.9                  | 39.1                     | °C/W |

| Junction to Top Characterization Parameter <sup>(Note 6)</sup> | $\Psi_{JT}$ | 11                     | 5                        | °C/W |

| (Note 5)Based on JESD51-2A(Still-Air)                          | i           |                        |                          |      |

(Note 6) The thermal characterization parameter to report the difference between junction temperature and the temperature at the top center of the outside surface of the component package.

(Note 7)Using a PCB board based on JESD51-3.

| (Note 7) Using a r OD board based on BEODOT-0. |           |                            |  |  |  |  |

|------------------------------------------------|-----------|----------------------------|--|--|--|--|

| Layer Number of<br>Measurement Board           | Material  | Board Size                 |  |  |  |  |

| Single                                         | FR-4      | 114.3mm x 76.2mm x 1.57mmt |  |  |  |  |

| Тор                                            |           |                            |  |  |  |  |

| Copper Pattern                                 | Thickness |                            |  |  |  |  |

| Footprints and Traces                          | 70µm      |                            |  |  |  |  |

|                                                |           |                            |  |  |  |  |

(Note 8)Using a PCB board based on JESD51-5, 7.

| Layer Number of       | Material  | Board Size               |          | Thermal \      | /ia <sup>(Note 9)</sup> |  |

|-----------------------|-----------|--------------------------|----------|----------------|-------------------------|--|

| Measurement Board     | Material  |                          |          | Pitch          | Diameter                |  |

| 4 Layers              | FR-4      | 114.3mm x 76.2mm x       | x 1.6mmt | 1.20mm         | Ф0.30mm                 |  |

| Тор                   | Тор       |                          | ers      | Bottom         |                         |  |

| Copper Pattern        | Thickness | Copper Pattern Thickness |          | Copper Pattern | Thickness               |  |

| Footprints and Traces | 70µm      | 74.2mm x 74.2mm          | 35µm     | 74.2mm x 74.2m | m 70µm                  |  |

(Note 9) This thermal via connects with the copper pattern of all layers..

# Recommended Operating Ratings (Ta= -25°C to +85°C)

| Item                   | Symbol            | Limit      | Unit | Conditions                                   |                   |

|------------------------|-------------------|------------|------|----------------------------------------------|-------------------|

|                        | V <sub>CCP1</sub> | 10 to 24   | V    | Pin 24                                       | (Note 1) (Note 2) |

| Supply voltage         | VCCP2             | 10 to 24   | V    | Pin 17                                       | (Note 1) (Note 2) |

|                        | Vdvdd             | 3.0 to 3.6 | V    | Pin 10                                       | (Note 1)          |

|                        |                   | 6.4        | Ω    | 21V <v<sub>CCP1,V<sub>CCP2</sub>≤24V</v<sub> | (Note 2)          |

| Minimum load impedance | RL                | 4.8        | Ω    | 14V <v<sub>CCP1,V<sub>CCP2</sub>≤21V</v<sub> | (Note 2)          |

|                        |                   | 3.6        | Ω    | V <sub>CCP1</sub> ,V <sub>CCP2</sub> ≤14V    | (Note 2)          |

(Note 1) The voltage that can be applied reference to GND (Pin 8, 18, 23).

(Note 2) Do not exceed Tj=150°C.

# **Electrical Characteristics**

(Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=8Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB, LC Filter: L=10μH, C<sub>g</sub>=0.47μF, Without Snubber circuit)

| Deverenter                                     | Currents of       |     | Limit |     | Unit  | Dis and Conditions                                                                                           |

|------------------------------------------------|-------------------|-----|-------|-----|-------|--------------------------------------------------------------------------------------------------------------|

| Parameter                                      | Symbol            | Min | Тур   | Max | Unit  | Pin and Conditions                                                                                           |

| Total circuit                                  |                   |     |       |     |       |                                                                                                              |

| Circuit current 1<br>(Normal mode)             | Icc1              | I   | 45    | 90  | mA    | Pin 17, 24, -infinity dBFS input,<br>No load                                                                 |

| (Normai mode)                                  | IDD1              | -   | 9     | 19  | mA    | Pin 10, -infinity dBFS input, No load                                                                        |

| Circuit current 2                              | Icc2              | I   | 110   | 400 | μA    | Pin 17, 24, -infinity dBFS input,<br>No load, V <sub>RSTX</sub> =0V, V <sub>MUTEX</sub> =0V                  |

| (Reset mode)                                   | I <sub>DD2</sub>  | -   | 2.5   | 7.0 | mA    | Pin 10, -infinity dBFS input, No load V <sub>RSTX</sub> =0V, V <sub>MUTEX</sub> =0V                          |

| Open-drain terminal<br>Low level voltage       | V <sub>ERR</sub>  | -   | -     | 0.8 | V     | Pin 13, I <sub>OUT</sub> =0.5mA                                                                              |

| High level input voltage                       | VIH               | 2.5 | -     | 3.3 | V     | Pin 1 - 5, 9, 11, 29 -32                                                                                     |

| Low level input voltage                        | VIL               | 0   | -     | 0.8 | V     | Pin 1 - 5, 9, 11, 29 -32                                                                                     |

| Input pull-up resistance                       | Rup               | 22  | 33    | -   | kΩ    | Pin 2 - 4, V <sub>IN</sub> = 0V                                                                              |

| Input pull-down resistance                     | Rdn               | 31  | 47    | -   | kΩ    | Pin 1, 29, 30, V <sub>IN</sub> = 3.3V                                                                        |

| Input current<br>(SCL, SDA terminal)           | lı∟               | -1  | 0     | -   | μA    | Pin 31, 32, V <sub>IN</sub> = 0V                                                                             |

| Input current<br>(SCL, SDA terminal)           | Іін               | -   | 0     | 1   | μA    | Pin 31, 32, V <sub>IN</sub> = 3.3V                                                                           |

| Speaker amplifier output                       |                   |     |       |     |       |                                                                                                              |

| Maximum output power 1 <sup>(Note 10)</sup>    | P <sub>O1</sub>   | -   | 10    | -   | W     | VCCP1, VCCP2=13V, THD+N=10%                                                                                  |

| Maximum output power 2(Note 10)                | P <sub>O2</sub>   | -   | 15    | -   | W     | V <sub>CCP1</sub> ,V <sub>CCP2</sub> =16V,THD+N=10%                                                          |

| Total harmonic distortion <sup>(Note 10)</sup> | THD               | -   | 0.08  | -   | %     | V <sub>CCP1</sub> ,V <sub>CCP2</sub> =12V, P <sub>0</sub> =1W,<br>BW=AES17(20-22kHz)<br>With snubber circuit |

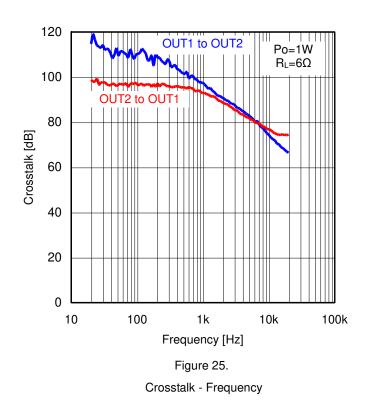

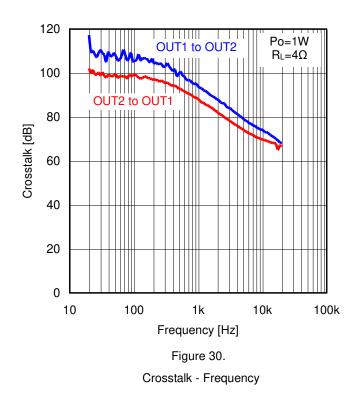

| Crosstalk <sup>(Note 10)</sup>                 | СТ                | 60  | 90    | -   | dB    | Po=1W, 1kHz BPF                                                                                              |

| PSRR <sup>(Note 10)</sup>                      | PSRR              | -   | 60    | -   | dB    | V <sub>ripple</sub> =1V <sub>rms</sub> , f=1kHz                                                              |

| Output noise voltage <sup>(Note 10)</sup>      | V <sub>NO</sub>   | -   | 150   | -   | μVrms | -Infinity dBFS input, BW=A-Weight                                                                            |

|                                                | f <sub>PWM1</sub> | -   | 256   | -   | kHz   | fs=32 kHz                                                                                                    |

| PWM (Pulse Width Modulation)                   | fpwm2             | -   | 352.8 | -   | kHz   | fs=44.1 kHz                                                                                                  |

| frequency                                      | fрwмз             | -   | 384   | -   | kHz   | fs=48 kHz                                                                                                    |

(Note 10) These items show the typical performance of device and depend on board layout, parts, and power supply. The standard value is in mounting device and parts on surface of ROHM's board directly.

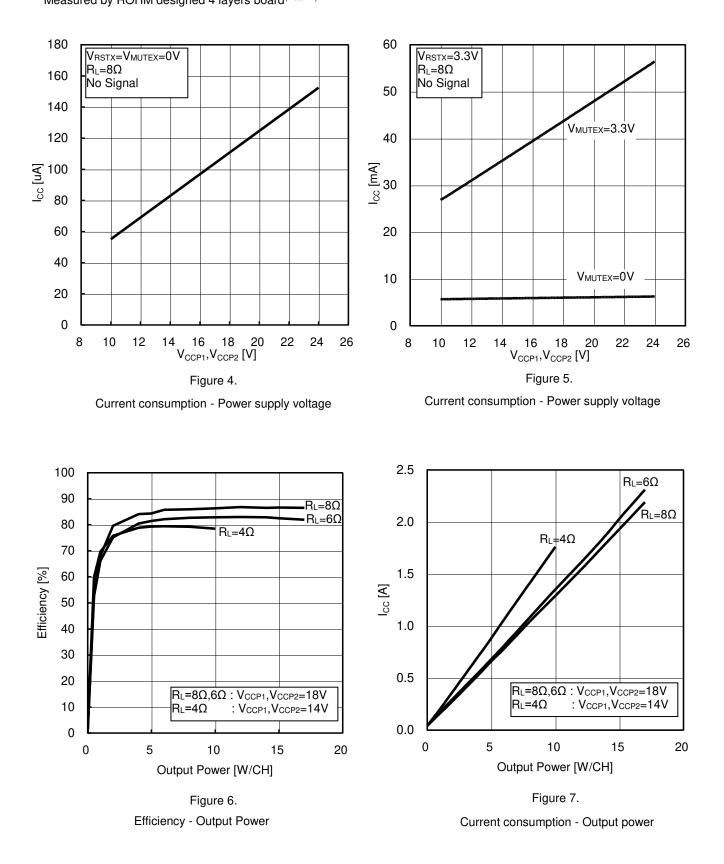

# **Typical Performance Curves**

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>, V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=8 $\Omega$ , DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/70µm/75µm For Application Evaluation Board

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=8Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB

Measured by ROHM designed 4 layers board (Note 11)

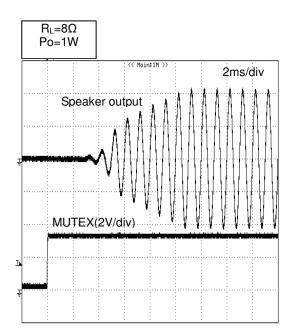

Figure 8. Waveform at soft start

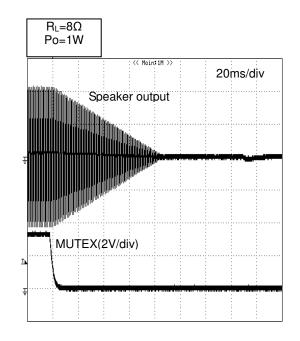

Figure 9. Waveform at soft mute

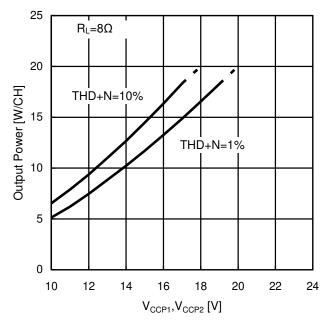

#### Figure 10.

separately. \* Use this IC in 20W or less output power even with heat dissipation measures.

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/75µm For Application Evaluation Board

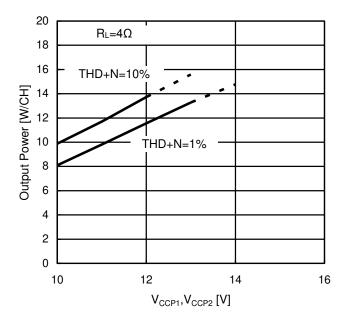

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

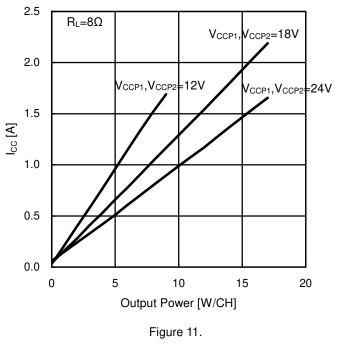

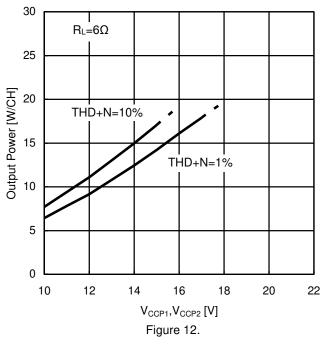

Output Power - Power supply voltage (RL=6Ω) \*Dotted line means exceeding maximum junction temperature. In that case heat dissipation measures such as the heat sink are necessary separately.

\* Use this IC in 20W or less output power even with heat dissipation measures.

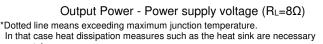

\*Dotted line means exceeding maximum junction temperature.

In that case heat dissipation measures such as the heat sink are necessary

separately. \* Use this IC in 15W or less output power even with heat dissipation measures.

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/35µm For Application Evaluation Board

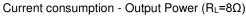

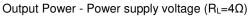

Current consumption - Output Power ( $R_L=6\Omega$ )

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=8Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB

Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

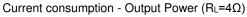

Unless otherwise specified Ta=25°C,  $V_{CCP1}$ ,  $V_{CCP2}$ =18V,  $V_{DVDD}$ =3.3V,  $V_{RSTX}$ =3.3V,  $V_{MUTEX}$ =3.3V, f=1kHz, fs=48kHz, RL=8 $\Omega$ , DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/70µm/75µm For Application Evaluation Board

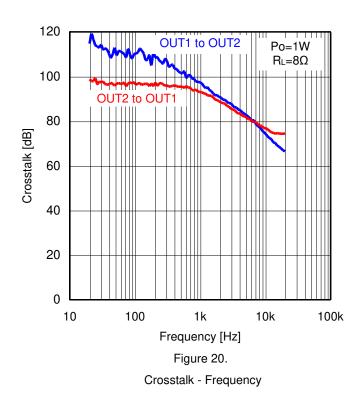

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=6Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB

Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/35µm For Application Evaluation Board

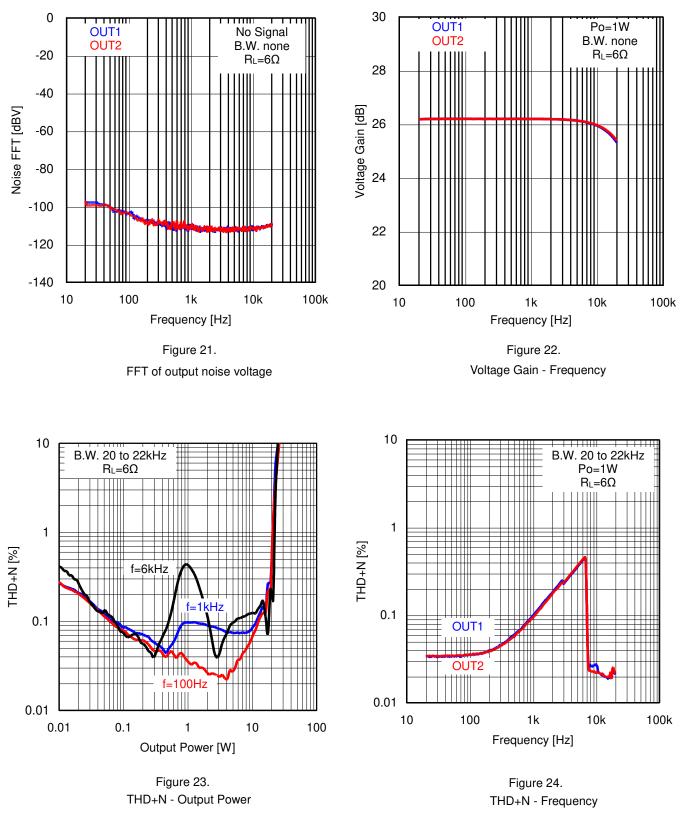

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=6Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/70µm/75µm For Application Evaluation Board

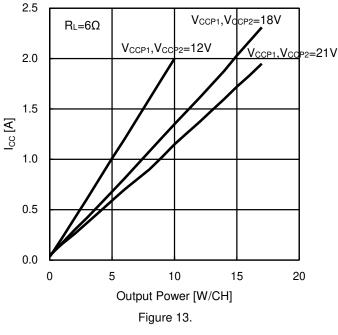

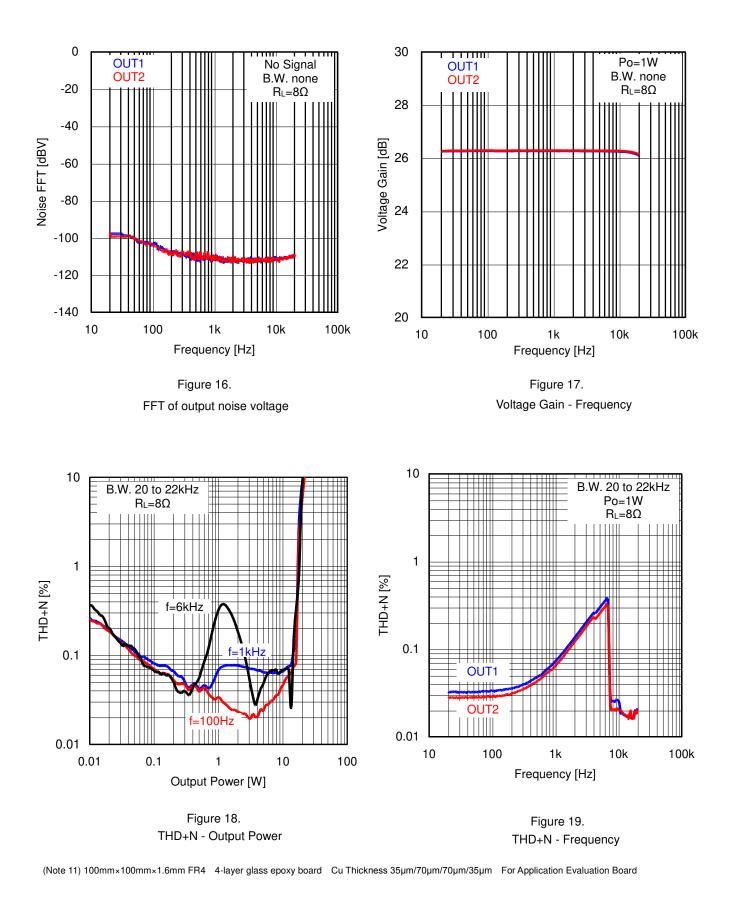

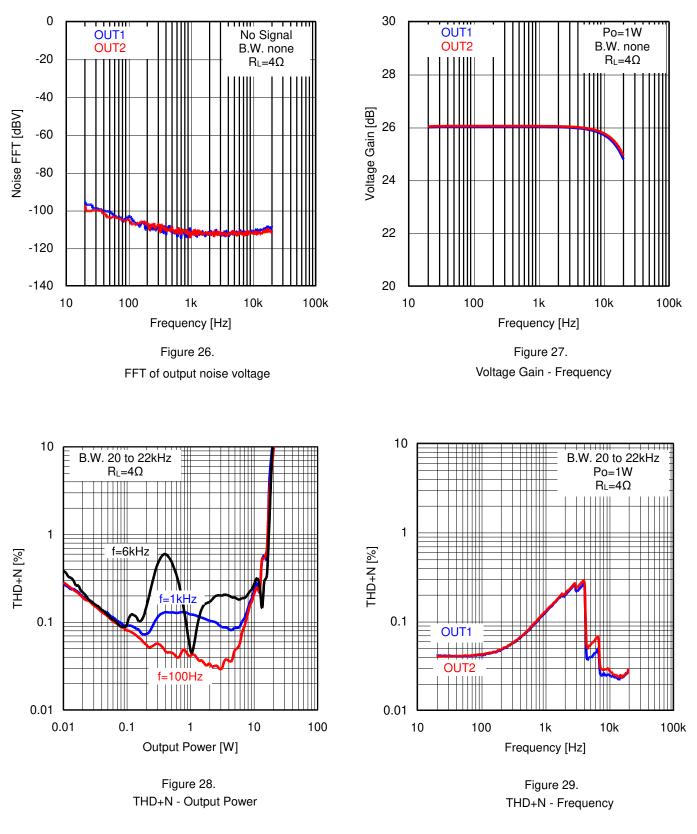

Unless otherwise specified Ta=25°C, V<sub>CCP1</sub>,V<sub>CCP2</sub>=18V, V<sub>DVDD</sub>=3.3V, V<sub>RSTX</sub>=3.3V, V<sub>MUTEX</sub>=3.3V, f=1kHz, fs=48kHz, R<sub>L</sub>=4Ω, DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB

Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/75µm For Application Evaluation Board

Unless otherwise specified Ta=25°C,  $V_{CCP1}$ ,  $V_{CCP2}$ =18V,  $V_{DVDD}$ =3.3V,  $V_{RSTX}$ =3.3V,  $V_{MUTEX}$ =3.3V, f=1kHz, fs=48kHz, RL=4 $\Omega$ , DSP: Through, Driver Gain(G<sub>DRV</sub>)=26dB Measured by ROHM designed 4 layers board<sup>(Note 11)</sup>

(Note 11) 100mm×100mm×1.6mm FR4 4-layer glass epoxy board Cu Thickness 35µm/70µm/70µm/70µm/75µm For Application Evaluation Board

#### **DSP Block Functional Overview**

| No. | Function           | Specification                                                                         |

|-----|--------------------|---------------------------------------------------------------------------------------|

| 1   | Pre-Scaler         | <ul> <li>Lch / Rch become same set point.</li> </ul>                                  |

|     |                    | •+48dB to -79dB (0.5dB step),-∞dB                                                     |

| 2   | Channel Mixer      | •It is able to set mixing of Left and Right channel which are inputted digital signal |

|     |                    | to Audio DSP                                                                          |

|     |                    | •Selectable in L,(L+R)/2, L-R, R, MUTE                                                |

| 3   | 12 Band BQ         | •12 Band Bi-quad(BQ) type filter .                                                    |

|     |                    | <ul> <li>Only 5 coefficients are required.(b0,b1,b2,a1,a2)</li> </ul>                 |

|     |                    | <ul> <li>Lch/Rch dependent or independent.</li> </ul>                                 |

|     |                    | <ul> <li>The Filter types which can be attained are</li> </ul>                        |

|     |                    | Peaking/Low-shelf/High-shelf/Low-pass/High-pass/All-pass/Notch.                       |

|     |                    | •There is soft transition function.                                                   |

| 4   | Fine Master Volume | <ul> <li>Lch / Rch become same set point or independent set.</li> </ul>               |

|     |                    | •+24dB to -103dB (0.125dB step),-∞dB                                                  |

|     |                    | <ul> <li>There are soft transition and soft mute functions.</li> </ul>                |

| 5   | 3 Band DRC         | •There are 3 band DRC.                                                                |

|     |                    | <ul> <li>It is possible to set the slope of compression level.</li> </ul>             |

| 6   | Post-scaler        | •Lch / Rch become same set point.                                                     |

|     |                    | •+48dB to -79dB (0.5dB step),-∞dB                                                     |

| 7   | Fine Post-scaler   | <ul> <li>Lch / Rch become independent set point.</li> </ul>                           |

|     |                    | •+0.7dB to -0.8dB (0.1dB step)                                                        |

| 8   | DC cut HPF         | •1 <sup>st</sup> order HPF                                                            |

|     |                    | •Cut off frequency fc : 1Hz                                                           |

| 9   | Hard Clipper       | •Lch / Rch become same set point.                                                     |

|     |                    | •Clip level : 0dB to -22.5dB (-0.1dB step)                                            |

Figure 31. DSP Block diagram

# RSTX Pin<sup>(Note 12) (Note 13)</sup>, MUTEX Pin function

| <br>            | ,                |                                |                                                                   |  |  |

|-----------------|------------------|--------------------------------|-------------------------------------------------------------------|--|--|

| RSTX<br>(29pin) | MUTEX<br>(30pin) | DSP block                      | Speaker output<br>(OUT1P, OUT1N, OUT2P, OUT2N)                    |  |  |

| Low             | Low              | Reset ON                       | High-Z_low <sup>(Note 14)</sup><br>(Low power consumption)        |  |  |

| High            | Low              | Normal operation<br>(Mute ON)  | High-Z_low <sup>(Note 14)</sup><br>(Mute ON) <sup>(Note 15)</sup> |  |  |

| High            | High             | Normal operation<br>(Mute OFF) | Normal operation<br>(Mute OFF)                                    |  |  |

| Low             | High             |                                | Don't use.                                                        |  |  |

(Note 12) When RSTX is set to low, internal registers are initialized. (Note 13) If  $V_{DVDD}$  is under 3V, RSTX is set to low once for 10ms(Min), and set to high again. Then DSP is needed to set parameter again. (Note 14) This means that all output transistors are OFF and output terminals are pulled down by 10kΩ (Typ).

(Note 15) Speaker output becomes High-Z low after elapse of PWM stop time after setting MUTEX low. Refer to PWM Sampling Frequency in next page for PWM stop time.

#### **PWM Sampling Frequency**

PWM sampling frequency of speaker output, Soft mute time, Soft start time and PWM stop time depend on sampling frequency (fs) of the digital audio signal. These transition times are changed by sending the data to select address 0x15[1:0].

| Sampling<br>frequency (fs) | PWM sampling<br>frequency | 0x15[1:0]<br>value | Soft mute<br>time | Soft start<br>time | PWM stop time |

|----------------------------|---------------------------|--------------------|-------------------|--------------------|---------------|

|                            |                           | 0x0                | 10.7ms            | 10.7ms             | 86ms          |

| 48kHz                      | 384kHz                    | 0x1                | 21.4ms            | 10.7ms             | 106ms         |

| 40KHZ                      | 304KHZ                    | 0x2                | 42.7ms            | 10.7ms             | 125ms         |

|                            |                           | 0x3                | 85.4ms            | 10.7ms             | 162ms         |

|                            | 352.8kHz                  | 0x0                | 11.7ms            | 11.7ms             | 93ms          |

| 44.1kHz                    |                           | 0x1                | 23.3ms            | 11.7ms             | 113ms         |

| 44. IKHZ                   |                           | 0x2                | 46.5ms            | 11.7ms             | 135ms         |

|                            |                           | 0x3                | 92.9ms            | 11.7ms             | 177ms         |

|                            |                           | 0x0                | 16.1ms            | 16.1ms             | 116ms         |

| 32 kHz                     | 256kHz                    | 0x1                | 32.1ms            | 16.1ms             | 148ms         |

| 32 KHZ                     | 200602                    | 0x2                | 64.1ms            | 16.1ms             | 178ms         |

|                            |                           | 0x3                | 128.1ms           | 16.1ms             | 241ms         |

Default = 0x3 \*Blue square means initial value.

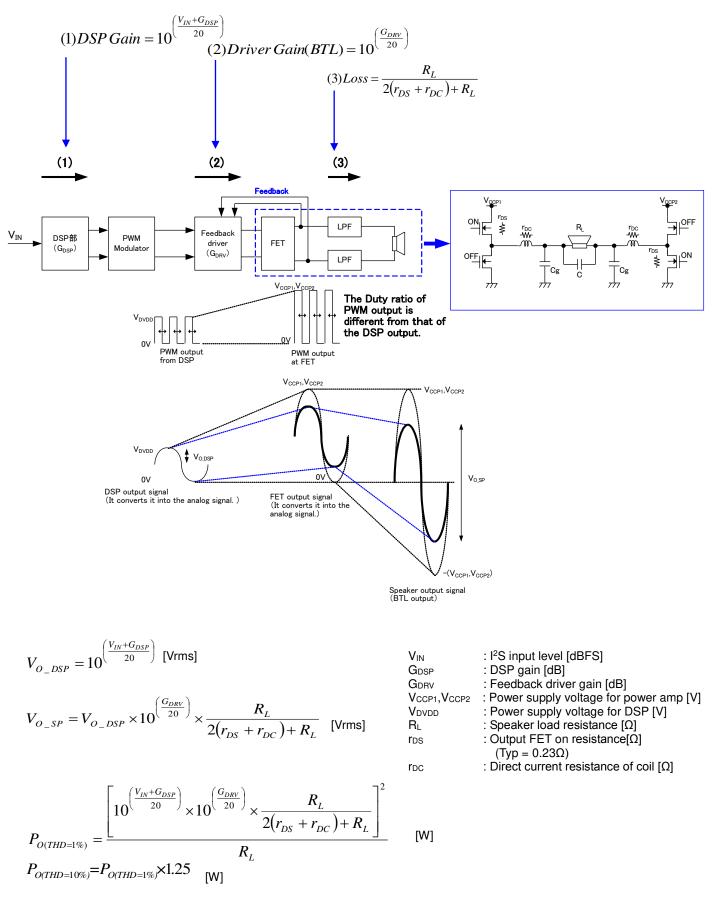

#### Setting Driver Gain (GDRV)

It can change the driver gain of the output FET driver part. Set it depending on speaker used because the maximum output level changes by speaker load impedance value.

When set the driver gain, change after setting MUTEX terminal to low (>PWM stop time). Pop noise may be occur if the driver gain is set while MUTEX=high.

Default = 0x03 \*Blue square means initial value.

| Select Address | Value | Driver Gain<br>G <sub>DRV</sub> (BTL) |

|----------------|-------|---------------------------------------|

| 0xF3[7:0]      | 0x03  | 26dB(Typ)                             |

| 0xF3[7:0]      | 0x0B  | 32dB(Typ)                             |

Regarding 0xF3 address,

Prohibit to set except data "0x03" and "0x0B" to address 0xF3.

The setting value is fixed by transmitting 0xF8=0x01. If the setting value of address 0xF3 is changed, certainly set 0xF8=0x01 again. In addition, Wait time more than 10ms is necessary after 0xF8=0x01 setting.

#### Setting of When Monaural output

When monaural output setting is applied as shown in Application Circuit Example3, set 0xF2 register during start-up (Refer to P.62 "7. The wake-up Procedure of power-up").

Setting 0xF2 = 0x0A, DC voltage protection function at the speaker of OUT2 side can be disabled, therefore it is possible to use Application Circuit Example3.

| Default = 0x02 *Blue square means initial value. |       |                   |  |  |  |  |  |

|--------------------------------------------------|-------|-------------------|--|--|--|--|--|

| Select Address                                   | Value | PWM Output Signal |  |  |  |  |  |

| 0xF2[7:0]                                        | 0x02  | Stereo            |  |  |  |  |  |

| 0xF2[7:0]                                        | 0x0A  | Monaural          |  |  |  |  |  |

Regarding 0xF2 address,

Prohibit to set except data "0x02" and "0x0A" to address 0xF2.

The setting value is fixed by transmitting 0xF8=0x01. If the setting value of address 0xF2 is changed, certainly set 0xF8=0x01 again. In addition, Wait time more than 10ms is necessary after 0xF8=0x01 setting.

# Level Diagram

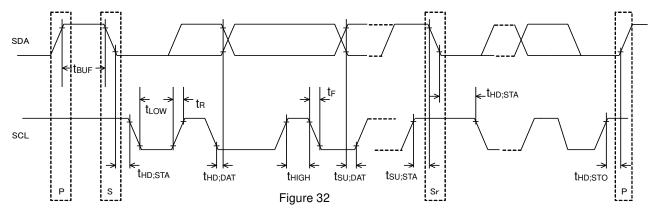

# 2 Wire Bus Control Signal Specification

1) Electrical Characteristics and Timing of Bus Line and I/O Stage

# SDA and SCL bus line characteristics<sup>(Note 17)</sup> (Unless otherwise specified Ta=25°C, V<sub>DVDD</sub>=3.3V)

|    | Parameter                                                                                       | Symbol       | High Spe    | Unit |      |

|----|-------------------------------------------------------------------------------------------------|--------------|-------------|------|------|

|    | Farameter                                                                                       | Symbol       | Min         | Max  | Unit |

| 1  | SCL clock frequency                                                                             | fscl         | 0           | 400  | kHz  |

| 2  | Bus free time between a STOP and START condition                                                | <b>t</b> BUF | 1.3         | -    | μs   |

| 3  | Hold time (repeated) START condition.<br>After this period, the first clock pulse is generated. | thd;sta      | 0.6         | -    | μs   |

| 4  | Low period of the SCL clock                                                                     | t∟ow         | 1.3         | -    | μs   |

| 5  | High period of the SCL clock                                                                    | tніgн        | 0.6         | -    | μs   |

| 6  | Set-up time for a repeated START condition                                                      | tsu;sta      | 0.6         | -    | μs   |

| 7  | Data hold time                                                                                  | thd;dat      | 0 (Note 16) | -    | μs   |

| 8  | Data set-up time                                                                                | tsu;dat      | 250         | -    | ns   |

| 9  | Rise time of both SDA and SCL signals                                                           | tR           | 20+0.1Cb    | 300  | ns   |

| 10 | Fall time of both SDA and SCL signals                                                           | t⊧           | 20+0.1Cb    | 300  | ns   |

| 11 | Set-up time for STOP condition                                                                  | tsu;sто      | 0.6         | -    | μs   |

| 12 | Capacitive load for each bus line                                                               | Cb           | -           | 400  | pF   |

The above-mentioned numerical values are all the values corresponding to V<sub>IHmin</sub> and the V<sub>ILmax</sub> level. (Note 16) To exceed an undefined area on the fall-edge of SCL (Refer to V<sub>IH</sub> min of the SCL signal), the transmitting set like SoC should internally offer the holding time of 300ns or more for the SDA signal.

(Note 17) SCL and SDA pin is not corresponding to threshold tolerance of 5V.

Use it within Input voltage 1 of the absolute maximum rating.

#### 2) Command Interface

2 wire Bus Control is used for command interface between host CPU. It not only writes but also it is possible to read it excluding a part of register. In addition to "Slave Address", set and write 1 byte of "Select Address" to read out the data. 2 wire bus Slave mode format is illustrated below.

|             | MSB LSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8 | MSB LSI        | 3 | MSB  | LSB | 3 |   | _                  |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|---|------|-----|---|---|--------------------|

| S           | Slave Address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | А | Select Address | Α | Data |     | Α | Ρ |                    |

|             | Figure 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |                |   |      |     |   |   |                    |

| A :<br>Sele | Slave Address :       Data of 8bit in total is sent with a bit of Read mode (high) or Write mode (low) after slave address (7bit) set by ADDR terminal. (MSB first)         A :       Acknowledge-bit will be added byte per byte in the data that acknowledge is sent and received. "low" will be sent and received when the data is correctly sent and received. There was no acknowledgement for "high".         Select Address :       Use 1byte of select address. (MSB first)         Data :       Sent and received data-byte data. (MSB first) |   |                |   |      |     |   |   | sent and received. |

| SD                          | A                                     | MS      | в 🛛 6       | X 5 X                   | _ <b></b>  |             | LSB       |                                    |     |

|-----------------------------|---------------------------------------|---------|-------------|-------------------------|------------|-------------|-----------|------------------------------------|-----|

| SC                          |                                       |         |             |                         |            |             |           |                                    |     |

| 3) Slave Add                | Start Conditi<br>SDA↓ SCL="H<br>dress |         |             | Figure 3                | 4          |             |           | Stop condition<br>A↑ SCL="High"    |     |

| •While AD<br>MSB            | DR Pin is "low'                       | ,       |             |                         |            |             | LSE       | 3                                  |     |

| A6                          | A5                                    | A4      | A3          | A2                      | A1         | A0          | R/W       | _                                  |     |

| 1                           | 0                                     | 0       | 0           | 0                       | 0          | 0           | 1/0       |                                    |     |

| •While AD<br>MSB            | DR Pin is "high                       | )"      |             |                         |            |             | LSE       | 3                                  |     |

| A6                          | A5                                    | A4      | A3          | A2                      | A1         | A0          | R/W       | _                                  |     |

| 1                           | 0                                     | 0       | 0           | 0                       | 0          | 1           | 1/0       |                                    |     |

| 4) Writing of<br>•Basic for |                                       | A Selec | ct Address  | Figure 3                | 5<br>ata A | Ρ           |           |                                    |     |

|                             | ement format                          |         |             | Master to S             |            |             | o Master  |                                    |     |

| S S                         | Slave Address                         | A Seleo | t Address   | A Da                    | ta 1 A     | Data 2      | A         | Data 3N                            | A P |

|                             |                                       |         | :           | Master to S<br>Figure 3 |            | Blave to    | o Master  |                                    |     |

|                             | I, the address<br>n the following     |         |             |                         |            |             |           | 0xD0 address at<br>cknowledge when |     |

| S S                         | Slave Address                         | A Re    | eq_Addr     | A Sele                  | ct Address | A P         |           |                                    |     |

| (ex.)                       | 0x80                                  |         | 0xD0        |                         | 0x20       |             |           |                                    |     |

| S S                         | Blave Address                         | A Da    | ta 1 A      | Data 2                  | Α          | A           | Data      | aNĀ P                              |     |

| (ex.)                       | 0x81                                  |         | 0x**        | 0x**                    |            |             | 0×        |                                    |     |

| :                           | Master to Slave                       | e,: SI  | ave to Mast | er,A:With A             | cknowledge | e,Ā:Without | Acknowled | dge                                |     |

|                             |                                       |         |             | Figure 3                | 7          |             |           |                                    |     |

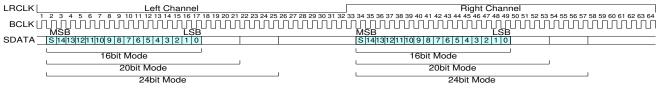

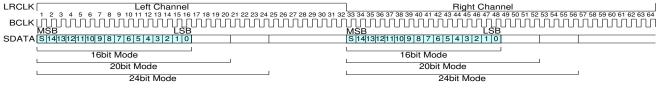

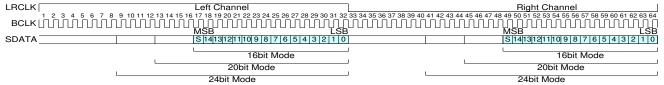

#### Format of Digital Audio Interface

- LRCLK: It is L/R Clock Input Signal It is available of 32kHz/44.1kHz/48kHz with those clocks (fs) that are same to the sampling frequency (fs). The data of the left channel and the right channel for one sample is input to this section.

- BCLK: It is Bit Clock Input Signal

It is used for the latch of data in every one bit by sampling frequency's 32 times frequency (32fs) or 48 times frequency (48fs) or 64 times sampling frequency (64fs). However if the 32fs is selected, the data length is held static of 16bit.

- SDATA: It is Data Input Signal It is amplitude data. Word length is different according to the resolution of the input digital audio signal. It is available of 16/ 20/ 24 bit.

The digital input format is available of  $I^2S$ , Left-justified and Right-justified formats. The figure below shows the timing chart of each transmission mode.

SDATAO: Audio Data Output After DSP Processing This output syncs with inputted LRCLK and BCLK. Output format is available of I<sup>2</sup>S format only.

#### BCLK Clock 64fs

# I<sup>2</sup>S 64fs Format

# Left-Justified 64fs Format

# **Right-Justified 64fs Format**

Figure 38

BCLK Clock 48fs

|                 | I <sup>2</sup> S 48fs Format<br>LRCLK Left Channel<br>1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 25<br>BCLK MSB<br>SDATA SIGNATION SI SIGNATION SIGNATION | Right Channel         9 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 1         1000000000000000000000000000000000000                                                                        |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | Left-Justified 48fs Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Right Channel         9 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48         1000000000000000000000000000000000000                                                                          |

|                 | Right-Justified 48fs Format         LRCLK       Left Channel         1 2 3 4 5 6 7 8 9 1011121314151617181920212223242526272825         BCLK       MSB         SDATA       SI44534211109981765141312110         16bit Mode       20bit Mode         24bit Mode       Figure 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Right Channel         9 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48         MSB         ISI [4]13[12[1][0] 8 [7]6 [5 [4] 3]2 [1]0         16bit Mode         20bit Mode         24bit Mode |

| BCLK Clock 32fs |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Right Channel                                                                                                                                                                                           |

|                 | BCLK A S A S A S A S A S A S A S A S A S A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 22 23 24 25 26 27 28 29 30 31 32 1<br>LSB                                                                                                                                                             |

|                 | Left-Justified 32fs Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                         |

|                 | Right-Justified 32fs Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Bight Channel                                                                                                                                                                                           |

Figure 40

### Format Setting for Digital Audio Interface

Set BCLK clock f<sub>s</sub>, word length and data format by transmitting command according to the inputted digital audio signal. SDATAO output word length is able to be set independently of input word length. It is available of I<sup>2</sup>S format only.

#### BCLK Clock

Default = 0x0 \*Blue square means initial value.