# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Gate Driver Providing Galvanic isolation Series Isolation voltage 2500Vrms 1ch Gate Driver Providing Galvanic Isolation

## BM60014FV-C

#### **General Description**

The BM60014FV-C is a gate driver with an isolation voltage of 2500Vrms, I/O delay time of 120ns, and minimum input pulse width of 70ns. It incorporates the fault signal output functions, Under-voltage Lockout (UVLO) function and Miller clamp function.

#### Features

- AEC-Q100 Qualified<sup>(Note1)</sup>

- Providing Galvanic Isolation

- Active Miller Clamping

- Fault signal output function

- Under-voltage Lockout function

- UL1577 Recognized:File No. E356010

- (Note1: Grade1)

#### Applications

- IGBT Gate Driver

- MOSFET Gate Driver

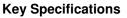

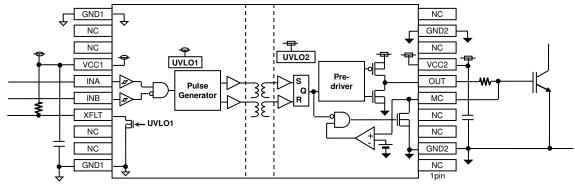

#### **Typical Application Circuits**

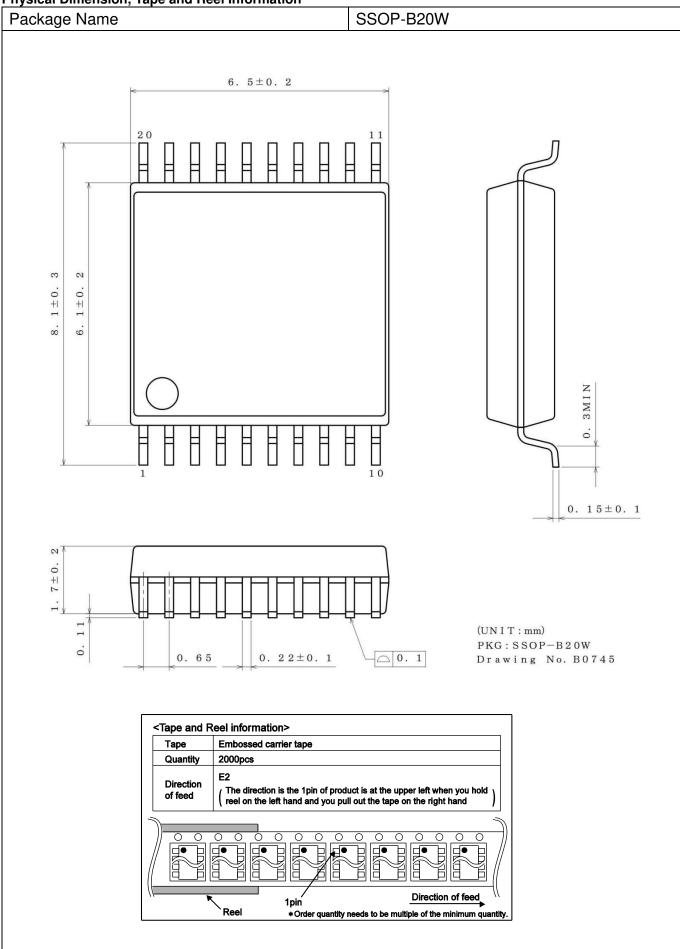

SSOP-B20W

Package

- Isolation voltage:

- Maximum gate drive voltage:

- I/O delay time:

2500Vrms 24V 120ns(Max) 70ns(Max)

Minimum input pulse width:

um input pulse width:

W(Typ) x D(Typ) x H(Max)

6.50mm x 8.10mm x 2.01mm

Figure 1. Application Circuits (IGBT Gate Driver)

Figure 2. Application Circuits (MOSFET Gate Driver)

OProduct structure : Silicon integrated circuit OThis product has no designed protection against radioactive rays

## **Recommended Range of External Constants**

| Pin Name | Symbol            | Recor | Unit |      |      |

|----------|-------------------|-------|------|------|------|

| Pin Name | Symbol            | Min.  | Тур. | Max. | Unit |

| VCC1     | C <sub>VCC1</sub> | 0.1   | 1.0  | -    | μF   |

| VCC2     | Cvcc2             | 0.33  | -    | -    | μF   |

#### **Pin Configurations**

|      |    | (TOP VIEW) | -  |      |

|------|----|------------|----|------|

| NC   | 1  | $\bigcirc$ | 20 | GND1 |

| GND2 | 2  | $\bigcirc$ | 19 | NC   |

| NC   | 3  |            | 18 | NC   |

| NC   | 4  |            | 17 | XFLT |

| MC   | 5  |            | 16 | INB  |

| OUT  | 6  |            | 15 | INA  |

| VCC2 | 7  |            | 14 | VCC1 |

| NC   | 8  |            | 13 | NC   |

| GND2 | 9  |            | 12 | NC   |

| NC   | 10 |            | 11 | GND1 |

|      |    |            |    |      |

## **Pin Descriptions**

| Pin No. | Pin Name | Function                     |

|---------|----------|------------------------------|

| 1       | NC       | No Connection                |

| 2       | GND2     | Output-side ground pin       |

| 3       | NC       | No Connection                |

| 4       | NC       | No Connection                |

| 5       | MC       | Output pin for Miller Clamp  |

| 6       | OUT      | Output pin                   |

| 7       | VCC2     | Output-side power supply pin |

| 8       | NC       | No Connection                |

| 9       | GND2     | Output-side ground pin       |

| 10      | NC       | No Connection                |

| 11      | GND1     | Input-side ground pin        |

| 12      | NC       | No Connection                |

| 13      | NC       | No Connection                |

| 14      | VCC1     | Input-side power supply pin  |

| 15      | INA      | Control input pin A          |

| 16      | INB      | Control input pin B          |

| 17      | XFLT     | Fault signal output pin      |

| 18      | NC       | No Connection                |

| 19      | NC       | No Connection                |

| 20      | GND1     | Input-side ground pin        |

#### Description of pins and cautions on layout of board

1) VCC1 (Input-side power supply pin) The VCC1 pin is a power supply pin on the input side. To suppress voltage fluctuations due to the current to drive internal transformers, connect a bypass capacitor between the VCC1 and the GND1 pins.

- 2) GND1 (Input-side ground pin) The GND1 pin is a ground pin on the input side.

- 3) VCC2 (Output-side positive power supply pin) The VCC2 pin is a power supply pin on the output side. To reduce voltage fluctuations due to OUT pin output current, connect a bypass capacitor between the VCC2 and the GND2 pins.

- 4) GND2 (Output-side ground pin) The GND2 pin is a ground pin on the output side.

- 5) INA, INB (Control input terminal)

The INA and INB pins are used to determine output logic.

| INB | INA | OUT |

|-----|-----|-----|

| Н   | L   | L   |

| Н   | Н   | L   |

| L   | L   | L   |

| L   | Н   | Н   |

#### 6) OUT (Output pin)

The OUT pin is used to drive the gate of a power device.

#### 7) MC (Output pin for Miller Clamp)

The MC pin is for preventing the increase in gate voltage due to the Miller current of the power device connected to the OUT pin. If the Miller Clamp function is not used, short-circuit the MC pin to the GND2 pin.

#### 8) XFLT (Fault signal output pin)

The XFLT pin is an open drain pin used to output a fault signal when a fault occurs (i.e., when the Under-voltage Lockout function (UVLO1) is activated).

| Conditions                                        | XFLT |

|---------------------------------------------------|------|

| While in normal operation                         | L    |

| When an Fault occurs<br>(When UVLO1 is activated) | Hi-Z |

#### Description of functions and examples of constant setting

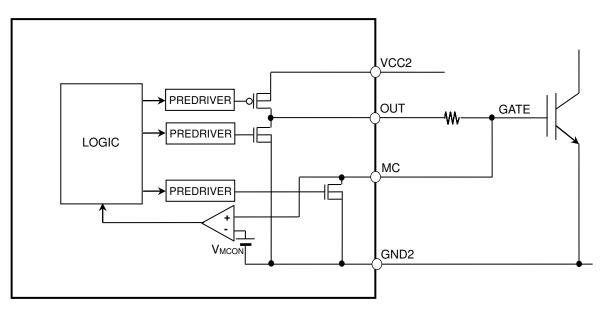

#### 1) Miller Clamp function

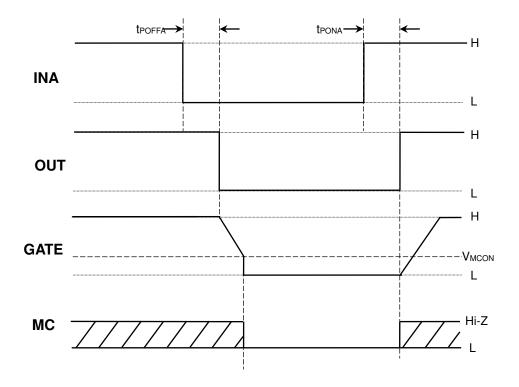

When INA=L and OUT pin voltage <  $V_{MCON}$  (typ 2V), the internal MOSFET of the MC pin is turned ON.

| INA | MC                          | Internal MOSFET of the MC pin |  |  |

|-----|-----------------------------|-------------------------------|--|--|

| L   | less than $V_{\text{MCON}}$ | ON                            |  |  |

| н   | Х                           | OFF                           |  |  |

Figure 3. Block diagram of Miller Clamp function.

Figure 4. Timing chart of Miller Clamp function

#### 2) Under-voltage Lockout (UVLO) function

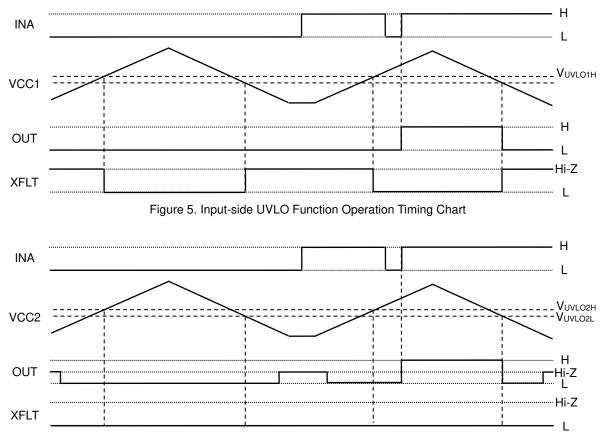

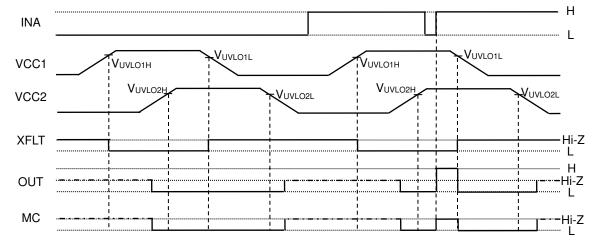

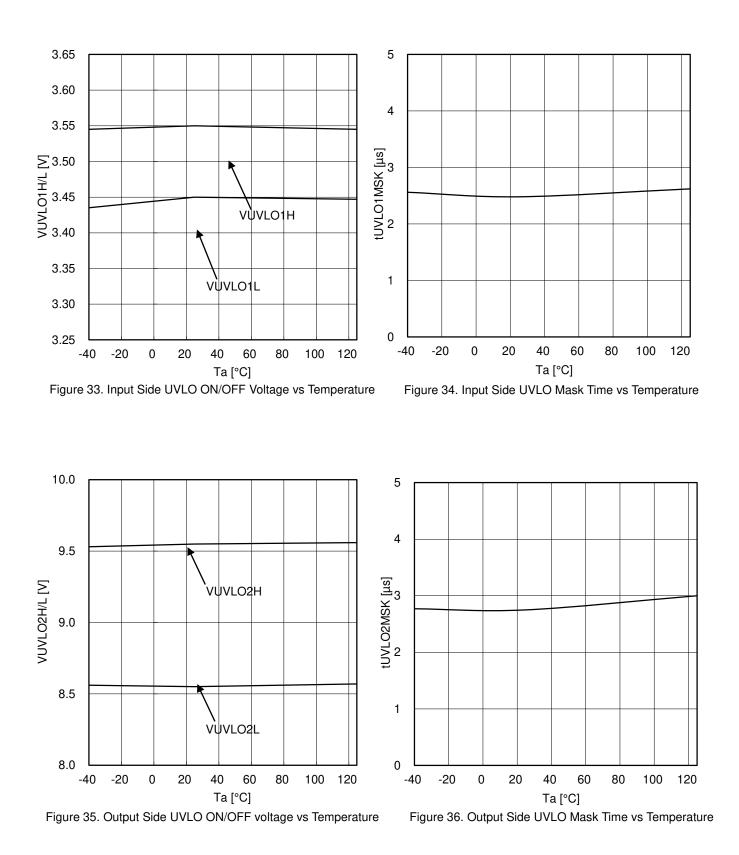

The BM60014FV-C incorporates the Under-voltage Lockout (UVLO) function both on the low and the high voltage sides. When the power supply voltage drops to the UVLO ON voltage (low voltage side typ 3.4V, high voltage side voltage typ 9.5V), the OUT pin will output the "L" signal. In addition, to prevent malfunctions due to noises, a mask time of tuvL01MSK (typ 2.5µs) and tuvL02MSK (typ 2.85µs) are set on both the low and the high voltage sides.

This IC does not have a function which feeds back the high voltage side state to the low voltage side. After the high voltage side UVLO is released, the input signal will take effect from the time after the input signal switches.

Figure 6. Output-side UVLO Function Operation Timing Chart

#### 3) I/O condition table

|     |                          |                  | Input            |             |             |             | Output |                  |  |

|-----|--------------------------|------------------|------------------|-------------|-------------|-------------|--------|------------------|--|

| No. | Status                   | V<br>C<br>C<br>1 | V<br>C<br>C<br>2 | I<br>N<br>B | I<br>N<br>A | O<br>U<br>T | M<br>C | X<br>F<br>L<br>T |  |

| 1   | VCC1UVLO                 | UVLO             | х                | х           | х           | L           | L      | Н                |  |

| 2   | VCC2UVLO                 | х                | UVLO             | х           | х           | L           | L      | L                |  |

| 3   | INB Active               | 0                | 0                | Н           | Х           | L           | L      | L                |  |

| 4   | Normal operation L input | 0                | 0                | L           | L           | L           | L      | L                |  |

| 5   | Normal operation H input | 0                | 0                | L           | Н           | H           | Hi-Z   | L                |  |

O: VCC1 or VCC2 > UVLO, X:Don't care

4) Power supply startup / shutoff sequence

-----: Since the VCC2 to GND2 pin voltage is low and the output MOS does not turn ON, the output pins become Hi-Z.

Figure 7. Power Supply Startup / Shutoff Sequence

#### **Absolute Maximum Ratings**

| Parameter                          | Symbol           | Limits                                     | Unit |

|------------------------------------|------------------|--------------------------------------------|------|

| Input-side supply voltage          | V <sub>CC1</sub> | -0.3~+7.0 <sup>(Note 1)</sup>              | V    |

| Output-side supply voltage         | V <sub>CC2</sub> | -0.3~+30.0 <sup>(Note 2)</sup>             | V    |

| INA pin input voltage              | VINA             | -0.3~+VCC1+0.3 or +7.0 <sup>(Note 3)</sup> | V    |

| INB pin input voltage              | V <sub>INB</sub> | -0.3~+VCC1+0.3 or +7.0 <sup>(Note1)</sup>  | V    |

| OUT pin output current (Peak 10µs) | Ioutpeak         | 5.0 <sup>(Note 3)</sup>                    | A    |

| XFLT pin output current            | IXFLT            | 10                                         | mA   |

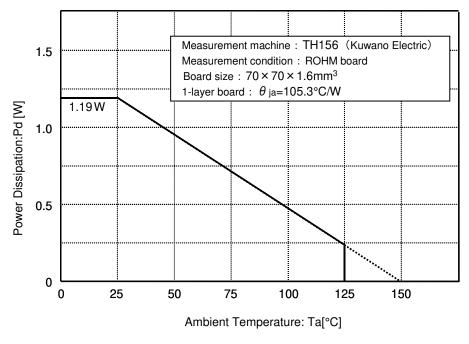

| Power dissipation                  | Pd               | 1.19 <sup>(Note 4)</sup>                   | W    |

| Operating temperature range        | Topr             | -40~+125                                   | °C   |

| Storage temperature range          | Tstg             | -55~+150                                   | °C   |

| Junction temperature               | Tjmax            | +150                                       | °C   |

(Note 1) Relative to GND1.

(Note 2) Relative to GND2.

(Note 2) Frequere to GND2. (Note 3) Should not exceed Pd and Tj=150°C (Note 4) Derate by 9.5mW/°C when operating above Ta=25°C. Mounted on a glass epoxy of 70mm × 70mm × 1.6mm.

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

#### **Recommended Operating Ratings**

| Parameter                  | Symbol                   | Min. | Max. | Units                    |

|----------------------------|--------------------------|------|------|--------------------------|

| Input-side supply voltage  | VCC1 <sup>(Note 5)</sup> | 4.5  | 5.5  | VCC1 <sup>(Note 5)</sup> |

| Output-side supply voltage | VCC2 <sup>(Note 6)</sup> | 10   | 24   | VCC2 <sup>(Note 6)</sup> |

(Note 5) Relative to GND1. (Note 6) Relative to GND2.

#### **Insulation Related Characteristics**

| Parameter                                     | Symbol           | Characteristic | Units |

|-----------------------------------------------|------------------|----------------|-------|

| Insulation Resistance (V <sub>IO</sub> =500V) | Rs               | >109           | Ω     |

| Insulation Withstand Voltage / 1min           | VISO             | 2500           | Vrms  |

| Insulation Test Voltage / 1sec                | V <sub>ISO</sub> | 3000           | Vrms  |

#### **Electrical Characteristics**

(Unless otherwise specified Ta=-40°C to 125°C, V cc1=4.5V to 5.5V, Vcc2=10V to 24V)

| Unless otherwise specified Tai<br>Parameter | Symbol              | Min.    | Typ. | Max.             | Unit  | Conditions                             |

|---------------------------------------------|---------------------|---------|------|------------------|-------|----------------------------------------|

| General                                     | Gymbol              | iviiri. | Typ. | Max.             | Onit  | Conditions                             |

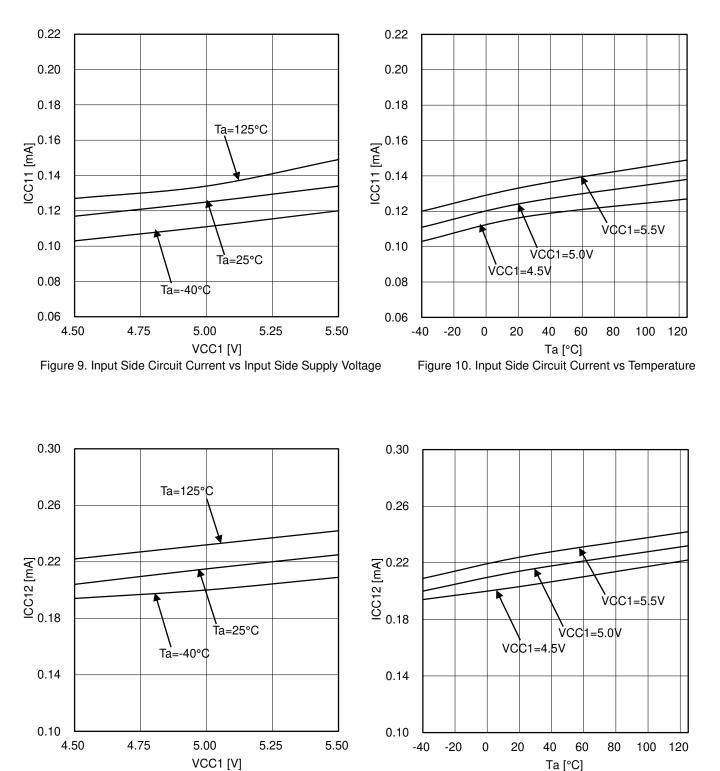

| Input side circuit current 1                | Icc11               | 0.06    | 0.14 | 0.22             | mA    |                                        |

| Input side circuit current 2                | ICC12               | 0.10    | 0.20 | 0.30             | mA    | INA =10kHz, Duty=50%                   |

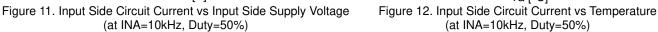

| Input side circuit current 3                | Icc13               | 0.15    | 0.30 | 0.45             | mA    | INA =20kHz, Duty=50%                   |

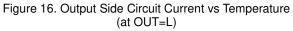

| Output side circuit current 1               | ICC21               | 0.26    | 0.44 | 0.62             | mA    | OUT=L                                  |

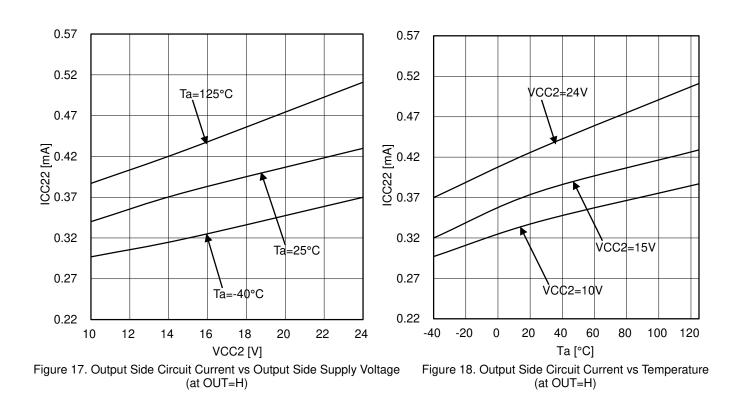

| Output side circuit current 2               | Icc22               | 0.22    | 0.38 | 0.57             | mA    | OUT=H                                  |

| Logic block                                 |                     |         | T    | I.               |       | Г <u> </u>                             |

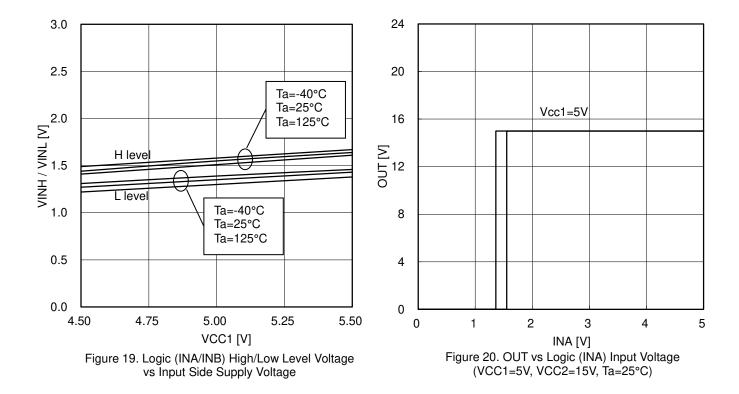

| Logic high level input voltage              | VINH                | 2.0     | -    | V <sub>CC1</sub> | V     | INA, INB                               |

| Logic low level input voltage               | VINL                | 0       | -    | 0.8              | V     | INA, INB                               |

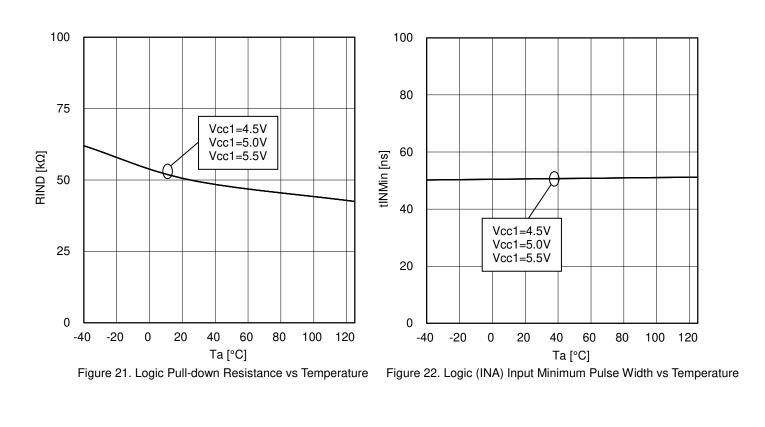

| Logic pull-down resistance                  | RIND                | 25      | 50   | 100              | kΩ    | INA, INB                               |

| Logic input minimum pulse width             | t <sub>INMIN</sub>  | -       | -    | 70               | ns    | INA, INB                               |

| Output                                      |                     |         |      |                  |       |                                        |

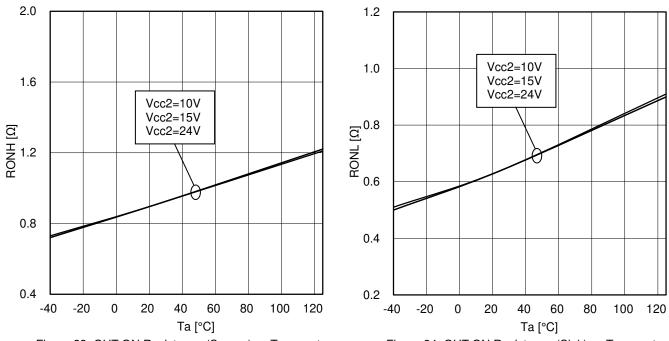

| OUT ON resistance (Source)                  | R <sub>ONH</sub>    | 0.4     | 0.9  | 2.0              | Ω     | Iout=-40mA                             |

| OUT ON resistance (Sink)                    | Ronl                | 0.2     | 0.6  | 1.3              | Ω     | Iout=40mA                              |

| OUT maximum current (Source)                | Іоитмахн            | 3.0     | 4.5  | -                | А     | VCC2=15V,<br>Guaranteed by design      |

| OUT maximum current (Sink)                  | IOUTMAXL            | 3.0     | 3.9  | -                | А     | VCC2=15V,<br>Guaranteed by design      |

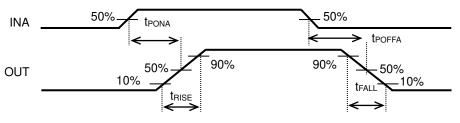

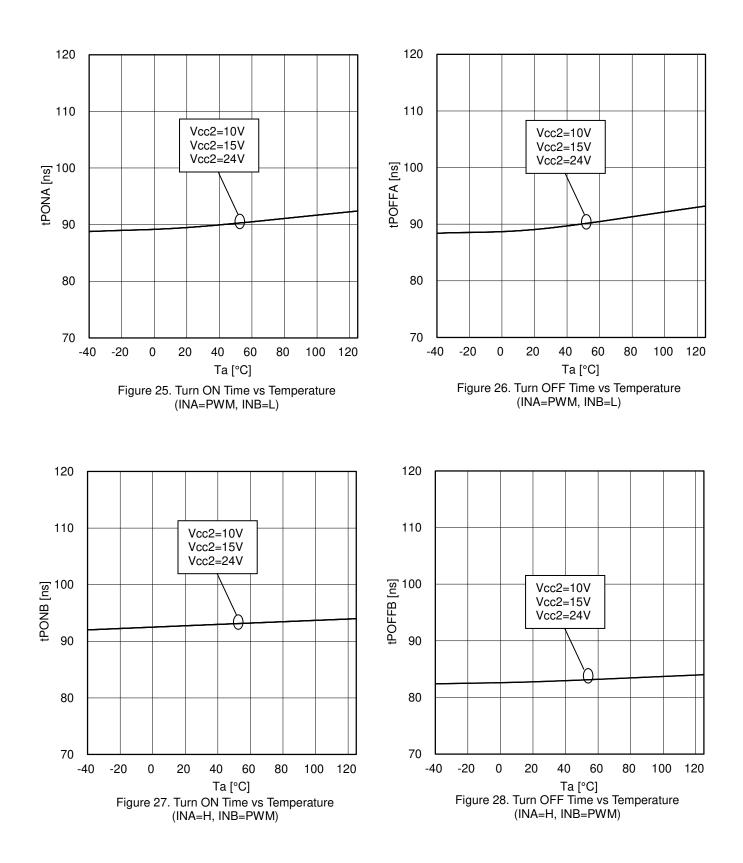

| Turn ON time                                | <b>t</b> PONA       | 70      | 90   | 120              | ns    | INA=PWM, INB=L                         |

| Turri ON time                               | <b>t</b> PONB       | 65      | 85   | 115              | ns    | INA=H, INB=PWM                         |

| Turn OFF time                               | <b>t</b> POFFA      | 70      | 90   | 120              | ns    | INA=PWM, INB=L                         |

|                                             | <b>t</b> POFFB      | 75      | 95   | 125              | ns    | INA=H, INB=PWM                         |

| Dranagation distortion                      | <b>t</b> PDISTA     | -25     | 0    | 25               | ns    | t <sub>POFFA</sub> — t <sub>PONA</sub> |

| Propagation distortion                      | <b>t</b> PDISTB     | -15     | 10   | 35               | ns    | t <sub>POFFB</sub> — t <sub>PONB</sub> |

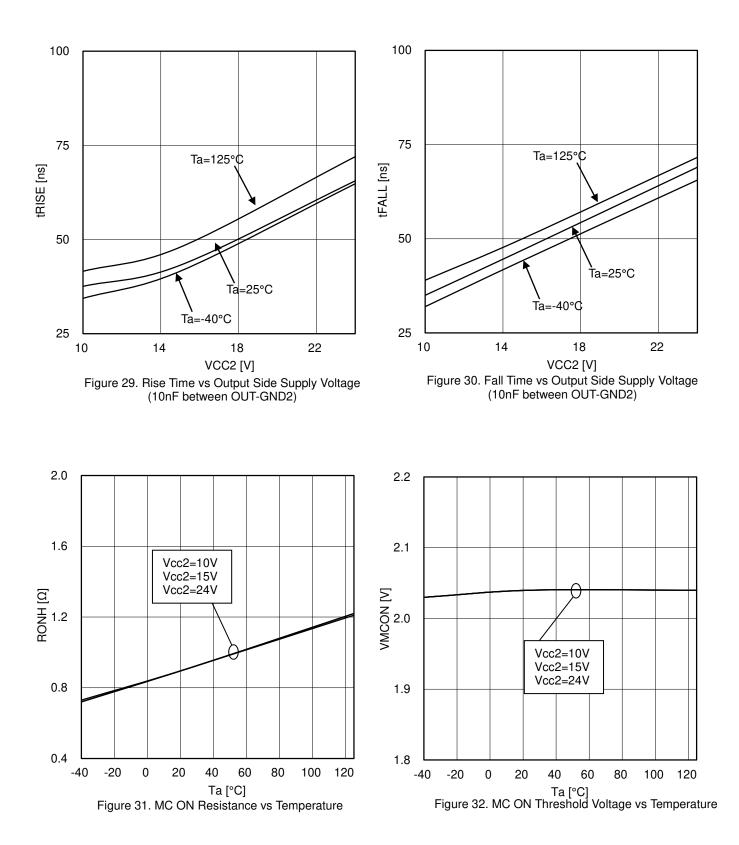

| Rise time                                   | trise               | -       | 50   | -                | ns    | 10nF between OUT-GND2                  |

| Fall time                                   | t <sub>FALL</sub>   | -       | 50   | -                | ns    | 10nF between OUT-GND2                  |

| MC ON resistance                            | RONMC               | 0.20    | 0.65 | 1.40             | Ω     | I <sub>MC</sub> =40mA                  |

| MC ON threshold voltage                     | V <sub>MCON</sub>   | 1.8     | 2    | 2.2              | V     |                                        |

| Common Mode Transient Immunity              | СМ                  | 100     | -    | -                | kV/μs | Guaranteed by design                   |

| Protection functions                        |                     |         |      |                  |       |                                        |

| VCC1 UVLO OFF voltage                       | V <sub>UVLO1H</sub> | 3.35    | 3.50 | 3.65             | V     |                                        |

| VCC1 UVLO ON voltage                        | VUVLO1L             | 3.25    | 3.40 | 3.55             | V     |                                        |

| VCC1 UVLO mask time                         | tuvlo1msk           | 1.0     | 2.5  | 5.0              | μs    |                                        |

| VCC2 UVLO OFF voltage                       | VUVLO2H             | 9.0     | 9.5  | 10.0             | V     |                                        |

| VCC2 UVLO ON voltage                        | VUVLO2L             | 8.0     | 8.5  | 9.0              | V     |                                        |

| VCC2 UVLO mask time                         | tuvlo2msk           | 1.00    | 2.85 | 5.00             | μs    |                                        |

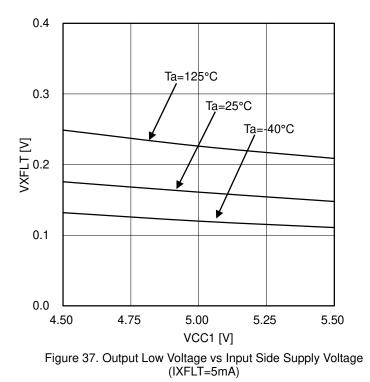

| XFLT output L voltage                       | VXFLT               | _       | 0.10 | 0.25             | V     | I <sub>XFLT</sub> =5mA                 |

Figure 8. IN-OUT Timing Chart

UL1577 Ratings Table Following values are described in UL Report.

| Parameter                               | Values | Units | Conditions       |

|-----------------------------------------|--------|-------|------------------|

| Side 1 (Input Side) Circuit Current     | 0.14   | mA    | VCC1=5.0V, OUT=L |

| Side 2 (Output Side) Circuit Current    | 0.44   | mA    | VCC2=V, OUT=L    |

| Side 1 (Input Side) Consumption Power   | 0.7    | mW    | VCC1=5.0V, OUT=L |

| Side 2 (Output Side) Consumption Power  | 6.6    | mW    | VCC2=15V, OUT=L  |

| Isolation Voltage                       | 2500   | Vrms  |                  |

| Maximum Operating (Ambient) Temperature | 125    | °C    |                  |

| Maximum Junction Temperature            | 150    | °C    |                  |

| Maximum Strage Temperature              | 150    | °C    |                  |

| Maximum Data Transmission Rate          | 2.5    | MHz   |                  |

#### **Typical Performance Curves**

Figure 15. Output Side Circuit Current vs Output Side Supply Voltage (at OUT=L)

Figure 23. OUT ON Resistance (Source) vs Temperature

Figure 24. OUT ON Resistance (Sink) vs Temperature

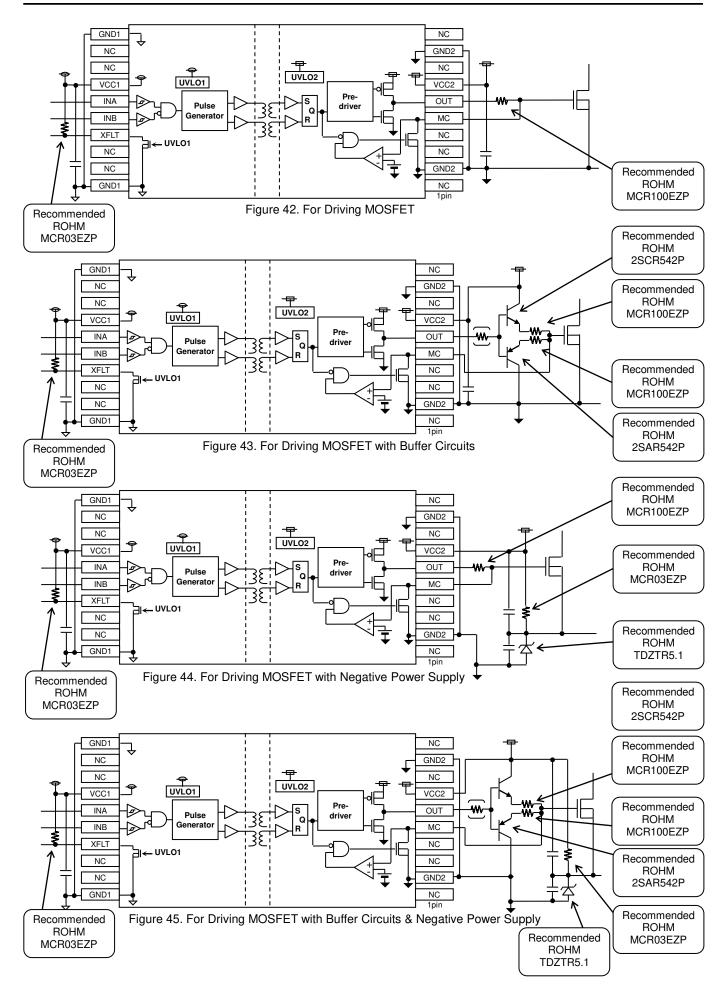

#### Selection of Components Externally Connected GND1 NC Ĵ NC GND2 P NC NC ዋ UVLO2 ኇ UVLO1 VCC1 VCC2 Pre-INA ✐ OUT Pulse driver Q Generato INB MC D R XFLT NC UVLO1 NC NC NC GND2 Recommended ROHM GND1 NC MCR100EZP 1pin Recommended Figure 38. For Driving IGBT ROHM MCR03EZP Recommended ROHM 2SCR542P GND1 NC Ĵ NC GND2 Recommended 于 UVLO2 ROHM NC NC <del>ि</del> UVLO1 MCR100EZP Ĵ VCC1 VCC2 Pre-INA ₩ ✐ OUT Pulse drive Q Generato INB R MC ₽ ş 7 XFLT NC Recommended UVLO1 ∍ו∢ ROHM NC NC MCR100EZP NC GND2 GND1 NC Recommended 1pir ROHM Figure 39. For Driving IGBT with Buffer Circuits 2SAR542P Recommended ROHM MCR03EZP Recommended ROHM GND1 NC Ĵ MCR100EZP NC GND2 ſ P NC NC -<del>♀</del> UVLO1 UVLO2 f VCC1 VCC2 Recommended Pre ROHM INA OUT Pulse drive MCR03EZP Generato INB MC ✐ R Ş XFLT NC UVLO1 Ы NC NC Recommended NC GND2 ROHM GND1 NC TDZTR5.1 1pir Figure 40. For Driving IGBT with Negative Power Supply Recommended Recommended ROHM ROHM MCR03EZP 2SCR542P GND1 NC Recommended Ĵ ROHM NC GND2 MCR100EZP NC NC UVL01 F VCC1 VCC2 Recommended Pre ₩ INA OUT ✐ Pulse drive ROHM G Generator INB ✐ MC MCR100EZP XFLT NC Recommended NC NC ROHM NC GND2 2SAR542P GND1 NC 1pin Recommended Recommended Figure 41. For Driving IGBT with Buffer Circuits & Negative Power Supply ROHM ROHM Recommended MCR03EZP MCR03EZP ROHM TDZTR5.1

#### **Power Dissipation**

Figure 46. SSOP-B20W Derating Curve

#### **Thermal Design**

Please make sure that the IC's chip temperature Tj is not over 150°C, while considering the IC's power consumption (W), package power (Pd) and ambient temperature (Ta). When Tj=150°C is exceeded, the function as a semiconductor will not operate and some problems (ex. Abnormal operation of various parasitic elements and increasing of leak current) occur. Constant use under these circumstances leads to deterioration and eventually IC may destruct. Tjmax=150°C must be strictly followed under all circumstances.

## I/O Equivalent Circuits

| Pin No | Name                        | I/O equivalence circuits |

|--------|-----------------------------|--------------------------|

|        | Function                    | I/O equivalence circuits |

| 1      | OUT                         |                          |

|        | Output pin                  |                          |

| 2      | MC                          |                          |

|        | Output pin for Miller clamp |                          |

| 3      | INA                         |                          |

|        | Control input pin A         |                          |

|        | INB                         |                          |

|        | Control input pin B         |                          |

| 4      | XFLT                        |                          |

|        | Fault signal output pin     |                          |

#### **Operational Notes**

#### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply terminals.

#### 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

#### 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

#### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

#### 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded, the rise in temperature of the chip may result in deterioration of the properties of the chip. The absolute maximum rating of the Pd stated in this specification is when the IC is mounted on a 70mm x 1.6mm glass epoxy board. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the Pd rating.

#### 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

#### 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

#### 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

#### 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

#### 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

#### **Operational Notes – continued**

#### **Unused Input Terminals** 11.

Input terminals of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input terminals should be connected to the power supply or ground line.

#### 12. **Regarding Input Pins of the IC**

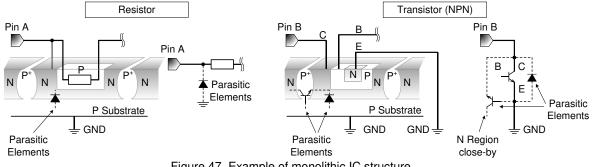

This monolithic IC contains P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode. When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

#### Figure 47. Example of monolithic IC structure

#### 13. **Ceramic Capacitor**

When using a ceramic capacitor, determine the dielectric constant considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

#### 14. Area of Safe Operation (ASO)

Operate the IC such that the output voltage, output current, and power dissipation are all within the Area of Safe Operation (ASO).

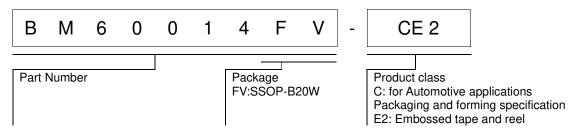

#### **Ordering Information**

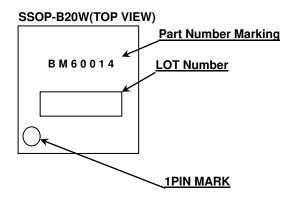

#### **Marking Diagrams**

#### Physical Dimension, Tape and Reel Information