Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# For Air-Conditioner Fan Motor

# 3-Phase Brushless Fan Motor Driver

# **BM6205FS**

### **General Description**

This motor driver IC adopts PrestoMOS™ as the output transistor, and put in a small full molding package with the 120° square wave commutation controller chip and the high voltage gate driver chip. The protection circuits for overcurrent, overheating, under voltage lock out and the high voltage bootstrap diode with current regulation are built-in. It provides optimum motor drive system and downsizing the built-in PCB of the motor.

### **Features**

- 600V PrestoMOS™ built-in

- Output current 2.5A

- Bootstrap operation by floating high side driver (including diode)

- 120° square wave commutation logic

- PWM control

- Rotational direction switch

- FG signal output with pulse number switch (4 or 12)

- VREG output (5V/30mA)

- Protection circuits provided: CL, OCP, TSD, UVLO, MLP and the external fault input

- Fault output (open drain)

## **Applications**

Air conditioners; air purifiers; water pumps; dishwashers; washing machines

# **Key Specifications**

Output MOSFET Voltage: 600V Driver Output Current (DC): ±2.5A (Max) Driver Output Current (Pulse): ±4.0A (Max) Output MOSFET DC On Resistance: 1.7Ω (Typ) Duty Control Voltage Range: 2.1V to 5.4V -20°C to +100°C Operating Case Temperature: Junction Temperature: +150°C ■ Power Dissipation: 3.00W

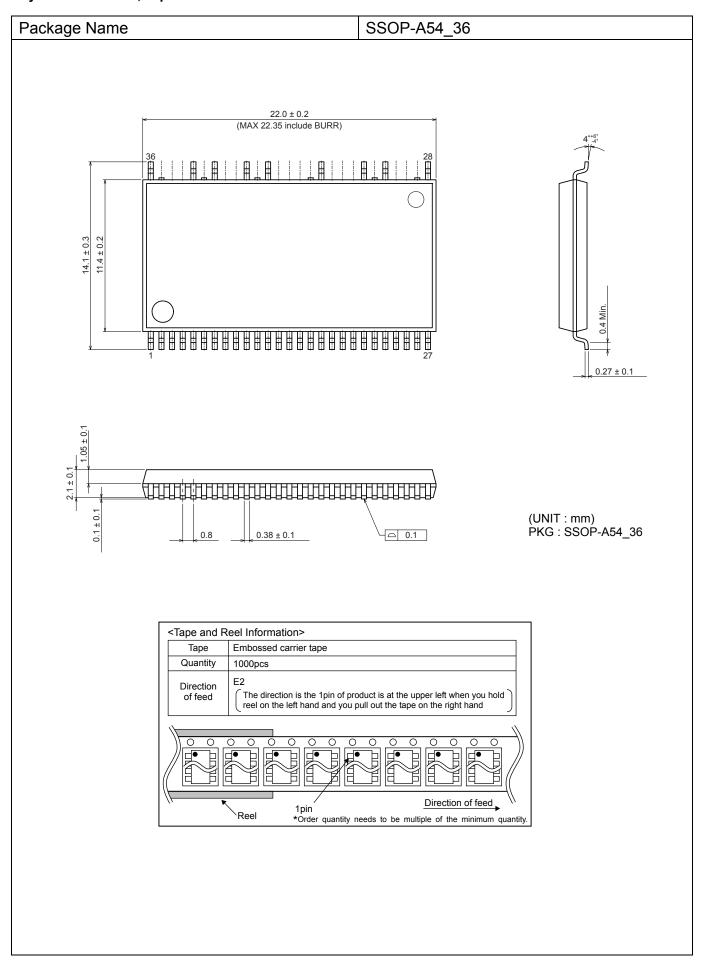

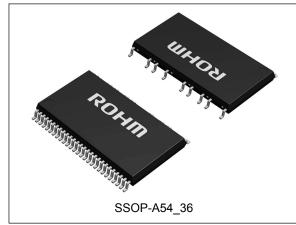

# Package

SSOP-A54\_36

W (Typ) x D (Typ) x H (Max) 22.0 mm x 14.1 mm x 2.4 mm

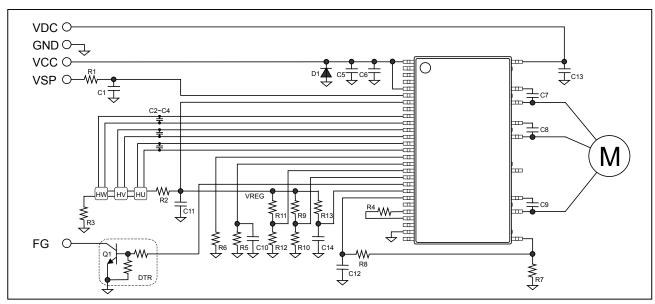

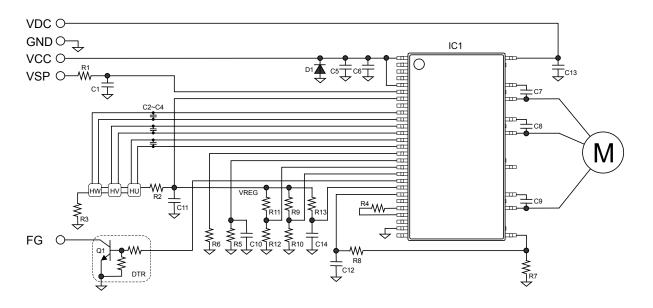

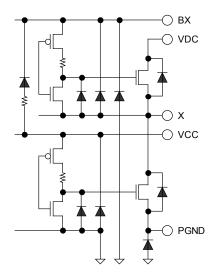

# **Typical Application Circuit**

Figure 1. Application Circuit Example

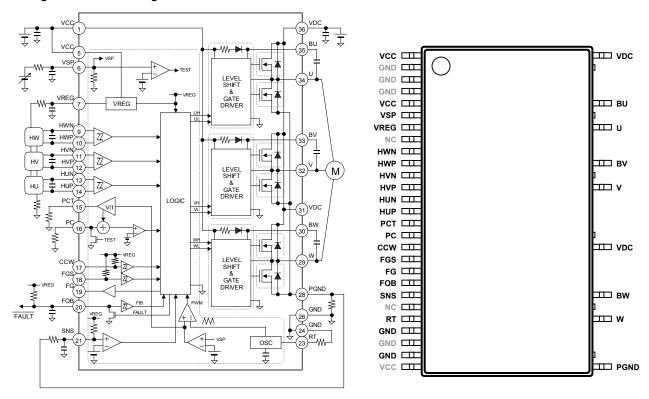

# **Block Diagram and Pin Configuration**

Figure 2. Block Diagram

Figure 3. Pin Configuration

# Pin Descriptions (NC: No Connection)

| Pin | Name | Function                         | Pin | Name | Function                      |

|-----|------|----------------------------------|-----|------|-------------------------------|

| 1   | VCC  | Low voltage power supply         | 36  | VDC  | High voltage power supply     |

| 2   | GND  | Ground                           | -   | VDC  |                               |

| 3   | GND  | Ground                           |     |      |                               |

| 4   | GND  | Ground                           |     |      |                               |

| 5   | VCC  | Low voltage power supply         | 35  | BU   | Phase U floating power supply |

| 6   | VSP  | Duty control voltage input pin   | -   | U    |                               |

| 7   | VREG | Regulator output                 | 34  | U    | Phase U output                |

| 8   | NC   |                                  |     |      |                               |

| 9   | HWN  | Hall input pin phase W-          |     |      |                               |

| 10  | HWP  | Hall input pin phase W+          | 33  | BV   | Phase V floating power supply |

| 11  | HVN  | Hall input pin phase V-          | -   | V    |                               |

| 12  | HVP  | Hall input pin phase V+          | 32  | V    | Phase V output                |

| 13  | HUN  | Hall input pin phase U-          |     |      |                               |

| 14  | HUP  | Hall input pin phase U+          |     |      |                               |

| 15  | PCT  | VSP offset voltage output pin    |     |      |                               |

| 16  | PC   | PWM switching arm setting pin    | -   | VDC  |                               |

| 17  | CCW  | Direction switch (H:CCW)         | 31  | VDC  | High voltage power supply     |

| 18  | FGS  | FG pulse # switch (H:12, L:4)    |     |      |                               |

| 19  | FG   | FG signal output                 |     |      |                               |

| 20  | FOB  | Fault signal output (open drain) |     |      |                               |

| 21  | SNS  | Over current sense pin           | 30  | BW   | Phase W floating power supply |

| 22  | NC   |                                  | -   | W    |                               |

| 23  | RT   | Carrier frequency setting pin    | 29  | W    | Phase W output                |

| 24  | GND  | Ground                           |     |      |                               |

| 25  | GND  | Ground                           |     |      |                               |

| 26  | GND  | Ground                           | -   | PGND |                               |

| 27  | VCC  | Low voltage power supply         | 28  | PGND | Ground (current sense pin)    |

Note) All pin cut surfaces visible from the side of package are no connected, except the pin number is expressed as a "-".

# **Description of Blocks**

## 1. Commutation Logic

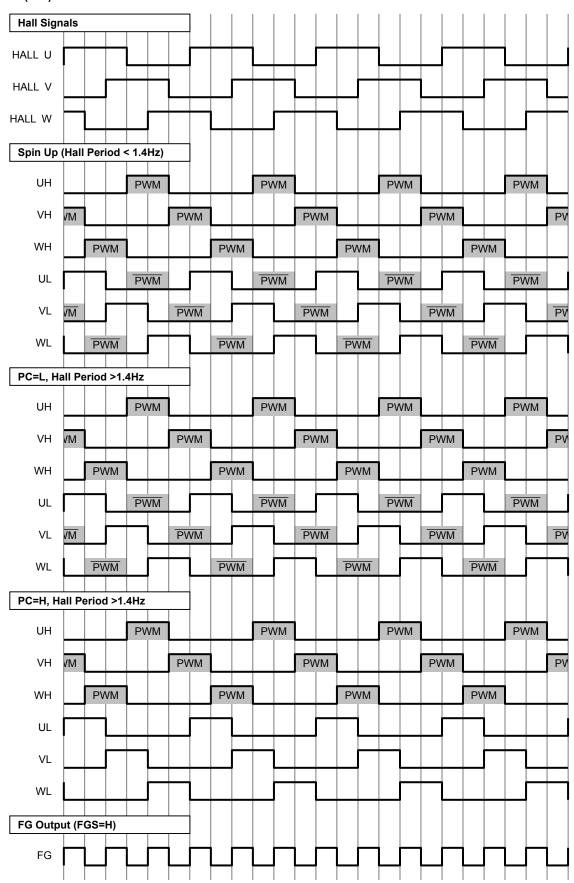

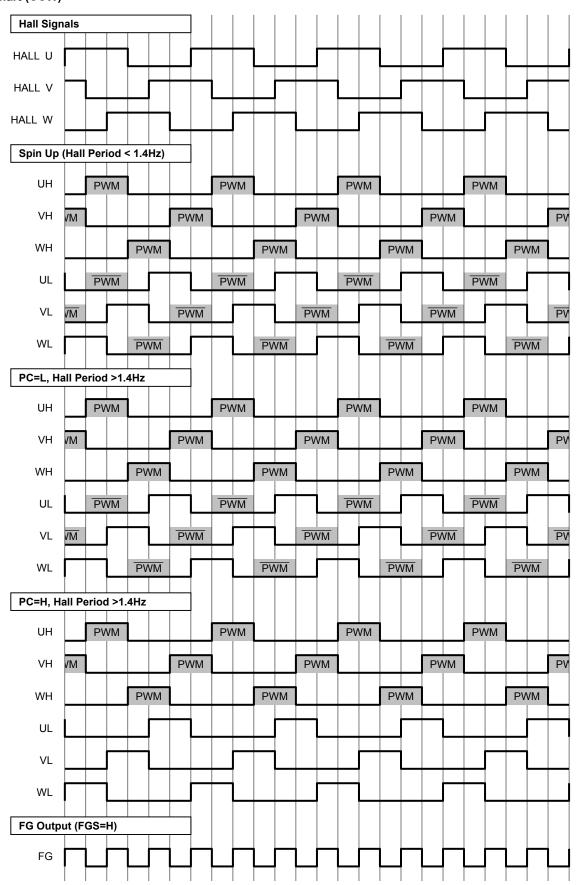

When the hall frequency is about 1.4-Hz or less (e.g. when the motor starts up), or PC pin is "L", the commutation mode is 120° square wave drive with upper and lower switching (synchronous switching). The controller monitors the hall frequency, and switches to upper switching when the hall frequency reaches or exceeds about 1.4-Hz over four consecutive cycles and PC pin is "H". Refer to the timing charts in figures 12 and 13.

| HU | HV | HW | UH  | VH  | WH  | UL  | VL  | WL  |

|----|----|----|-----|-----|-----|-----|-----|-----|

| Н  | L  | Н  | L   | PWM | L   | Н   | PWM | L   |

| Н  | L  | L  | L   | L   | PWM | Н   | L   | PWM |

| Н  | Н  | L  | L   | L   | PWM | L   | Н   | PWM |

| L  | Н  | L  | PWM | L   | L   | PWM | Н   | L   |

| L  | Н  | Н  | PWM | L   | L   | PWM | L   | Н   |

| L  | L  | Н  | L   | PWM | L   | L   | PWM | Н   |

Table 1. 120° commutation (synchronous switching) truth table

# 2. Duty Control

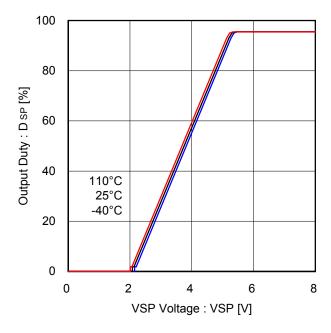

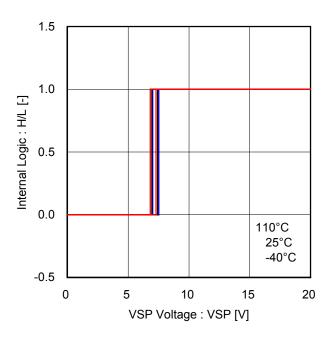

The switching duty can be controlled by forcing DC voltage with value from  $V_{SPMIN}$  to  $V_{SPMAX}$  to the VSP pin. When the VSP voltage is higher than  $V_{SPTST}$ , the controller forces PC pin voltage to ground (Testing mode, maximum duty and synchronous switching). The VSP pin is pulled down internally by a 200 k $\Omega$  resistor. Therefore, note the impedance when setting the VSP voltage with a resistance voltage divider.

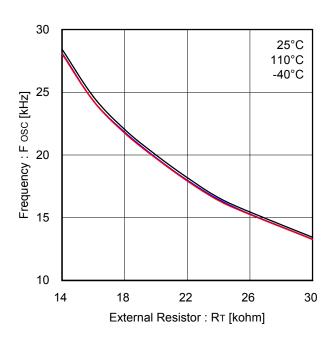

## 3. Carrier Frequency Setting

The carrier frequency setting can be freely adjusted by connecting an external resistor between the RT pin and ground. The RT pin is biased to a constant voltage, which determines the charge current to the internal capacitor. Carrier frequencies can be set within a range from about 16 kHz to 50 kHz. Refer to the formula to the right.

$$f_{OSC}[kHz] = \frac{400}{R_T[kohm]}$$

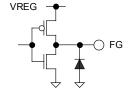

# 4. FG Signal Output

The number of FG output pulses can be switched in accordance with the number of poles and the rotational speed of the motor. The FG signal is output from the FG pin. The 12-pulse signal is generated from the three hall signals (exclusive NOR), and the 4-pulse signal is the same as hall U signal. It is recommended to pull up FGS pin to VREG voltage when malfunctioning because of the noise.

| FGS | No. of pulse |  |  |  |  |

|-----|--------------|--|--|--|--|

| Н   | 12           |  |  |  |  |

| L   | 4            |  |  |  |  |

# 5. Direction of Motor Rotation Setting

The direction of rotation can be switched by the CCW pin. When CCW pin is "H" or open, the motor rotates at CCW direction. It is recommended to pull up CCW pin to VREG voltage when malfunctioning because of the noise.

| CCW | Direction |

|-----|-----------|

| Н   | CCW       |

| L   | CW        |

# 6. Hall Signal Comparator

The hall comparator provides voltage hysteresis to prevent noise malfunctions. The bias current to the hall elements should be set to the input voltage amplitude from the element, at a value higher than the minimum input voltage,  $V_{HALLMIN}$ . We recommend connecting a ceramic capacitor with value from 100 pF to 0.01  $\mu$ F, between the differential input pins of the hall comparator. Note that the bias to hall elements must be set within the common mode input voltage range  $V_{HALLCM}$ .

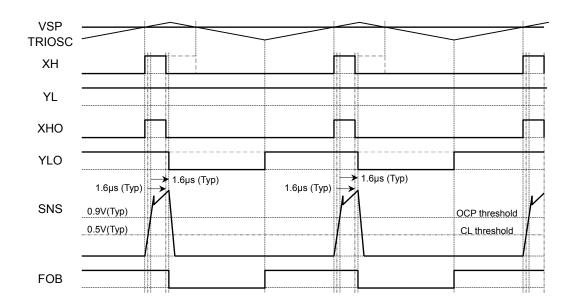

### 7. Output Duty Pulse Width Limiter

Pulse width duty is controlled during PWM switching in order to ensure the operation of internal power transistor. The controller doesn't output pulse of less than  $T_{MIN}$  (0.8 $\mu$ s minimum), nor output a duty pulse of  $D_{MAX}$  or more. Dead time is forcibly provided to prevent internal power transistors to turn-on simultaneously in upper and lower side in gate driver output (for example, UH and UL) of each arm. This will not overlap the minimum time  $T_{DT}$  (1.6 $\mu$ s minimum). Because of this, the maximum duty of the synchronous switching mode is 84% (typical).

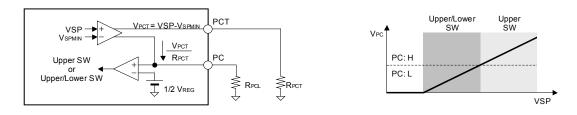

# 8. PWM Switching Arm Setting

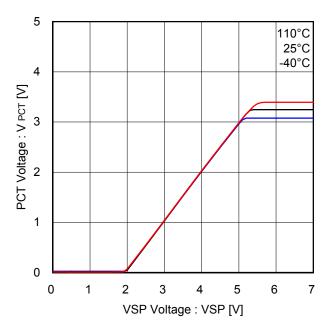

The PWM switching arm can choose one from the synchronous switching or the upper switching. When PC is "L", the switching mode is the synchronous. And also when PC is "H", the switching mode is the upper switching. However, when the hall cycle is about 1.4-Hz or less, the switching mode keeps the synchronous even if PC is "H". When the PWM control is entering to the testing mode, the controller forces PC pin voltage to ground and synchronous switching mode. Therefore, when PC pin pull-up to VREG pin, at least a resistor with a value 10k  $\Omega$  or more. The VSP offset voltage (Figure 32) is buffered to PCT pin, to connect an external resistor between PCT pin and ground. The internal bias current is determined by PCT voltage and the resistor value -  $V_{PCT}$  /  $R_{PCT}$  -, and mixed to PC pin. Because you can freely determine the slope by the resistance ratio of PC pin and PCT pin, which allows you to adjust the voltage command value to switch the synchronous switching or the upper switching. Please select the  $R_{PCT}$  value from 50 k $\Omega$  to 200 k $\Omega$  in the range on the basis of 100 k $\Omega$ , because the PCT pin current capability is a 100  $\mu$ A or less.

Figure 4. PWM Switching Arm Setting

### 9. Current Limiter (CL) Circuit and Overcurrent Protection (OCP) Circuit

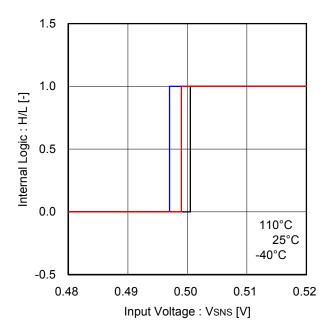

The current limiter circuit can be activated by connecting a low value resistor for current detection between the output stage ground (PGND) and the controller ground (GND). When the SNS pin voltage reaches or surpasses the threshold value ( $V_{SNS}$ , 0.5V typical), the controller forces all the upper switching arm inputs low (UH, VH, WH = L, L, L), thus initiating the current limiter operation. When the SNS pin voltage swings below the ground, it is recommended to insert a resistor - 1.5 k $\Omega$  or more - between SNS pin and PGND pin to prevent malfunction. Since this limiter circuit is not a latch type, it returns to normal operation - synchronizing with the carrier frequency - once the SNS pin voltage falls below the threshold voltage. A filter is built into the overcurrent detection circuit to prevent malfunctions, and does not activate when a short pulse of less than  $T_{MASK}$  is present at the input.

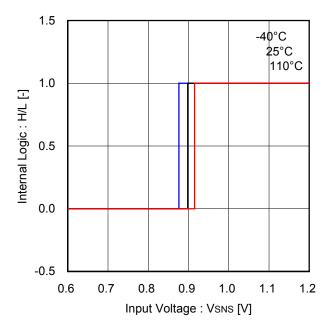

When the SNS pin voltage reaches or surpasses the threshold value ( $V_{OVER}$ , 0.9V typical) because of the power fault or the short circuit except the ground fault, the gate driver outputs low to the gate of all output MOSFETs, thus initiating the overcurrent protection operation. Since this protection circuit is also not a latch type, it returns to normal operation synchronizing with the carrier frequency.

### 10. Under Voltage Lock Out (UVLO) Circuit

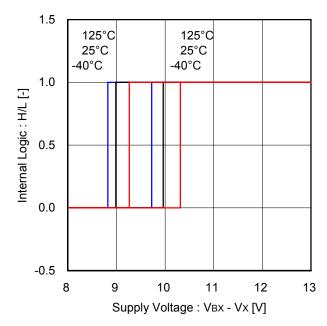

To secure the lowest power supply voltage necessary to operate the controller and the driver, and to prevent under voltage malfunctions, the UVLO circuits are independently built into the upper side floating driver, the lower side driver and the controller. When the supply voltage falls to  $V_{UVL}$  or below, the controller forces driver outputs low. When the voltage rises to  $V_{UVH}$  or above, the UVLO circuit ends the lockout operation and returns the chip only after 32 carrier periods (1.6ms for the default 20kHz frequency) to normal operation. Even if the controller returns to normal operation, the output begins from the following control input signal.

The voltage monitor circuit (4.0V nominal) is built-in for the VREG voltage. Therefore, the UVLO circuit does not release operation when the VREG voltage rising is delayed behind the VCC voltage rising even if VCC voltage becomes  $V_{UVH}$  or more.

# 11. Thermal Shutdown (TSD) Circuit

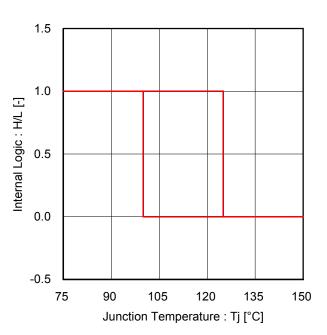

The TSD circuit operates when the junction temperature of the controller exceeds the preset temperature (125°C nominal). At this time, the controller forces all driver outputs low. Since thermal hysteresis is provided in the TSD circuit, the chip returns to normal operation when the junction temperature falls below the preset temperature (100°C nominal). The TSD circuit is designed only to shut the IC off to prevent thermal runaway. It is not designed to protect the IC or guarantee its operation in the presence of extreme heat. Do not continue to use the IC after the TSD circuit is activated, and do not use the IC in an environment where activation of the circuit is assumed.

Moreover, it is not possible to follow the output MOSFET junction temperature rising rapidly because it is a gate driver chip that monitors the temperature and it is likely not to function effectively.

# 12. Motor Lock Protection (MLP) Circuit

When the controller detects the motor locking during fixed time of 4 seconds nominal when each edge of the hall signal doesn't input either, the controller forces all driver outputs low under a fixed time 20 seconds nominal, and self-returns to normal operation. This circuit is enabled if the voltage force to VSP is over the duty minimum voltage  $V_{SPMIN}$ , and note that the motor cannot start up when the controller doesn't detect the motor rotation by the minimum duty control. Even if the edge of the hall signal is inputted within range of the OFF state by this protection circuit, it is ignored. But if the VSP is forced to ground level once, the protection can be canceled immediately.

## 13. Hall Signal Wrong Input Detection

Hall element abnormalities may cause incorrect inputs that vary from the normal logic. When all hall input signals go high or low, the hall signal wrong input detection circuit forces all driver outputs low. And when the controller detects the abnormal hall signals continuously for four times or more motor rotation, the controller forces all driver outputs low and latches the state. It is released if the duty control voltage VSP is forced to ground level once.

# 14. Internal Voltage Regulator

The internal voltage regulator VREG is output for the bias of the hall element and the phase control setting. However, when using the VREG function, be aware of the  $I_{\text{OMAX}}$  value. If a capacitor is connected to the ground in order to stabilize output, a value of 1  $\mu\text{F}$  or more should be used. In this case, be sure to confirm that there is no oscillation in the output.

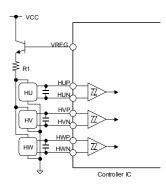

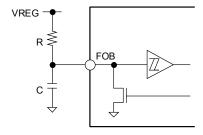

Figure 5. VREG Output Pin Application Example

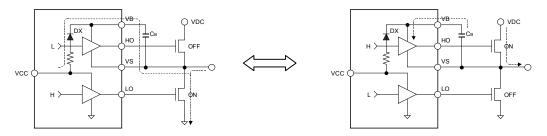

# 15. Bootstrap Operation

Figure 6. Charging Period

Figure 7. Discharging Period

The bootstrap is operated by the charge period and the discharge period being alternately repeated for bootstrap capacitor (CB) as shown in the figure above. In a word, this operation is repeated while the output of an external transistor is switching with synchronous rectification. Because the supply voltage of the floating driver is charged from the VCC power supply to CB through prevention of backflow diode DX, it is approximately (VCC-1V). The resistance series connection with DX has the impedance of approximately  $200~\Omega$ . Because the total gate charge is needed only by the carrier frequency in the upper switching section of  $120^{\circ}$  commutation driving, please set it after confirming actual application operation.

# 16. Fault Signal Output

When the controller detects either state that should be protected the overcurrent (OCP) and the over temperature (TSD), the FOB pin outputs low (open drain) and it returns to normal operation synchronizing with the carrier frequency. Even when this function is not used, the FOB pin is pull-up to the voltage of 3V or more and at least a resistor with a value 10k  $\Omega$  or more. A filter is built into the fault signal input circuit to prevent malfunctions by the switching noise, and does not activate when a short pulse of less than  $T_{MASK}$  is present at the input. The time to the fault operation is the sum total of the propagation delay time of the detection circuit and the filter time, 1.6µs (typical).

Figure 8. Fault Operation ~ OCP ~ Timing Chart

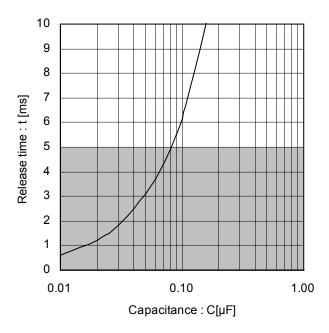

The release time from the protection operation can be changed by inserting an external capacitor. Refer to the formula below. Release time of 5ms or more is recommended.

$$t = -ln(1 - \frac{2.3}{V_{REG}}) \cdot R \cdot C \quad [s]$$

Figure 9. Release Time Setting Application Circuit

Figure 10. Release Time (Reference Data @R=100kΩ)

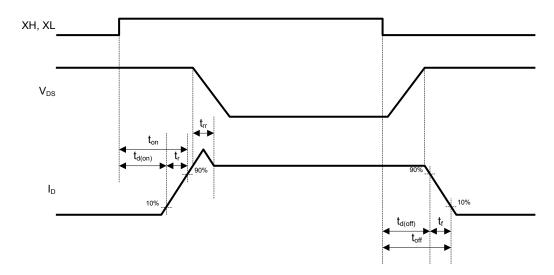

# 17. Switching Time

Figure 11. Switching Time Definition

| Parameter                | Symbol               | Reference | Unit | Conditions                               |

|--------------------------|----------------------|-----------|------|------------------------------------------|

|                          | t <sub>dH(on)</sub>  | 870       | ns   |                                          |

| Hint Olds Outtables      | $t_{rH}$             | 125       | ns   |                                          |

| High Side Switching Time | t <sub>rrH</sub>     | 250       | ns   | VDC=300V, VCC=15V, I <sub>D</sub> =1.25A |

| Time                     | t <sub>dH(off)</sub> | 660       | ns   | Inductive load                           |

|                          | $t_fH$               | 30        | ns   |                                          |

|                          | t <sub>dL(on)</sub>  | 890       | ns   | The propagation delay time: Internal     |

| Lauroida Orritalaina     | t <sub>rL</sub>      | 130       | ns   | gate driver input stage to the driver    |

| Low Side Switching Time  | t <sub>rrL</sub>     | 190       | ns   | IC output.                               |

|                          | t <sub>dL(off)</sub> | 740       | ns   |                                          |

|                          | t <sub>fL</sub>      | 30        | ns   |                                          |

# **Timing Chart (CW)**

Figure 12. Timing Chart (Clockwise)

# **Timing Chart (CCW)**

Figure 13. Timing Chart (Counter Clockwise)

# **Controller Outputs and Operation Mode Summary**

|                   | Detected direction                                               | Forward (CW:U~V~W, CCW:U~W~V)     |                                       |                           |                    | Reverse (CW:U~W~V, CCW:U~V~W) |         |                 |      |  |

|-------------------|------------------------------------------------------------------|-----------------------------------|---------------------------------------|---------------------------|--------------------|-------------------------------|---------|-----------------|------|--|

| Conditions        | Hall sensor frequency                                            | < 1.                              | 4Hz                                   | 1.41                      | 1.4Hz <            |                               | < 1.4Hz |                 | łz < |  |

|                   | PC pin                                                           | L                                 | Н                                     | L                         | Н                  | L                             | Н       | L               | Н    |  |

|                   | VSP < V <sub>SPMIN</sub><br>(Duty off)                           |                                   |                                       |                           | Upper and l        | ower arm off                  |         |                 |      |  |

| Normal operation  | V <sub>SPMIN</sub> < VSP < V <sub>SPMAX</sub><br>(Control range) | Upper and lower<br>switching      |                                       |                           | Upper<br>switching | Upper and lower               |         | Upper switching |      |  |

|                   | V <sub>SPTST</sub> < VSP<br>(Testing mode)                       |                                   |                                       | Upper and lower switching |                    | switching                     |         | Opper Switching |      |  |

|                   | Current limiter (Note 1)                                         |                                   | Upper arm off Upper and lower arm off |                           |                    |                               |         |                 |      |  |

|                   | Overcurrent (Note 2)                                             |                                   |                                       |                           |                    |                               |         |                 |      |  |

|                   | TSD (Note 2)                                                     |                                   |                                       |                           |                    |                               |         |                 |      |  |

| Protect operation | External input (Note 2)                                          | Upper and lower arm off           |                                       |                           |                    |                               |         |                 |      |  |

| ,                 | UVLO (Note 3)                                                    |                                   |                                       |                           |                    |                               |         |                 |      |  |

|                   | Motor lock                                                       |                                   |                                       |                           |                    |                               |         |                 |      |  |

|                   | Hall sensor abnormally                                           | Upper and lower arm off and latch |                                       |                           |                    |                               |         |                 |      |  |

(Note) The controller monitors both edges of three hall sensors for detecting period.

(Note 1) It returns to normal operation by the carrier frequency synchronization.

(Note 2) It works together with the fault operation, and returns after the release time synchronizing with the carrier frequency.

(Note 3) It returns to normal operation after 32 cycles of the carrier oscillation period.

# **Absolute Maximum Ratings** (Ta=25°C)

| Parameter                         | Symbol                                                       | Ratings                          | Unit |

|-----------------------------------|--------------------------------------------------------------|----------------------------------|------|

| Output MOSFET                     | $V_{ m DSS}$                                                 | 600 <sup>(Note 1)</sup>          | V    |

| Supply Voltage                    | V <sub>DC</sub>                                              | -0.3 to +600 <sup>(Note 1)</sup> | V    |

| Output Voltage                    | $V_U$ , $V_V$ , $V_W$                                        | -0.3 to +600 <sup>(Note 1)</sup> | V    |

| High Side Supply Pin Voltage      | $V_{BU}, V_{BV}, V_{BW}$                                     | -0.3 to +600 <sup>(Note 1)</sup> | V    |

| High Side Floating Supply Voltage | $V_{BU}$ - $V_{U}$ , $V_{BV}$ - $V_{V}$ , $V_{BW}$ - $V_{W}$ | -0.3 to +20                      | V    |

| Low Side Supply Voltage           | Vcc                                                          | -0.3 to +20                      | V    |

| Duty Control Voltage              | V <sub>SP</sub>                                              | -0.3 to +20                      | V    |

| All Others                        | V <sub>I/O</sub>                                             | -0.3 to +5.5                     | V    |

| Driver Outputs (DC)               | I <sub>OMAX(DC)</sub>                                        | ±2.5 (Note 1)                    | А    |

| Driver Outputs (Pulse)            | I <sub>OMAX(PLS)</sub>                                       | ±4.0 (Note 1, 2)                 | А    |

| Fault Signal Output               | I <sub>OMAX(FOB)</sub>                                       | 15 <sup>(Note 1)</sup>           | mA   |

| Power Dissipation                 | Pd                                                           | 3.00 <sup>(Note 3)</sup>         | W    |

| Thermal Resistance                | R <sub>thj-c</sub>                                           | 15                               | °C/W |

| Operating Case Temperature        | T <sub>C</sub>                                               | -20 to +100                      | °C   |

| Storage Temperature               | T <sub>STG</sub>                                             | -55 to +150                      | °C   |

| Junction Temperature              | T <sub>jmax</sub>                                            | 150                              | °C   |

(Note) All voltages are with respect to ground.

(Note 1) Do not, however, exceed Pd or ASO.

(Note 2)  $Pw \le 10\mu s$ , Duty cycle  $\le 1\%$

(Note 3) Mounted on a 70mm x 70mm x 1.6mm FR4 glass-epoxy board with less than 3% copper foil. Derated at 24mW/°C above 25°C.

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

# **Recommended Operating Conditions** (Tc=25°C)

| Parameter                         | Symbol                                                       | Min  | Тур | Max  | Unit |

|-----------------------------------|--------------------------------------------------------------|------|-----|------|------|

| Supply Voltage                    | $V_{DC}$                                                     | -    | 310 | 400  | V    |

| High Side Floating Supply Voltage | $V_{BU}$ - $V_{U}$ , $V_{BV}$ - $V_{V}$ , $V_{BW}$ - $V_{W}$ | 13.5 | 15  | 16.5 | V    |

| Low Side Supply Voltage           | V <sub>CC</sub>                                              | 13.5 | 15  | 16.5 | V    |

| Bootstrap Capacitor               | Св                                                           | 1.0  | -   | -    | μF   |

| VREG Bypass Capacitor             | $C_{VREG}$                                                   | 1.0  | -   | -    | μF   |

| Shunt Resistor (PGND)             | R <sub>S</sub>                                               | 0.5  | -   | -    | Ω    |

| Junction Temperature              | Tj                                                           | -    | -   | 125  | °C   |

(Note) All voltages are with respect to ground.

# Electrical Characteristics (Driver part, unless otherwise specified, Ta=25°C and VCC=15V)

| Parameter              | Symbol               | Min | Тур  | Max  | Unit | Conditions                                |  |  |

|------------------------|----------------------|-----|------|------|------|-------------------------------------------|--|--|

| Power Supply           |                      |     |      |      |      |                                           |  |  |

| HS Quiescence Current  | I <sub>BBQ</sub>     | 30  | 70   | 150  | μΑ   | VSP=0V, each phase                        |  |  |

| LS Quiescence Current  | Iccq                 | 0.2 | 0.7  | 1.3  | mA   | VSP=0V                                    |  |  |

| Output MOSFET          |                      |     |      |      |      |                                           |  |  |

| D-S Breakdown Voltage  | V <sub>(BR)DSS</sub> | 600 | -    | -    | V    | I <sub>D</sub> =1mA, VSP=0V               |  |  |

| Leak Current           | I <sub>DSS</sub>     | -   | -    | 100  | μΑ   | V <sub>DS</sub> =600V, VSP=0V             |  |  |

| DC On Resistance       | R <sub>DS(ON)</sub>  | -   | 1.7  | 2.5  | Ω    | I <sub>D</sub> =1.25A                     |  |  |

| Diode Forward Voltage  | V <sub>SD</sub>      | -   | 1.1  | 1.5  | V    | I <sub>D</sub> =1.25A                     |  |  |

| Bootstrap Diode        |                      |     |      |      |      |                                           |  |  |

| Leak Current           | I <sub>LBD</sub>     | -   | -    | 10   | μΑ   | V <sub>BX</sub> =600V                     |  |  |

| Forward Voltage        | $V_{FBD}$            | 1.5 | 1.8  | 2.1  | V    | I <sub>BD</sub> =-5mA, including series-R |  |  |

| Series Resistance      | R <sub>BD</sub>      | -   | 200  | -    | Ω    |                                           |  |  |

| Under Voltage Lock Out |                      |     |      |      |      |                                           |  |  |

| HS Release Voltage     | V <sub>BUVH</sub>    | 9.5 | 10.0 | 10.5 | V    | V <sub>BX</sub> - V <sub>X</sub>          |  |  |

| HS Lockout Voltage     | V <sub>BUVL</sub>    | 8.5 | 9.0  | 9.5  | V    | V <sub>BX</sub> - V <sub>X</sub>          |  |  |

Electrical Characteristics (Controller part, unless otherwise specified, Ta=25°C and VCC=15V)

| Parameter                               | Symbol              | Min                    | Тур                    | Max                   | Unit              | Conditions                               |

|-----------------------------------------|---------------------|------------------------|------------------------|-----------------------|-------------------|------------------------------------------|

| Power Supply                            | <b>Cy</b>           |                        | .,,,,                  | mux                   | <b></b>           | Containe                                 |

| Supply Current                          | I <sub>CC</sub>     | 0.8                    | 1.7                    | 3.0                   | mA                | VSP=0V                                   |

| VREG Voltage                            | V <sub>REG</sub>    | 4.5                    | 5.0                    | 5.5                   | V                 | I <sub>O</sub> =-30mA                    |

| Hall Comparators                        | V KEG               | 4.0                    | 0.0                    | 0.0                   | V                 | 10- 00111/1                              |

| Input Bias Current                      | I <sub>HALL</sub>   | -2.0                   | -0.1                   | 2.0                   | μA                | V <sub>IN</sub> =0V                      |

| Common Mode Input                       | V <sub>HALLCM</sub> | 0                      | -0.1                   | V <sub>REG</sub> -1.5 | V                 | VIN-OV                                   |

| Minimum Input Level                     | V HALLMIN           | 50                     | _                      | V REG-1.0             | mV <sub>p-p</sub> |                                          |

| Hysteresis Voltage P                    | VHALLHY+            | 5                      | 13                     | 23                    | mV                |                                          |

| Hysteresis Voltage N                    | VHALLHY+            | -23                    | -13                    | -5                    | mV                |                                          |

| Duty Control                            | V HALLHY-           | -23                    | -13                    | -:                    | IIIV              |                                          |

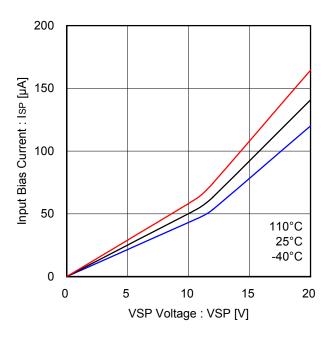

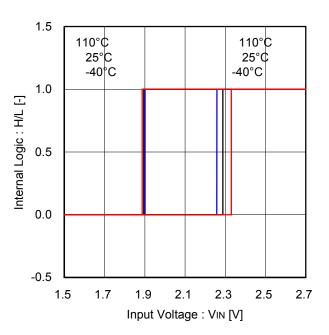

| Input Bias Current                      | 1                   | 15                     | 25                     | 35                    |                   | \/ -5\/                                  |

| Duty Minimum Voltage                    | I <sub>SP</sub>     | 1.8                    | 2.1                    | 2.4                   | μA<br>V           | V <sub>IN</sub> =5V                      |

| , , , , , , , , , , , , , , , , , , , , | V <sub>SPMIN</sub>  |                        |                        |                       | V                 |                                          |

| Duty Maximum Voltage                    | V <sub>SPMAX</sub>  | 5.1                    | 5.4                    | 5.7                   |                   |                                          |

| Testing Operation Range                 | V <sub>SPTST</sub>  | 8.2                    | -                      | 18                    | V                 | F 00111                                  |

| Minimum Output Duty                     | D <sub>MIN</sub>    | -                      | 2                      | -                     | %                 | F <sub>OSC</sub> =20kHz                  |

| Maximum Output Duty                     | D <sub>MAX</sub>    | -                      | 95                     | -                     | %                 | F <sub>OSC</sub> =20kHz, upper switching |

| Mode Switch - FGS and C                 |                     |                        | T                      |                       |                   | T                                        |

| Input Bias Current                      | I <sub>IN</sub>     | -70                    | -50                    | -30                   | μA                | V <sub>IN</sub> =0V                      |

| Input High Voltage                      | $V_{INH}$           | 3                      | -                      | $V_{REG}$             | V                 |                                          |

| Input Low Voltage                       | $V_{INL}$           | 0                      | -                      | 1                     | V                 |                                          |

| Fault Input/Output - FOB                |                     | T                      | T                      |                       |                   | 1                                        |

| Input High Voltage                      | V <sub>FOBIH</sub>  | 3                      | -                      | $V_{REG}$             | V                 |                                          |

| Input Low Voltage                       | $V_{FOBIL}$         | 0                      | -                      | 1                     | V                 |                                          |

| Output Low Voltage                      | $V_{FOBOL}$         | 0                      | 0.07                   | 0.60                  | V                 | I <sub>O</sub> =5mA                      |

| Monitor Output - FG                     |                     |                        |                        |                       |                   |                                          |

| Output High Voltage                     | $V_{MONH}$          | V <sub>REG</sub> -0.40 | V <sub>REG</sub> -0.08 | $V_{REG}$             | V                 | I <sub>O</sub> =-2mA                     |

| Output Low Voltage                      | $V_{MONL}$          | 0                      | 0.02                   | 0.40                  | V                 | I <sub>O</sub> =2mA                      |

| <b>Current Detection</b>                |                     |                        |                        |                       |                   |                                          |

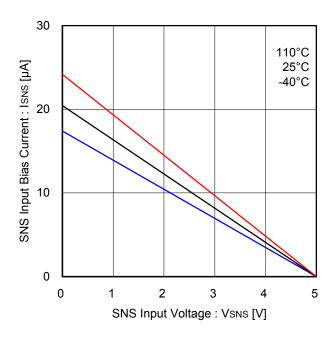

| Input Bias Current                      | $I_{SNS}$           | -30                    | -20                    | -10                   | μA                | V <sub>IN</sub> =0V                      |

| Current Limiter Voltage                 | $V_{SNS}$           | 0.48                   | 0.50                   | 0.52                  | V                 |                                          |

| Overcurrent Voltage                     | V <sub>OVER</sub>   | 0.84                   | 0.90                   | 0.96                  | V                 |                                          |

| Noise Masking Time                      | T <sub>MASK</sub>   | 0.8                    | 1.0                    | 1.2                   | μs                |                                          |

| PWM Switching Arm Setti                 | ng                  |                        |                        |                       |                   |                                          |

| Threshold Voltage                       | $V_{PC}$            | -0.05                  | 0                      | 0.05                  | V                 | 1/2·V <sub>REG</sub> , reference voltage |

| Carrier Frequency Oscilla               | tor                 |                        |                        |                       |                   |                                          |

| Carrier Frequency                       | Fosc                | 18                     | 20                     | 22                    | kHz               | $R_T$ =20k $\Omega$                      |

| Under Voltage Lock Out                  |                     |                        |                        |                       |                   |                                          |

| - · · · · · · · · · · · · · · · · · · · |                     |                        |                        |                       |                   |                                          |

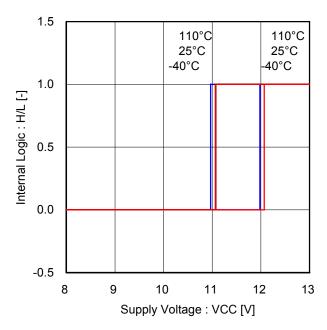

| LS Release Voltage                      | V <sub>CCUVH</sub>  | 11.5                   | 12.0                   | 12.5                  | V                 |                                          |

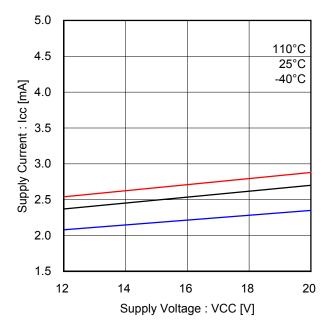

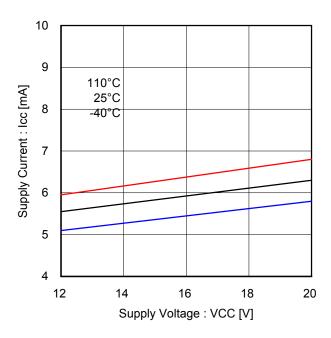

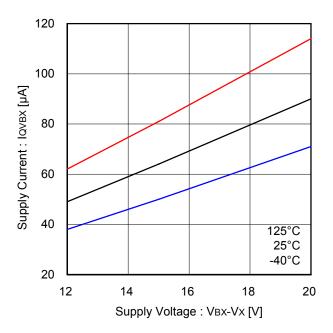

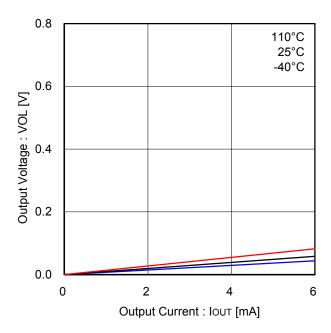

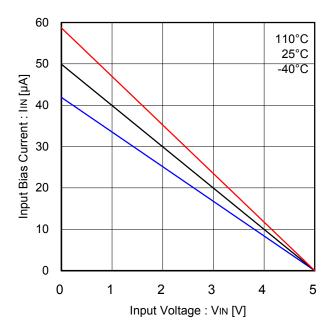

# Typical Performance Curves (Reference data)

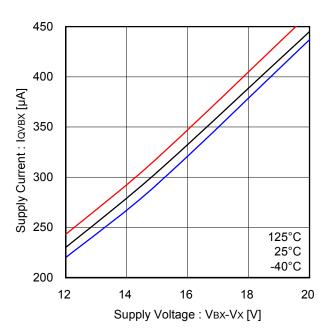

Figure 14. Quiscence Current (Low Side Drivers)

Figure 15. Low Side Drivers Operating Current (F<sub>PWM</sub>: 20kHz)

Figure 16. Quiescence Current (High Side Driver, Each Phase)

Figure 17. High Side Driver Operating Current (F<sub>PWM</sub>: 20kHz, Each Phase)

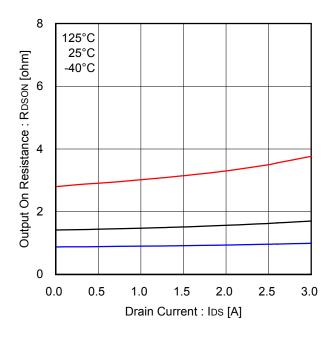

Figure 18. Output MOSFET ON Resistance

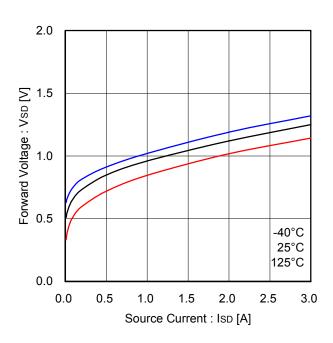

Figure 19. Output MOSFET Body Diode

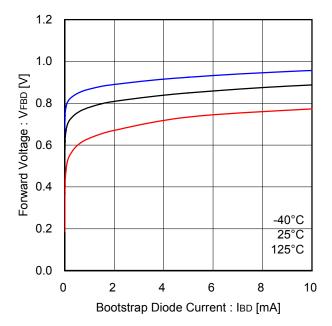

Figure 20. Bootstrap Diode Forward Voltage

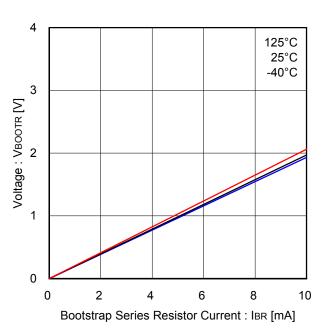

Figure 21. Bootstrap Series Resistor

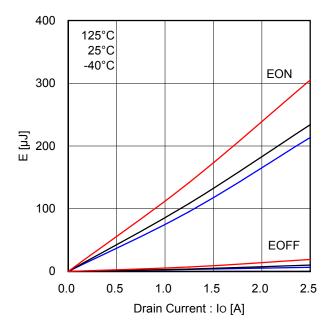

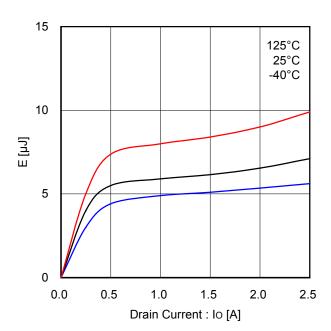

Figure 22. High Side Switching Loss (VDC=300V)

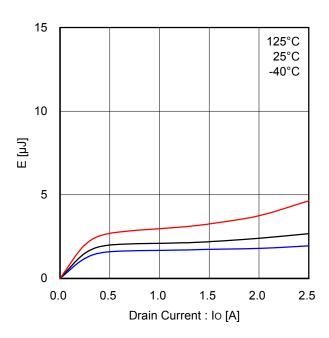

Figure 23. High Side Recovery Loss (VDC=300V)

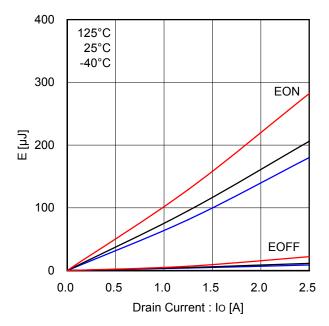

Figure 24. Low Side Switching Loss (VDC=300V)

Figure 25. Low Side Recovery Loss (VDC=300V)

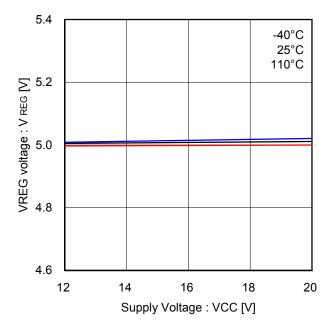

Figure 26. VREG - VCC

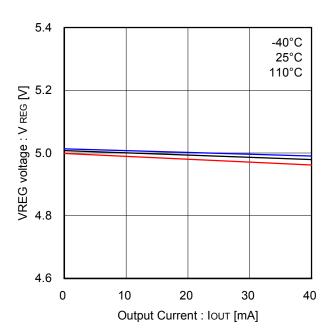

Figure 27. VREG Drive Capability

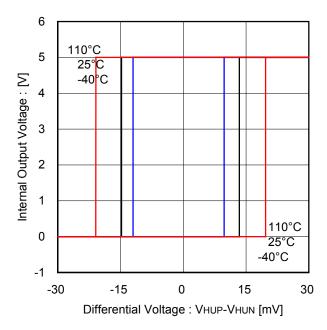

Figure 28. Hall Comparator Hysteresis Voltage

Figure 29. VSP Input Bias Current

Figure 30. Output Duty - VSP Voltage (PC=H)

Figure 31. Testing Mode Threshold Voltage

Figure 32. VSP - PCT Offset Voltage

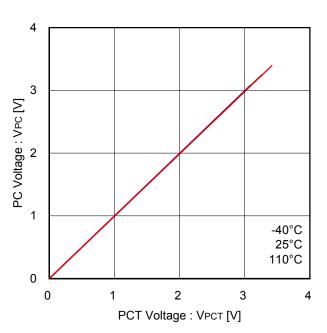

Figure 33. PCT - PC Linearity (RPCT=RPC= $100k\Omega$ )

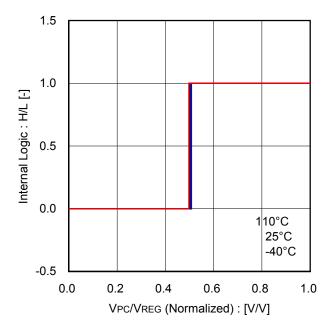

Figure 34. PWM Switching Arm Threshold Voltage

Figure 35. Carrier Frequency - RT

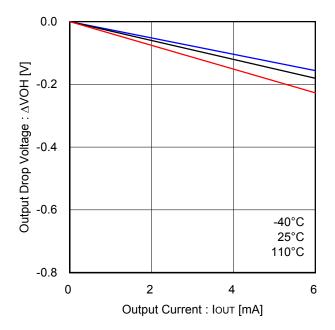

Figure 36. High Side Output Voltage (FG)

Figure 37. Low Side Output Voltage (FG)

Figure 38. Input Bias Current (CCW, FGS)

Figure 39. Input Threshold Voltage (CCW, FGS, FOB)

Figure 40. SNS Input Bias Current

Figure 41. Current Limiter Input Threshold Voltage (SNS)

Figure 42. OCP Input Threshold Voltage (SNS)

Figure 43. Thermal Shutdown

Figure 44. Under Voltage Lock Out (High Side Driver, Each Phase)

Figure 45. Under Voltage Lock Out (Low Side Drivers)

# **Application Example**

Figure 46. Application Example (120° Commutation Driver)

# Parts List

| unto Lic |       |              |                    |       |        |         |               |

|----------|-------|--------------|--------------------|-------|--------|---------|---------------|

| Parts    | Value | Manufacturer | Type               | Parts | Value  | Ratings | Type          |

| IC1      |       | ROHM         | BM6205FS           | C1    | 0.1µF  | 50V     | Ceramic       |

| R1       | 1kΩ   | ROHM         | MCR18EZPF1001      | C2    | 2200pF | 50V     | Ceramic       |

| R2       | 150Ω  | ROHM         | MCR18EZPJ151       | C3    | 2200pF | 50V     | Ceramic       |

| R3       | 150Ω  | ROHM         | MCR18EZPJ151       | C4    | 2200pF | 50V     | Ceramic       |

| R4       | 20kΩ  | ROHM         | MCR18EZPF2002      | C5    | 10 μF  | 50V     | Ceramic       |

| R5       | 100kΩ | ROHM         | MCR18EZPF1003      | C6    | 10 μF  | 50V     | Ceramic       |

| R6       | 100kΩ | ROHM         | MCR18EZPF1003      | C7    | 2.2µF  | 50V     | Ceramic       |

| R7       | 0.5Ω  | ROHM         | MCR50JZHFL1R50 x 3 | C8    | 2.2µF  | 50V     | Ceramic       |

| R8       | 10kΩ  | ROHM         | MCR18EZPF1002      | C9    | 2.2µF  | 50V     | Ceramic       |

| R9       | 0Ω    | ROHM         | MCR18EZPJ000       | C10   | 0.1µF  | 50V     | Ceramic       |

| R10      | -     | -            | -                  | C11   | 2.2µF  | 50V     | Ceramic       |

| R11      | 0Ω    | ROHM         | MCR18EZPJ000       | C12   | 100pF  | 50V     | Ceramic       |

| R12      | -     | -            | -                  | C13   | 0.1µF  | 630V    | Ceramic       |

| R13      | 100kΩ | ROHM         | MCR18EZPF1003      | C14   | 0.1µF  | 50V     | Ceramic       |

| Q1       | -     | ROHM         | DTC124EUA          | НХ    | -      | -       | Hall elements |

| D1       | -     | ROHM         | KDZ20B             |       |        |         |               |

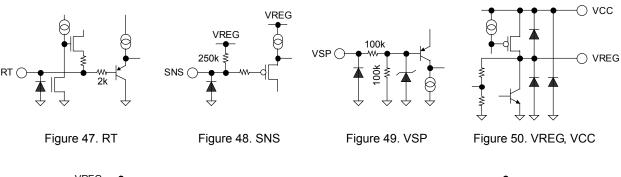

# I/O Equivalence Circuits

Figure 51. FG

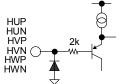

Figure 52. HXP, HXN

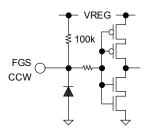

Figure 53. FGS, CCW

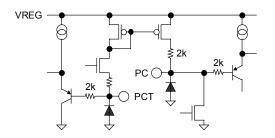

Figure 54. PC, PCT

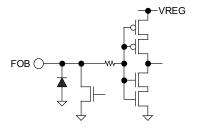

Figure 55. FOB

Figure 56. VCC, PGND, VDC, BX(BU/BV/BW), X(U/V/W)

### **Operational Notes**

### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply terminals.

# 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

# 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition. However, pins that drive inductive loads (e.g. motor driver outputs, DC-DC converter outputs) may inevitably go below ground due to back EMF or electromotive force. In such cases, the user should make sure that such voltages going below ground will not cause the IC and the system to malfunction by examining carefully all relevant factors and conditions such as motor characteristics, supply voltage, operating frequency and PCB wiring to name a few.

# 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

# 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. The absolute maximum rating of the Pd stated in this specification is when the IC is mounted on a 70mm x 70mm x 1.6mm glass epoxy board. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the Pd rating.

# 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

# 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

## 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

# 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

# 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

### 11. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

# 12. Regarding the Input Pin of the IC

Do not force voltage to the input pins when the power does not supply to the IC. Also, do not force voltage to the input pins that exceed the supply voltage or in the guaranteed the absolute maximum rating value even if the power is supplied to the IC.

When using this IC, the high voltage pins VDC, BU/U, BV/V and BW/W need a resin coating between these pins. It is judged that the inter-pins distance is not enough. If any special mode in excess of absolute maximum ratings is to be implemented with this product or its application circuits, it is important to take physical safety measures, such as providing voltage-clamping diodes or fuses. And, set the output transistor so that it does not exceed absolute maximum ratings or ASO. In the event a large capacitor is connected between the output and ground, and if VCC and VDC are short-circuited with 0V or ground for any reason, the current charged in the capacitor flows into the output and may destroy the IC.

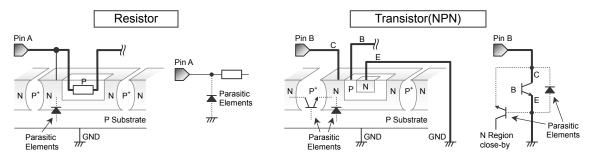

This IC contains the controller chip, P+ isolation and P substrate layers between adjacent elements in order to keep them isolated. P-N junctions are formed at the intersection of the P layers with the N layers of other elements, creating a parasitic diode or transistor. For example (refer to figure below):

When GND > Pin A and GND > Pin B, the P-N junction operates as a parasitic diode.

When GND > Pin B, the P-N junction operates as a parasitic transistor.

Parasitic diodes inevitably occur in the structure of the IC. The operation of parasitic diodes can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions that cause these diodes to operate, such as applying a voltage lower than the GND voltage to an input pin (and thus to the P substrate) should be avoided.

Figure A-1. Example of IC structure

# 13. Ceramic Capacitor

When using a ceramic capacitor, determine the dielectric constant considering the change of capacitance with temperature and the decrease in nominal capacitance due to DC bias and others.

# 14. Area of Safe Operation (ASO)

Operate the IC such that the output voltage, output current, and power dissipation are all within the Area of Safe Operation (ASO).

# **Physical Dimension, Tape and Reel Information**