Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Data sheet

# **BMA253**Digital, triaxial acceleration sensor

**Bosch Sensortec**

#### BMA253: Data sheet

Document revision 1.0

Document release date 20 August 2015

Document number BST-BMA253-DS000-01

Technical reference code(s) 0 273 016 001

Notes Data in this document are subject to change without notice.

Product photos and pictures are for illustration purposes only and

may differ from the real product's appearance.

Not for publishing

#### **BMA253**

# 12 BIT, DIGITAL, TRIAXIAL ACCELERATION SENSOR WITH INTELLIGENT ON-CHIP MOTION-TRIGGERED INTERRUPT CONTROLLER

#### **Key features**

Ultra-Small package

Digital interface

Programmable functionality

On-chip FIFO

On-chip interrupt controller

LGA package (12 pins), footprint 2mm x 2mm, height 0.95mm

SPI (4-wire, 3-wire), I<sup>2</sup>C, 2 interrupt pins

V<sub>DDIO</sub> voltage range: 1.2V to 3.6V

Acceleration ranges ±2g/±4g/±8g/±16g

Low-pass filter bandwidths 1kHz - <8Hz Integrated FIFO with a depth of 32 frames Motion-triggered interrupt-signal generation for

- new data

- any-motion (slope) detection

- tap sensing (single tap / double tap)

- orientation recognition

- flat detection

- low-g/high-g detection

- no-motion / inactivity detection

Low current consumption, short wake-up time, advanced features for system power management

- Ultra-low power

- Temperature sensor

- RoHS compliant, halogen-free

#### **Typical applications**

- Display profile switching

- Menu scrolling, tap / double tap sensing

- Gaming

- Pedometer / step counting

- Free-fall detection

- E-compass tilt compensation

- Drop detection for warranty logging

- Advanced system power management for mobile applications

#### **General description**

The BMA253 is a triaxial, low-g acceleration sensor with digital output for consumer applications. It allows measurements of acceleration in three perpendicular axes. An evaluation circuitry (ASIC) converts the output of a micromechanical acceleration-sensing structure (MEMS) that works according to the differential capacitance principle.

Package and interfaces of the BMA253 have been defined to match a multitude of hardware requirements. Since the sensor features an ultra-small footprint and a flat package it is ingeniously suited for mobile applications.

The BMA253 offers a variable  $V_{DDIO}$  voltage range from 1.2V to 3.6V and can be programmed to optimize functionality, performance and power consumption in customer specific applications.

Page 3

In addition it features an on-chip interrupt controller enabling motion-based applications without use of a microcontroller.

The BMA253 senses tilt, motion, inactivity and shock vibration in cell phones, handhelds, computer peripherals, man-machine interfaces, virtual reality features and game controllers.

Page 4

### **Index of Contents**

| 1. SPECIFICATION                                                                                                                                                                                                                                                                                                                                                                | 8        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2. ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                                                                                                     | 11       |

| 3. BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                | 12       |

| 4. FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       | 13       |

| 4.1 SUPPLY VOLTAGE AND POWER MANAGEMENT                                                                                                                                                                                                                                                                                                                                         | 13       |

| 4.2 POWER MODES                                                                                                                                                                                                                                                                                                                                                                 | 14       |

| 4.3 SENSOR DATA                                                                                                                                                                                                                                                                                                                                                                 | 18       |

| 4.3.1 Acceleration data4.3.2 Temperature sensor                                                                                                                                                                                                                                                                                                                                 |          |

| 4.4 Self-test                                                                                                                                                                                                                                                                                                                                                                   | 20       |

| 4.5 OFFSET COMPENSATION                                                                                                                                                                                                                                                                                                                                                         | 21       |

| 4.5.1 SLOW COMPENSATION                                                                                                                                                                                                                                                                                                                                                         | 23<br>24 |

| 4.6 Non-volatile memory                                                                                                                                                                                                                                                                                                                                                         | 25       |

| 4.7 Interrupt controller                                                                                                                                                                                                                                                                                                                                                        | 26       |

| 4.7.1 GENERAL FEATURES 4.7.2 MAPPING TO PHYSICAL INTERRUPT PINS (INTTYPE TO INT PIN#) 4.7.3 ELECTRICAL BEHAVIOUR (INT PIN# TO OPEN-DRIVE OR PUSH-PULL). 4.7.4 NEW DATA INTERRUPT 4.7.5 SLOPE / ANY-MOTION DETECTION 4.7.6 TAP SENSING 4.7.7 ORIENTATION RECOGNITION 4.7.8 FLAT DETECTION 4.7.9 LOW-G INTERRUPT 4.7.10 HIGH-G INTERRUPT 4.7.11 NO-MOTION / SLOW MOTION DETECTION |          |

| 4.8 SOFTRESET                                                                                                                                                                                                                                                                                                                                                                   | 44       |

| 5. FIFO OPERATION                                                                                                                                                                                                                                                                                                                                                               | 45       |

| 5.1 FIFO OPERATING MODES                                                                                                                                                                                                                                                                                                                                                        | 45       |

| 5.2 FIFO DATA READOUT                                                                                                                                                                                                                                                                                                                                                           | 46       |

| 5.3 FIFO FRAME COUNTER AND OVERRUN FLAG                                                                                                                                                                                                                                                                                                                                         | 46       |

| 5.4 FIFO Interrupts                                                                                                                                                                                                                                                                                                                                                             | 47       |

| 6. | REGISTER DESCRIPTION          | .48 |

|----|-------------------------------|-----|

|    | 6.1 GENERAL REMARKS           | 48  |

|    | 6.2 REGISTER MAP              | 49  |

|    | REGISTER 0x00 (BGW_CHIPID)    | 50  |

|    | REGISTER 0x02 (ACCD_X_LSB)    | 50  |

|    | REGISTER 0x03 (ACCD_X_MSB)    | 51  |

|    | REGISTER 0x04 (ACCD_Y_LSB)    | 52  |

|    | REGISTER 0x05 (ACCD_Y_MSB)    | 53  |

|    | REGISTER 0x06 (ACCD_Z_LSB)    | 54  |

|    | REGISTER 0x07 (ACCD_Z_MSB)    | 55  |

|    | REGISTER 0x08 (ACCD_TEMP)     | 56  |

|    | REGISTER 0x09 (INT_STATUS_0)  | 57  |

|    | REGISTER 0x0A (INT_STATUS_1)  | 58  |

|    | REGISTER 0x0B (INT_STATUS_2)  | 59  |

|    | REGISTER 0x0C (INT_STATUS_3)  | 60  |

|    | REGISTER 0x0E (FIFO_STATUS)   | 61  |

|    | REGISTER 0x0F (PMU_RANGE)     | 62  |

|    | REGISTER 0x10 (PMU_BW)        | 62  |

|    | REGISTER 0x11 (PMU_LPW)       | 63  |

|    | REGISTER 0x12 (PMU_LOW_POWER) | 64  |

|    | REGISTER 0x13 (ACCD_HBW)      | 65  |

|    | REGISTER 0x14 (BGW_SOFTRESET) | 66  |

|    | REGISTER 0x16 (INT_EN_0)      | 66  |

|    | REGISTER 0x17 (INT_EN_1)      | 67  |

|    | REGISTER 0x18 (INT_EN_2)      | 68  |

|    | REGISTER 0x19 (INT_MAP_0)     | 69  |

|    | REGISTER 0x1A (INT_MAP_1)     | 70  |

|    | REGISTER 0x1B (INT_MAP_2)     | 71  |

|    | REGISTER 0x1E (INT_SRC)       | 72  |

|    | REGISTER 0x20 (INT_OUT_CTRL)  | 73  |

|    | REGISTER 0x21 (INT_RST_LATCH) | 74  |

|    | REGISTER 0x22 (INT_0)         | 74  |

|    | REGISTER 0x23 (INT_1)         | 75  |

|    | REGISTER 0x24 (INT 2)         | 75  |

Page 6

| REC    | GISTER 0x25 (INT_3)                               | 76  |

|--------|---------------------------------------------------|-----|

| REC    | GISTER 0x26 (INT_4)                               | 76  |

| REC    | GISTER 0x27 (INT_5)                               | 77  |

| REC    | GISTER 0x28 (INT_6)                               | 78  |

| REC    | GISTER 0x29 (INT_7)                               | 78  |

| REC    | GISTER 0x2A (INT_8)                               | 79  |

| REC    | GISTER 0x2B (INT_9)                               | 80  |

| REC    | GISTER 0x2C (INT_A)                               | 81  |

| REC    | GISTER 0x2D (INT_B)                               | 82  |

| REC    | GISTER 0x2E (INT_C)                               | 82  |

| REC    | GISTER 0x2F (INT_D)                               | 83  |

| REC    | GISTER 0x30 (FIFO_CONFIG_0)                       | 84  |

| REC    | GISTER 0x32 (PMU_SELF_TEST)                       | 85  |

| REC    | GISTER 0x33 (TRIM_NVM_CTRL)                       | 86  |

| REC    | GISTER 0x34 (BGW_SPI3_WDT)                        | 87  |

| REC    | GISTER 0x36 (OFC_CTRL)                            | 88  |

| REC    | GISTER 0x37 (OFC_SETTING)                         | 89  |

| REC    | GISTER 0x38 (OFC_OFFSET_X)                        | 90  |

|        | GISTER 0x39 (OFC_OFFSET_Y)                        |     |

|        | GISTER 0x3A (OFC_OFFSET_Z)                        |     |

|        | GISTER 0x3B (TRIM_GP0)                            |     |

| REC    | GISTER 0x3C (TRIM_GP1)                            | 93  |

| REC    | GISTER 0x3E (FIFO_CONFIG_1)                       | 94  |

| REC    | GISTER 0x3F (FIFO_DATA)                           | 95  |

| 7 DIG  | GITAL INTERFACES                                  | 96  |

|        | SERIAL PERIPHERAL INTERFACE (SPI)                 |     |

|        | INTER-INTEGRATED CIRCUIT (I <sup>2</sup> C)       |     |

|        | .2.1 SPI and I <sup>2</sup> C Access Restrictions |     |

| -      |                                                   |     |

| 8. PIN | I-OUT AND CONNECTION DIAGRAM                      | 105 |

|        | PIN-OUT                                           |     |

| 8.2    | CONNECTION DIAGRAM 4-WIRE SPI                     | 106 |

| 8.3    | CONNECTION DIAGRAM 3-WIRE SPI                     | 107 |

| 8.4    | CONNECTION DIAGRAM I <sup>2</sup> C               | 108 |

Page 7

| 9. PACKAGE                           | 109 |

|--------------------------------------|-----|

| 9.1 OUTLINE DIMENSIONS               | 109 |

| 9.2 Sensing axes orientation         | 110 |

| 9.3 LANDING PATTERN RECOMMENDATION   | 111 |

| 9.4 Marking                          | 112 |

| 9.4.1 Mass production devices        |     |

| 9.5 SOLDERING GUIDELINES             | 113 |

| 9.6 HANDLING INSTRUCTIONS            | 114 |

| 9.7 TAPE AND REEL SPECIFICATION      |     |

| 9.7.1 ORIENTATION WITHIN THE REEL    | 116 |

| 9.8 ENVIRONMENTAL SAFETY             |     |

| 9.8.1 HALOGEN CONTENT                |     |

| 10. LEGAL DISCLAIMER                 | 118 |

| 10.1 Engineering samples             | 118 |

| 10.2 PRODUCT USE                     | 118 |

| 10.3 APPLICATION EXAMPLES AND HINTS  | 118 |

| 11 DOCUMENT HISTORY AND MODIFICATION | 110 |

# 1. Specification

Unless stated otherwise, the given values are over lifetime, operating temperature and voltage ranges. Minimum/maximum values are  $\pm 3\sigma$ .

Table 1: Parameter specification

| OPERATING CONDITIONS                               |                                   |                                                                                 |                      |                       |                      |       |

|----------------------------------------------------|-----------------------------------|---------------------------------------------------------------------------------|----------------------|-----------------------|----------------------|-------|

| Parameter                                          | Symbol                            | Condition                                                                       | Min                  | Тур                   | Max                  | Units |

| Acceleration<br>Range                              | gFS2g<br>gFS4g<br>gFS8g<br>gFS16g | Selectable<br>via serial digital<br>interface                                   |                      | ±2<br>±4<br>±8<br>±16 |                      | g g g |

| Supply Voltage<br>Internal Domains                 | $V_{DD}$                          |                                                                                 | 1.62                 | 2.4                   | 3.6                  | V     |

| Supply Voltage<br>I/O Domain                       | $V_{\text{DDIO}}$                 |                                                                                 | 1.2                  | 2.4                   | 3.6                  | V     |

| Voltage Input<br>Low Level                         | $V_{IL}$                          | SPI & I <sup>2</sup> C                                                          |                      |                       | 0.3V <sub>DDIO</sub> | -     |

| Voltage Input<br>High Level                        | $V_{IH}$                          | SPI & I <sup>2</sup> C                                                          | $0.7V_{DDIO}$        |                       |                      | -     |

| Voltage Output<br>Low Level                        | $V_{OL}$                          | I <sub>OL</sub> = 3mA, SPI & I <sup>2</sup> C                                   |                      |                       | 0.2V <sub>DDIO</sub> | -     |

| Voltage Output<br>High Level                       | $V_{OH}$                          | I <sub>OH</sub> = 3mA, SPI                                                      | 0.8V <sub>DDIO</sub> |                       |                      | -     |

| Total Supply<br>Current in<br>Normal Mode          | I <sub>DD</sub>                   | $T_A=25$ °C, bw = 1kHz<br>$V_{DD}=V_{DDIO}=2.4V$                                |                      | 130                   |                      | μΑ    |

| Total Supply<br>Current in<br>Suspend Mode         | I <sub>DDsum</sub>                | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                        |                      | 2.1                   |                      | μΑ    |

| Total Supply<br>Current in<br>Deep Suspend<br>Mode | I <sub>DDdsum</sub>               | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                        |                      | 1                     |                      | μΑ    |

| Total Supply<br>Current in<br>Low-power Mode<br>1  | I <sub>DDlp1</sub>                | $T_A$ =25°C, bw = 1kHz<br>$V_{DD}$ = $V_{DDIO}$ = 2.4V<br>sleep duration = 25ms |                      | 6.5                   |                      | μΑ    |

| Total Supply<br>Current in<br>Low-power Mode<br>2  | I <sub>DDlp2</sub>                | $T_A$ =25°C, bw = 1kHz<br>$V_{DD}$ = $V_{DDIO}$ = 2.4V<br>sleep duration = 25ms |                      | 66                    |                      | μΑ    |

Page 9

| Total Supply<br>Current in<br>Standby Mode   | I <sub>DDsbm</sub> | $T_A=25^{\circ}C$ $V_{DD}=V_{DDIO}=2.4V$                                      |     | 62  |     | μА     |

|----------------------------------------------|--------------------|-------------------------------------------------------------------------------|-----|-----|-----|--------|

| Wake-Up Time 1                               | $t_{w,up1}$        | from Low-power Mode<br>1 or Suspend Mode or<br>Deep Suspend Mode<br>bw = 1kHz |     | 1.3 | 1.8 | ms     |

| Wake-Up Time 2                               | t <sub>w,up2</sub> | from Low-power Mode<br>2 or Stand-by Mode<br>bw = 1kHz                        |     | 1   | 1.2 | ms     |

| Start-Up Time                                | $t_{s,up}$         | POR, bw = 1kHz                                                                |     |     | 3   | ms     |

| Non-volatile<br>memory (NVM)<br>write-cycles | n <sub>NVM</sub>   |                                                                               |     |     | 15  | cycles |

| Operating<br>Temperature                     | T <sub>A</sub>     |                                                                               | -40 |     | +85 | °C     |

#### **OUTPUT SIGNAL**

| Parameter                          | Symbol             | Condition                                                                                   | Min | Тур   | Max | Units  |

|------------------------------------|--------------------|---------------------------------------------------------------------------------------------|-----|-------|-----|--------|

|                                    | S <sub>2g</sub>    | $g_{FS2g}$ , $T_A=25$ °C                                                                    |     | 1024  |     | LSB/g  |

| Sensitivity                        | $S_{4g}$           | $g_{FS4g}$ , $T_A = 25$ °C                                                                  |     | 512   |     | LSB/g  |

| Sensitivity                        | S <sub>8g</sub>    | $g_{FS8g}$ , $T_A=25$ °C                                                                    |     | 256   |     | LSB/g  |

|                                    | S <sub>16g</sub>   | $g_{FS16g}$ , $T_A=25$ °C                                                                   |     | 128   |     | LSB/g  |

| Sensitivity<br>Temperature Drift   | TCS                | $g_{FS2g}$ , Nominal $V_{DD}$ supplies                                                      |     | ±0.02 |     | %/K    |

| Zaro-g Offset                      | Off <sub>new</sub> | $g_{FS2g}$ , $T_A$ =25°C,<br>nominal $V_{DD}$ supplies,<br>before soldering                 |     | ±20   |     | mg     |

| Zero-g Offset                      | Off                | $g_{FS2g}$ , $T_A$ =25°C,<br>nominal $V_{DD}$ supplies,<br>over life-time                   |     | ±80   |     | mg     |

| Zero-g Offset<br>Temperature Drift | TCO                | $g_{FS2g}$ , Nominal $V_{DD}$ supplies                                                      |     | ±1    |     | mg/K   |

|                                    | bw <sub>8</sub>    |                                                                                             |     | 8     |     | Hz     |

|                                    | bw <sub>16</sub>   |                                                                                             |     | 16    |     | Hz     |

|                                    | bw <sub>31</sub>   | ond I cit                                                                                   |     | 31    |     | Hz     |

| Bandwidth                          | bw <sub>63</sub>   | 2 <sup>nd</sup> order filter,<br>bandwidth                                                  |     | 63    |     | Hz     |

| Danawidin                          | bw <sub>125</sub>  | programmable                                                                                |     | 125   |     | Hz     |

|                                    | bw <sub>250</sub>  | , 0                                                                                         |     | 250   |     | Hz     |

|                                    | $bw_{500}$         |                                                                                             |     | 500   |     | Hz     |

|                                    | bw <sub>1000</sub> |                                                                                             |     | 1,000 |     | Hz     |

| Nonlinearity                       | NL                 | best fit straight line,<br>g <sub>FS2g</sub>                                                |     | ±0.5  |     | %FS    |

| Output Noise<br>Density            | n <sub>rms</sub>   | g <sub>FS2g</sub> , T <sub>A</sub> =25°C<br>Nominal V <sub>DD</sub> supplies<br>Normal mode |     | 220   |     | μg/√Hz |

BST-BMA253-DS000-01 | Revision 1.0 | August 2015

Bosch Sensortec

|                                               | Bata onoot                 |                                                               |     |      |     |       |

|-----------------------------------------------|----------------------------|---------------------------------------------------------------|-----|------|-----|-------|

| Temperature<br>Sensor<br>Measurement<br>Range | Ts                         |                                                               | -40 |      | 85  | °C    |

| Temperature<br>Sensor Slope                   | dTs                        |                                                               |     | 0.5  |     | K/LSB |

| Temperature<br>Sensor Offset                  | OTs                        |                                                               |     | ±2   |     | K     |

|                                               | Mechanical Characteristics |                                                               |     |      |     |       |

| Parameter                                     | Symbol                     | Condition                                                     | Min | Тур  | Max | Units |

| Cross Axis<br>Sensitivity                     | S                          | relative contribution<br>between any two of<br>the three axes |     | 1    |     | %     |

| Alignment Error                               | E <sub>A</sub>             | relative to package outline                                   |     | ±0.5 |     | o     |

# 2. Absolute maximum ratings

Table 2: Absolute maximum ratings

| Parameter                                  | Condition                    | Min  | Max             | Units |

|--------------------------------------------|------------------------------|------|-----------------|-------|

| Voltago at Supply Din                      | $V_{DD}$ Pin                 | -0.3 | 4.25            | V     |

| Voltage at Supply Pin                      | $V_{DDIO}$ Pin               | -0.3 | 4.25            | V     |

| Voltage at any Logic Pin                   | Non-Supply Pin               | -0.3 | $V_{DDIO}$ +0.3 | V     |

| Passive Storage Temp. Range                | ≤ 65% rel. H.                | -50  | +150            | °C    |

| None-volatile memory (NVM)  Data Retention | T = 85°C,<br>after 15 cycles | 10   |                 | у     |

|                                            | Duration ≤ 200µs             |      | 10,000          | g     |

| Mechanical Shock                           | Duration ≤ 1.0ms             |      | 2,000           | g     |

|                                            | Free fall onto hard surfaces |      | 1.8             | m     |

|                                            | HBM, at any Pin              |      | 2               | kV    |

| ESD                                        | CDM                          |      | 500             | V     |

|                                            | MM                           |      | 200             | V     |

#### Note:

Stress above these limits may cause damage to the device. Exceeding the specified electrical limits may affect the device reliability or cause malfunction.

# 3. Block diagram

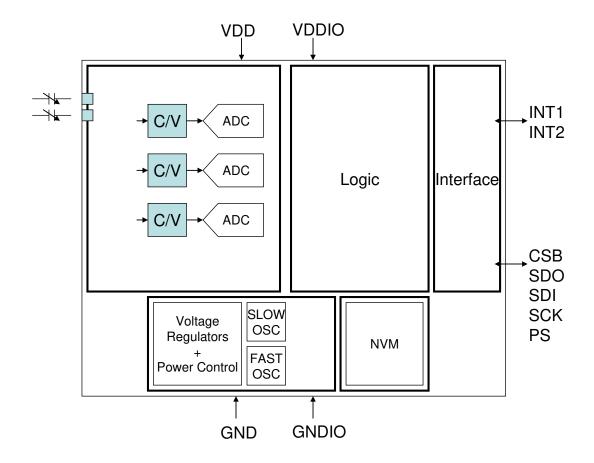

Figure 1 shows the basic building blocks of the BMA253:

Figure 1: Block diagram of BMA253

Page 13

#### 4. Functional description

Note: Default values for registers can be found in chapter 6.

#### 4.1 Supply voltage and power management

The BMA253 has two distinct power supply pins:

- $\bullet$   $V_{DD}$  is the main power supply for the internal blocks

- V<sub>DDIO</sub> is a separate power supply pin used for supplying power for the interface

There are no limitations on the voltage levels of both pins relative to each other, as long as each of them lies within its operating range. Furthermore, the device can be completely switched off ( $V_{DD} = 0V$ ) while keeping the  $V_{DDIO}$  supply on ( $V_{DDIO} > 0V$ ) or vice versa.

When the  $V_{DDIO}$  supply is switched off, all interface pins (CSB, SDI, SCK, PS) must be kept close to  $GND_{IO}$  potential.

The device contains a power-on reset (POR) generator. It resets the logic part and the register values after powering-on  $V_{DD}$  and  $V_{DDIO}$ . Please note, that all application specific settings which are not equal to the default settings (refer to 6.2 register map), must be re-set to its designated values after POR.

There are no constraints on the switching sequence of both supply voltages. In case the  $I^2C$  interface shall be used, a direct electrical connection between  $V_{DDIO}$  supply and the PS pin is needed in order to ensure reliable protocol selection. For SPI interface mode the PS pin must be directly connected to  $GND_{IO}$ .

#### 4.2 Power modes

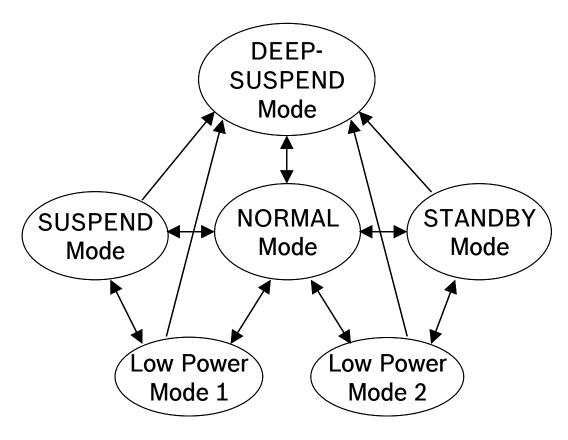

The BMA253 has six different power modes. Besides normal mode, which represents the fully operational state of the device, there are five energy saving modes: deep-suspend mode, suspend mode, standby mode, low-power mode 1 and low-power mode 2.

The possible transitions between the power modes are illustrated in figure 2:

Figure 2: Power mode transition diagram

After power-up BMA253 is in normal mode so that all parts of the device are held powered-up and data acquisition is performed continuously.

In **deep-suspend** mode the device reaches the lowest possible power consumption. Only the interface section is kept alive. No data acquisition is performed and the content of the configuration registers is lost. Deep suspend mode is entered (left) by writing '1' ('0') to the (0x11) deep\_suspend bit while (0x11) suspend bit is set to '0'. The I<sup>2</sup>C watchdog timer remains functional. The (0x11) deep\_ suspend bit, the (0x34) spi3 bit, (0x34) i2c\_wdt\_en bit and the (0x34) i2c\_wdt\_sel bit are functional in deep-suspend mode. Equally the interrupt level and driver configuration registers (0x20) int1\_lvl, (0x20) int1\_od, (0x20) int2\_lvl, and (0x20) int2\_od are accessible. Still it is possible to enter normal mode by performing a softreset as described in chapter 4.8. Please note, that all application specific settings which are not equal to the default settings (refer to 6.2 register map), must be re-set to its designated values after leaving deep-suspend mode.

Page 15

In **suspend mode** the whole analog part is powered down. No data acquisition is performed. While in suspend mode the latest acceleration data and the content of all configuration registers are kept. Writing to and reading from registers is supported except from the (0x3E) fifo\_config\_1, (0x30) fifo\_config\_0 and (0x3F) fifo\_data register. It is possible to enter normal mode by performing a softreset as described in chapter 4.8.

Suspend mode is entered (left) by writing '1' ('0') to the (0x11) suspend bit after bit (0x12) lowpower\_mode has been set to '0'. Although write access to registers is supported at the full interface clock speed (SCL or SCK), a waiting period must be inserted between two consecutive write cycles (please refer also to section 7.2.1).

In **standby mode** the analog part is powered down, while the digital part remains largely operational. No data acquisition is performed. Reading and writing registers is supported without any restrictions. The latest acceleration data and the content of all configuration registers are kept. Standby mode is entered (left) by writing '1' ('0') to the (0x11) suspend bit after bit (0x12) lowpower\_mode has been set to '1'. It is also possible to enter normal mode by performing a softreset as described in chapter 4.8.

In **low-power mode 1**, the device is periodically switching between a sleep phase and a wake-up phase. The wake-up phase essentially corresponds to operation in normal mode with complete power-up of the circuitry. The sleep phase essentially corresponds to operation in suspend mode. Low-power mode is entered (left) by writing '1' ('0') to the (0x11) lowpower\_en bit with bit (0x12) lowpower\_mode set to '0'. Read access to registers is possible except from the (0x3F) fifo\_data register. However, unless the register access is synchronised with the wake-up phase, the restrictions of the suspend mode apply.

**Low-power mode 2** is very similar to low-power mode 1, but register access is possible at any time without restrictions. It consumes more power than low-power mode 1. In low-power mode 2 the device is periodically switching between a sleep phase and a wake-up phase. The wake-up phase essentially corresponds to operation in normal mode with complete power-up of the circuitry. The sleep phase essentially corresponds to operation in standby mode. Low-power mode is entered (left) by writing '1' ('0') to the (0x11) lowpower\_en bit with bit (0x12) lowpower\_mode set to '1'.

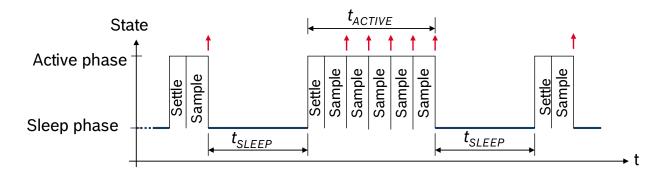

The timing behaviour of the low-power modes 1 and 2 depends on the setting of the (0x12) sleeptimer\_mode bit. When (0x12) sleeptimer\_mode is set to '0', the event-driven time-base mode (EDT) is selected. In EDT the duration of the wake-up phase depends on the number of samples required by the enabled interrupt engines. If an interrupt is detected, the device stays in the wake-up phase as long as the interrupt condition endures (non-latched interrupt), or until the latch time expires (temporary interrupt), or until the interrupt is reset (latched interrupt). If no interrupt is detected, the device enters the sleep phase immediately after the required number of acceleration samples have been taken and an active interface access cycle has ended. The EDT mode is recommended for power-critical applications which do not use the FIFO. Also, EDT mode is compatible with legacy BST sensors. Figure 3 shows the timing diagram for low-power modes 1 and 2 when EDT is selected.

Figure 3: Timing Diagram for low-power mode 1/2, EDT

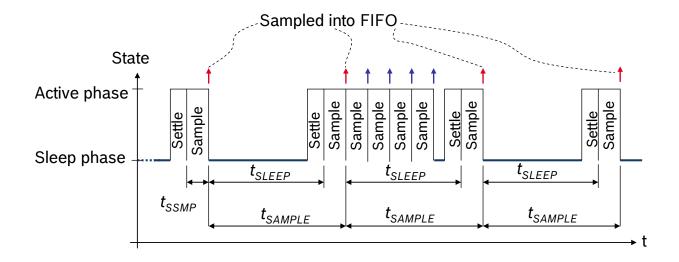

When (0x12) sleeptimer\_mode is set to '1', the equidistant-sampling mode (EST) is selected. The use of the EST mode is recommended when the FIFO is used since it ensures that equidistant samples are sampled into the FIFO regardless of whether the active phase is extended by active interrupt engines or interface activity. In EST mode the sleep time  $t_{SLEEP}$  is defined as shown in Figure 4. The FIFO sampling time  $t_{SAMPLE}$  is the sum of the sleep time  $t_{SLEEP}$  and the sensor data sampling time  $t_{SSMP}$ . Since interrupt engines can extend the active phase to exceed the sleep time  $t_{SLEEP}$ , equidistant sampling is only guaranteed if the bandwidth has been chosen such that  $1/(2 * bw) = n * t_{SLEEP}$  where n is an integer. If this condition is infringed, equidistant sampling is not possible. Once the sleep time has elapsed the device will store the next available sample in the FIFO. This set-up condition is not recommended as it may result in timing jitter.

Figure 4: Timing Diagram for low-power mode 1/2, EST

The sleep time for lower-power mode 1 and 2 is set by the (0x11) sleep\_dur bits as shown in the following table:

Table 3: Sleep phase duration settings

| (0x11)<br>sleep_dur | Sleep Phase<br>Duration<br>t <sub>sleep</sub> |

|---------------------|-----------------------------------------------|

| 0000b               | 0.5ms                                         |

| 0001b               | 0.5ms                                         |

| 0010b               | 0.5ms                                         |

| 0011b               | 0.5ms                                         |

| 0100b               | 0.5ms                                         |

| 0101b               | 0.5ms                                         |

| 0110b               | 1ms                                           |

| 0111b               | 2ms                                           |

| 1000b               | 4ms                                           |

| 1001b               | 6ms                                           |

| 1010b               | 10ms                                          |

| 1011b               | 25ms                                          |

| 1100b               | 50ms                                          |

| 1101b               | 100ms                                         |

| 1110b               | 500ms                                         |

| 1111b               | 1s                                            |

The current consumption of the BMA253 in low-power mode 1 ( $I_{DDlp1}$ ) and low-power mode 2 ( $I_{DDlp2}$ ) can be estimated with the following formulae:

$$I_{DDlp1} \approx \frac{t_{sleep} \cdot I_{DDsum} + t_{active} \cdot I_{DD}}{t_{sleep} + t_{active}} \,.$$

$$I_{DDlp2} \approx \frac{t_{sleep} \cdot I_{DDsbm} + t_{active} \cdot I_{DD}}{t_{sleep} + t_{active}}$$

When estimating the length of the wake-up phase  $t_{active}$ , the corresponding typical wake-up time,  $t_{w,up1}$  or  $t_{w,up2}$  and  $t_{ut}$  (given in Table 4) have to be considered:

If bandwidth is >=31.25 Hz:

$$t_{active} = t_{ut} + t_{w,up1} - 0.9 \text{ ms}$$

(or  $t_{active} = t_{ut} + t_{w,up2} - 0.9 \text{ ms}$ ) else:  $t_{active} = 4 t_{ut} + t_{w,up1} - 0.9 \text{ ms}$  (or  $t_{active} = 4 t_{ut} + t_{w,up2} - 0.9 \text{ ms}$ )

During the wake-up phase all analog modules are held powered-up, while during the sleep phase most analog modules are powered down. Consequently, a wake-up time of at least  $t_{w,up1}$  ( $t_{w,up2}$ ) is needed to settle the analog modules so that reliable acceleration data are generated.

Page 18

#### 4.3 Sensor data

#### 4.3.1 Acceleration data

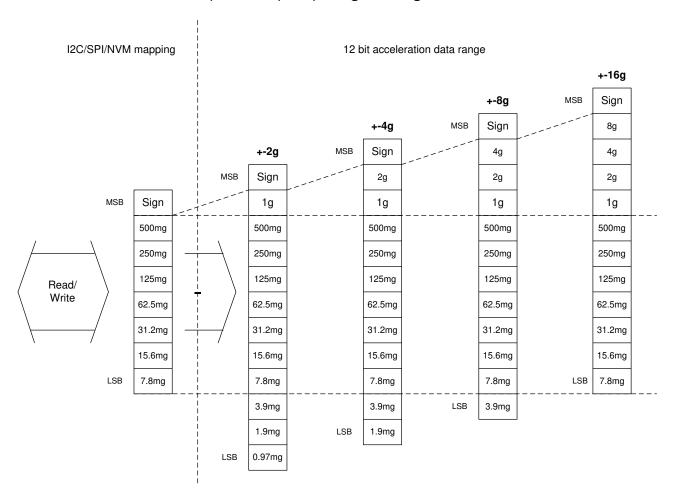

The width of acceleration data is 12 bits given in two's complement representation. The 12 bits for each axis are split into an MSB upper part (one byte containing bits 11 to 4) and an LSB lower part (one byte containing bits 3 to 0 of acceleration and a (0x02, 0x04, 0x06) new\_data flag). Reading the acceleration data registers shall always start with the LSB part. In order to ensure the integrity of the acceleration data, the content of an MSB register is locked by reading the corresponding LSB register (shadowing procedure). When shadowing is enabled, the MSB must always be read in order to remove the data lock. The shadowing procedure can be disabled (enabled) by writing '1' ('0') to the bit shadow\_dis. With shadowing disabled, the content of both MSB and LSB registers is updated by a new value immediately. Unused bits of the LSB registers may have any value and should be ignored. The (0x02, 0x04, 0x06) new\_data flag of each LSB register is set if the data registers have been updated. The flag is reset if either the corresponding MSB or LSB part is read.

Two different streams of acceleration data are available, unfiltered and filtered. The unfiltered data is sampled with 2kHz. The sampling rate of the filtered data depends on the selected filter bandwidth and is always twice the selected bandwidth (BW = ODR/2). Which kind of data is stored in the acceleration data registers depends on bit (0x13)  $data_high_bw$  is '0' ('1'), then filtered (unfiltered) data is stored in the registers. Both data streams are offset-compensated.

The bandwidth of filtered acceleration data is determined by setting the (0x10) bw bit as followed:

| bw    | Bandwidth | Update Time t <sub>ut</sub> |

|-------|-----------|-----------------------------|

| 00xxx | *)        | -                           |

| 01000 | 7.81Hz    | 64ms                        |

| 01001 | 15.63Hz   | 32ms                        |

| 01010 | 31.25Hz   | 16ms                        |

| 01011 | 62.5Hz    | 8ms                         |

| 01100 | 125Hz     | 4ms                         |

| 01101 | 250Hz     | 2ms                         |

| 01110 | 500Hz     | 1ms                         |

| 01111 | 1000Hz    | 0.5ms                       |

| 1xxxx | *)        | -                           |

Table 4: Bandwidth configuration

<sup>\*)</sup> Note: Settings 00xxx result in a bandwidth of 7.81 Hz; settings 1xxxx result in a bandwidth of 1000 Hz. It is recommended to actively set an application specific and an appropriate bandwidth and to use the range from '01000b' to '01111b' only in order to be compatible with future products.

Page 19

The BMA253 supports four different acceleration measurement ranges. A measurement range is selected by setting the (0x0F) range bits as follows:

Table 5: Range selection

| Range  | Acceleration measurement range | Resolution |

|--------|--------------------------------|------------|

| 0011   | ±2g                            | 0.98mg/LSB |

| 0101   | ±4g                            | 1.95mg/LSB |

| 1000   | ±8g                            | 3.91mg/LSB |

| 1100   | ±16g                           | 7.81mg/LSB |

| others | reserved                       | -          |

#### 4.3.2 Temperature sensor

The width of temperature data is 8 bits given in two's complement representation. Temperature values are available in the (0x08) temp register.

The slope of the temperature sensor is 0.5 K/LSB, its center temperature is  $23^{\circ}\text{C}$  [(0x08) temp = 0x00].

Page 20

#### 4.4 Self-test

This feature permits to check the sensor functionality by applying electrostatic forces to the sensor core instead of external accelerations. By actually deflecting the seismic mass, the entire signal path of the sensor can be tested. Activating the self-test results in a static offset of the acceleration data; any external acceleration or gravitational force applied to the sensor during active self-test will be observed in the output as a superposition of both acceleration and self-test signal.

Before the self-test is enabled the g-range should be set to 8 g.The self-test is activated individually for each axis by writing the proper value to the (0x32) self\_test\_axis bits ('01b' for x-axis, '10b' for y-axis, '11b' for z-axis, '00b' to deactivate self-test). It is possible to control the direction of the deflection through bit (0x32) self\_test\_sign. The excitation occurs in negative (positive) direction if (0x32) self\_test\_sign = '0b' ('1b'). The amplitude of the deflection has to be set high by writing (0x32) self\_test\_amp='1b'. After the self-test is enabled, the user should wait 50ms before interpreting the acceleration data.

In order to ensure a proper interpretation of the self-test signal it is recommended to perform the self-test for both (positive and negative) directions and then to calculate the difference of the resulting acceleration values. Table 6 shows the minimum differences for each axis. The actually measured signal differences can be significantly larger.

Table 6: Self-test difference values

|                                     | x-axis signal | y-axis signal | z-axis signal |

|-------------------------------------|---------------|---------------|---------------|

| resulting minimum difference signal | 800 mg        | 800 mg        | 400 mg        |

It is recommended to perform a reset of the device after a self-test has been performed. If the reset cannot be performed, the following sequence must be kept to prevent unwanted interrupt generation: disable interrupts, change parameters of interrupts, wait for at least 50ms, enable desired interrupts.

#### 4.5 Offset compensation

Offsets in measured signals can have several causes but they are always unwanted and disturbing in many cases. Therefore, the BMA253 offers an advanced set of four digital offset compensation methods which are closely matched to each other. These are slow, fast, and manual compensation as well as inline calibration.

The compensation is performed with unfiltered data, and is then applied to both, unfiltered and filtered data. If necessary the result of this computation is saturated to prevent any overflow errors (the smallest or biggest possible value is set, depending on the sign). However, the registers used to read and write compensation values have only a width of 8 bits.

An overview of the offset compensation principle is given in figure 5:

Figure 5: Principle of offset compensation

Page 22

The public offset compensation registers (0x38) offset\_x, (0x39) offset\_y, (0x3A) offset\_z are images of the corresponding registers in the NVM. With each image update (see section 4.6 Non-volatile memory for details) the contents of the NVM registers are written to the public registers. The public registers can be over-written by the user at any time. After changing the contents of the public registers by either an image update or manually, all 8bit values are extended to 12bit values for internal computation. In the opposite direction, if an internally computed value changes it is converted to an 8bit value and stored in the public register.

Depending on the selected g-range the conversion from 12bit to 8bit values can result in a loss of accuracy of one to several LSB. This is shown in figure 5.

In case an internally computed compensation value is too small or too large to fit into the corresponding register, it is saturated in order to prevent an overflow error.

By writing '1' to the (0x36) offset\_reset bit, all offset compensation registers are reset to zero.

#### 4.5.1 Slow compensation

Slow compensation is based on a  $1^{st}$  order high-pass filter, which continuously drives the average value of the output data stream of each axis to zero. The bandwidth of the high-pass filter is configured with bit (0x37) cut\_off according to Table 7.

Table 7: Compensation period settings

| (0x37)<br>cut_off | high-pass filter<br>bandwidth      | Example<br>bw = 500 Hz                          |

|-------------------|------------------------------------|-------------------------------------------------|

| 0b                | $\frac{1Hz \times bw *}{1000 Hz}$  | $\frac{1Hz \times 500  Hz}{1000  Hz} = 0.5  Hz$ |

| 1b                | $\frac{10Hz \times bw *}{1000 Hz}$ | $\frac{10Hz \times 500Hz}{1000Hz} = 5Hz$        |

<sup>\*</sup>bw: please insert selected decimal data bandwidth value [Hz] from table 4

The slow compensation can be enabled (disabled) for each axis independently by setting the bits  $(0x36) hp_xen, hp_yen, hp_zen$  to '1' ('0'), respectively.

Slow compensation should not be used in combination with low-power mode. In low-power mode the conditions (availability of necessary data) for proper function of slow compensation are not fulfilled.

#### 4.5.2 Fast compensation

Fast compensation is a one-shot process by which the compensation value is set in such a way that when added to the raw acceleration, the resulting acceleration value of each axis approaches the target value. This is best suited for "end-of-line trimming" with the customer's device positioned in a well-defined orientation. For fast compensation the g-range has to be switched to 2g.

The algorithm in detail: An average of 16 consecutive acceleration values is computed and the difference between target value and computed value is written to (0x38, 0x39, 0x34) offset\_filt\_x/y/z. The public registers (0x38, 0x39, 0x34) offset\_filt\_x/y/z are updated with the contents of the internal registers (using saturation if necessary) and can be read by the user.

Fast compensation is triggered for each axis individually by setting the (0x36) cal\_trigger bits as shown in Table 8:

Table 8: Fast compensation axis selection

| (0x36)<br>cal_trigger | Selected Axis |

|-----------------------|---------------|

| 00b                   | none          |

| 01b                   | X             |

| 10b                   | у             |

| 11b                   | Z             |

Page 24

Register (0x36) cal\_trigger is a write-only register. Once triggered, the status of the fast correction process is reflected in the status bit (0x36) cal\_rdy. Bit (0x36) cal\_rdy is '0' while the correction is in progress. Otherwise it is '1'. Bit (0x36) cal\_rdy is '0' when (0x36) cal\_trigger is not '00'.

For the fast offset compensation, the compensation target can be chosen by setting the bits (0x37) offset\_target\_x, (0x37) offset\_target\_y, and (0x37) offset\_target\_z according to Table 9:

(0x37)

Target value

00b

0g

01b

+1g

-1g

0g

10b

11b

Table 9: Offset target settings

Fast compensation should not be used in combination with any of the low-power modes. In low-power mode the conditions (availability of necessary data) for proper function of fast compensation are not fulfilled.

#### 4.5.3 Manual compensation

The contents of the public compensation registers (0x38, 0x39, 0x3A) offset\_filt\_x/y/z can be set manually via the digital interface. It is recommended to write into these registers directly after a new data interrupt has occurred in order not to disturb running offset computations.

Writing to the offset compensation registers is not allowed while the fast compensation procedure is running.

#### 4.5.4 Inline calibration

For certain applications, it is often desirable to calibrate the offset once and to store the compensation values permanently. This can be achieved by using one of the aforementioned offset compensation methods to determine the proper compensation values and then storing these values permanently in the NVM. See section 4.6 Non-volatile memory for details of the storing procedure.

Each time the device is reset, the compensation values are loaded from the non-volatile memory into the image registers and used for offset compensation until they are possibly overwritten using one of the other compensation methods.

Page 25

#### 4.6 Non-volatile memory

The entire memory of the BMA253 consists of three different kinds of registers: hard-wired, volatile, and non-volatile. Part of it can be both read and written by the user. Access to non-volatile memory is only possible through (volatile) image registers.

Altogether, there are eight registers (octets) with NVM backup which are accessible by the user. The addresses of the image registers range from 0x38 to 0x3C. While the addresses up to 0x3A are used for offset compensation (see 4.4 Offset Compensation), addresses 0x3B and 0x3C are general purpose registers not linked to any sensor-specific functionality.

The content of the NVM is loaded to the image registers after a reset (either POR or softreset) or after a user request which is performed by writing '1' to the write-only bit (0x33)  $nvm_load$ . As long as the image update is in progress, bit (0x33)  $nvm_rdy$  is '0', otherwise it is '1'.

The image registers can be read and written like any other register.

Writing to the NVM is a three-step procedure:

- 1. Write the new contents to the image registers.

- 2. Write '1' to bit (0x33) nvm\_prog\_mode in order to unlock the NVM.

- 3. Write '1' to bit (0x33) nvm\_prog\_trig and keep '1' in bit (0x33) nvm\_prog\_mode in order to trigger the write process.

Writing to the NVM always renews the entire NVM contents. It is possible to check the write status by reading bit  $(0x33) \ nvm_rdy$ . While  $(0x33) \ nvm_rdy = '0'$ , the write process is still in progress; if  $(0x33) \ nvm_rdy = '1'$ , then writing is completed. As long as the write process is ongoing, no change of power mode and image registers is allowed. Also, the NVM write cycle must not be initiated while image registers are updated, in low-power mode, and in suspend mode.

Please note that the number of permitted NVM write-cycles is limited as specified in Table 1. The number of remaining write-cycles can be obtained by reading bits (0x33)  $nvm_remain$ .