Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

**Data Sheet**

# **BMA456**Digital, triaxial acceleration sensor

**Bosch Sensortec**

### **Data Sheet BMA456**

Part number(s) 0 273 141 282

Document revision 1.1

Release date 26 October 2017

Document number BST-BMA456-DS000-01

Notes Subject to change without notice.

Product photos and pictures are for illustration purposes only and may

differ from the real product's appearance.

Page 2

16 bit, digital, triaxial acceleration sensor with intelligent on-chip motion-triggered interrupt features optimized for wearable applications.

### **Key features**

• Small package size LGA package (12 pins), footprint 2mm x 2mm,

height 0.65 mm

Digital interface

SPI (4-wire, 3-wire), I<sup>2</sup>C, 2 interrupt pins

V<sub>DDIO</sub> voltage range: 1.2V to 3.6V

Programmable functionality

Acceleration ranges ±2g/±4g/±8g/±16g

Low-pass filter bandwidths 684Hz - <8Hz up to a max. output data read out of 1.6 kHz

On-chip FIFO

Integrated FIFO on sensor with 1 kb

On-chip interrupt features

Step Counter optimized for wearable devices

Activity Recognition: Running, Walking, Still

Tilt-On-Wrist detection

Tap/Double tap interrupt

Any-/No-Motion interrupt

Ultra-low power

Low current consumption of data acquisition and all

integrated features

• (Secondary) Auxiliary Interface Hub for ext. Magnetometer and data synchronization

RoHS compliant, halogen-free

### Typical applications

Applications with height constrains

- Plug 'n' Play Step-Counter solution with watermark functionality

- Fitness applications / Activity Tracking

- Power management for wearable applications

- Display on/off and profile switching

- User interface without hardware buttons

- E-compass tilt compensation and data synchronization

- High performance angle measurements

### **Table of contents**

| 1. | SPECIFICATION                                    | 7  |

|----|--------------------------------------------------|----|

| 2. | ABSOLUTE MAXIMUM RATINGS                         | 10 |

| 3. | QUICK START GUIDE                                | 11 |

|    | Note about using the BMA456:                     |    |

|    | First application setup examples algorithms:     |    |

| 4. | FUNCTIONAL DESCRIPTION                           | 15 |

| _  | 4.1. SUPPLY VOLTAGE AND POWER MANAGEMENT         | 16 |

|    | 4.2. DEVICE INITIALIZATION                       |    |

|    | 4.3. Power Modes                                 |    |

|    |                                                  | _  |

|    | 4.4. SENSOR DATA                                 |    |

|    | Filter Settings                                  |    |

|    | Accelerometer data processing for low power mode |    |

|    | Data Ready Interrupt                             |    |

|    | Temperature Sensor                               |    |

|    | Sensor Time                                      |    |

|    | Configuration Changes                            |    |

| _  | 4.5. FIFO                                        | 24 |

|    | Frames                                           |    |

|    | Conditions and Details                           |    |

|    | FIFO data synchronization                        | 29 |

|    | FIFO synchronization with external interrupts    | 30 |

|    | FIFO Interrupts                                  | 30 |

|    | FIFO Reset                                       | 30 |

| 4  | 4.6. Interrupt Features                          | 31 |

|    | Global Configuration                             | 31 |

|    | Step Detector / Step Counter                     | 33 |

|    | Walking activity recognition                     | 36 |

|    | Tilt on Wrist                                    |    |

|    | Double tap / Tap detection                       |    |

|    | Any Motion / No motion detection                 | 41 |

| 4  | 4.7. GENERAL INTERRUPT PIN CONFIGURATION         | 43 |

|    | Electrical Interrupt Pin Behavior                |    |

|    | Interrupt Pin Mapping                            | 43 |

| 4  | 4.8. AUXILIARY SENSOR INTERFACE                  | 44 |

|    | Structure and Concept                            | 44 |

|    | Interface Configuration                          |    |

|    | Setup mode (AUX_IF_CONF.aux_manual_en =0b1)      |    |

|    | Data mode (AUX_IF_CONF.aux_manual_en=0)          |    |

|    | Delay (Time Offset)                              | 48 |

Page 4

|   | 4.9.  | SENSOR SELF-TEST                         | 49 |

|---|-------|------------------------------------------|----|

|   | 4.10. | Offset Compensation                      | 50 |

|   | Mai   | nual Offset Compensation                 | 50 |

|   | Inlir | ne Calibration                           | 50 |

|   | 4.11. | Non-Volatile Memory                      | 51 |

|   | 4.12. | Soft-Reset                               | 51 |

| 5 | . RE  | GISTER DESCRIPTION                       | 52 |

|   | 5.1.  | General Remarks                          |    |

|   |       |                                          |    |

|   | 5.2.  |                                          |    |

|   | _     | gister (0x00) CHIP_ID                    |    |

|   | _     | gister (0x02) ERR_REG                    |    |

|   | _     | gister (0x03) STATUS                     |    |

|   | _     | gister (0x0A) DATA_0                     |    |

|   | _     | gister (0x0B) DATA_1                     |    |

|   | _     | gister (0x0C) DATA_2gister (0x0D) DATA_3 |    |

|   | _     | gister (0x0E) DATA_3gister (0x0E) DATA 4 |    |

|   | _     | gister (0x0F) DATA_4gister (0x0F) DATA_5 |    |

|   | _     | gister (0x10) DATA_5                     |    |

|   | _     | gister (0x10) DATA_0gister (0x11) DATA_7 |    |

|   | _     | gister (0x12) DATA_r                     |    |

|   | _     | gister (0x13) DATA_0                     |    |

|   | _     | gister (0x14) DATA 10                    |    |

|   | _     | gister (0x15) DATA 11                    |    |

|   | _     | gister (0x16) DATA 12                    |    |

|   | _     | gister (0x17) DATA 13                    |    |

|   | _     | gister (0x18) SENSORTIME 0               |    |

|   | _     | gister (0x19) SENSORTIME_1               |    |

|   |       | gister (0x1A) SENSORTIME_2               |    |

|   |       | gister (0x1B) EVENT                      |    |

|   | Re    | gister (0x1C) INT_STATUS_0               | 72 |

|   |       | gister (0x1D) INT_STATUS_1               |    |

|   | Reg   | gister (0x1E) STEP_COUNTER_0             | 73 |

|   | Reg   | gister (0x1F) STEP_COUNTER_1             | 74 |

|   | Reg   | gister (0x20) STEP_COUNTER_2             | 74 |

|   | Reg   | gister (0x21) STEP_COUNTER_3             | 75 |

|   | Reg   | gister (0x22) TEMPERATURE                | 75 |

|   | Reg   | gister (0x24) FIFO_LENGTH_0              | 76 |

|   |       | gister (0x25) FIFO_LENGTH_1              |    |

|   |       | gister (0x26) FIFO_DATA                  |    |

|   |       | gister (0x27) ACTIVITY_TYPE              |    |

|   | _     | gister (0x2A) INTERNAL_STATUS            |    |

|   | Reg   | gister (0x40) ACC_CONF                   | 79 |

|      | egister (0x41) ACC_RANGE                              |     |

|------|-------------------------------------------------------|-----|

|      | egister (0x44) AUX_CONF                               |     |

|      | egister (0x45) FIFO_DOWNS                             |     |

|      | egister (0x46) FIFO_WTM_0                             |     |

|      | egister (0x47) FIFO_WTM_1egister (0x48) FIFO_CONFIG_0 |     |

|      | egister (0x49) FIFO_CONFIG_0                          |     |

|      | egister (0x4B) AUX_DEV_ID                             |     |

|      | egister (0x4C) AUX IF CONF                            |     |

|      | egister (0x4D) AUX_RD_ADDR                            |     |

| Re   | egister (0x4E) AUX_WR_ADDR                            | 86  |

|      | egister (0x4F) AUX_WR_DATA                            |     |

|      | egister (0x53) INT1_IO_CTRL                           |     |

|      | egister (0x54) INT2_IO_CTRL                           |     |

|      | egister (0x55) INT_LATCHegister (0x56) INT1 MAP       |     |

|      | egister (0x56) INT1_MAPegister (0x57) INT2_MAP        |     |

|      | egister (0x58) INT_MAP_DATA                           |     |

|      | egister (0x59) INIT CTRL                              |     |

|      | egister (0x5E) FEATURES_IN                            |     |

| Re   | egister (0x5F) INTERNAL_ERROR                         | 96  |

|      | egister (0x6A) NVM_CONF                               |     |

|      | egister (0x6B) IF_CONF                                |     |

|      | egister (0x6D) ACC_SELF_TEST                          |     |

|      | egister (0x70) NV_CONFegister (0x71) OFFSET 0         |     |

|      | egister (0x71) OFFSET_1                               |     |

|      | egister (0x73) OFFSET_2                               |     |

|      | egister (0x7C) PWR CONF                               |     |

| Re   | egister (0x7D) PWR_CTRL                               | 101 |

| Re   | egister (0x7E) CMD                                    | 101 |

| DI   | GITAL INTERFACES                                      | 103 |

| 6.1. | Interfaces                                            | 103 |

| 6.2. | PRIMARY INTERFACE                                     | 104 |

| 6.3. | PRIMARY INTERFACE I2C/SPI PROTOCOL SELECTION          | 105 |

| 6.4. | SPI INTERFACE AND PROTOCOL                            | 105 |

| 6.5. | PRIMARY I2C INTERFACE                                 | 110 |

| 6.6. | SPI AND I <sup>2</sup> C Access Restrictions          | 114 |

| 6.7. | AUXILIARY INTERFACE                                   | 114 |

| PII  | N-OUT AND CONNECTION DIAGRAMS                         | 115 |

| 7.1. | PIN-OUT                                               | 115 |

| 7.2. | CONNECTION DIAGRAMS WITHOUT AUXILIARY INTERFACE       | 116 |

6.

7.

Page 6

| SF      | o                                            | 116 |

|---------|----------------------------------------------|-----|

| 12      | C                                            | 117 |

| 7.3.    | CONNECTION DIAGRAMS WITH AUXILIARY INTERFACE | 117 |

|         | 인<br>-                                       |     |

| 120     | C                                            | 118 |

| B. PA   | ACKAGE                                       | 119 |

| 8.1.    | PACKAGE OUTLINE DIMENSIONS                   | 119 |

| 8.2.    | SENSING AXIS ORIENTATION                     | 120 |

| 8.3.    | LANDING PATTERN RECOMMENDATION               | 122 |

| 8.4.    | Marking                                      | 123 |

|         | ass production                               |     |

| Er      | ngineering samples                           | 123 |

| 8.5.    | SOLDERING GUIDELINES                         | 124 |

| 8.6.    | HANDLING INSTRUCTIONS                        | 125 |

| 8.7.    | TAPE AND REEL SPECIFICATION                  | 126 |

| 8.8.    | ENVIRONMENTAL SAFETY                         | 127 |

|         | alogen content                               |     |

| Int     | ernal package structure                      | 127 |

| 9. LE   | GAL DISCLAIMER                               | 128 |

| 9.1. EN | NGINEERING SAMPLES                           | 128 |

| 9.2. PF | RODUCT USE                                   | 128 |

| 9.3. AI | PPLICATION EXAMPLES AND HINTS                | 128 |

| 10 D    | OCUMENT HISTORY AND MODIFICATION             | 129 |

Page 7

### 1. Specification

Unless stated otherwise, the given values are over lifetime, operating temperature and voltage ranges. Minimum/maximum values are  $\pm 3\sigma$ .

### **Parameter Specification**

|                                                   |                    | OPERATING CONI                                                          | DITIONS              |     |                      |        |

|---------------------------------------------------|--------------------|-------------------------------------------------------------------------|----------------------|-----|----------------------|--------|

| Parameter                                         | Symbol             | Condition                                                               | Min                  | Тур | Max                  | Units  |

| Acceleration                                      | <b>g</b> FS2g      | Selectable                                                              |                      | ±2  |                      | g      |

| Range                                             | <b>g</b> FS4g      | via serial digital<br>interface                                         |                      | ±4  |                      | g      |

|                                                   | <b>g</b> FS8g      | interface                                                               |                      | ±8  |                      | g      |

|                                                   | <b>g</b> FS16g     |                                                                         |                      | ±16 |                      | g      |

| Supply Voltage<br>Internal Domains                | $V_{DD}$           |                                                                         | 1.62                 | 1.8 | 3.6                  | V      |

| Supply Voltage<br>I/O Domain                      | $V_{DDIO}$         |                                                                         | 1.2                  | 1.8 | 3.6                  | V      |

| Voltage Input<br>Low Level                        | $V_{IL}$           | SPI & I <sup>2</sup> C                                                  |                      |     | 0.3V <sub>DDIO</sub> | -      |

| Voltage Input<br>High Level                       | V <sub>IH</sub>    | SPI & I <sup>2</sup> C                                                  | $0.7V_{DDIO}$        |     |                      | -      |

| Voltage Output<br>Low Level                       | V <sub>OL</sub>    | $V_{DDIO}$ >=1.62V,<br>$I_{OL}$ <=2mA, SPI                              |                      |     | 0.2V <sub>DDIO</sub> | -      |

|                                                   |                    | $V_{DDIO}$ <1.62V, $I_{OL}$ <=1.5mA, SPI                                |                      |     | $0.2V_{\text{DDIO}}$ | -      |

| Voltage Output<br>High Level                      | V <sub>OH</sub>    | $V_{DDIO}$ >=1.62V,<br>$I_{OH}$ <=2mA, SPI                              | 0.8V <sub>DDIO</sub> |     |                      | -      |

|                                                   |                    | $V_{DDIO}$ <=1.62V,<br>$I_{OH}$ <=1.5mA, SPI                            | 0.8V <sub>DDIO</sub> |     |                      | -      |

| Total Supply<br>Current in<br>Performance<br>mode | I <sub>DD</sub>    | Nominal V <sub>DD</sub> and V <sub>DDIO</sub> , 25°C, g <sub>FS4g</sub> |                      | 150 |                      | μΑ     |

| Total Supply<br>Current in<br>Suspend Mode        | DDsum              | Nominal $V_{DD}$ and $V_{DDIO}$ , 25°C                                  |                      | 3.5 |                      | μΑ     |

| Total Supply<br>Current in<br>Low-power Mode      | I <sub>DDlp1</sub> | Nominal $V_{DD}$ and $V_{DDIO}$ , 25°C 50 Hz ODR                        |                      | 14  |                      | μΑ     |

| Power-Up Time                                     | ts_up              |                                                                         |                      |     | 1                    | ms     |

| Non-volatile<br>memory (NVM)<br>write-cycles      | n <sub>NVM</sub>   |                                                                         |                      |     | 15                   | cycles |

BST-BMA456-DS000-01 | Version 1.1 | October 2017

<sup>©</sup> Bosch Sensortec GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of disposal such as copying and passing on to third parties. BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany.

Note: Specifications within this document are subject to change without notice.

Page 8

| Operating<br>Temperature           | T <sub>A</sub>      |                                                                         | -40  |                            | +85  | °C          |

|------------------------------------|---------------------|-------------------------------------------------------------------------|------|----------------------------|------|-------------|

|                                    |                     | OUTPUT SIGN                                                             | ΑL   |                            |      |             |

| Parameter                          | Symbol              | Condition                                                               | Min  | Тур                        | Max  | Units       |

| Sensitivity                        | S <sub>2g</sub>     | g <sub>FS2g</sub> , T <sub>A</sub> =25°C                                |      | 16384                      |      | LSB/g       |

|                                    | S <sub>4g</sub>     | g <sub>FS4g</sub> , T <sub>A</sub> =25°C                                |      | 8192                       |      | LSB/g       |

|                                    | S <sub>8g</sub>     | $g_{FS8g}$ , $T_A=25$ °C                                                |      | 4096                       |      | LSB/g       |

|                                    | S <sub>16g</sub>    | $g_{FS16g}$ , $T_A=25$ °C                                               |      | 2048                       |      | LSB/g       |

| Sensitivity Temperature Drift      | TCS                 |                                                                         |      | 0.005                      |      | %/K         |

| Zero-g Offset                      | Off                 | Nominal $V_{DD}$ and $VDD_{IO}$ , 25°C, $g_{FS4g}$                      |      | 20                         |      | mg          |

| Zero-g Offset<br>Temperature Drift | TCO                 | X/Y - Axes                                                              |      | 0.2                        |      | mg/K        |

|                                    |                     | Z-Axis                                                                  |      | 0.35                       |      | mg/K        |

| Output Data Rate                   | ODR <sub>PERF</sub> | Performance mode                                                        | 12.5 |                            | 1600 | Hz          |

|                                    | ODR <sub>12.5</sub> |                                                                         |      | 5.06                       |      | Hz          |

|                                    | ODR <sub>25</sub>   |                                                                         |      | 10.12                      |      | Hz          |

|                                    | ODR <sub>50</sub>   |                                                                         |      | 20.25                      |      | Hz          |

|                                    | ODR <sub>100</sub>  |                                                                         |      | 40.5                       |      | Hz          |

| Output data rate                   | ODR <sub>200</sub>  | 3dB cutoff frequency                                                    |      | 80                         |      | Hz          |

| and BW in<br>Performance<br>mode   | ODR <sub>400</sub>  | of the accelerometer according to ODR with normal filter                |      | 162 (155<br>for Z<br>axis) |      | Hz          |

| mode                               | ODR <sub>800</sub>  | mode                                                                    |      | 324<br>(262 for<br>Z axis) |      | Hz          |

|                                    | ODR <sub>1600</sub> |                                                                         |      | 684<br>(353 for<br>Z axis) |      | HZ          |

| Output Data Rate                   | $ODR_{LPM}$         | Low-power mode                                                          | 0.78 |                            | 400  | Hz          |

| Nonlinearity                       | NL                  | Nominal V <sub>DD</sub> and VDD <sub>IO</sub> , 25°C, g <sub>FS4g</sub> |      | 0.5                        |      | %FS         |

| Output Noise<br>Density            | n <sub>dens</sub>   | Nominal V <sub>DD</sub> and VDD <sub>IO</sub> , 25°C, g <sub>FS4g</sub> |      | 120                        |      | µg/√Hz      |

| Power Supply<br>Rejection Ratio    | PSRR                |                                                                         |      | 1                          |      | mg/50m<br>V |

BST-BMA456-DS000-01 | Version 1.1 | October 2017

Page 9

| MECHANICAL CHARACTERISTICS |                |                                                               |     |     |     |       |  |  |  |  |

|----------------------------|----------------|---------------------------------------------------------------|-----|-----|-----|-------|--|--|--|--|

| Parameter                  | Symbol         | Condition                                                     | Min | Тур | Max | Units |  |  |  |  |

| Cross Axis<br>Sensitivity  | S              | relative contribution<br>between any two of<br>the three axes |     | 0.5 |     | %     |  |  |  |  |

| Alignment Error            | E <sub>A</sub> | relative to package<br>outline                                |     | 0.5 |     | 0     |  |  |  |  |

BST-BMA456-DS000-01 | Version 1.1 | October 2017

### 2. Absolute maximum ratings

### **Absolute maximum ratings**

| Parameter                   | Condition                    | Min  | Max                   | Units |

|-----------------------------|------------------------------|------|-----------------------|-------|

| Voltage at Supply Pin       | V <sub>DD</sub> Pin          | -0.3 | 4                     | V     |

|                             | V <sub>DDIO</sub> Pin        | -0.3 | 4                     | V     |

| Voltage at any Logic Pin    | Non-Supply Pin               | -0.3 | $V_{DDIO} + 0.3, < 4$ | V     |

| Passive Storage Temp. Range | ≤ 65% rel. H.                | -50  | +150                  | °C    |

| None-volatile memory (NVM)  | $T = 85^{\circ}C,$           | 10   |                       | У     |

| Data Retention              | after 15 cycles              |      |                       |       |

| Mechanical Shock            | Duration ≤ 200µs             |      | 10,000                | g     |

|                             | Duration ≤ 1.0ms             |      | 2,000                 | g     |

|                             | Free fall onto hard surfaces |      | 1.8                   | m     |

| ESD, at any pin             | HBM                          |      | 2                     | kV    |

|                             | CDM                          |      | 500                   | V     |

|                             | MM                           |      | 200                   | V     |

#### Note:

Stress above these limits may cause damage to the device. Exceeding the specified electrical limits may affect the device reliability or cause malfunction.

Page 11

### 3. Quick Start Guide

The purpose of this chapter is to help developers who want to start working with the BMA456 by giving you some very basic hands-on application examples to get started.

### Note about using the BMA456:

The communication between application processor and BMA456 will happen either over i2c or spi interface. For more information about the interfaces, read the related chapter 6.

Before starting the test, the device has to be properly connected to the master (AP) and powered up. For more information about it, read the related chapter 7. Pin-out and Connection Diagrams.

### First application setup examples algorithms:

After correct power up by setting the correct voltage to the appropriate external pins, the BMA456 enters automatically into the Power On Reset (POR) sequence. In order to properly make use of the BMA456, certain steps from host processor side are needed. The most typical operations will be explained in the following application examples in form of flow-diagrams.

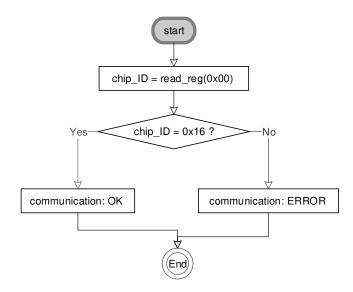

### **Example 1: Testing communication with the BMA456 and initializing feature engine**

a. -reading chip id (checking correct communication)

b. -performing initialization sequence (interrupt feature engine)

### c. -checking the correct status of the interrupt feature engine

BST-BMA456-DS000-01 | Version 1.1 | October 2017

Page 13

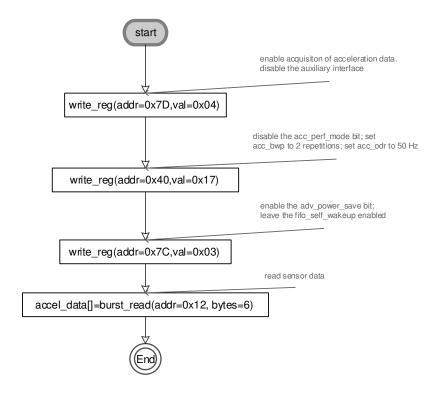

### **Example 2:** Reading acceleration data from BMA456 (example: low power mode) -setting data processing parameters (power, bandwidth, range) and reading sensor data

Page 14

### **Further steps:**

The BMA456 has many more capabilities that are described in this document and include FIFO, power saving modes, synchronization capabilities with host processor, data synchronization and integration with third party sensors, many interrupts generation and more features like step counter, etc.

### 4. Functional Description

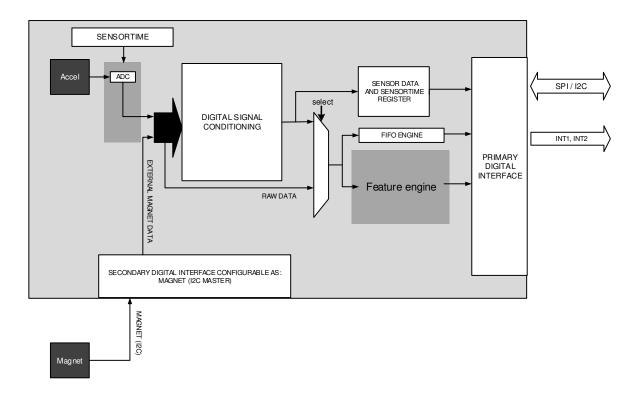

### **Block Diagram**

Page 16

### 4.1. Supply Voltage and Power Management

BMA456 has two distinct power supply pins:

- VDD is the main power supply.

- VDDIO is a separate power supply pin used for supplying power for the interface including the auxiliary interface.

There are no limitations with respect to the voltage level applied to the VDD and VDDIO pins, as long as it lies within the respective operating range. Furthermore, the device can be completely switched off (VDD= 0V) while keeping the VDDIO supply within operating range or vice versa. However if the VDDIO supply is switched off, all interface pins (CSB, SDX, SCX) must be kept close to GNDIO potential. The device is reset when the supply voltage applied to at least one supply pin VDD or VDDIO falls below the specified minimum values. No constraints exist for the minimum slew-rate of the voltage applied to the VDD and VDDIO pins.

Page 17

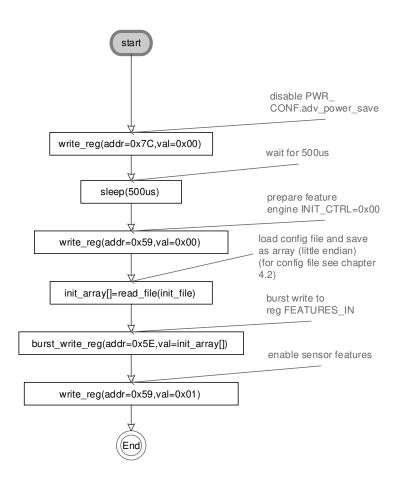

#### 4.2. Device Initialization

After power up sequence the accelerometer is in suspend mode, device must initialized through the following procedure. Initialization has to be performed as well after every POR or soft reset.

- Disable advanced power save mode: PWR\_CONF.adv\_power\_save =0b0

- Wait for 450 us. The register <u>SENSORTIME 0</u> increments every 39.25 μsec and may be used for accurate timing.

- Write INIT CTRL.init ctrl=0x00

- Load configuration file

- Burst write initialization data to Register <u>FEATURES IN</u>. The configuration file is included in the driver available on the Bosch Sensortec website (<u>www.bosch-sensortec.com</u>) or from your regional support team. Optionally the configuration file can be written to the Register <u>FEATURES IN</u> in several consecutive burst write access. Every burst write must contain an even number of bytes.

- Optionally: Burst read configuration file from Register <u>FEATURES\_IN</u> and check correctness

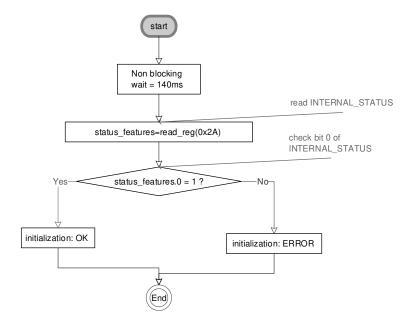

- Enable sensor features— write 0x01 into register <a href="INIT\_CTRL.init\_ctrl">INIT\_CTRL.init\_ctrl</a>. This operation must not be performed more than once after POR or softreset.

- Wait until Register <u>INTERNAL STATUS.message</u> contains the value 0b1. This will happen after at most 140-150 msec.

After initialization sequence has been completed, the device is in configuration mode (power mode). Now it is possible to switch to the required power mode and all features are ready to use as described in chapter 4.

Page 18

#### 4.3. Power Modes

The power state of the BMA456 is controlled through the registers <a href="PWR\_CONF">PWR\_CONF</a> and <a href="PWR\_CTRL">PWR\_CTRL</a> enables and disables the accelerometer and the auxiliary sensor. The Register <a href="PWR\_CONF">PWR\_CONF</a> controls which power state the sensors enter if they are enabled or disabled in the Register <a href="PWR\_CTRL">PWR\_CTRL</a>. The power state impacts the behavior of the sensor with respect to start-up time, available functions, etc. but not the sensor data quality. The sensor data quality is controlled in the Registers <a href="ACC\_CONF">ACC\_CONF</a>.

In all global power configurations both register contents and FIFO contents are retained.

<u>Low Power Mode</u>: This power configuration aggressively reduces power of the device as much as possible. The low power mode configuration is activated through enabling <u>PWR\_CONF.adv\_power\_save</u>=0b1 and disabling <u>ACC\_CONF.acc\_perf\_mode</u>=0b0. In this configuration these externally user visible features may not be available:

- Register writes need an inter-write-delay of at least 1000 us.

- The sensors log data into the FIFO in performance and low power mode. When the FIFO watermark interrupt is active, the FIFO is accessible for reading in low power mode until a burst read operation on Register FIFO DATA completes when PWR CONF.fifo self wakeup=0b1. When PWR CONF.fifo self wakeup=0b0, the user needs to disable advanced power save mode (PWR CONF.adv power save=0b0) before reading the FIFO and wait for 250 μs.

- To read out FIFO data w/o a FIFO watermark interrupt, the advanced power save configuration needs to be disabled (<u>PWR\_CONF.adv\_power\_save</u>=0b0)

The table below shows a few examples with the optimal power configurations

| Usecase                     | ACC_CONF.acc_perf_mod | PWR_CONF.adv_power_sa | PWR_CTRL.acc_en | Power consumption   |

|-----------------------------|-----------------------|-----------------------|-----------------|---------------------|

| Configuration mode          | х                     | 0                     | Х               | tbd                 |

| Suspend (lowest power mode) | Х                     | 1                     | 0               | suspend power       |

| Performance mode accel      | 1                     | Χ                     | 1               | accel power         |

| Low power mode              | 0                     | 1                     | 1               | Depends on ACC CONF |

The <u>PWR\_CTRL</u> register is used to enable and disable sensors. Per default, all sensors are disabled. Acceleration sensor must be enabled by setting <u>PWR\_CTRL.acc\_en=0b1</u>.

Page 19

The auxiliary sensor functionality is supported only when the auxiliary interface is connected for the auxiliary sensor operation. If the auxiliary interface is not used for auxiliary sensor operation, then the auxiliary sensor interface must remain disabled by setting <a href="PWR">PWR</a> CTRL.aux en=0b0 (default).

To change the power mode of the auxiliary sensor, both the power mode of the auxiliary interface and the auxiliary sensor part needs to be changed, e.g. to set the auxiliary sensor to suspend mode:

- Set the auxiliary sensor interface to suspend in Register <u>PWR\_CTRL.aux\_en</u>=0b0. Changing

the auxiliary sensor interface power mode to suspend does not imply any mode change in the

auxiliary sensor.

- The auxiliary sensor part itself must be put into suspend mode by writing the respective configuration bits of the auxiliary sensor part. The power mode of the auxiliary sensor part is controlled by setting the BMA456 auxiliary sensor interface into manual mode by <u>AUX IF CONF.aux manual en=0b1</u> and then communicating with the auxiliary sensor part through the BMA456 registers <u>AUX RD ADDR</u>, <u>AUX WR ADDR</u>, and <u>AUX WR DATA</u>. For details see Chapter 4.8.

Page 20

#### 4.4. Sensor Data

#### **Acceleration Data**

The width of acceleration data is 16 bits given in two's complement representation in the registers <a href="DATA-8">DATA-8</a> to <a href="DATA-13">DATA-13</a>. The 16 bits for each axis are split into an MSB upper part and an LSB lower part. Reading the acceleration data registers shall always start with the LSB part. In order to ensure the integrity of the acceleration data, the content of an MSB register is locked by reading the corresponding LSB register (shadowing procedure).

### **Filter Settings**

The accelerometer digital filter can be configured through the Register ACC\_CONF.

#### Note:

Illegal settings in configuration registers will result in an error code in Register <u>ERR\_REG</u>. The content of the data register is undefined, and if the FIFO is used, it may contain no value.

### Accelerometer data processing for performance mode

Performance mode is enabled with <u>ACC CONF.acc perf mode</u>=0b1. In this power mode, the accelerometer data is sampled at equidistant points in the time, defined by the accelerometer output data rate parameter <u>ACC CONF.acc odr</u>. The output data rate can be configured in one of eight different valid ODR configurations going from 12.5 Hz up to 1600Hz.

The filter bandwidth shows a 3db cutoff frequency shown in the following table:

Table 12: 3dB cutoff frequency of the accelerometer according to ODR with normal filter mode

| Accelerometer ODR [Hz]    | 12.5 | 25    | 50    | 100  | 200 | 400      | 800      | 1600     |

|---------------------------|------|-------|-------|------|-----|----------|----------|----------|

| 3dB Cutoff frequency [Hz] |      |       |       |      |     | 162      | 324      | 684      |

|                           | 5.06 | 10.12 | 20.25 | 40.5 | 80  | (155 for | (262 for | (353 for |

|                           |      |       |       |      |     | Z axis)  | Z axis)  | Z axis)  |

Page 21

### Accelerometer data processing for low power mode

Low be enabled by PWR\_CONF.adv\_power\_save=0b1 power mode can and ACC\_CONF.acc\_perf\_mode=0b0. In this power mode, the accelerometer regularly changes between a suspend power mode phase where no measurement is performed and a performance power mode phase, where data is acquired. The period of the duty cycle for changing between suspend and performance mode will be determined by the output data rate (ACC\_CONF.acc\_odr). The output data rate can be configured in one of 10 different valid ODR configurations going from 0.78Hz up to 400Hz. The samples acquired during the normal mode phase will be averaged and the result will be the output data. The number of averaged samples can be determined by the parameter ACC\_CONF.acc\_bwp through the following formula:

averaged samples = 2<sup>(Val(acc\_bwp))</sup> skipped samples = (1600/ODR)-averaged samples

A higher number of averaged samples will result in a lower noise level of the signal, but since the performance power mode phase is increased, the power consumption will also rise.

### **Data Ready Interrupt**

This interrupt fires whenever a new data sample set from accelerometer, and auxiliary sensor is complete. This allows a low latency data readout. In non-latched mode, the interrupt and the flag in Register <a href="INT\_STATUS\_1">INT\_STATUS\_1</a> are cleared automatically after 1/(3200Hz). If this automatic clearance is unwanted, latched-mode can be used (see chapter 4.7).

In order to enable/use the data ready interrupt map it on the desired interrupt pin via INT\_MAP\_DATA.

### **Temperature Sensor**

The temperature sensor has 8 bits. The temperature value is defined in Register <u>TEMPERATURE</u> and updated every 1.28 s.

It is always on, when a sensor is active.

| Value | Temperature |

|-------|-------------|

| 0x7F  | 150 °C      |

| •••   |             |

| 0x00  | 23 °C       |

| •••   |             |

| 0x81  | -104 °C     |

| 0x80  | Invalid     |

When there is no valid temperature information available (i.e. last measurement before the time defined above), the temperature indicates an invalid value: 0x80.

Page 22

#### **Sensor Time**

The BMA456 supports the concept of sensortime. Its core element is a free running counter with a width of 24 bits. It increments with a resolution of 39.0625us. The user can access the current state of the counter by reading registers <u>SENSORTIME 0</u> to <u>SENSORTIME 2</u>.

All sensor events e.g. updates of data registers are synchronous to this sensor time register as defined in the table below. With every update of the data register or the FIFO, a bit *m* in the registers <a href="SENSORTIME">SENSORTIME</a> 0 to <a href="SENSORTIME">SENSORTIME</a> 2 toggles where *m* depends on the output data rate for the data register and the output data rate and the FIFO downsampling rate for the FIFO. The table below shows which bit toggles for which update rate of data register and FIFO

| Bit m in sensor_time | 23     | 22     | 21    | 20    | 19    | 18    | 17   | 16   |

|----------------------|--------|--------|-------|-------|-------|-------|------|------|

| Resolution [s]       | 327.68 | 163.84 | 81.92 | 40.96 | 20.48 | 10.24 | 5.12 | 2.56 |

| Update rate [Hz]     | 0.0031 | 0.0061 | 0.012 | 0.024 | 0.049 | 0.10  | 0.20 | 0.39 |

| Bit <i>m</i> in sensor_time | 15   | 14   | 13    | 12   | 11   | 10 | 9  | 8   | 7   | 6   | 5     | 4     | 3      | 2     | 1     | 0     |

|-----------------------------|------|------|-------|------|------|----|----|-----|-----|-----|-------|-------|--------|-------|-------|-------|

| Resolution [ms]             | 1280 | 640  | 320   | 160  | 80   | 40 | 20 | 10  | 5   | 2.5 | 1.250 | 0.625 | 0.3125 | 0.156 | 0.078 | 0.039 |

| Update rate [Hz]            | 0.78 | 1.56 | 3.125 | 6.25 | 12.5 | 25 | 50 | 100 | 200 | 400 | 800   | 1600  | 3200   |       |       |       |

The sensortime is synchronized with the data capturing in the data register and the FIFO. Between the data sampling and the data capturing there is a delay which depends on the settings in the Register ACC CONF. The sensortime supports multiple seconds of sample counting and a sub-microsecond resolution, see Register SENSORTIME 0 for details.

Burst reads on the registers <u>SENSORTIME 0</u> to <u>SENSORTIME 2</u> deliver always consistent values, i.e. the value of the register does not change during the burst read.

### **Configuration Changes**

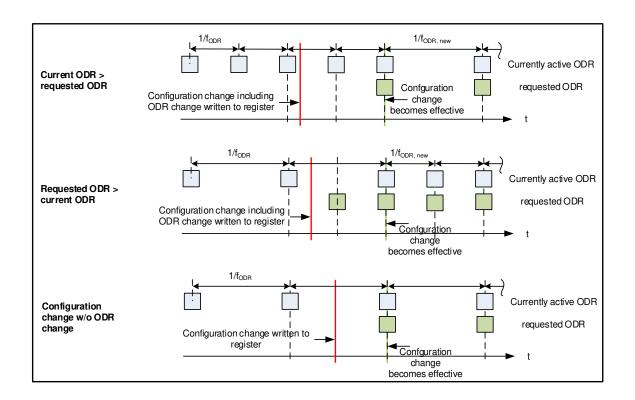

If accelerometer configuration settings in registers <u>ACC CONF</u>, <u>ACC RANGE</u>, or <u>AUX CONF</u> are changed while the accelerometer (<u>PWR CTRL.acc en</u> = 0b1) or auxiliary sensor (<u>PWR CTRL.aux en</u> = 0b1) is enabled, the configuration changes are not immediately applied. The configuration changes become effective if a sampling event for the currently active ODR coincides with a sampling event for the newly requested ODR on the sensortime sampling grid. In the case where the currently active ODR equals the newly requested ODR, the configuration changes become effective at the next sampling event. See also following figure.

Page 24

#### 4.5. FIFO

The device supports the following FIFO operating modes:

- Streaming mode: overwrites oldest data on FIFO full condition

- FIFO mode: discards newest data on FIFO full condition

The FIFO depth is 1024 byte and supports the following interrupts:

- FIFO full interrupt

- FIFO watermark interrupt

FIFO is enabled with <u>FIFO CONFIG 1.fifo acc en</u>=0b1 (0b0= disabled). To enable the FIFO for the auxiliary interface (magnetometer) set FIFO CONFIG 1.fifo aux en=0b1 (0b0=disabled).

#### **Frames**

The FIFO captures data in frames, which consist of a header and a payload. The FIFO can be configured to skip the header (headerless mode) in which case only payload is stored.

- In header mode (standard configuration) each regular frame consists of a one byte header describing properties of the frame, (which sensors are included in this frame) and the data itself. Beside the regular frames, there are control frames.

- In headerless mode the FIFO contains sampled data only.

#### Header mode

The header has a length of 8 bit and the following format:

| Bit     | 7       | 6     | 5        | 4    | 3 | 2 | 1         | 0  |

|---------|---------|-------|----------|------|---|---|-----------|----|

| Content | fh_mode | <1:0> | fh_parm< | 3:0> |   |   | fh_ext<1: | 0> |

These fh mode and fh parm and fh ext fields are defined below

| fh_mode<1:0>  | Definition | fh_parm <3:0>   | fh_ext<1:0>          |

|---------------|------------|-----------------|----------------------|

| 0b10          | Regular    | Enabled sensors | Tag of INT2 and INT1 |

| 0b01          | Control    | Control opcode  |                      |

| 0b00 and 0b11 | Reserved   | Na              |                      |

f\_parm=0b0000 is invalid for regular mode, a header of 0x80 indicates an uninitialized frame.

In a regular frame, fh\_parm frame defines which sensors are included in the data part of the frame. The format is

| Name    | fh_parm<3:0> |               |          |               |

|---------|--------------|---------------|----------|---------------|

| Bit     | 3            | 2             | 1        | 0             |

| Content | Reserved     | FIFO_aux_data | Reserved | FIFO_acc_data |

BST-BMA456-DS000-01 | Version 1.1 | October 2017

<sup>©</sup> Bosch Sensortec GmbH reserves all rights even in the event of industrial property rights. We reserve all rights of disposal such as copying and passing on to third parties. BOSCH and the symbol are registered trademarks of Robert Bosch GmbH, Germany.

Note: Specifications within this document are subject to change without notice.

Page 25

When FIFO\_<sensor x>\_data is 0b1 (0b0) data for sensor x is included (not included) in the data part of the frame.

The fh\_ext<1:0> field are used for external tagging.

The data format for data frames is identical to the format defined for the <u>Register (0x0A) DATA 0</u> to <u>Register (0x17) DATA 13</u> register. Only frames which contain data of at least one sensor will be written into the FIFO. E.g. fh\_parm=0b0101 the data in the frame are shown below. If the read burst length is less than 8 byte, the number of auxiliary sensor data in the frame is reduced to the burst length.

| DATA[X] | Acronym           |                                                                                        |

|---------|-------------------|----------------------------------------------------------------------------------------|

| X=0     | AUX_0             | copy of register $Val(\underline{AUX\ RD\ ADDR})$ in auxiliary sensor register map     |

| X=1     | AUX_1             | copy of register $Val(AUX RD ADDR)+1$ in auxiliary sensor register map                 |

| X=2     | AUX_2             | copy of register $Val(\underline{AUX\ RD\ ADDR}\ )+2$ in auxiliary sensor register map |

| X=3     | AUX_3             | copy of register $Val(AUX RD ADDR) + 3$ in auxiliary sensor register map               |

| X=4     | AUX_4             | copy of register $Val(\underline{AUX\ RD\ ADDR}\ )+4$ in auxiliary sensor register map |

| X=5     | AUX_5             | copy of register Val( <u>AUX_RD_ADDR</u> )+5 in auxiliary sensor register map          |

| X=6     | AUX_6             | copy of register $Val(\underline{AUX\_RD\_ADDR})+6$ in auxiliary sensor register map   |

| X=7     | AUX_7             | copy of register Val( <u>AUX_RD_ADDR</u> )+7 in auxiliary sensor register map          |

| X=8     | ACC_X<7:0> (LSB)  |                                                                                        |

| X=9     | ACC_X<15:8> (MSB) |                                                                                        |

| X=10    | ACC_Y<7:0> (LSB)  |                                                                                        |

| X=11    | ACC_Y<15:8> (MSB) |                                                                                        |

| X=12    | ACC_Z<7:0> (LSB)  |                                                                                        |

| X=13    | ACC_Z<15:8> (MSB) |                                                                                        |

#### Headerless mode

When the data rates of all enabled sensor elements are identical, the FIFO header may be disabled in FIFO CONFIG 1.fifo header en.

The headerless mode supports only regular frames. To be able to distinguish frames from each other, all frames must have the same size. For this reason, any change in configuration that have an impact to frame size or order of data within a frame will cause an instant flush of FIFO, restarting capturing of data with the new settings.