Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## Serial EEPROM Series Standard EEPROM Microwire BUS EEPROM(3-Wire)

# **BR93Lxx-W**

#### General Description

BR93Lxx-W is serial EEPROM of serial 3-line interface method

#### Features

- 3-line communications of chip select, serial clock, serial data input / output (the case where input and output are shared)

- Actions available at high speed 2MHz clock(2.5V to 5.5V)

- Speed write available (write time 5ms max.)

- Same package and pin layout from 1Kbit to 16Kbit

- 1.8V to 5.5V single power source action

- Address auto increment function at read action

- Write mistake prevention function

- Write prohibition at power on

- Write prohibition by command code

- Write mistake prevention function at low voltage

- Program cycle auto delete and auto end function

- Program condition display by READY / BUSY

- Low current consumption

- At write action (at 5V): 1.2mA (Typ.)

- At read action (at 5V): 0.3mA (Typ.)

- At standby action (at 5V): 0.1µA (Typ.)(CMOS input)

- TTL compatible( input / outputs)

- Data retention for 40 years

- Endurance up to 1,000,000 times

- Data at shipment all addresses FFFFh

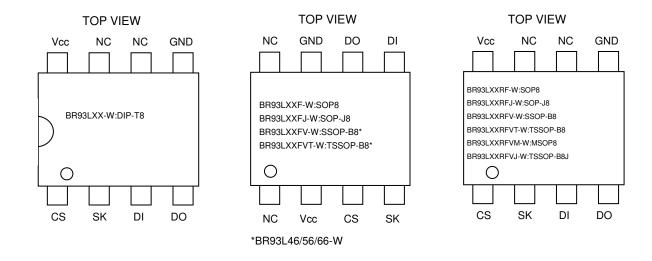

#### ●Packages W(Typ.) x D(Typ.) x H(Max.)

SOP8

5.00mm x 6.20mm x 1.71mm

TSSOP-B8

3.00mm x 6.40mm x 1.20mm

4.90mm x 6.00mm x 1.65mm

TSSOP-B8J 3.00mm x 4.90mm x 1.10mm

SSOP-B8 3.00mm x 6.40mm x 1.35mm

MSOP8 2.90mm x 4.00mm x 0.90mm

9.30mm x 6.50mm x 7.10mm

Figure.1 RROSI vv\_W

| <b>DUBOLXX</b> | DD35LXX-W  |           |                      |    |     |     |      |     |      |     |       |       |               |        |

|----------------|------------|-----------|----------------------|----|-----|-----|------|-----|------|-----|-------|-------|---------------|--------|

| Package type   |            |           |                      | SC | )P8 | SOI | P-J8 | SSO | P-B8 | TSS | OP-B8 | MSOP8 | TSSOP-<br>B8J | DIP-T8 |

| Capacity       | Bit format | Туре      | Power source voltage | F  | RF  | FJ  | RFJ  | FV  | RFV  | FVT | RFVT  | RFVM  | RFVJ          | ı      |

| 1Kbit          | 64×16      | BR93L46-W | 1.8V to 5.5V         | •  | •   | •   | •    | •   | •    | •   | •     | •     | •             | •      |

| 2Kbit          | 128×16     | BR93L56-W | 1.8V to 5.5V         | •  | •   | •   | •    | •   | •    | •   | •     | •     | •             | •      |

| 4Kbit          | 256×16     | BR93L66-W | 1.8V to 5.5V         | •  | •   | •   | •    | •   | •    | •   | •     | •     | •             | •      |

| 8Kbit          | 512×16     | BR93L76-W | 1.8V to 5.5V         | •  | •   | •   | •    |     | •    |     | •     | •     | •             | •      |

| 16Kbit         | 1K×16      | BR93L86-W | 1.8V to 5.5V         | •  | •   | •   | •    |     | •    |     | •     | •     | •             | •      |

● Absolute Maximum Ratings (Ta=25°C)

| Parameter                 | Symbol | Limits          | Unit | Remarks                                                        |

|---------------------------|--------|-----------------|------|----------------------------------------------------------------|

| Impressed voltage         | Vcc    | -0.3 to +6.5    | ٧    |                                                                |

|                           |        | 450 (SOP8)      |      | When using at Ta=25°C or higher, 4.5mW, to be reduced per 1°C. |

|                           |        | 450 (SOP-J8)    |      | When using at Ta=25°C or higher, 4.5mW, to be reduced per 1°C. |

|                           |        | 300 (SSOP-B8)   |      | When using at Ta=25°C or higher, 3.0mW, to be reduced per 1°C. |

| Permissible dissipation   | Pd     | 330 (TSSOP-B8)  | mW   | When using at Ta=25°C or higher, 3.3mW, to be reduced per 1°C. |

|                           |        | 310 (MSOP8)     |      | When using at Ta=25°C or higher, 3.1mW, to be reduced per 1°C. |

|                           |        | 310 (TSSOP-B8J) |      | When using at Ta=25°C or higher, 3.1mW, to be reduced per 1°C. |

|                           |        | 800(DIP-T8)     |      | When using at Ta=25°C or higher, 8.0mW, to be reduced per 1°C  |

| Storage temperature range | Tstg   | -65 to +125     | °C   |                                                                |

| Action temperature range  | Topr   | -40 to +85      | °C   |                                                                |

| Terminal voltage          | -      | -0.3 to Vcc+0.3 | V    |                                                                |

## ● Memory Cell Characteristics(Vcc=1.8V to 5.5V)

| Darameter         |           | Limit | Unit | Condition |           |

|-------------------|-----------|-------|------|-----------|-----------|

| Parameter         | Min.      | Тур.  | Max. | Unit      | Condition |

| Endurance *1      | 1,000,000 | -     | -    | Times     | Ta=25°C   |

| Data retention *1 | 40        | -     | -    | Years     | Ta=25°C   |

OShipment data all address FFFFh

\*1 : Not 100% TESTED

Recommended Operating Ratings

| Parameter            | Symbol | Limits     | Unit |

|----------------------|--------|------------|------|

| Power source voltage | Vcc    | 1.8 to 5.5 | V    |

| Input voltage        | VIN    | 0 to Vcc   | V    |

## Electrical Characteristics

(Unless otherwise specified, VCC=2.5V to 5.5V, Ta=-40 $^{\circ}$ C to +85 $^{\circ}$ C)

| Davamatav                     | Currele el | Limits    |                |           | 1.1  | Condition                       |  |

|-------------------------------|------------|-----------|----------------|-----------|------|---------------------------------|--|

| Parameter                     | Symbol     | Min.      | Min. Typ. Max. |           | Unit | Condition                       |  |

| "L" input voltage 1           | VIL1       | -0.3      | -              | 0.8       | V    | 4.0V≦Vcc≦5.5V                   |  |

| "L" input voltage 2           | VIL2       | -0.3      | -              | 0.2 x Vcc | V    | Vcc≦4.0V                        |  |

| "H" input voltage 1           | VIH1       | 2.0       | -              | Vcc +0.3  | V    | 4.0V≦Vcc≦5.5V                   |  |

| "H" input voltage 2           | VIH2       | 0.7 x Vcc | -              | Vcc +0.3  | V    | Vcc≦4.0V                        |  |

| "L" output voltage 1          | VOL1       | 0         | -              | 0.4       | V    | IoL=2.1mA, 4.0V≦Vcc≦5.5V        |  |

| "L" output voltage 2          | VOL2       | 0         | -              | 0.2       | V    | IoL=100µA                       |  |

| "H" output voltage 1          | VoH1       | 2.4       | -              | Vcc       | V    | IOH=-0.4mA, 4.0V≦VCC≦5.5V       |  |

| "H" output voltage 2          | VOH2       | Vcc -0.2  | -              | Vcc       | V    | ΙΟΗ=-100μA                      |  |

| Input leak current            | lu         | -1        | -              | 1         | μΑ   | VIN=0V to VCC                   |  |

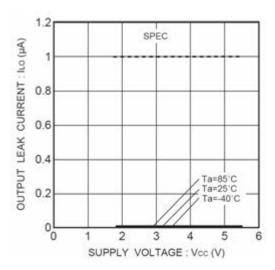

| Output leak current           | ILO        | -1        | -              | 1         | μΑ   | VOUT=0V to VCC, CS=0V           |  |

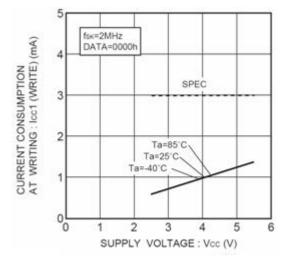

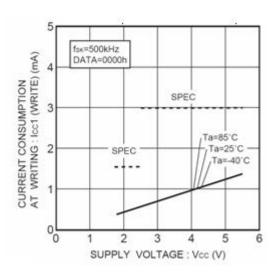

| 0                             | ICC1       | -         | -              | 3.0       | mA   | fsk=2MHz, te/w=5ms (WRITE)      |  |

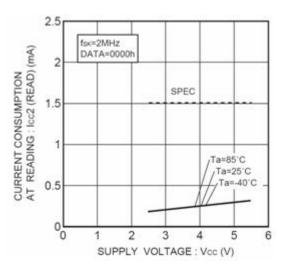

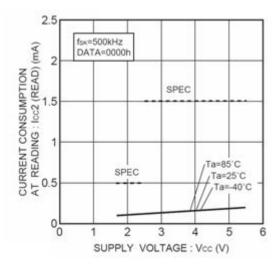

| Current consumption at action | ICC2       | -         | -              | 1.5       | mA   | fsk=2MHz (READ)                 |  |

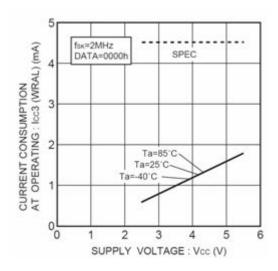

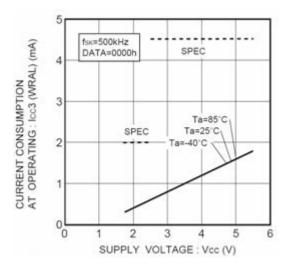

|                               | Icc3       | -         | -              | 4.5       | mA   | fsk=2MHz, te/w=5ms (WRAL, ERAL) |  |

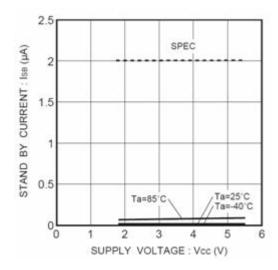

| Standby current               | Isb        | -         | -              | 2         | μΑ   | CS=0V, DO=OPEN                  |  |

(Unless otherwise specified, Vcc =1.8V to 2.5V, Ta=-40°C to +85°C)

| Davamatav                     | Cumahaal |           | Limits         |           | Unit | O a sa aliki a sa                 |  |

|-------------------------------|----------|-----------|----------------|-----------|------|-----------------------------------|--|

| Parameter                     | Symbol   | Min.      | Тур.           | Гур. Мах. |      | Condition                         |  |

| "L" input voltage             | VIL      | -0.3      | -              | 0.2 x Vcc | V    |                                   |  |

| "H" input voltage             | VIH      | 0.7 x Vcc | -              | Vcc+0.3   | V    |                                   |  |

| "L" output voltage            | Vol      | 0         | -              | 0.2       | V    | IoL=100µA                         |  |

| "H" output voltage            | Vон      | Vcc-0.2   | -              | Vcc       | V    | Іон=-100μΑ                        |  |

| Input leak current            | ILI      | -1        | -              | 1         | μΑ   | VIN=0V to VCC                     |  |

| Output leak current           | ILO      | -1        | -              | 1         | μA   | Vout=0V to Vcc, CS=0V             |  |

| 0                             | ICC1     | -         | -              | 1.5       | mA   | fsk=500kHz, tE/w=5ms (WRITE)      |  |

| Current consumption at action | ICC2     | -         | -              | 0.5       | mA   | fsk=500kHz (READ)                 |  |

|                               | Icc3     | -         | -              | 2         | mA   | fsk=500kHz, tE/W=5ms (WRAL, ERAL) |  |

| Standby current ISB 2         |          | μA        | CS=0V, DO=OPEN |           |      |                                   |  |

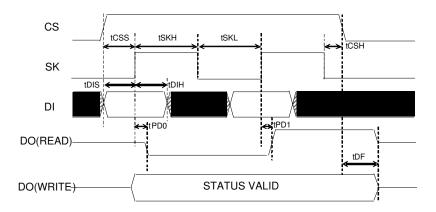

## Action Timing Characteristics

$(Ta=-40^{\circ}C \text{ to } +85^{\circ}C, Vcc=2.5V \text{ to } 5.5V)$

| Parameter                            | Cymbal           | 2.5  | Unit |      |       |

|--------------------------------------|------------------|------|------|------|-------|

| Parameter                            | Symbol           | Min. | Тур. | Max. | Uffil |

| SK frequency                         | f <sub>SK</sub>  | -    | -    | 2    | MHz   |

| SK "H" time                          | t <sub>skh</sub> | 230  | -    | -    | ns    |

| SK "L" time                          | t <sub>SKL</sub> | 230  | -    | -    | ns    |

| CS "L" time                          | t <sub>CS</sub>  | 200  | -    | -    | ns    |

| CS setup time                        | t <sub>CSS</sub> | 50   | -    | -    | ns    |

| DI setup time                        | t <sub>DIS</sub> | 100  | -    | -    | ns    |

| CS hold time                         | t <sub>CSH</sub> | 0    | -    | -    | ns    |

| DI hold time                         | t <sub>DIH</sub> | 100  | -    | -    | ns    |

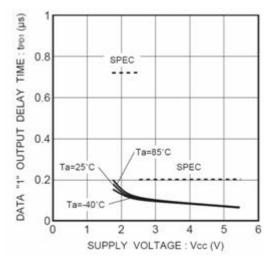

| Data "1" output delay time           | t <sub>PD1</sub> | -    | -    | 200  | ns    |

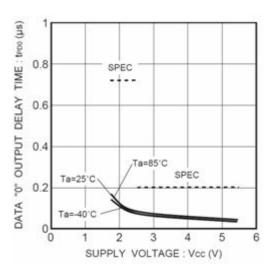

| Data "0" output delay time           | t <sub>PD0</sub> | -    | -    | 200  | ns    |

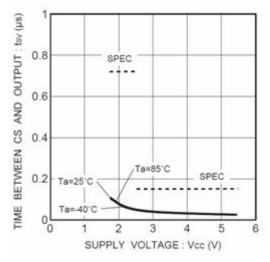

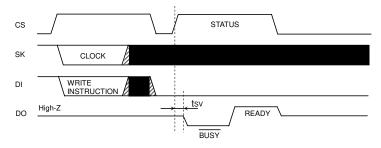

| Time from CS to output establishment | t <sub>sv</sub>  | -    | -    | 150  | ns    |

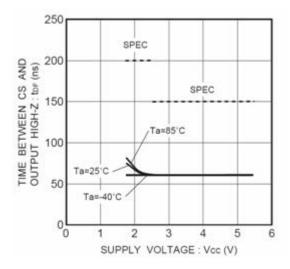

| Time from CS to High-Z               | t <sub>DF</sub>  | -    | -    | 150  | ns    |

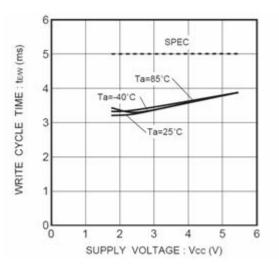

| Write cycle time                     | t <sub>E/W</sub> | -    | -    | 5    | ms    |

$(Ta=-40^{\circ}C \text{ to } +85^{\circ}C, VCC=1.8V \text{ to } 2.5V)$

| Dorometer                            | Cymbal           | 1.8  | Unit |      |       |

|--------------------------------------|------------------|------|------|------|-------|

| Parameter                            | Symbol           | Min. | Тур. | Max. | Ullit |

| SK frequency                         | f <sub>SK</sub>  | -    | -    | 500  | kHz   |

| SK "H" time                          | t <sub>SKH</sub> | 0.8  | -    | -    | us    |

| SK "L" time                          | t <sub>SKL</sub> | 0.8  | -    | -    | us    |

| CS "L" time                          | t <sub>CS</sub>  | 1    | -    | -    | us    |

| CS setup time                        | t <sub>CSS</sub> | 200  | -    | -    | ns    |

| DI setup time                        | t <sub>DIS</sub> | 100  | -    | -    | ns    |

| CS hold time                         | t <sub>CSH</sub> | 0    | -    | -    | ns    |

| DI hold time                         | t <sub>DIH</sub> | 100  | -    | -    | ns    |

| Data "1" output delay time           | t <sub>PD1</sub> | -    | -    | 0.7  | us    |

| Data "0" output delay time           | t <sub>PD0</sub> | -    | -    | 0.7  | us    |

| Time from CS to output establishment | t <sub>SV</sub>  | -    | -    | 0.7  | us    |

| Time from CS to High-Z               | t <sub>DF</sub>  | -    | -    | 200  | ns    |

| Write cycle time                     | t <sub>E/W</sub> | -    | -    | 5    | ms    |

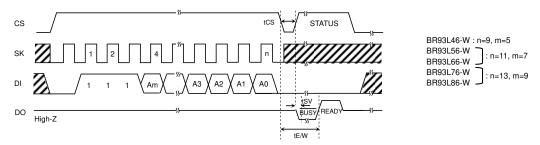

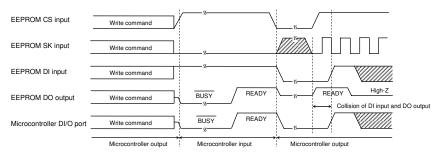

## ●Sync Data Input / Output Timing

OData is taken by DI sync with the rise of SK.

OAt read action, data is output from DO in sync with the rise of SK.

OThe status signal at write (READY / BUSY) is output after tCS from the fall of CS after write command input, at the area DO where CS is "H", and valid until the next command start bit is input. And, while CS is "L", DO becomes High-Z.

OAfter completion of each mode execution, set CS "L" once for internal circuit reset, and execute the following action mode.

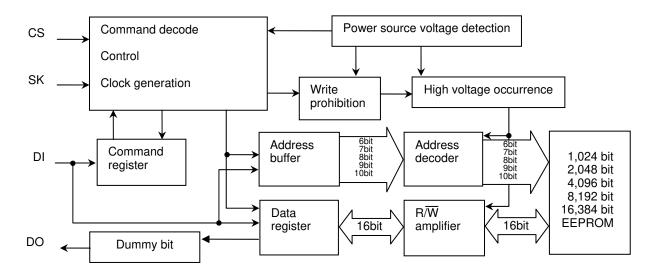

## ● Block Diagram

### Pin Configurations

## Pin Descriptions

| Pin name | 1/0    | Function                                                           |

|----------|--------|--------------------------------------------------------------------|

| Vcc      | -      | Power source                                                       |

| GND      | -      | All input / output reference voltage, 0V                           |

| CS       | Input  | Chip select input                                                  |

| SK       | Input  | Serial clock input                                                 |

| DI       | Input  | Start bit, ope code, address, and serial data input                |

| DO       | Output | Serial data output, READY / BUSY internal condition display output |

| NC       | -      | Non connected terminal, Vcc, GND or OPEN                           |

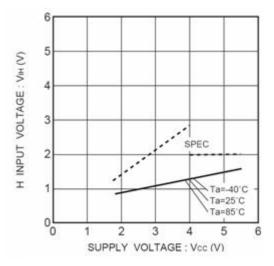

### **●**Typical Performance Curves

(The following characteristic data are typ. values.)

Figure 2. H input voltage VIH (CS,SK,DI)

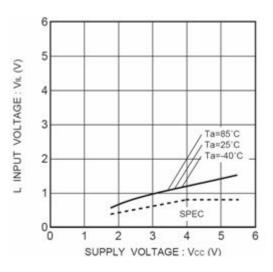

Figure 3. L input voltage VIL (CS,SK,DI)

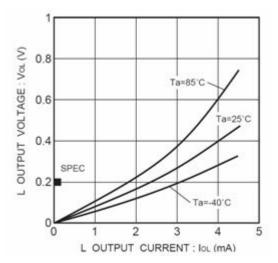

Figure 4. L output voltage VOL-IOL (Vcc=1.8V)

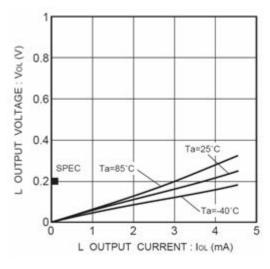

Figure 5. L output voltage VOL-IOL (Vcc=2.5V)

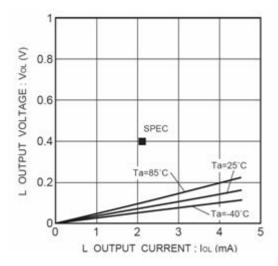

Figure 6. L output voltage VOL-IOL (Vcc=4.0V)

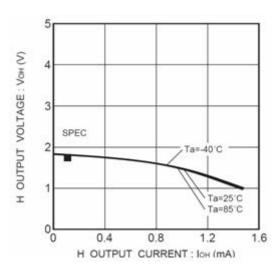

Figure 7. H output voltage VOH-IOH (Vcc=1.8V)

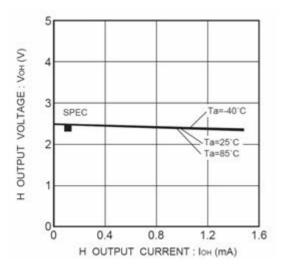

Figure 8. H output voltage VOH-IOH (Vcc=2.5V)

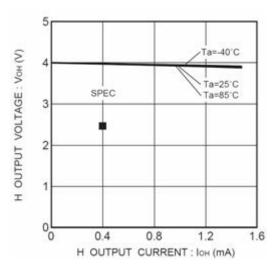

Figure 9. H output voltage VOH-IOH (Vcc=4.0V)

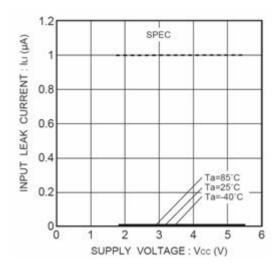

Figure 10. Input leak current ILI (CS,SK,DI)

Figure 11. Output leak current ILO (DO)

Figure 12. Current consumption at WRITE action ICC1 (WRITE, fSK=2MHz)

Figure 13. Consumption current at READ action ICC2 (READ, fSK=2MHz)

Figure 14. Consumption current at WRAL action ICC3 (WRAL, fSK=2MHz)

Figure 15. Current consumption at WRITE action ICC1 (WRITE, fSK=500kHz)

Figure 16. Consumption current at READ action ICC2 (READ, fSK=500kHz)

Figure 17. Consumption current at WRAL action ICC3 (WRAL, fSK=500kHz)

Figure 18. Consumption current at standby action ISB

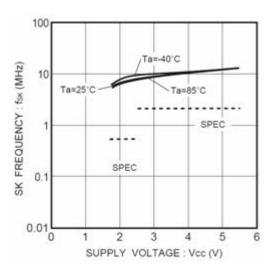

Figure 19. SK frequency fSK

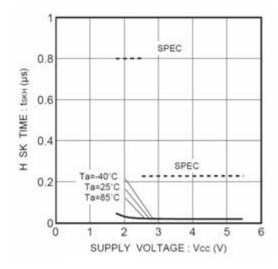

Figure 20. SK high time tSKH

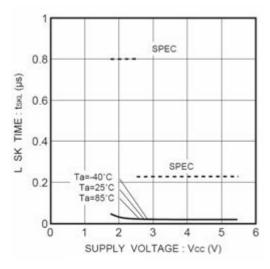

Figure 21. SK low time tSKL

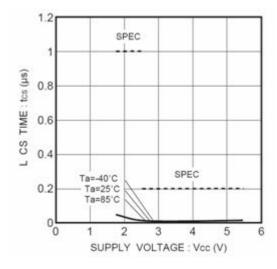

Figure 22. CS low time tCS

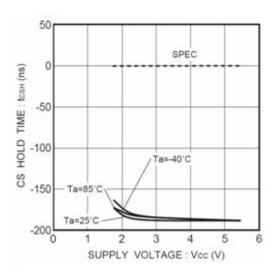

Figure 23. CS hold time tCSH

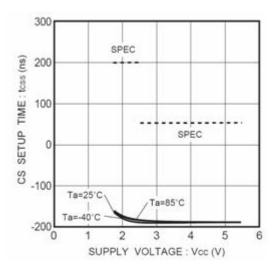

Figure 24. CS setup time tCSS

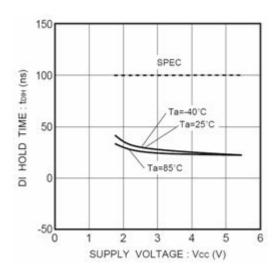

Figure 25. DI hold time tDIH

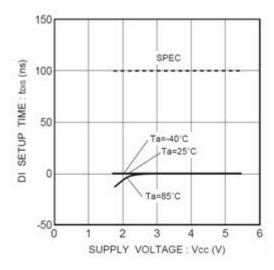

Figure 26. DI setup time tDIS

Figure 27. Data "0" output delay time tPD0

Figure 28. Output data "1" delay time tPD1

Figure 29. Time from CS to output establishment tSV

Figure 30. Time from CS to High-Z tDF

Figure 31. Write cycle time tE/W

#### Description of Operations

Communications of the Microwire Bus are carried out by SK (serial clock), DI (serial data input),DO (serial data output), and CS (chip select) for device selection.

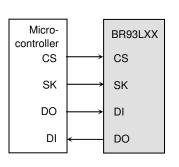

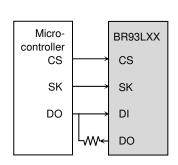

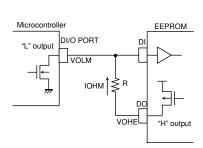

When to connect one EEPROM to a microcontroller, connect it as shown in Figure 32 (a) or Figure 32 (b). When to use the input and output common I/O port of the microcontroller, connect DI and DO via a resistor as shown in Figure 31 (b) (Refer to page 19.), and connection by 3 lines is available.

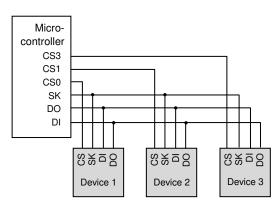

In the case of plural connections, refer to Figure 32 (c).

Figure 32-(a) Connection by 4 lines

Figure 32-(b) Connection by 3 lines

Figure 32-(c) Connection example of plural devices

Figure 32. Connection method with microcontroller

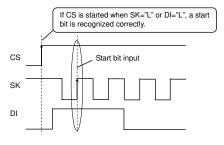

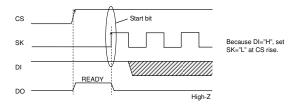

Communications of the Microwire Bus are started by the first "1" input after the rise of CS. This input is called a start bit. After input of the start bit, input ope code, address and data. Address and data are input all in MSB first manners. "0" input after the rise of CS to the start bit input is all ignored. Therefore, when there is limitation in the bit width of PIO of the microcontroller, input "0" before the start bit input, to control the bit width.

#### Command Mode

| 0                   | Start | Ope  |                   | Data                    |                               |                       |

|---------------------|-------|------|-------------------|-------------------------|-------------------------------|-----------------------|

| Command             | bit   | code | BR93L46-W         | BR93L56/66-W            | BR93L76/86-W                  | Data                  |

| Read (READ)         | 1     | 10   | A5,A4,A3,A2,A1,A0 | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15 to D0(READ DATA)  |

| Write enable (WEN)  | 1     | 00   | 1 1 ****          | 1 1 *****               | 1 1 ******                    |                       |

| Write (WRITE)       | 1     | 01   | A5,A4,A3,A2,A1,A0 | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 | D15 to D0(WRITE DATA) |

| Write all (WRAL)    | 1     | 00   | 0 1 ****          | 0 1 *****               | 0 1 ******                    | D15 to D0(WRITE DATA) |

| Write disable (WDS) | 1     | 00   | 0 0 ****          | 0 0 *****               | 0 0 ******                    |                       |

| Erase (ERASE)       | 1     | 11   | A5,A4,A3,A2,A1,A0 | A7,A6,A5,A4,A3,A2,A1,A0 | A9,A8,A7,A6,A5,A4,A3,A2,A1,A0 |                       |

| Chip erase (ERAL)   | 1     | 00   | 1 0 ****          | 1 0 *****               | 1 0 ******                    |                       |

Input the address and the data in MSB first manners.

A7 of BR93L56-W becomes Don't Care. A9 of BR93L76-W becomes Don't Care.

Acceptance of all the commands of this IC starts at recognition of the start bit.

The start bit means the first "1" input after the rise of CS.

As for \*, input either VIH or VIL.

<sup>\*</sup>Start bit

<sup>\*1</sup> As for read, by continuous SK clock input after setting the read command, data output of the set address starts, and address data in significant order are sequentially output continuously. (Auto increment function)

<sup>\*2</sup> When the read and the write all commands are executed, data written in the selected memory cell is automatically deleted, and input data is written.

#### Timing Chart

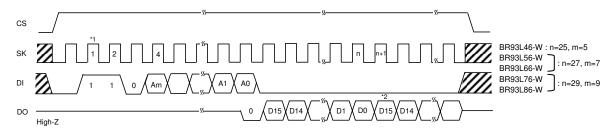

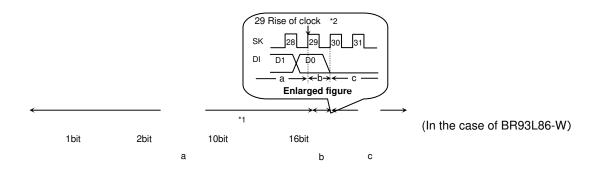

#### 1) Read cycle (READ)

<sup>\*1</sup> Start bit

When data "1" is input for the first time after the rise of CS, this is recognized as a start bit. And when "1" is input after plural "0" are input, it is recognized as a start bit, and the following operation is started. This is common to all the commands to described hereafter.

Figure 33. Read cycle

OWhen the read command is recognized, input address data (16bit) is output to serial. And at that moment, at taking A0, in sync with the rise of SK, "0" (dummy bit) is output. And, the following data is output in sync with the rise of SK. This IC has an address auto increment function valid only at read command. This is the function where after the above read execution, by continuously inputting SK clock, the above address data is read sequentially. And, during the auto increment, keep CS at "H".

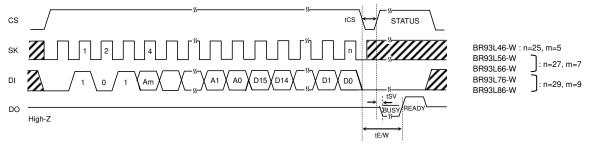

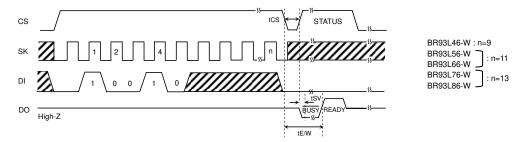

#### 2) Write cycle (WRITE)

Figure 34. Write cycle

OIn this command, input 16bit data (D15 to D0) are written to designated addresses (Am to A0). The actual write starts by the fall of CS of D0 taken SK clock.

When STATUS is not detected, (CS="L" fixed) Max. 5ms in conformity with tE/W, and when STATUS is detected (CS="H"), all commands are not accepted for areas where "L" (BUSY) is output from D0, therefore, do not input any command.

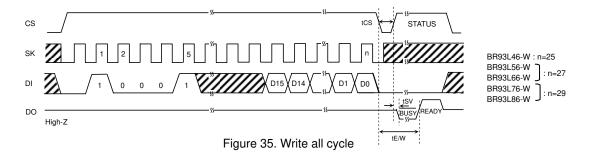

#### 3) Write all cycyle (WRAL)

OIn this command, input 16bit data is written simultaneously to all adresses. Data is not written continuously per one word but is written in bulk, the write time is only Max. 5ms in conformity with tE/W.

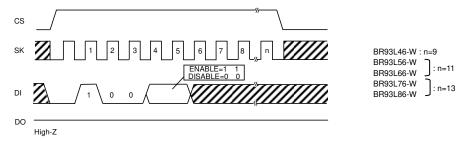

4) Write enable (WEN) / disable (WDS) cycle

Figure 36. Write enable (WEN) / disable (WDS) cycle

- O At power on, this IC is in write disable status by the internal RESET circuit. Before executing the write command, it is necessary to execute the write enable command. And, once this command is executed, it is valid unit the write disable command is executed or the power is turned off. However, the read command is valid irrespective of write enable / diable command. Input to SK after 6 clocks of this command is available by either "H" or "L", but be sure to input it.

- O When the write enable command is executed after power on, write enable status gets in. When the write disable command is executed then, the IC gets in write disable status as same as at power on, and then the write command is canceled thereafter in software manner. However, the read command is executable. In write enable status, even when the write command is input by mistake, write is started. To prevent such a mistake, it is recommended to execute the write disable command after completion of write.

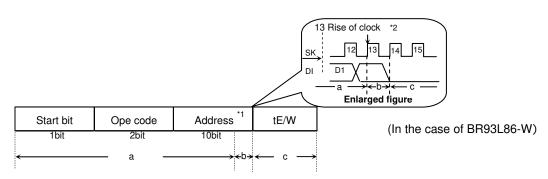

- 5) Erase cycle timing (ERASE)

Figure 37. Erase cycle timing

OIn this command, data of the designated address is made into "1". The data of the designated address becomes "FFFFh". Actual ERASE starts at the fall of CS after the fall of A0 taken SK clock. In ERASE, status can be detected in the same manner as in WRITE command.

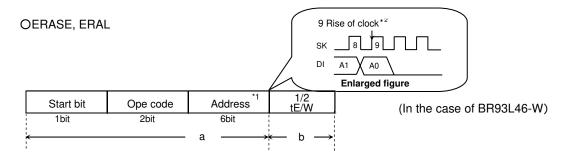

6) Chip erase cycle timing (ERAL)

Figure 38. Chip erase cycle timing

OIn this command, data of all addresses is erased. Data of all addresses becomes "FFFFh". Actual ERASE starts at the fall of CS after the fall of the n-th clock from the start bit input. In ERAL, status can be detected in the same manner as in WRITE command.

#### Application

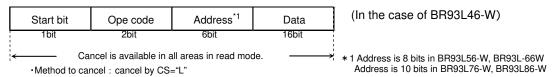

1) Method to cancel each command

#### **OREAD**

Figure 39. READ cancel available timing

- a : From start bit to 25 clock rise\*2 Cancel by CS="L"

- b : 25 clock rise and after\*<sup>2</sup> Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again. And when SK clock is input continuously, cancellation is not available.

- \*1 Address is 8 bits in BR93L56-W, BR93L66-W Address is 10 bits in BR93L76-W BR93L86-W

- \*2 27 clocks in BR93L56-W, BR93L66-W 29 clocks in BR93L76-W BR93L86-W

- a : From start bit to 29 clock rise Cancel by CS="L"

- b : 29 clock rise and after Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

- Cancel by CS="L"

However, when write is started in b area (CS is ended), cancellation is not available by any means.

And when SK clock is output continuously is not available.

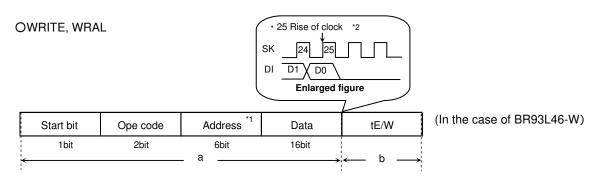

- Figure 40. WRITE, WRAL cancel available timing

- Note 1) If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

- Note 2) If CS is started at the same timing as that of the SK rise, write execution/cancel becomes unstable, therefore, it is recommended to fail in SK="L" area.

As for SK rise, recommend timing of tCSS/tCSH or higher.

- a : From start bit to 9 clock rise\*2

Cancel by CS="L"

- $b:9\ \text{clock}$  rise and after\*  $^{*2}$

Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again. And when SK clock is input continuously, cancellation is not available.

- \* 1 Address is 8 bits in BR93L56-W, BR93L66-W Address is 10 bits in BR93L76-W

- \* 2 11 clocks in BR93L56-W, BR93L66-W 13 clocks in BR93L76-W

- a : From start bit to 13 clock rise Cancel by CS="L"

- b : 13 clock rise and after Cancellation is not available by any means. If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

- c: 14 clock rise and after

Cancel by CS="L"

However, when write is started in b area (CS is ended), cancellation is not

available by any means.

And when SK clock is output continuously is not available.

- Note 1) If Vcc is made OFF in this area, designated address data is not guaranteed, therefore write once again.

- Note 2) If CS is started at the same timing as that of the SK rise, write execution/cancel becomes unstable, therefore, it is recommended to fail in SK="L" area.

As for SK rise, recommend timing of tCSS/tCSH or higher.

Figure 41. ERASE, ERAL cancel available timing

## 2) At standby

#### OStandby current

When CS is "L", SK input is "L", DI input is "H", and even with middle electric potential, current does not increase.

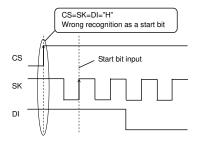

## **OTiming**

As shown in Figure 42, when SK at standby is "H", if CS is started, DI status may be read at the rise edge. At standby and at power ON/OFF, when to start CS, set SK input or DI input to "L" status. (Refer to Figure 42)

Figure 42. Wrong action timing

Figure 43. Normal action timing

#### 3) Equivalent circuit

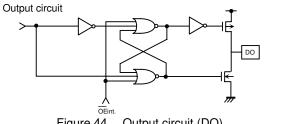

Figure 44. Output circuit (DO)

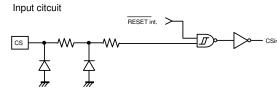

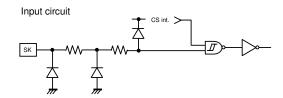

Figure 45. Input circuit (CS)

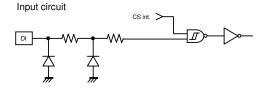

Figure 46. Input circuit (DI)

Figure 47. Input circuit (SK)

### 4) I/O peripheral circuit

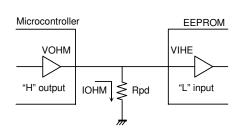

## 4-1) Pull down CS.

By making CS="L" at power ON/OFF, mistake in operation and mistake write are prevented.

#### OPull down resistance Rpd of CS pin

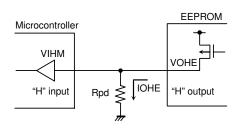

To prevent mistake in operation and mistake write at power ON/OFF, CS pull down resistance is necessary. Select an appropriate value to this resistance value from microcontroller VOH, IOH, and VIL characteristics of this IC.

Figure 48. CS pull down resistance

$$\mathsf{Rpd} \, \geqq \, \frac{\mathsf{VOHM}}{\mathsf{IOHM}} \quad \cdots \quad \textcircled{1}$$

$$\mathsf{VOHM} \, \geqq \, \mathsf{VIHE} \qquad \cdots \quad \textcircled{2}$$

Example) When V<sub>CC</sub> =5V, VIHE=2V, VOHM=2.4V, IOHM=2mA, from the equation ①,

$$\mathsf{Rpd} \; \geqq \; \frac{2.4}{2 \times 10^3}$$

$$\therefore \; \; \mathsf{Rpd} \; \geqq \; \; 1.2 \, [\mathsf{k}\,\Omega]$$

With the value of Rpd to satisfy the above equation, VOHM becomes 2.4V or higher, and VIHE (=2.0V), the equation ② is also satisfied.

: EEPROM VIH specifications VIHE VOHM : Microcontroller VOH specifications · IOHM : Microcontroller IOH specifications

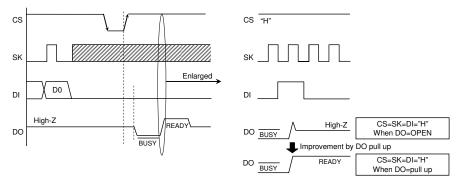

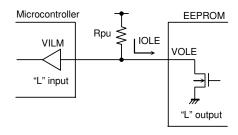

## 4-2) DO is available in both pull up and pull down.

Do output become "High-Z" in other READY /  $\overline{\text{BUSY}}$  output timing than after data output at read command and write command. When malfunction occurs at "High-Z" input of the microcontroller port connected to DO, it is necessary to pull down and pull up DO. When there is no influence upon the microcontroller actions, DO may be OPEN. If DO is OPEN, and at timing to output status READY, at timing of CS="H", SK="H", DI="H", EEPROM recognizes this as a start bit, resets READY output, and DO="High-Z", therefore, READY signal cannot be detected. To avoid such output, pull up DO pin for improvement.

Figure 49. READY output timing at DO=OPEN

OPull up resistance Rpu and pull down resistance Rpd of DO pin

As for pull up and pull down resistance value, select an appropriate value to this resistance value from microcontroller VIH, VIL, and VOH, IOH, VOL, IOL characteristics of this IC.

Figure 50. DO pull up resistance

Figure 51. DO pull down resistance

Example) When  $V_{CC}$  =5V, VOLE=0.4V, IOLE=2.1mA, VILM=0.8V, from the equation  $\Im$ ,

Rpu

$$\geq \frac{5-0.4}{2.1 \times 10^{-3}}$$

$$\therefore$$

Rpu  $\geq$  2.2 [k  $\Omega$ ]

With the value of Rpu to satisfy the above equation, VOLE becomes 0.4V or below, and with VILM(=0.8V), the equation ④ is also satisfied.

VOLE : EEPROM VOL specifications

IOLE : EEPROM IOL specifications

VILM : Microcontroller VIL specifications

$$\mathsf{Rpd} \; \geqq \; \frac{\mathsf{VOHE}}{\mathsf{IOHE}} \quad \cdots \quad (5)$$

Rpd

$$\geq \frac{5-0.2}{0.1 \times 10^{-3}}$$

$$\therefore$$

Rpd  $\geq$  48 [k $\Omega$ ]

With the value of Rpd to satisfy the above equation, VOHE becomes 2.4V or below, and with VIHM (=3.5V), the equation 6 is also satisfied.

VOHE : EEPROM VOH specifications

IOHE : EEPROM IOH specifications

VIHM : Microcontroller VIH specifications

5) READY / BUSY status display (DO terminal)

(common to BR93L46-W, BR93L56-W, BR93L66-W, BR93L76-W, BR93L86-W)

This display outputs the internal status signal. When CS is started after tCS (Min.200ns) from CS fall after write command input, "H" or "L" is output.

$R/\overline{B}$  display="L" ( $\overline{BUSY}$ ) = write under execution

(DO status) After the timer circuit in the IC works and creates the period of tE/W, this time circuit completes automatically.

And write to the memory cell is made in the period of tE/W, and during this period, other command is not accepted.

R/B display = "H" (READY) = command wait status

(DO status) Even after tE/W (max.5ms) from write of the memory cell, the following command is accepted.

Therefore, CS="H" in the period of tE/W, and when input is in SK, DI, malfunction may occur, therefore, DI="L" in the area CS="H". (Especially, in the case of shared input port, attention is required.)

\*Do not input any command while status signal is output. Command input in BUSY area is cancelled, but command input in READY area is accepted. Therefore, status READY output is cancelled, and malfunction and mistake write may be made.

Figure 52. R/B status output timing chart

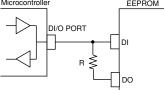

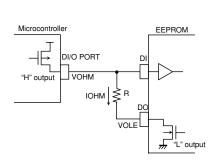

6) When to directly connect DI and DO

This IC has independent input terminal DI and output terminal DO, and separate signals are handled on timing chart, meanwhile, by inserting a resistance R between these DI and DO terminals, it is possible to carry out control by 1 control line.

Microcontroller EEPROM

Figure 53. DI, DO control line common connection

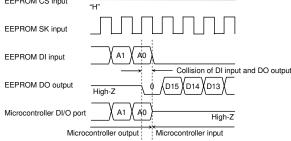

OData collision of microcontroller DI/O output and DO output and feedback of DO output to DI input.

Drive from the microcontroller DI/O output to DI input on I/O timing, and signal output from DO output occur at the same time in the following points.

(1) 1 clock cycle to take in A0 address data at read command Dummy bit "0" is output to DO terminal.

→When address data A0 = "1" input, through current route occurs.

Figure 54. Collision timing at read data output at DI, DO direct connection

(2) Timing of CS = "H" after write command. DO terminal in READY /  $\overline{BUSY}$  function output.

When the next start bit input is recognized, "HIGH-Z" gets in.

→Especially, at command input after write, when CS input is started with microcontroller DI/O output "L", READY output "H" is output from DO terminal, and through current route occurs.

Feedback input at timing of these (1) and (2) does not cause disorder in basic operations, if resistance R is inserted.

Figure 55. Collision timing at DI, DO direct connection

Note) As for the case (2), attention must be paid to the following.

When status READY is output, DO and DI are shared, DI="H" and the microcontroller DI/O="High-Z" or the microcontroller DI/O="H",if SK clock is input, DO output is input to DI and is recognized as a start bit, and malfunction may occur. As a method to avoid malfunction, at status READY output, set SK="L", or start CS within 4 clocks after "H" of READY signal is output.

Figure 56. Start bit input timing at DI, DO direct connection

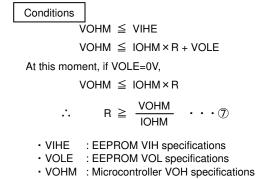

#### OSelection of resistance value R

The resistance R becomes through current limit resistance at data collision. When through current flows, noises of power source line and instantaneous stop of power source may occur. When allowable through current is defined as I, the following relation should be satisfied. Determine allowable current amount in consideration of impedance and so forth of power source line in set. And insert resistance R, and set the value R to satisfy EEPROM input level VIH/VIL even under influence of voltage decline owing to leak current and so forth. Insertion of R will not cause any influence upon basic operations.

## (1) Address data A0 = "1" input, dummy bit "0" output timing

(When microcontroller DI/O output is "H", EEPROM DO outputs "L", and "H" is input to DI)

- · Make the through current to EEPROM 10mA or below.

- See to it that the level VIH of EEPROM should satisfy the following.

• IOHM : Microcontroller IOH specifications

Figure 57. Circuit at DI, DO direct connection (Microcontroller DI/O "H" output, EEPROM "L" output)

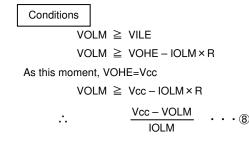

#### (2) DO status READY output timing

(When the microcontroller DI/O is "L", EEPROM DO output "H", and "L" is input to DI)

· Set the EEPROM input level VIL so as to satisfy the following.

VILE : EEPROM VIL specifications

VOHE : EEPROM VOH specifications

VOLM : Microcontroller VOL specifications

IOLM : Microcontroller IOL specifications

Example) When Vcc=5V, VOHM=5V, IOHM=0.4mA, VOLM=5V, IOLM=0.4mA,

From the equation 7,

$$R \ge \frac{5}{0.4 \times 10^{-3}}$$

$$\therefore$$

R  $\geq$  12.5 [k $\Omega$ ] · · · 9

From the equation®,

$$R \ge \frac{Vcc - VOLM}{IOLM}$$

$$R \ge \frac{5 - 0.4}{2.1 \times 10^{-3}}$$

$$\therefore \qquad R \, \geqq \quad 2.2 \, [k\Omega] \qquad \cdot \cdot \cdot \cdot \textcircled{10}$$

Therefore, from the equations (9) and (10),

$$\therefore$$

R  $\geq$  12.5 [k $\Omega$ ]

Figure 58. Circuit at DI, DO direct connection (Microcontroller DI/O "L" output, EEPROM "H" output)

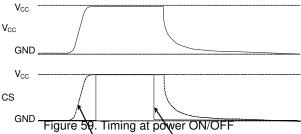

#### 7) Notes on power ON/OFF

#### · At power ON/OFF, set CS "L".

When CS is "H", this IC gets in input accept status (active). If power is turned on in this status, noises and the likes may cause malfunction, mistake write or so. To prevent these, at power ON, set CS "L". (When CS is in "L" status, all inputs are cancelled.) And at power decline, owing to power line capacity and so forth, low power status may continue long. At this case too, owing to the same reason, malfunction, mistake write may occur, therefore, at power OFF too, set CS "L".

(Bad example) CS pin is pulled up to Vcc.

Bad example

`Good exampleGood example) It is "L" at power ON/OFF.

In this case, CS becomes "H" (active status), and EEPROM may have malfunction, mistake write owing to noise and the likes.

Even when CS input is High-Z, the status becomes like this case, which please note.

Set 10ms or higher to recharge at power OFF.

When power is turned on without observing this condition,

IC internal circuit may not be reset, which please note.

#### **OPOR** citcuit

This IC has a POR (Power On Reset) circuit as a mistake write countermeasure. After POR action, it gets in write disable status. The POR circuit is valid only when power is ON, and does not work when power is OFF. However, if CS is "H" at power ON/OFF, it may become write enable status owing to noises and the likes. For secure actions, observe the follwing conditions.

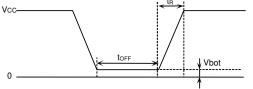

- 1. Set CS="L"

- 2. Turn on power so as to satisfy the recommended conditions of tR, tOFF, Vbot for POR circuit action.

Figure 60. Rise waveform diagram

Recommended conditions of tR, tOFF, Vbot

| t <sub>R</sub> | t <sub>OFF</sub> | Vbot          |

|----------------|------------------|---------------|

| 10ms or below  | 10ms or higher   | 0.3V or below |

| 100ms or below | 10ms or higher   | 0.2V or below |

LVCC (VCC-Lockout) circuit prevents data rewrite action at low power, and prevents wrong write. At LVCC voltage (Typ.=1.2V) or below, it prevent data rewrite.

#### 8) Noise countermeasures

**OLVCC** circuit

### OVcc noise (bypass capacitor)

When noise or surge gets in the power source line, malfunction may occur, therefore, for removing these, it is recommended to attach a by pass capacitor  $(0.1\mu\text{F})$  between IC Vcc and GND, At that moment, attach it as close to IC as possible. And, it is also recommended to attach a bypass capacitor between board Vcc and GND.

#### **OSK** noise

When the rise time (tR) of SK is long, and a certain degree or more of noise exists, malfunction may occur owing to clock bit displacement. To avoid this, a Schmitt trigger circuit is built in SK input. The hysteresis width of this circuit is set about 0.2V, if noises exist at SK input, set the noise amplitude 0.2Vp-p or below. And it is recommended to set the rise time (tR) of SK 100ns or below. In the case when the rise time is 100ns or higher, take sufficient noise countermeasures. Make the clock rise, fall time as small as possible.

#### Notes for Use

- (1) Described numeric values and data are design representative values, and the values are not guaranteed.

- (2) We believe that application circuit examples are recommendable, however, in actual use, confirm characteristics further sufficiently. In the case of use by changing the fixed number of external parts, make your decision with sufficient margin in consideration of static characteristics and transition characteristics and fluctuations of external parts and our IC.

- (3) Absolute Maximum Ratings

If the absolute maximum ratings such as impressed voltage and action temperature range and so forth are exceeded, IC may be destructed. Do not impress voltage and temperature exceeding the absolute maximum ratings. In the case of fear exceeding the absolute maximum ratings, take physical safety countermeasures such as fuses, and see to it that conditions exceeding the absolute maximum ratings should not be impressed to IC.

- (4) GND electric potential

- Set the voltage of GND terminal lowest at any action condition. Make sure that each terminal voltage is not lower than that of GND terminal in consideration of transition status.

- (5) Heat design

- In consideration of allowable loss in actual use condition, carry out heat design with sufficient margin.

- (6) Terminal to terminal shortcircuit and wrong packaging When to package IC onto a board, pay sufficient attention to IC direction and displacement. Wrong packaging may destruct IC. And in the case of shortcircuit between IC terminals and terminals and power source, terminal and GND owing to foreign matter, IC may be destructed.

- (7) Use in a strong electromagnetic field may cause malfunction, therefore, evaluate design sufficiently

#### Status of this document

The Japanese version of this document is formal specification. A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document formal version takes priority.

## Package specifications

RFVM

Blank

Double cell

E2 : reel shape emboss taping TR : reel shape emboss taping

: MSOP8

: DIP-T8