Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

BT860-Sx

Bluetooth v4.2 Dual-Mode UART HCI Module

Version 1.0

#### BT860-Sx

Datasheet

# **REVISION HISTORY**

| Version | Date        | Notes           | Contributor             | Approver      |

|---------|-------------|-----------------|-------------------------|---------------|

| 1.0     | 12 Jan 2018 | Initial Version | Jacky Kuo<br>Raj Khatri | Jonathan Kaye |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

|         |             |                 |                         |               |

#### BT860-Sx

#### Datasheet

# **C**ONTENTS

| 1     | Scope                                      | 4  |

|-------|--------------------------------------------|----|

| 2     | Operational Description                    | 4  |

| 3     | Block Diagram and Descriptions             | 5  |

| 4     | Specifications                             | 6  |

| 5     | Pin Definitions                            | 6  |

| 6     | DC Electrical Characteristics              | 8  |

| 7     | RF Characteristics                         | 9  |

| 8     | Interface                                  | 10 |

| 8.1.  | Global Coexistence Interface               | 10 |

| 8.2.  | UART Interface                             | 10 |

| 8.3.  | PCM Interface                              | 11 |

| 8.4.  | I <sup>2</sup> S Interface                 | 18 |

| 9     | Antenna Performance                        | 20 |

| 10    | Mechanical Dimensions and Land Pattern     | 22 |

| 11    | Implementation Note                        | 23 |

| 11.1. | PCB Layout on Host PCB                     | 23 |

| 12    | Application Note for Surface Mount Modules | 24 |

| 12.1. | Introduction                               | 24 |

| 12.2. | Shipping                                   | 24 |

| 12.3. | Reflow Parameters                          | 26 |

| 13    | Japan (MIC) Regulatory                     | 27 |

| 13.1. | Antenna Information                        | 27 |

| 14    | FCC Regulatory                             | 27 |

| 15    | Industry Canada Regulatory                 | 29 |

| 16    | European Union Regulatory                  | 31 |

| 17    | Ordering Information                       | 32 |

| 17.1. | General Comments                           | 32 |

| 18    | Bluetooth SIG Approvals                    | 32 |

| 19    | Additional Assistance                      | 34 |

#### 1 SCOPE

This document describes key hardware aspects of the Laird BT860-Sx Bluetooth HCI modules. This document is intended to assist device manufacturers and related parties with the integration of this module into their host devices. Data in this document are drawn from several sources including data sheets for the CYW20704A2. Because the BT860-Sx is currently in development stage, this document is preliminary and the information in this document is subject to change. Please contact Laird Technologies or visit the Laird website at <a href="https://www.lairdtech.com">www.lairdtech.com</a> to obtain the most recent version of this document.

BT860-SA module

BT860-ST module

#### 2 OPERATIONAL DESCRIPTION

The BT860-Sx series of UART HCI modules leverage the Cypress CYW20704 A2 chipset to provide exceptionally low power consumption with outstanding range for OEMs needing both Classic Bluetooth and Bluetooth Low Energy support. The Bluetooth v4.2 core specification shortens your development time and provides enhanced throughput, security and privacy.

The BT860-Sx modules are ideal when designers need both performance and minimum size. For maximum flexibility in integration, they support a host UART interface, I<sup>2</sup>S and PCM audio interfaces, GPIO, and Cypress'GCI coexistence (2-Wire). The modules provide excellent RF performance and identical footprint options for integrated antenna or an external antenna via a trace pin.

These modules present a Bluetooth standard HCI interface with support for Linux / Android and Embedded Bluetooth software stacks for operating system backed devices. Additionally, Laird has partnered with Searan for support of their ultra small, flexible 'dotstack' platform for embedded Cortex M3 and M4 implementations.

# Features and Benefit: 8 TROHS

- Bluetooth v4.2 Dual mode (Classic Bluetooth and BLE)

- Compact footprint

- 2-wire Cypress Global Coexistence Interface (GCI)

- High antenna radiation gain and efficiency

- Good interference rejection for multi-com system (GSM/WCDMA)

- Class 1 output 8 dBm

- UART, I<sup>2</sup>S, and PCM

- Industrial Temperature Range

- 512 Kbits EEPROM support

- Bluetooth Controller subsystem

- FCC, IC, CE, RCM and Giteki approvals

#### **Application Areas**

- Medical devices

- ePOS terminals

- Barcode scanners

- Industrial Cable Replacement

- IoT PlatformsAutomotive Diagnostic Equipment

- Personal Digital Assistants (PDA)

# 3 BLOCK DIAGRAM AND DESCRIPTIONS

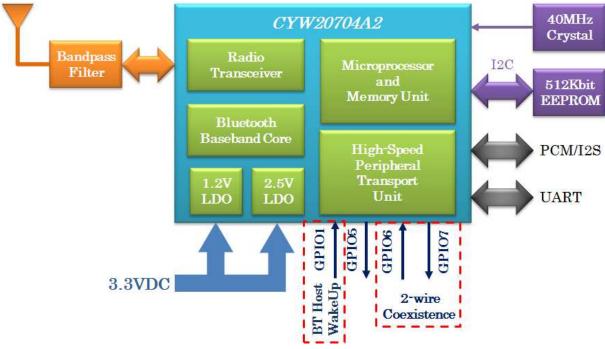

Figure 1: BT860 Module block diagram

| CYW20704A2<br>(Main chip) | The BT860-Sx is based on CYW20704A2 dual mode chip. The chip is a single-chip radio with on-chip LDO regulators and baseband IC for Bluetooth 2.4 GHz systems including EDR to 3 Mbps.                                                                                                                                                                                               |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Dedicated signal and baseband processing is included for full Bluetooth operation. The chip provides I <sup>2</sup> S/PCM and UART interfaces. There are two general purpose I/Os be configured for proprietary of Cypress GCI used and a general purpose I/O can be configured for scan/inquire/paging/data traffic of indicator. These three I/Os pins are controlled by firmware. |

| Antenna                   | BT860-SA – The antenna is a ceramic monopole chip antenna. BT860-ST – Trace Pad provision for use with a range of certified External Antennas                                                                                                                                                                                                                                        |

| Band Pass<br>Filter       | The band pass filter filters the out-of-band emissions from the transmitter to meet the specific regulations for type approvals of various countries.                                                                                                                                                                                                                                |

| EEPROM                    | There are 512 Kbits EEPROM embedded on the BT860-Sx module which can be used to store parameters, such as BD_ADDR, maximum TX power, PCM configuration.                                                                                                                                                                                                                              |

| Crystal                   | The embedded 40 MHz crystal is used for generating the clock for the entire module.                                                                                                                                                                                                                                                                                                  |

|                           |                                                                                                                                                                                                                                                                                                                                                                                      |

# 4 SPECIFICATIONS

Table 1: BT860 specifications

| Categories                | Feature                      | Implementation                                    |  |  |  |

|---------------------------|------------------------------|---------------------------------------------------|--|--|--|

|                           | Bluetooth®                   | V4.2 Dual Mode (BR / EDR / LE)                    |  |  |  |

|                           | Frequency                    | 2.402 - 2.480 GHz                                 |  |  |  |

| Wireless                  | Maximum Transmit             | Class 1                                           |  |  |  |

| Specification             | Power                        | +8 dBm from antenna                               |  |  |  |

|                           | Receive Sensitivity          | -94 dBm                                           |  |  |  |

|                           | Range                        | Circa 100 meters                                  |  |  |  |

|                           | Data Rates                   | Up to 3 Mbps (over-the-air)                       |  |  |  |

| Host Interface            | UART                         | Up to 4 Mbps                                      |  |  |  |

| nost interrace            | GPIO                         | 3.3V for all general purpose I/Os                 |  |  |  |

| Operational Modes         | HCI                          | Host Controller Interface over UART               |  |  |  |

| EEPROM                    | 2-wire                       | 512 Kbits                                         |  |  |  |

| Coexistence               | 802.11 (Wi-Fi)               | 2-Wire Cypress Global Coexistence Interface (GCI) |  |  |  |

| Supply Voltage            | Supply                       | 3.0V – 3.6V                                       |  |  |  |

| Power                     | Current                      | Idle Mode ~8 mA                                   |  |  |  |

| Consumption               |                              | File Transfer ~43 mA                              |  |  |  |

| Antenna Option            | Internal                     | Multilayer ceramic antenna                        |  |  |  |

|                           | External                     | Trace Pad                                         |  |  |  |

| Physical                  | Dimensions                   | 8.5 x 12.85 x 2.2 mm (BT860-SA)                   |  |  |  |

| (Width x Length x Height) | 2511010110                   | 8.5 x 12.85 x 1.9 mm (BT860-ST)                   |  |  |  |

| Environmental             | Operating                    | -30° C to +85° C                                  |  |  |  |

|                           | Storage                      | -40° C to +85° C                                  |  |  |  |

| Miscellaneous             | Lead Free                    | Lead-free and RoHS compliant                      |  |  |  |

| iviiscellalieuus          | Warranty                     | One-Year Warranty                                 |  |  |  |

| Approvals                 | Bluetooth®                   | Controller Subsystem Approved                     |  |  |  |

| η <b>ρη υναι</b> ς        | FCC / IC / CE / RCM / Giteki | All BT860-Sx series                               |  |  |  |

|                           |                              |                                                   |  |  |  |

# 5 PIN DEFINITIONS

Table 2: BT860 pin definitions

| Pin<br>No. | Pin Name | 1/0            | Supply<br>Domain | Description                    | If Unused |

|------------|----------|----------------|------------------|--------------------------------|-----------|

| 1          | NC       |                |                  |                                | NC        |

| 2          | GND      | GND            |                  | Ground                         | GND       |

| 3          | GPIO_5   | Bi-directional | 3V3              | Programmable input/output line |           |

| 4          | UART_RTS | Bi-directional | 3V3              | UART request to send output    | NC        |

| 5          | UART_TXD | Bi-directional | 3V3              | UART transmit data             | NC        |

| 6          | UART_CTS | Bi-directional | 3V3              | UART clear to send input       | NC        |

#### BT860-Sx

Datasheet

| Pin<br>No. | Pin Name        | 1/0            | Supply<br>Domain | Description                                                      | If Unused |

|------------|-----------------|----------------|------------------|------------------------------------------------------------------|-----------|

| 7          | UART_RXD        | Bi-directional | 3V3              | UART receive data                                                | NC        |

| 8          | RESET           | Input          | 3V3              | Active-low reset input                                           | N/A       |

| 9          | 3.3V            | Input          | 3V3              | Module main DC power supply, Input to internal 1.2V and 2.5V LDO | N/A       |

| 10         | NC              |                |                  |                                                                  | NC        |

| 11         | GND             | GND            |                  | Ground                                                           | GND       |

| 12         | GND             | GND            |                  | Ground                                                           | GND       |

| 13         | GND             | GND            |                  | Ground                                                           | GND       |

| 14         | GND             | GND            |                  | Ground                                                           | GND       |

| 15         | GND             | GND            |                  | Ground                                                           | GND       |

| 16         | GND             | GND            |                  | Ground                                                           | GND       |

| 17         | RF              |                |                  | BT860-ST RF signal output (50 $\Omega$ ) BT860-SA No connection  |           |

| 18         | GND             | GND            |                  | Ground                                                           | GND       |

| 19         | I2S_WS/PCM_SYNC | Bidirectional  | 3V3              | PCM sync/I2S word select                                         | NC        |

| 20         | I2S_CLK/PCM_CLK | Bidirectional  | 3V3              | PCM/I2S clock                                                    | NC        |

| 21         | I2S_DI/PCM_IN   | Bidirectional  | 3V3              | PCM/I2S data input                                               | NC        |

| 22         | I2S_OUT/PCM_OUT | Bidirectional  | 3V3              | PCM/I2S data output                                              | NC        |

| 23         | GND             | GND            |                  | Ground                                                           | GND       |

| 24         | NC              |                |                  |                                                                  | NC        |

| 25         | BT_SECI_IN      | Input          | 3V3              | Coexistence data input                                           | NC        |

| 26         | BT_SECI_OUT     | Output         | 3V3              | Coexistence data output                                          | NC        |

| 27         | NC              |                |                  |                                                                  | NC        |

| 28         | NC              |                |                  |                                                                  | NC        |

| 29         | BT_HOST_WAKE    | Output         | 3V3              | BT device to wake up the Host                                    | NC        |

| 30         | GND             | GND            |                  | Ground                                                           | NC        |

| Din Dofi   | nition Note:    |                |                  |                                                                  |           |

#### **Pin Definition Note:**

**Note 1** The GPIO\_5 controlled by the default firmware for the status of BT860 indications.

# 6 DC ELECTRICAL CHARACTERISTICS

Table 3: Absolute maximum rating

| Rating                     | Min | Max  | Unit |

|----------------------------|-----|------|------|

| Storage temperature        | -40 | +150 | °C   |

| Operating Temperature      | -30 | +85  | °C   |

| ESD Contact Discharge      | -4  | +4   | KV   |

| ESD Air Discharge          | -8  | +8   | KV   |

| Moisture Sensitivity Level | 4   | -    | -    |

| 3V3 Input                  | 3.0 | 3.6  | V    |

Table 4: Recommended operating conditions

| Rating                | Min | Max  | Unit           |

|-----------------------|-----|------|----------------|

| Storage temperature   | -40 | +150 | <sup>o</sup> C |

| Operating Temperature | -30 | +85  | °C             |

| 3V3 Input             | 3.0 | 3.6  | V              |

Table 5: Digital I/O characteristics

| Normal Operation                                                          | Min     | Тур. | Max | Unit |

|---------------------------------------------------------------------------|---------|------|-----|------|

| V <sub>IL</sub> Input Low Voltage (VDDO * = 3V3)                          | -       | -    | 0.8 | V    |

| V <sub>IH</sub> Input High Voltage (VDDO * = 3V3)                         | 2.0     | -    | -   | V    |

| V <sub>OL</sub> Output Low Voltage                                        | -       | -    | 0.4 | V    |

| V <sub>OH</sub> Output High Voltage                                       | 3V3-0.4 | -    | -   | V    |

| I <sub>IL</sub> Input Low Current                                         | -       | -    | 1.0 | μΑ   |

| I <sub>IH</sub> Input High Current                                        | -       | -    | 1.0 | μΑ   |

| I <sub>OL</sub> Output Low Current (VDDO * = 3V3, V <sub>OL</sub> = 0.4V) | -       | -    | 2.0 | mA   |

| I <sub>OH</sub> Output Low Current (VDDO * = 3V3, V <sub>OH</sub> = 2.9V) | -       | -    | 2.0 | mA   |

| C <sub>IN</sub> Input Capacitance                                         | -       | -    | 0.4 | рF   |

<sup>\*:</sup> The VDDO is denoted the digital I/O voltage and it's depended on the Pin9 (3V3) input of module.

Table 6: Current consumption

| Normal Operation       | Peak (8 dBm) | Unit |

|------------------------|--------------|------|

| Idle                   | 8            | mA   |

| Inquiry                | 23           | mA   |

| File Transfer          | 43           | mA   |

| BLE Connected (Master) | 26           | mA   |

| BLE Scan (Master)      | 26           | mA   |

| BLE File Transfer      | 27           | mA   |

# 7 RF CHARACTERISTICS

Table 7: BDR/EDR/BLE transmitter characteristics (Input = 3V3 @ 25° C)

|                                             | Parameter                   | Min | Тур. | Max | BT. Spec. | Unit |

|---------------------------------------------|-----------------------------|-----|------|-----|-----------|------|

| Classic BT (BDR) - GFS                      | K Maximum RF Transmit Power | 6   | 8    | 10  | 20        | dBm  |

| Classic BT - EDR Maxii                      | num RF Transmit Power       | 2   | 4    | 6   | 20        | dBm  |

| BLE Maximum RF Trai                         | nsmit Power                 | 6   | 8    | 10  | 20        | dBm  |

| RF power variation ov                       | er temperature range        | -   | 2.0  | -   | -         | dB   |

| RF power variation ov                       | er BT band                  | -   | 2    | -   | -         | dB   |

| RF power control step                       | )                           | 2   | 4    | 8   | -         | dB   |

| Initial Carrier Frequer                     | icy Tolerance               | -   | 10   | -   | ±75       | kHz  |

| BLE Frequency Accura                        | асу                         |     | 10   |     | ±150      | kHz  |

| 20 dB Bandwidth                             |                             | -   | 920  | -   | 1000      | kHz  |

|                                             | 1.0 MHz <  M-N  < 1.5 MHz   | -   | -    | -39 | -26       | dBc  |

| In-Band Spurious<br>Emissions               | 1.5 MHz <  M-N  < 2.5 MHz   | -   | -    | -39 | -20       | dBm  |

| 211110010110                                | $ M-N  \geq 2.5  MHz$       | -   | -    | -47 | -40       | dBm  |

| BLE In-Band                                 | $f_{TX} \pm 2 MHz$          | -   | -    | -48 | -20       | dBm  |

| Emission                                    | $f_{TX} \pm [3 + n] MHz$    | -   | -    | -47 | -30       | dBm  |

| Drift rate                                  |                             | -   | 10   | -   | +/-25     | kHz  |

| ΔF <sub>1Avg</sub>                          |                             | -   | 152  | -   | 140<>175  | kHz  |

| ΔF <sub>2Max</sub>                          |                             | 100 | -    | -   | 99.9      | %    |

| ΔF <sub>2Avg</sub> / ΔF <sub>1Avg</sub>     |                             | -   | 1.0  | -   | ≥ 0.8     |      |

| BLE ΔF <sub>1Avg</sub>                      |                             | -   | 245  | -   | 225<>275  | kHz  |

| BLE ΔF <sub>2Max</sub>                      |                             | 100 | -    | -   | 99.9      | %    |

| BLE ΔF <sub>2Avg</sub> / ΔF <sub>1Avg</sub> |                             | -   | 1.0  | -   | ≧ 0.8     |      |

Table 8: BDR/EDR/BLE receiver sensitivity (Input = 3V3 @ 25°C)

| Parameter Conditions  |                                  | Min | Тур. | Max | BT. Spec. | Unit |

|-----------------------|----------------------------------|-----|------|-----|-----------|------|

|                       | GFSK, 0.1% BER, 1Mbps            | -   | -90  | -   | -70       | dBm  |

| Consitivity           | $\pi$ /4-DQPSK, 0.01% BER, 2Mbps | -   | -94  | -   | -70       | dBm  |

| Sensitivity           | 8-DPSK, 0.01% BER, 3Mbps         | -   | -87  | -   | -70       | dBm  |

|                       | BLE GFSK, 30.8% PER, 1Mbps       | -   | -94  | -   | -70       | dBm  |

| Sensitivity variation | All Modulations (Over BT band)   | -   | 2    | -   | -         | dB   |

#### 8 INTERFACE

#### 8.1. Global Coexistence Interface

The BT860-Sx supports the proprietary Cypress Global Coexistence Interface (GCI) which is a 2-wire interface.

The following key features are associated with the interface:

- Enhanced coexistence data can be exchanged over GCI\_SECI\_IN and GCI\_SECI\_OUT a two-wire interface, one serial input (GCI\_SECI\_IN), and one serial output (GCI\_SECI\_OUT). The both pins are controlled by the configuration file that is stored in EEPROM from the host.

- It supports generic UART communication between WLAN and Bluetooth devices.

- To conserve power, it is disabled when inactive.

- It supports automatic resynchronization upon waking from sleep mode.

- It supports a baud rate of up to 4 Mbps.

Table 9 shows the two-wire BT coexistence interface assignments.

Table 9: BT GCI Two-Wire Coexistence

| Coexistence Signal Name | Signal Assignment |

|-------------------------|-------------------|

| BT_SECI_IN              | GPIO_6            |

| BT_SECI_OUT             | GPIO_7            |

#### 8.2. UART Interface

The BT860-Sx has a single UART for Bluetooth. The UART is a standard four-wire interface (RX, TX, RTS, and CTS) with adjustable baud rates from 38400 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate may be selected through a vendor-specific UART HCI command.

UART has a 1040-byte receive FIFO and 1040-byte transmits FIFO to support EDR. Access to the FIFO is conducted through the AHB interface through either DMA or the CPU. The UART supports the Bluetooth 4.2 UART HCI specification: H4, and a custom Extended H4. The default baud rate is 115.2 Kbaud.

The BT860-Sx UART can perform XON/XOFF flow control and includes hardware support for Serial Line Input Protocol (SLIP). It can also perform wake-on activity. For the BT860-Sx is supported BT to wake-up Host.

Normally, the UART baud rate is set by a configuration record downloaded after device reset, or by automatic baud rate detection, and the host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is included through a vendor-specific command that allows the host to adjust the contents of the baud rate registers. The BT860-Sx UART operates correctly with the host UART if the combined baud rate error of the two devices is within ±2%.

Table 10: Example of common baud rates

| Actual Rate | Error (%)                                |

|-------------|------------------------------------------|

| 400000      | 0.00                                     |

| 3000000     | 0.00                                     |

| 2000000     | 0.00                                     |

| 1500000     | 0.00                                     |

| 923077      | 0.16                                     |

|             | 4000000<br>3000000<br>2000000<br>1500000 |

| Desired Rate | Actual Rate | Error (%) |

|--------------|-------------|-----------|

| 460800       | 461538      | 0.16      |

| 230400       | 230796      | 0.17      |

| 115200       | 115385      | 0.16      |

| 57600        | 57692       | 0.16      |

| 38400        | 38400       | 0.00      |

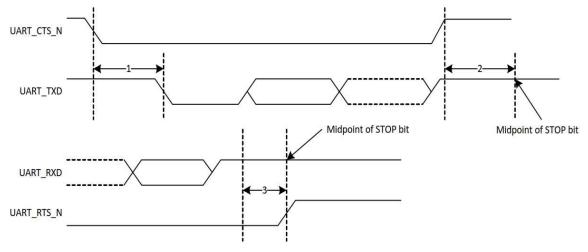

Table 11 and Figure 2 show UART timing of specifications.

Table 11: UART timing specifications

| Reference | Characteristics                                        | Min. | Тур. | Max. | Unit           |

|-----------|--------------------------------------------------------|------|------|------|----------------|

| 1         | Delay time UART_CTS_N low to UART TXD valid            | -    | -    | 1.50 | Bit<br>periods |

| 2         | Setup time UART_CTS_N high before midpoint of stop bit | -    | -    | 0.67 | Bit<br>periods |

| 3         | Delay time<br>Midpoint of stop bit to UART_CTS_N high  | -    | -    | 1.33 | Bit<br>periods |

Figure 2: UART timing

#### 8.3. PCM Interface

The BT860-Sx supports two independent PCM interfaces that share the pins with I2S interfaces. The PCM interface on the BT860-Sx can connect to linear PCM Codec devices in master or slave mode. In master mode, the BT860 generates the PCM\_CLK and PCM\_SYNC signals, and in slave mode, these signals are provided by another master on the PCM interface and are inputs to the BT860.

The configuration of the PCM interface may be adjusted by the host using vendor-specific HCI commands.

For additional information, refer to the DVK-BT86x User Guide available from the BT86x product page of the Laird website.

#### 8.3.1. Slot Mapping

The BT860-Sx supports up to three simultaneous full-duplex SCO or eSCO channels through the PCM interface. These three channels are time-multiplexed onto the single PCM interface by using a time-slotting scheme where the 8 kHz or 16 kHz audio sample interval is divided into as many as 16 slots. The number of slots is dependent on the selected interface rate of 128 kHz, 512 kHz, or 1024 kHz. The corresponding number of slots for these interface rate is 1, 2, 4, 8 and 16, respectively. Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tristates its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tristates its output after the falling edge of the PCM clock during the last bit of the slot.

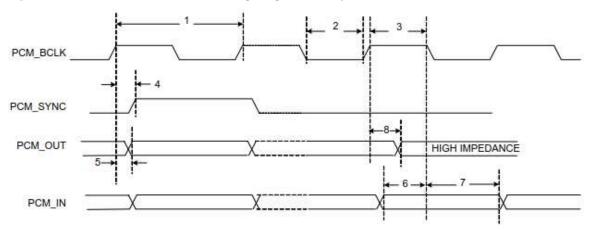

#### 8.3.2. Frame Synchronization

The BT860-Sx supports both short- and long-frame synchronization in both master and slave modes. In short-frame synchronization mode, the frame synchronization signal uses an active-high pulse at the audio frame rate that is a single-bit period in width and is synchronized to the rising edge of the bit clock. The PCM slave looks for a high on the falling edge of the bit clock and expects the first bit of the first slot to start at the next rising edge of the clock.

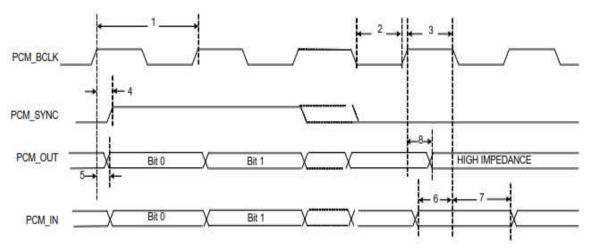

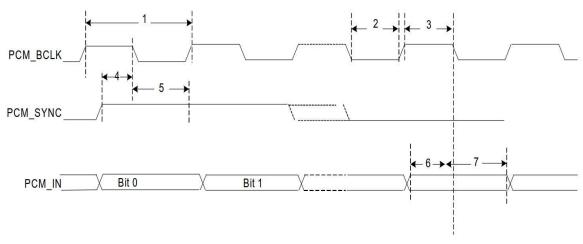

Figure 3 and Table 12 shows PCM Timing Diagram and Specifications for the master mode of short-frame.

Figure 3: PCM timing diagram (Short-Frame Sync, Master Mode)

Table 12: PCM Interface timing specifications (Short-Frame Sync, Master Mode)

| Reference | Characteristics                                                                              | Min. | Тур. | Max. | Unit |

|-----------|----------------------------------------------------------------------------------------------|------|------|------|------|

| 1         | PCM bit clock frequency                                                                      | -    | -    | 12   | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41   | -    | -    | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41   | -    | -    | ns   |

| 4         | PCM_SYNC setup                                                                               | 0    | -    | 25   | ns   |

| 5         | PCM_OUT delay                                                                                | 0    | -    | 25   | ns   |

| 6         | PCM_IN setup                                                                                 | 8    | -    | -    | ns   |

| 7         | PCM_IN hold                                                                                  | 8    | -    | -    | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance | 0    | -    | 25   | ns   |

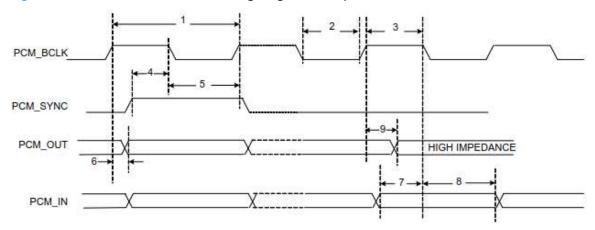

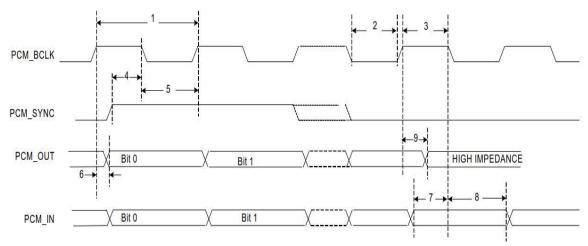

Figure 4 and Table 13 shows PCM Timing Diagram and Specifications for the slave mode of short-frame.

Figure 4: PCM timing diagram (Short-Frame Sync, Slave Mode)

Table 13: PCM Interface timing specifications (Short-Frame Sync, Slave Mode)

| Reference | Characteristics                                                                              | Min. | Тур. | Max. | Unit |

|-----------|----------------------------------------------------------------------------------------------|------|------|------|------|

| 1         | PCM bit clock frequency                                                                      | -    | -    | 12   | MHz  |

| 2         | PCM bit clock LOW                                                                            | 41   | -    | -    | ns   |

| 3         | PCM bit clock HIGH                                                                           | 41   | -    | -    | ns   |

| 4         | PCM_SYNC setup                                                                               | 8    | -    | -    | ns   |

| 5         | PCM_SYNC_hold                                                                                | 8    | -    | -    | ns   |

| 6         | PCM_OUT delay                                                                                | 0    | -    | 25   | ns   |

| 7         | PCM_IN setup                                                                                 | 8    | -    | -    | ns   |

| 8         | PCM_IN hold                                                                                  | 8    | -    | -    | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last bit period to PCM_OUT becoming high impedance |      | -    | 25   | ns   |

In long-frame synchronization mode, the frame synchronization signal is again an active-high pulse at the audio frame rate; however, the duration is three bit periods and the pulse starts coincident with the first bit of the first slot.

Figure 5 through Table 14 shows PCM Timing Diagram and Specifications for the master mode of long-frame.

Figure 5: PCM timing diagram (Long-Frame Sync, Master Mode)

Table 14: PCM Interface timing specifications (Long-Frame Sync, Master Mode)

| Reference | Characteristics                                                                                | Min. | Тур. | Max. | Unit |

|-----------|------------------------------------------------------------------------------------------------|------|------|------|------|

| 1         | PCM bit clock frequency                                                                        | -    | -    | 12   | MHz  |

| 2         | PCM bit clock LOW                                                                              | 41   | -    | -    | ns   |

| 3         | PCM bit clock HIGH                                                                             | 41   | -    | -    | ns   |

| 4         | PCM_SYNC delay                                                                                 | 0    | -    | 25   | ns   |

| 5         | PCM_OUT delay                                                                                  | 0    | -    | 25   | ns   |

| 6         | PCM_IN setup                                                                                   | 8    | -    | -    | ns   |

| 7         | PCM_IN hold                                                                                    | 8    | -    | -    | ns   |

| 8         | Delay from rising edge of PCM_BCLK during last  bit period to PCM_OUT becoming high  impedance |      | -    | 25   | ns   |

Figure 6 and Table 15: PCM Interface timing specifications (Long-Frame Sync, Slave Mode) shows PCM Timing Diagram and Specifications for the slave mode of long-frame

Figure 6: PCM timing diagram (Long-Frame Sync, Slave Mode)

Table 15: PCM Interface timing specifications (Long-Frame Sync, Slave Mode)

| Reference | Characteristics                                                                                | Min. | Тур. | Max. | Unit |

|-----------|------------------------------------------------------------------------------------------------|------|------|------|------|

| 1         | PCM bit clock frequency                                                                        | -    | -    | 12   | MHz  |

| 2         | PCM bit clock LOW                                                                              | 41   | -    | -    | ns   |

| 3         | PCM bit clock HIGH                                                                             | 41   | -    | -    | ns   |

| 4         | PCM_SYNC setup                                                                                 | 8    | -    | -    | ns   |

| 5         | PCM_SYNC_hold                                                                                  | 8    | -    | -    | ns   |

| 6         | PCM_OUT delay                                                                                  | 0    | -    | 25   | ns   |

| 7         | PCM_IN setup                                                                                   | 8    | -    | -    | ns   |

| 8         | PCM_IN hold                                                                                    | 8    | -    | -    | ns   |

| 9         | Delay from rising edge of PCM_BCLK during last 9 bit period to PCM_OUT becoming high impedance |      | -    | 25   | ns   |

#### 8.3.3. Data Formatting

The BT860-Sx may be configured to generate and accept several different data formats. For conventional narrowband speech mode, the BT860-Sx uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits can be configured to support various data formats on the PCM interface. The remaining three bits are ignored on the input and may be filled with 0s, 1s, a sign bit, or a programmed value on the output. The default format is 13-bit 2's complement data, left justified, and clocked MSB first.

#### 8.3.4. Wideband Speech Support

When the host encodes Wideband Speech (WBS) packets in transparent mode, the encoded packets are transferred over the PCM bus for an eSCO voice connection. In this mode, the PCM bus is typically configured in master mode for a 4 kHz sync rate with 16-bit samples, resulting in a 64 Kbps bit rate. The BT860-Sx also supports slave transparent mode using a proprietary rate-matching scheme. In SBC-code mode, linear 16-bit data at 16 kHz (256Kbps rate) is transferred over the PCM bus.

Americas: +1-800-492-2320

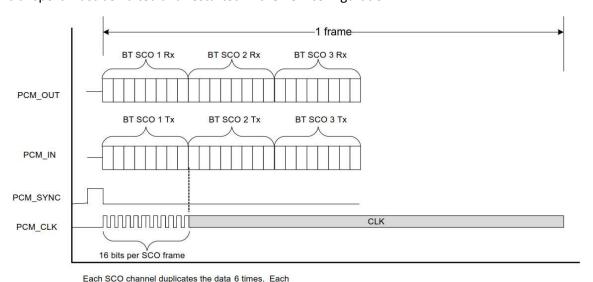

#### 8.3.5. Multiplexed Bluetooth Over PCM

Bluetooth supports multiple audio streams within the Bluetooth channel and both 16 kHz and 8 kHz streams can be multiplexed. This mode of operation is only supported when the Bluetooth host is the master. Figure 7 shows the operation of the multiplexed transport with three simultaneous SCO connections. To accommodate additional SCO channels, the transport clock speed is increased. To change between modes of operation, the transport must be halted and restarted in the new configuration.

WBS frame duplicates the data 3 times per frame

Figure 7: Functional Multiples Data diagram

#### 8.3.6. Burst PCM Mode

In this mode of operation, the PCM bus runs at a significantly higher rate of operation to allow the host to duty cycle its operation and save current. In this mode of operation, the PCM bus can operate at a rate of up to 24 MHz. This mode of operation is initiated with an HCl command from the host.

Figure 8 and Table 15 shows PCM Burst mode timing diagram and specifications for the receive-only mode of short-frame sync.

Figure 8: PCM Burst Mode timing (Receive Only, Short Frame Sync)

Table 15: PCM Burst Mode Specifications (Receive Only, Short-Frame Sync)

| Reference | Characteristics         | Min. | Тур. | Max. | Unit |

|-----------|-------------------------|------|------|------|------|

| 1         | PCM bit clock frequency | -    | -    | 24   | MHz  |

| 2         | PCM bit clock LOW       | 20.8 | -    | -    | ns   |

| 3         | PCM bit clock HIGH      | 20.8 | -    | -    | ns   |

| 4         | PCM_SYNC setup          | 8    | -    | -    | ns   |

| 5         | PCM_SYNC_hold           | 8    | -    | -    | ns   |

| 6         | PCM_IN setup            | 8    | -    | -    | ns   |

| 7         | PCM_IN hold             | 8    | -    | -    | ns   |

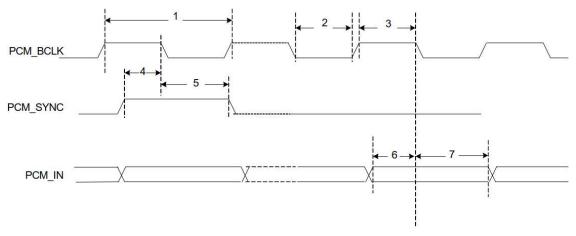

Figure 9 and Table 16 shows PCM Burst mode timing diagram and specifications for the receive-only mode of long-frame sync.

Figure 9: PCM Burst Mode Timing (Receive Only, Long Frame Sync)

Table 16: PCM Burst Mode Specifications (Receive Only, Long-Frame Sync)

| Reference | Characteristics         | Min. | Тур. | Max. | Unit |

|-----------|-------------------------|------|------|------|------|

| 1         | PCM bit clock frequency | -    | -    | 24   | MHz  |

| 2         | PCM bit clock LOW       | 20.8 | -    | -    | ns   |

| 3         | PCM bit clock HIGH      | 20.8 | -    | -    | ns   |

| 4         | PCM_SYNC setup          | 8    | -    | -    | ns   |

| 5         | PCM_SYNC_hold           | 8    | -    | -    | ns   |

| 6         | PCM_IN setup            | 8    | -    | -    | ns   |

| 7         | PCM_IN hold             | 8    | -    | -    | ns   |

#### 8.4. I<sup>2</sup>S Interface

The BT860-Sx supports two independent I<sup>2</sup>S digital audio ports. The I<sup>2</sup>S interface supports both master and slave modes. The I<sup>2</sup>S signals are:

I<sup>2</sup>S clock: I<sup>2</sup>S SCK

I<sup>2</sup>S Word Select: I<sup>2</sup>S WS

I<sup>2</sup>S Data Out: I<sup>2</sup>S SDO

I<sup>2</sup>S Data In: I<sup>2</sup>S SDI

I<sup>2</sup>S SCK and I<sup>2</sup>S WS become outputs in master mode and inputs in slave mode, while I<sup>2</sup>S SDO always stays as an output. The channel word length is 16 bits and the data is justified so that the MSB of the left-channel data is aligned with the MSB of the I<sup>2</sup>S bus, per the I<sup>2</sup>S specification. The MSB of each data word is transmitted one bit clock cycle after the I<sup>2</sup>S WS transition, synchronous with the falling edge of bit clock. Left-channel data is transmitted when I<sup>2</sup>S WS is low, and right-channel data is transmitted when I<sup>2</sup>S WS is high. Data bits sent by the BT860 are synchronized with the falling edge of I2S\_SCK and should be sampled by the receiver on the rising edge of I2S\_SSCK.

The clock rate in master mode is either of the following:

48 kHz x 32 bits per frame = 1.536 MHz

48 kHz x 50 bits per frame = 2.400 MHz

The master clock is generated from the input reference clock using a N/M clock divider.

In the slave mode, any clock rate is supported to a maximum of 3.072 MHz.

#### **8.4.1.** I<sup>2</sup>S Timing

Timing values specified in Table 17 are relative to high and low threshold levels.

Table 17: Timing for I2S Transmitters and Receivers

|                            | Transmitter                                             |              |              | Receiver  |              |              |         | Notes   |  |  |

|----------------------------|---------------------------------------------------------|--------------|--------------|-----------|--------------|--------------|---------|---------|--|--|

|                            | Lower Limit                                             |              | Uppei        | r Limit   | Lower Limit  |              | Uppei   | r Limit |  |  |

|                            | Min                                                     | Max          | Min          | Max       | Min          | Max          | Min     | Max     |  |  |

| Clock Period T             | $T_{tr}$                                                | -            | -            | -         | $T_r$        | -            | -       | -       |  |  |

|                            | Master Mode: Clock generated by transmitter or receiver |              |              |           |              |              |         |         |  |  |

| HIGH t <sub>HC</sub>       | $0.35T_{tr}$                                            | -            | -            | -         | $0.35T_{tr}$ | -            | -       | -       |  |  |

| LOW t <sub>LC</sub>        | $0.35T_{tr}$                                            | -            | -            | -         | $0.35T_{tr}$ | -            | -       | -       |  |  |

|                            | ľ                                                       | Master Mo    | de: Clock    | generated | l by transr  | nitter or r  | eceiver |         |  |  |

| HIGH t <sub>HC</sub>       | -                                                       | $0.35T_{tr}$ | -            | -         | -            | $0.35T_{tr}$ | -       | -       |  |  |

| LOW t <sub>LC</sub>        | -                                                       | $0.35T_{tr}$ | -            | -         | -            | $0.35T_{tr}$ | -       | -       |  |  |

| Rise time t <sub>RC</sub>  | -                                                       | -            | $0.15T_{tr}$ | -         | -            | -            | -       | -       |  |  |

|                            |                                                         |              |              | Transmi   | itter        |              |         |         |  |  |

| Delay t <sub>dtr</sub>     | -                                                       | -            | -            | 0.8T      | -            | -            | -       | -       |  |  |

| Hold time t <sub>htr</sub> | 0                                                       | -            | -            | -         | -            | -            | -       | -       |  |  |

| Receiver                   |                                                         |              |              |           |              |              |         |         |  |  |

| Setup time t <sub>sr</sub> | -                                                       | -            | -            | -         | -            | $0.2T_{r}$   | -       | -       |  |  |

| Hold time t <sub>hr</sub>  | -                                                       | -            | -            | -         | -            | 0            | -       | -       |  |  |

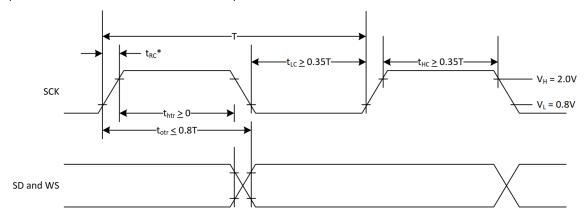

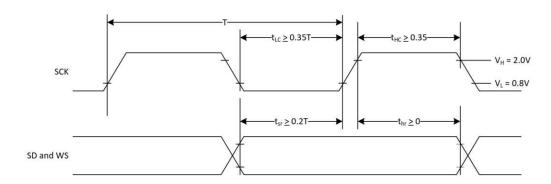

The time periods specified in Figure 10 and Figure 11 are defined by the transmitter speed. The receiver specifications must match transmitter performance.

T = Clock period

T<sub>tr</sub> = Minimum allowed clock period for transmitter

$T = T_{tr}$

Figure 10: I<sup>2</sup>S Transmitter timing

T = Clock period

T<sub>r</sub> = Minimum allowed clock period for transmitter

$T > T_r$

Figure 11: I<sup>2</sup>S Receiver Timing

<sup>\*</sup>  $t_{\text{RC}}$  is only relevant for transmitters in slave mode.

### 9 ANTENNA PERFORMANCE

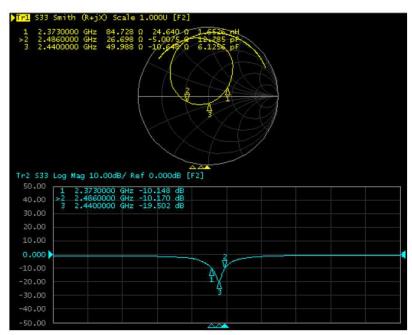

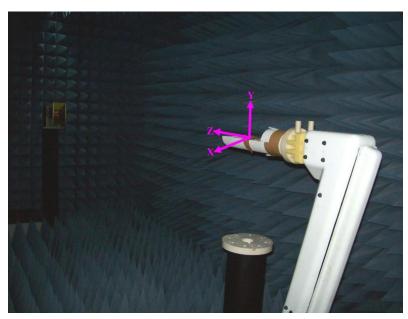

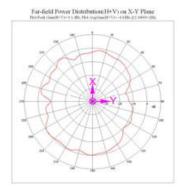

Table 18, Figure 12, Figure 13, and Figure 14 show the antenna gain and performance.

Table 18: Antenna gain

| Unit in dBi @ 2440MHz | XY-Plane |      | XZ-Plane |      | YZ-Plane |      | Efficiency |  |

|-----------------------|----------|------|----------|------|----------|------|------------|--|

| AT3216-B2R7HAA        | Peak     | Avg. | Peak     | Avg. | Peak     | Avg. | Efficiency |  |

|                       | 0.1      | -4.1 | 1.8      | -3.3 | -0.2     | -6.8 | 41%        |  |

Figure 12: Antenna Return Loss

Figure 13: Measurement XYZ polarization

Table 19: Plane definitions

| XY-Plane | Theta = 90° |

|----------|-------------|

| XZ-Plane | Phi = 0°    |

| YZ-Plane | Phi = 90°   |

# ◆XY-plane

#### Unit: dBi

|          | Peak gain | Avg. gain |

|----------|-----------|-----------|

| XY-plane | 0.1       | -4.1      |

# ♦XZ-plane

|          | Peak gain | Avg. gain |

|----------|-----------|-----------|

| XZ-plane | 1.8       | -3.3      |

# ♦YZ-plane

Peak gain Avg. gain

YZ-plane -0.2 -6.8

Figure 14: Antenna pattern

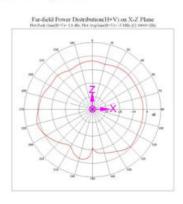

## 10 Mechanical Dimensions and Land Pattern

# 10.1. BT860 Mechanical Drawing

#### **Bottom View Device Pads**

- \* Dimensions from corner of BT860

- Pin1

**Note:** Dimensions are in millimetres.

Tolerances: .xx ±0.03 mm

.x ±1.3 mm

#### 11 IMPLEMENTATION NOTE

#### 11.1. PCB Layout on Host PCB

#### Checklist (for PCB):

- Must locate the BT860 module close to the edge of PCB.

- Use solid GND plane on inner layer (for best EMC and RF performance).

- Place GND vias close to module GND pads as possible

- Route traces to avoid noise being picked up on VCC supply.

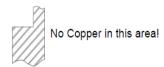

- Antenna Keep-out area:

- Ensure there is no copper in the antenna keep-out area on any layers of the host PCB.

- Keep all mounting hardware and metal clear of the area to allow proper antenna radiation.

- For best antenna performance, place the BT860 module on the edge of the host PCB, preferably in the corner with the antenna facing the corner.

- A different host PCB thickness dielectric will have small effect on antenna.

Figure 15: Recommend Antenna keep-out area (in Blue) used on the BT860

#### 11.1.1. Antenna Keep-out and Proximity to Metal or Plastic

Checklist (for metal /plastic enclosure):

- Minimum safe distance for metals without seriously compromising the antenna (tuning) is 40 mm top/bottom and 30 mm left or right.

- Metal close to the BT860-SA chip monopole antenna (bottom, top, left, right, any direction) will have degradation on the antenna performance. The amount of degradation is entirely system dependent which means some testing by customers is required (in their host application).

- Any metal closer than 20 mm starts to significantly degrade performance (S11, gain, radiation efficiency).

- It is best that the customer tests the range with mock-up (or actual prototype) of the product to assess effects of enclosure height (and material whether metal or plastic).

#### 12 Application Note for Surface Mount Modules

#### 12.1. Introduction

Laird surface mount modules are designed to conform to all major manufacturing guidelines. This application note is intended to provide additional guidance beyond the information that is presented in the user manual. This application note is considered a living document and is updated as new information is presented.

The modules are designed to meet the needs of a number of commercial and industrial applications. They are easy to manufacture and they conform to current automated manufacturing processes.

## 12.2. Shipping

#### 12.2.1. Tape and Reel Package Information

**Note:** Ordering information for Tape and Reel packaging is an addition of T/R to the end of the full module part number. For example, BT860 becomes BT860-Sx-xx-T/R.

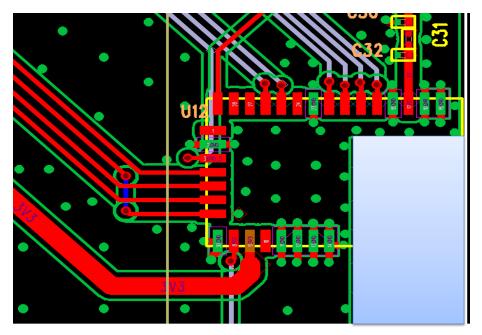

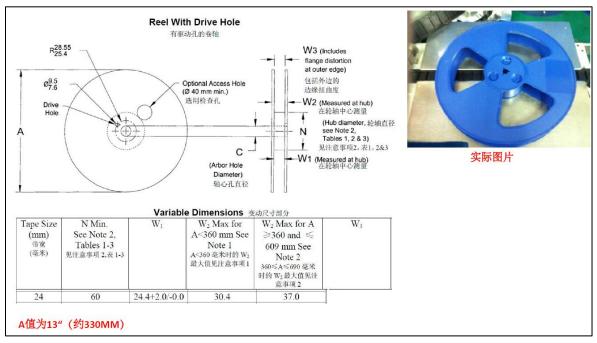

Figure 16: Reel specifications

Figure 17: Tape specifications

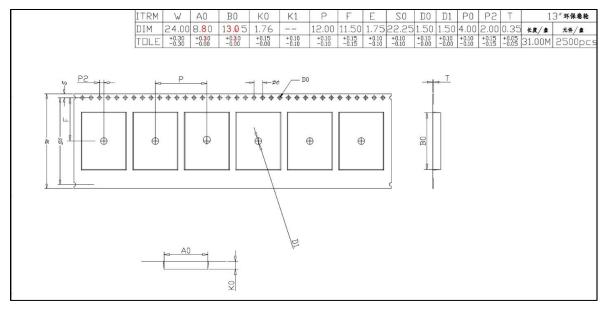

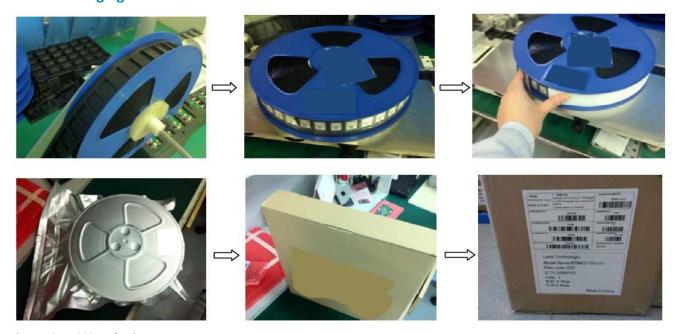

There are 2500 x BT860-Sx modules taped in a reel (and packaged in a pizza box) and five boxes per carton (12,500 modules per carton). Reel, boxes, and carton are labeled with the appropriate labels. See Figure 18.

#### 12.2.2. Packaging Process

Figure 18: BT860 packaging process