Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# BTS4160DGA

Smart High-Side Power Switch

**Automotive Power**

| 1                                                    | Overview 3                                                                                                                                                                                                                                |

|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                    | Block Diagram 5                                                                                                                                                                                                                           |

| 3<br>3.1<br>3.2<br>3.3                               | Pin Configuration 6 Pin Assignment 6 Pin Definitions and Functions 6 Voltage and Current Definition 7                                                                                                                                     |

| <b>4</b> 4.1 4.2 4.3                                 | General Product Characteristics 8 Absolute Maximum Ratings 8 Functional Range 9 Thermal Resistance 9                                                                                                                                      |

| 5<br>5.1<br>5.2<br>5.3<br>5.3.1<br>5.4               | Power Stage 10 Output ON-State Resistance 10 Turn ON / OFF Characteristics 10 Inductive Output Clamp 11 Maximum Load Inductance 12 Electrical Characteristics Power Stage 13                                                              |

| 6<br>6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.5.1<br>6.6 | Protection Mechanisms 14 Loss of Ground Protection 14 Undervoltage Protection 14 Overvoltage Protection 14 Reverse Polarity Protection 15 Overload Protection 15 Current Limitation 15 Electrical Characteristics Protection Functions 17 |

| 7<br>7.1<br>7.2<br>7.2.1<br>7.2.2<br>7.3             | Diagnostic Mechanism 18 ST 0/1 Pin 18 ST0/1 Signal in Case of Failures 18 Diagnostic in Open Load, Channel OFF 18 ST 0/1 Signal in case of Over Temperature 20 Electrical Characteristics Diagnostic Functions 20                         |

| <b>8</b><br>8.1<br>8.2                               | Input Pins 22 Input Circuitry 22 Electrical Characteristics 22                                                                                                                                                                            |

| <b>9</b><br>9.1                                      | <b>Application Information</b> 23 Further Application Information 23                                                                                                                                                                      |

| 10                                                   | Package Outlines 24                                                                                                                                                                                                                       |

| 11                                                   | Revision History 25                                                                                                                                                                                                                       |

Data Sheet 2 Rev. 1.0, 2008-03-18

#### **Smart High-Side Power Switch**

BTS4160DGA

#### **Two Channel Device**

#### 1 Overview

#### **Basic Features**

- Fit for 12V application

- Two Channel Device

- Very low Stand-by Current

- CMOS Compatible Inputs

- Electrostatic Discharge Protection (ESD)

- Optimized Electromagnetic Compatibility

- · Logic ground independent from load ground

- Very low Leakage Current from OUT to the load in OFF state

- Green Product (RoHS compliant)

- AEC Qualified

PG-DSO-14-37

#### **Description**

The BTS4160DGA is a dual channel Smart High-Side Power Switch. It is embedded in a PG-DSO-14-37 package, providing protective functions and diagnostics. The power transistor is built by a N-channel power MOSFET with charge pump. The device is monolithically integrated in Smart technology. It is specially designed to drive relays as well as resistive loads in the harsh automotive environment.

Table 1 Electrical Parameters (short form)

| Parameter                                            | Symbol                | Value                  |

|------------------------------------------------------|-----------------------|------------------------|

| Operating voltage range                              | $V_{SOP}$             | 5.5V 20V               |

| Maximum load per channel                             | $P_{BULB}$            | 2 * R5W, relays or LED |

| Over voltage protection                              | $V_{\rm S(AZ)}$       | 43V                    |

| Max ON State resistance at $T_j$ = 150°C per channel | $R_{DS(ON)}$          | 320m $Ω$               |

| Nominal load current (one channel active)            | $I_{L \text{ (nom)}}$ | 1.8A                   |

| Minimum current limitation                           | $I_{L\_SCR}$          | 6.5A                   |

| Standby current for the whole device with load       | $I_{S(off)}$          | 8μΑ                    |

| Maximum reverse battery voltage                      | $-V_{\rm s(REV)}$     | 16V                    |

#### **Diagnostic Feature**

- · Open load in OFF

- · Feedback of the thermal shutdown in ON state

- · Diagnostic feedback with open drain output

| Туре       | Package      | Marking    |

|------------|--------------|------------|

| BTS4160DGA | PG-DSO-14-37 | BTS4160DGA |

Data Sheet 3 Rev. 1.0, 2008-03-18

Overview

#### **Protection Functions**

- Short circuit protection

- Overload protection

- · Current limitation

- Thermal shutdown

- Overvoltage protection (including load dump) with external resistor

- Loss of ground and loss of  $V_{\rm S}$  protection

- Electrostatic discharge protection (ESD)

#### **Application**

· All types of relays and resistive loads

Data Sheet 4 Rev. 1.0, 2008-03-18

**Block Diagram**

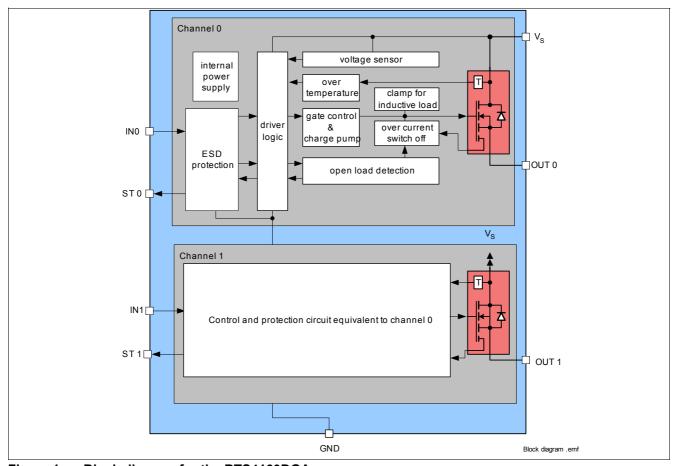

# 2 Block Diagram

Figure 1 Block diagram for the BTS4160DGA

**Pin Configuration**

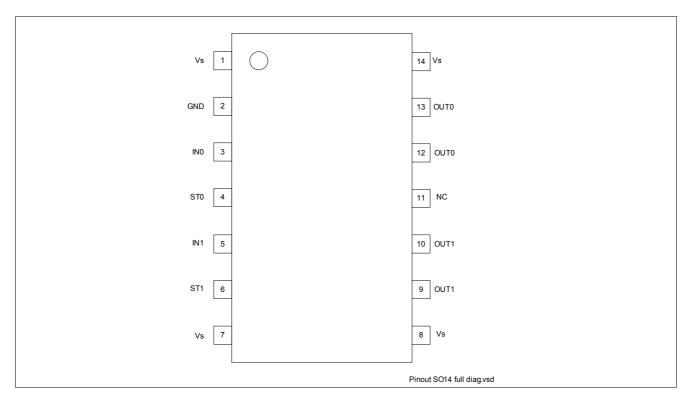

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin Configuration

#### 3.2 Pin Definitions and Functions

| Pin         | Symbol  | Function                                                                          |

|-------------|---------|-----------------------------------------------------------------------------------|

| 2           | GND     | Ground; Ground connection                                                         |

| 3           | IN0     | Input channel 0                                                                   |

|             |         | Input signal for channel 0. Activate the channel in case of logic high level      |

| 4           | ST 0    | Diagnostic feedback; Channel 0. Open drain                                        |

| 5           | IN1     | Input channel 1                                                                   |

|             |         | Input signal for channel 1. Activate the channel in case of logic high level      |

| 6           | ST 1    | Diagnostic feedback; Channel 1. Open drain                                        |

| 9;10        | OUT1    | Output 1; Protected High side power output channel 11)                            |

| 11          | NC      | Not Connected                                                                     |

| 12;13       | OUT0    | Output 0; Protected High side power output channel 01)                            |

| 1, 7, 8, 14 | $V_{S}$ | Battery voltage                                                                   |

|             |         | Design the wiring for the simultaneous max. short circuit currents from channel 0 |

|             |         | and 1 and also for low thermal resistance                                         |

<sup>1)</sup> All output pins of a channel have to be connected together on the PCB.

**Pin Configuration**

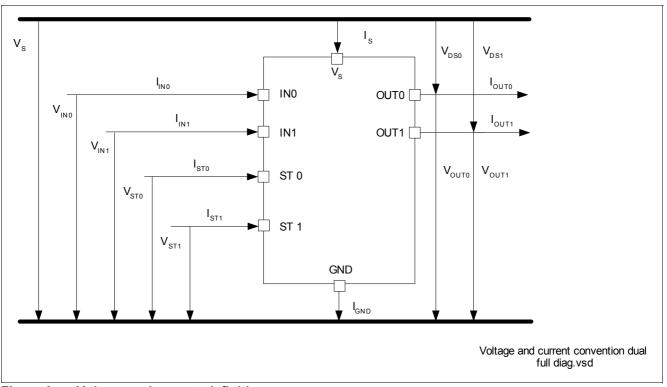

# 3.3 Voltage and Current Definition

Figure 3 shows all terms used in this data sheet, with associated convention for positive values.

Figure 3 Voltage and current definition

**General Product Characteristics**

#### 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

#### Absolute Maximum Ratings 1)

$T_i$  = 25°C; (unless otherwise specified)

| Pos.     | Parameter                                     | Symbol                 | Lin      | nit values          | Unit         | Conditions                                                                                                                                   |

|----------|-----------------------------------------------|------------------------|----------|---------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------|

|          |                                               |                        | Min.     | Max.                |              |                                                                                                                                              |

| Voltage  | s                                             | •                      | <u>'</u> | <u>'</u>            |              |                                                                                                                                              |

| 4.1.1    | Supply voltage                                | $V_{S}$                | -0.3     | 43                  | V            | _                                                                                                                                            |

| 4.1.2    | Reverse polarity Voltage                      | - $V_{\rm S(REV)}$     | 0        | 16                  | V            | _                                                                                                                                            |

| 4.1.3    | Supply voltage for short circuit protection   | $V_{\mathrm{bat(SC)}}$ | 0        | 20                  | V            | $R_{\rm ECU}$ = 20m $\Omega$ , $R_{\rm Cable}$ = 16m $\Omega$ /m $L_{\rm Cable}$ = 1 $\mu$ H/m, $\ell$ = 0 or 5m $^{2}$ see <b>Chapter 6</b> |

| Input pi | ns                                            |                        |          |                     |              |                                                                                                                                              |

| 4.1.4    | Voltage at INPUT pins                         | $V_{IN}$               | -10      | 16                  | V            | _                                                                                                                                            |

| 4.1.5    | Current through INPUT pins                    | $I_{IN}$               | -0.3     | 0.3                 | mA           | _                                                                                                                                            |

| Status p | oin                                           |                        |          |                     |              |                                                                                                                                              |

| 4.1.6    | Current through ST pin                        | I <sub>ST</sub>        | -5       | 5                   | mA           | _                                                                                                                                            |

| Power s  | stage                                         | •                      |          | <u>'</u>            |              |                                                                                                                                              |

| 4.1.7    | Load current                                  | $ I_{L} $              | _        | I <sub>L(LIM)</sub> | Α            | _                                                                                                                                            |

| 4.1.8    | Power dissipation (DC), all channel active    | $P_{TOT}$              | _        | 0.9                 | W            | $T_{\rm A}$ = 85°C,<br>$T_{\rm i}$ <150°C                                                                                                    |

| 4.1.9    | Maximum Switchable inductance, single pulse   | $E_{AS}$               | _        | 65                  | mJ           | $I_{\rm L}$ = 2.9A,<br>$V_{\rm S}$ = 12V                                                                                                     |

| Temper   | atures                                        |                        | -        |                     | <del>'</del> | -                                                                                                                                            |

| 4.1.10   | Junction Temperature                          | $T_{\rm j}$            | -40      | 150                 | °C           | _                                                                                                                                            |

| 4.1.11   | Dynamic temperature increase while switching  | $\Delta T_{\rm j}$     | _        | 60                  | K            | _                                                                                                                                            |

| 4.1.12   | Storage Temperature                           | $T_{\mathrm{stg}}$     | -55      | 150                 | °C           | _                                                                                                                                            |

| ESD Su   | sceptibility                                  | 19                     |          |                     |              | +                                                                                                                                            |

| 4.1.13   | ESD Resistivity IN pin                        | $V_{ESD}$              | -1       | 1                   | kV           | HBM <sup>3)</sup>                                                                                                                            |

| 4.1.14   | ESD Resistivity ST pin                        | $V_{ESD}$              | -4       | 4                   | kV           | HBM <sup>3)</sup>                                                                                                                            |

| 4.1.15   | ESD Resistivity OUT to all other pins shorted | $V_{ESD}$              | -5       | 5                   | kV           | HBM <sup>3)</sup>                                                                                                                            |

|          | *                                             | •                      | •        |                     |              | •                                                                                                                                            |

<sup>1)</sup> Not subject to production test, specified by design

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2)</sup> Set up in accordance to AEC Q100-012 and AEC Q101-006

<sup>3)</sup> ESD susceptibility HBM according to EIA/JESD 22-A 114B

#### **General Product Characteristics**

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### 4.2 Functional Range

| Pos.  | Parameter                                                | Symbol       | Liı  | mit values   | Unit | Conditions                                                                                                                                               |

|-------|----------------------------------------------------------|--------------|------|--------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                          |              | Min. | Max.         |      |                                                                                                                                                          |

| 4.2.1 | Operating Voltage                                        | $V_{SOP}$    | 5.5  | 20           | V    | $V_{\rm IN}$ = 4.5V, $R_{\rm L}$ = 12 $\Omega$ , $V_{\rm DS}$ < 0.5V                                                                                     |

| 4.2.2 | Undervoltage switch OFF                                  | $V_{SUV}$    | -    | 4.5          | V    | $T_{\rm j}$ = -40°C,<br>$V_{\rm DS}$ < 0.5V                                                                                                              |

| 4.2.3 | Operating current One channel active Two channels active | $I_{GND}$    |      | 0.9<br>1.7   | mA   | V <sub>IN</sub> = 5V                                                                                                                                     |

| 4.2.4 | Standby current for whole device with load               | $I_{S(OFF)}$ | -    | 8<br>8<br>12 | μΑ   | $T_{\rm j}$ = 25°C<br>$T_{\rm j}$ = 85°C <sup>1)</sup><br>$T_{\rm j}$ = 150°C,<br>$V_{\rm s}$ = 12V,<br>$R_{\rm L}$ = 12 $\Omega$ ,<br>$V_{\rm IN}$ = 0V |

<sup>1)</sup> Not subject to production test. Specified by design

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

#### 4.3 Thermal Resistance

| Pos.  | Parameter                                                 | Symbol               | Limit values |          |      | Unit | Conditions                           |

|-------|-----------------------------------------------------------|----------------------|--------------|----------|------|------|--------------------------------------|

|       |                                                           |                      | Min.         | Тур.     | Max. |      |                                      |

| 4.3.1 | Junction to Soldering Point each channel                  | $R_{\mathrm{thJSP}}$ | -            | _        | 15   | K/W  | _1)                                  |

| 4.3.2 | Junction to Ambient One channel active Two channel active | $R_{thJA}$           | _<br>_       | 70<br>45 | -    | K/W  | with 6cm² cooling area <sup>1)</sup> |

<sup>1)</sup> Not subject to production test, specified by design

# 5 Power Stage

The power stages are built by an N-channel vertical power MOSFET (DMOS) with charge pump.

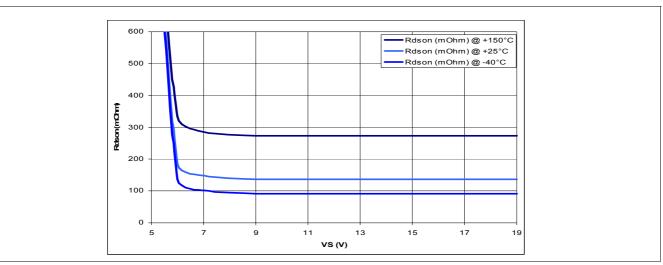

#### 5.1 Output ON-State Resistance

The ON-state resistance  $R_{\rm DS(ON)}$  depends on the supply voltage as well as the junction temperature T<sub>j</sub>. **Figure 4** shows the dependencies for the typical ON-state resistance. The behavior in reverse polarity is described in **Chapter 6.4**.

Figure 4 Typical ON-State Resistance

A high signal (See **Chapter 8**) at the input pin causes the power DMOS to switch ON with a dedicated slope, which is optimized in terms of EMC emission.

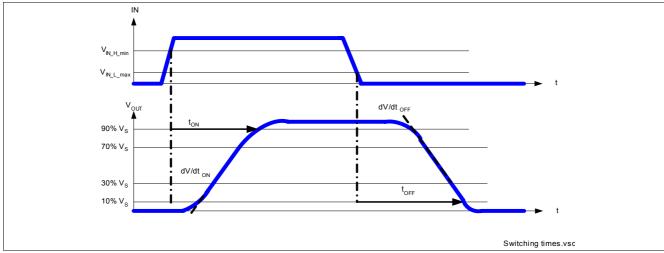

#### 5.2 Turn ON / OFF Characteristics

Figure 5 shows the typical timing when switching a resistive load.

Figure 5 Turn ON/OFF (resistive) timing

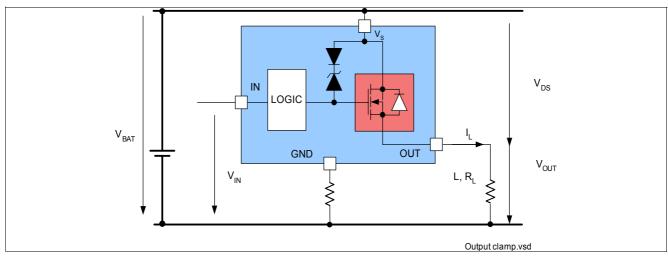

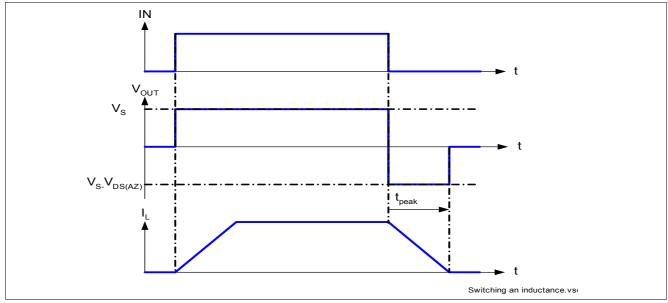

#### 5.3 Inductive Output Clamp

When switching OFF inductive loads with high side switches, the voltage  $V_{\rm OUT}$  drops below ground potential, because the inductance intends to continue driving the current. To prevent the destruction of the device due to high voltages, there is a voltage clamp mechanism implemented that keeps the negative output voltage at a certain level ( $V_{\rm S}$ - $V_{\rm DS(AZ)}$ ). Please refers to **Figure 6** and **Figure 7** for details. Nevertheless, the maximum allowed load inductance is limited.

Figure 6 Output clamp (OUT0 and OUT1)

Figure 7 Switching an inductance

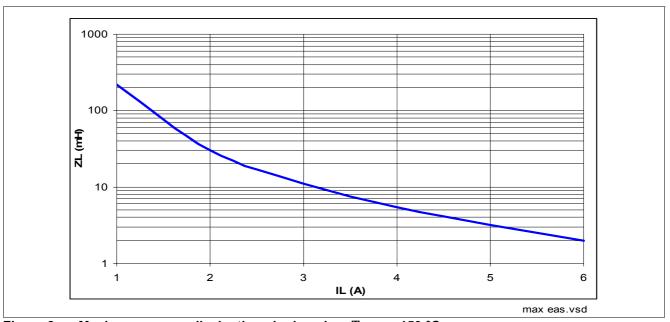

#### 5.3.1 Maximum Load Inductance

During demagnetization of inductive loads, energy has to be dissipated in the BTS4160DGA. This energy can be calculated with following equation:

$$E = V_{DS(AZ)} \times \frac{L}{R_L} \times \left[ \frac{V_S - V_{DS(AZ)}}{R_L} \times ln \left( 1 - \frac{R_L \times I_L}{V_S - V_{DS(AZ)}} \right) + I_L \right]$$

Following equation simplifies under the assumption of  $R_L = 0\Omega$ .

$$E = \frac{1}{2} \times L \times I^{2} \times \left(1 - \frac{V_{S}}{V_{S} - V_{DS(AZ)}}\right)$$

The energy, which is converted into heat, is limited by the thermal design of the component. See **Figure 8** for the maximum allowed inductivity.

Figure 8 Maximum energy dissipation single pulse,  $T_{i,Start}$  = 150 °C

# 5.4 Electrical Characteristics Power Stage

#### **Electrical Characteristics: Power Stage**

$V_{\rm S}$  = 12 V,  $T_{\rm j}$  = -40 °C to +150 °C. Typical values are given at  $T_{\rm j}$  = 25°C

| Pos.  | Parameter                                                                       | Symbol             | Limit values |        |        | Unit | Conditions                                                                              |

|-------|---------------------------------------------------------------------------------|--------------------|--------------|--------|--------|------|-----------------------------------------------------------------------------------------|

|       |                                                                                 |                    | Min.         | Тур.   | Max.   |      |                                                                                         |

| 5.4.1 | ON-State Resistance per channel                                                 | $R_{DS(ON)}$       | _            | 160    | -      | mΩ   | $I_{L}$ = 2A,<br>$V_{IN}$ = 5V,<br>$T_{j}$ = 25°C,<br>See <b>Figure 4</b> <sup>1)</sup> |

|       |                                                                                 |                    | _            | 260    | 320    |      | $T_{\rm j}$ = 150°C.                                                                    |

| 5.4.2 | Nominal load current per channel One channel active Two channel active          | $I_{L(nom)}$       | 1.7<br>1.2   | _<br>_ | _<br>_ | A    | $T_{\rm A}$ = 85°C <sup>1)</sup> ,<br>$T_{\rm j}$ <150°C.                               |

| 5.4.3 | Drain to source clamping voltage $V_{\rm DS(AZ)}$ = $V_{\rm S}$ - $V_{\rm OUT}$ | $V_{DS(AZ)}$       | 41           | 47     | 52     | V    | $I_{\rm DS}$ = 40mA <sup>2)</sup>                                                       |

| 5.4.4 | Output leakage current per channel                                              | $I_{L(OFF)}$       | _            | 1      | 5      | μΑ   | $V_{\text{IN}} = 0\text{V},$<br>$V_{\text{OUT}} = 0\text{V}.$                           |

| 5.4.5 | Slew rate ON 10% to 30% $V_{\rm S}$                                             | $dV/dt_{ON}$       | 0.2          | _      | 1      | V/µs | $R_{L}$ =12 $\Omega$ , $V_{S}$ =12 $V$ .                                                |

| 5.4.6 | Slew rate OFF 70% to 40% $V_{\rm S}$                                            | -d $V/dt_{ m OFF}$ | 0.2          | -      | 1.1    | V/µs | See Figure 5                                                                            |

| 5.4.7 | Turn-ON time to 90% $V_{\rm S}$ Includes propagation delay                      | t <sub>ON</sub>    | _            | 100    | 250    | μs   |                                                                                         |

| 5.4.8 | Turn-OFF time to 10% $V_{\rm S}$ Includes propagation delay                     | $t_{OFF}$          | -            | 100    | 270    | μs   |                                                                                         |

<sup>1)</sup> Not subject to production test, specified by design

<sup>2)</sup> Voltage is measured by forcing  $I_{\rm DS.}$

#### 6 Protection Mechanisms

The device provides embedded protective functions. Integrated protection functions are designed to prevent the destruction of the IC from fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are designed for neither continuous nor repetitive operation.

#### 6.1 Loss of Ground Protection

In case of loss of the module ground, where the load remains connected to ground, the device protects itself by automatically turning OFF (when it was previously ON) or remains OFF, regardless of the voltage applied on IN pins. In that case, a maximum  $I_{(\text{OUTGND})}$  can flow out of the output.

#### 6.2 Undervoltage Protection

Below  $V_{\rm SOP\_min,}$ , the under voltage mechanism is met. If the supply voltage is below the under voltage mechanism, the device is OFF (turns OFF). As soon as the supply voltage is above the under voltage mechanism, then the device can be switched ON and the protection functions are operational.

#### 6.3 Overvoltage Protection

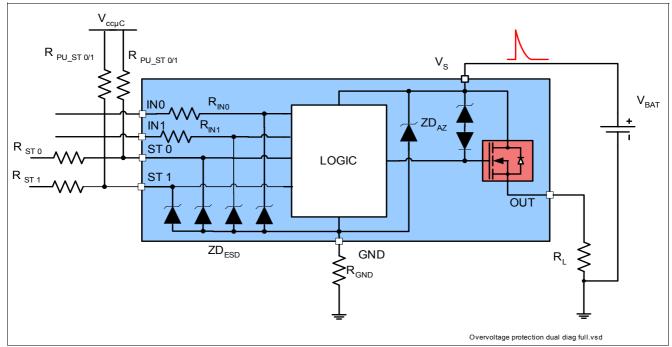

There is a clamp mechanism for over voltage protection. To guarantee this mechanism operates properly in the application, the current in the zener diode  $ZD_{AZ}$  has to be limited by a ground resistor. **Figure 9** shows a typical application to withstand overvoltage issues. In case of supply greater than  $V_{S(AZ)}$ , the power transistor switches ON and the voltage across logic section is clamped. As a result, the internal ground potential rises to  $V_S - V_{S(AZ)}$ . Due to the ESD zener diodes, the potential at pins IN and ST 0/1 rises almost to that potential, depending on the impedance of the connected circuitry. Integrated resistors are provided at the IN pins to protect the input circuitry from excessive current flow during this condition but an external resistor must be provided at the ST0/1 pins.

Figure 9 Over voltage protection with external components

In the case the supply voltage is in between of  $V_{\rm S(SC)\ max}$  and  $V_{\rm DS(AZ)}$ , the output transistor is still operational and follow the input. If at least one channel is in ON state, parameters are no longer warranted and lifetime is reduced compared to normal mode. This specially impacts the short circuit robustness, as well as the maximum energy  $E_{\rm AS}$  the device can handle.

Data Sheet 14 Rev. 1.0, 2008-03-18

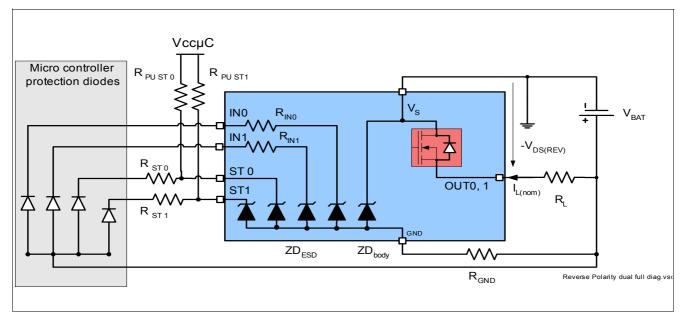

#### 6.4 Reverse Polarity Protection

In case of reverse polarity, the intrinsic body diode causes power dissipation. The current in this intrinsic body diode is limited by the load itself. Additionally, the current into the ground path and the logical pins has to be limited to the maximum current described in **Chapter 4.1**, sometimes with an external resistor. **Figure 10** shows a typical application. The  $R_{\rm GND}$  resistor is used to limit the current in the zener protection of the device. Resistors  $R_{\rm IN}$  and  $R_{\rm ST}$  are used to limit the current in the logic of the device and in the ESD protection stage. The recommended value for  $R_{\rm GND}$  is  $150\Omega$ , for  $R_{\rm ST~0/1}$  =  $15k\Omega$ . In case the over voltage is not considered in the application,  $R_{\rm GND}$  can be replaced by a Shottky diode.

Figure 10 Reverse polarity protection with external components

#### 6.5 Overload Protection

In case of overload, or short circuit to ground, the BTS4160DGA offers several protections mechanisms.

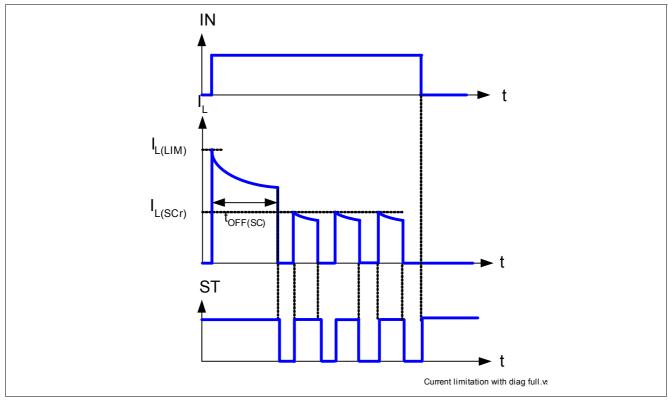

#### 6.5.1 Current Limitation

At first step, the instantaneous power in the switch is maintained to a safe level by limiting the current to the maximum current allowed in the switch  $I_{\text{L(LIM)}}$ . During this time, the DMOS temperature is increasing, which affects the current flowing in the DMOS. At thermal shutdown, the device turns OFF and cools down. A restart mechanism is used, after cooling down, the device restarts and limits the current to  $I_{\text{L(SCR)}}$ . **Figure 11** shows the behavior of the current limitation as a function of time.

Figure 11 Current limitation function of the time

#### 6.6 Electrical Characteristics Protection Functions

**Electrical Characteristics: Protection**

$V_{\rm S}$  = 12 V,  $T_{\rm j}$  = -40 °C to +150 °C. Typical values are given at  $T_{\rm j}$  = 25°C

| Pos.   | Parameter                                          | Symbol                           | Limit values |             |                | Unit | Conditions                                                                            |

|--------|----------------------------------------------------|----------------------------------|--------------|-------------|----------------|------|---------------------------------------------------------------------------------------|

|        |                                                    |                                  | Min.         | Тур.        | Max.           |      |                                                                                       |

| Loss o | of ground                                          | 11                               |              |             |                |      |                                                                                       |

| 6.6.1  | Output leakage current while GND disconnected      | $I_{\mathrm{OUT}(\mathrm{GND})}$ | 0            | _           | 2              | mA   | GND disconnected                                                                      |

| Revers | se polarity                                        | +                                | +            |             | <del>-  </del> | -    |                                                                                       |

| 6.6.2  | Drain source diode voltage during reverse polarity | $-V_{\mathrm{DS(REV)}}$          | _            | 600         | _              | mV   | $I_{L}$ = -2A,<br>$V_{S}$ = 12V,<br>$V_{IN}$ = 0V,<br>$T_{j}$ = 150°C <sup>1)</sup> . |

| Overvo | oltage                                             | 1                                |              | 1           |                |      |                                                                                       |

| 6.6.3  | Over voltage protection                            | $V_{S(AZ)}$                      | 41           | 47          | 52             | V    | $I_{\rm s}$ = 40mA                                                                    |

| Overlo | ad condition                                       |                                  |              |             |                |      |                                                                                       |

| 6.6.4  | Load current limitation                            | $I_{L(LIM)}$                     | -<br>-<br>5  | -<br>9<br>- | 14<br>-<br>-   | A    | $T_{\rm j}$ = -40°C,<br>$T_{\rm j}$ = 25°C,<br>$T_{\rm j}$ = 150°C.                   |

| 6.6.5  | Repetitive short circuit current limitation        | $I_{L(SCR)}$                     | -            | 6.5         | _              | Α    | One channel <sup>1)</sup>                                                             |

| 6.6.6  | Thermal shutdown temperature                       | $T_{jSC}$                        | 150          | _           | _              | °C   | _1)                                                                                   |

| 6.6.7  | Thermal shutdown hysteresis                        | $\Delta T_{JT}$                  | _            | 10          | _              | K    | _ 1)                                                                                  |

<sup>1)</sup> Not subject to production test, but specified by design

## 7 Diagnostic Mechanism

For diagnosis purpose, the BTS4160DGA provides a status pin per channel.

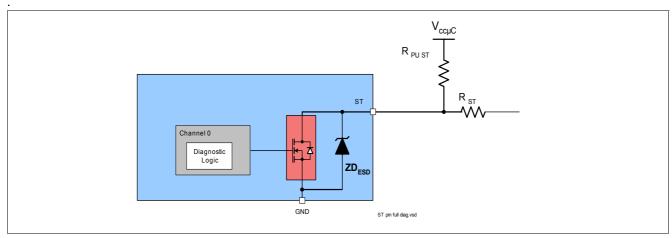

#### 7.1 ST 0/1 Pin

BTS4160DGA status pins are an open drain, active low circuit. **Figure 12** shows the equivalent circuitry. As long as no "hard" failure mode occurs (Short circuit to GND / Over temperature or open load in OFF), the signal is permanently high, and due to a required external pull-up to the logic voltage will exhibit a logic high in the application. A suggested value for the  $R_{\rm PU,ST01}$  is  $15 {\rm k}\Omega$ .

Figure 12 Status output circuitry

#### 7.2 ST0/1 Signal in Case of Failures

Table 3 gives a guick reference for the logical state of the ST 0/1 pins during device operation.

Table 3 ST Pin truth table

| Device operation  | IN | OUT                 | ST              |

|-------------------|----|---------------------|-----------------|

| Normal operation  | L  | L                   | Н               |

|                   | Н  | Н                   | Н               |

| Open Load channel | L  | > V <sub>(OL)</sub> | L <sup>1)</sup> |

|                   | Н  | Н                   | Н               |

| Over temp channel | L  | L                   | Н               |

|                   | Н  | L                   | L               |

<sup>1)</sup>L if potential at the output exceeds the Openload detection voltage

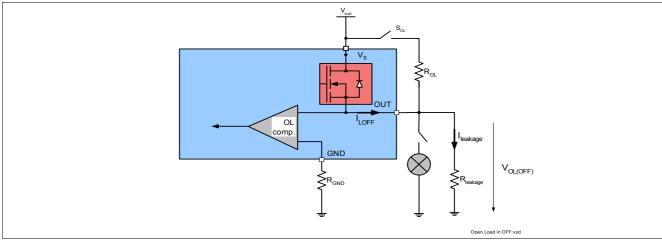

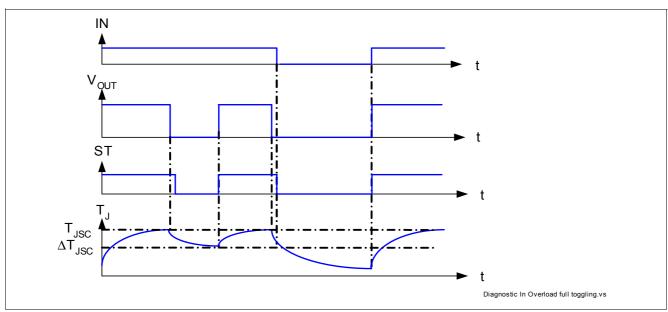

#### 7.2.1 Diagnostic in Open Load, Channel OFF

For open load diagnosis in OFF-state, an external output pull-up resistor ( $R_{\rm OL}$ ) is recommended. For calculation of the pull-up resistor value, the leakage currents and the open load threshold voltage  $V_{\rm OL(OFF)}$  has to be taken into account. Figure 13 gives a sketch of the situation and Figure 14 shows the typical timing diagram.

$I_{\rm leakage}$  defines the leakage current in the complete system, including  $I_{\rm L(OFF)}$  (see **Chapter 5.4**) and external leakages e.g. due to humidity, corrosion, etc... in the application.

To reduce the stand-by current of the system, an open load resistor switch  $S_{\mathrm{OL}}$  is recommended.

If the channel is OFF, the output is no longer pulled down by the load and  $V_{\rm OL}$  voltage rises to nearly  $V_{\rm S}$ . This is recognized by the device as open load. The voltage threshold is given by  $V_{\rm OL(OFF)}$ . In that case, the ST 0/1 signal is switched to a logical low  $V_{\rm ST01(L)}$ .

Figure 13 Open load detection in OFF electrical equivalent circuit

Figure 14 ST 0/1 in open load condition

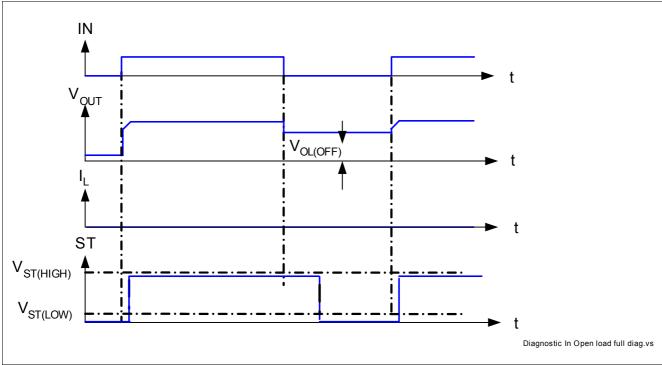

## 7.2.2 ST 0/1 Signal in case of Over Temperature

In case of over temperature, the junction temperature reaches the thermal shutdown temperature  $T_{\rm jSC}$ . In that case, the ST 0/1 signal is toggling between  $V_{\rm ST01(L)}$  and  $V_{\rm ST01(H)}$ . Figure 15 gives a sketch of the situation.

Figure 15 Sense signal in overtemperature condition

#### 7.3 Electrical Characteristics Diagnostic Functions

#### **Electrical Characteristics: Diagnostics**

$V_{\rm S}$  = 12 V,  $T_{\rm i}$  = -40 °C to +150 °C. Typical values are given at  $T_{\rm i}$  = 25 °C

| Pos.   | Parameter                                                     | Symbol                   | Limit values |      | ues  | Unit | Conditions                                                     |

|--------|---------------------------------------------------------------|--------------------------|--------------|------|------|------|----------------------------------------------------------------|

|        |                                                               |                          | Min.         | Тур. | Max. |      |                                                                |

| Load o | condition threshold for diagnosti                             | С                        |              |      |      |      |                                                                |

| 7.3.1  | Open Load detection threshold in OFF state                    | $V_{OL(OFF)}$            | 1.7          | 2.8  | 4.0  | V    | -                                                              |

| ST 0/1 | pin                                                           |                          |              |      |      |      |                                                                |

| 7.3.2  | Status output (open drain)<br>High level; Zener limit voltage | V <sub>ST (HIGH)</sub>   | 5.4          | _    | _    | V    | I <sub>ST</sub> =+1.6mA <sup>1)</sup> ,<br>Zener Limit voltage |

| 7.3.3  | Status output (open drain)<br>Low level                       | $V_{\rm ST  (LOW)}$      | _            | _    | 0.6  | V    | $I_{\rm ST}$ =+1.6mA <sup>1)</sup>                             |

| Diagno | ostic timing                                                  |                          |              |      |      |      |                                                                |

| 7.3.4  | Status change after positive input slope with open load       | $t_{\rm dST(ON\_OL)}$    | _            | 10   | 20   | μs   | _2)                                                            |

| 7.3.5  | Status change after positive input slope with overload        | t <sub>dST(ON_OvL)</sub> | 30           | _    | _    | μs   | _2)                                                            |

#### **Electrical Characteristics: Diagnostics** (cont'd)

$V_{\rm S}$  = 12 V,  $T_{\rm j}$  = -40 °C to +150 °C. Typical values are given at T $_{\rm j}$  = 25°C

| Pos.  | Parameter                                               | Symbol                 | Limit values |      |      | Unit | Conditions |

|-------|---------------------------------------------------------|------------------------|--------------|------|------|------|------------|

|       |                                                         |                        | Min.         | Тур. | Max. |      |            |

| 7.3.6 | Status change after negative input slope with open load | $t_{ m dST(OFF\_OL)}$  | _            | -    | 500  | μs   | _          |

| 7.3.7 | Status change after negative input slope with overload  | $t_{ m dST(OFF\_OvL)}$ | _            | _    | 20   | μs   | _2)        |

<sup>1)</sup> If ground resistor R<sub>GND</sub> is used, the voltage drop across this resistor has to be added

<sup>2)</sup> Not subject to production test, specified by design

**Input Pins**

# 8 Input Pins

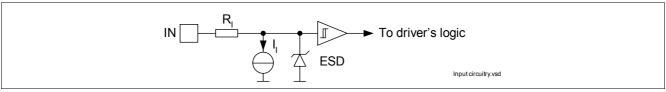

### 8.1 Input Circuitry

The input circuitry is CMOS compatible. The concept of the Input pin is to react to voltage transition and not to voltage threshold. With the Schmidt trigger, it is impossible to have the device in an un-defined state, if the voltage on the input pin is slowly increasing or decreasing. The output is either OFF or ON but cannot be in an linear or undefined state. The input circuitry is compatible with PWM applications. **Figure 16** shows the electrical equivalent input circuitry. The pull down current source ensures the channel is OFF with a floating input.

Figure 16 Input pin circuitry

#### 8.2 Electrical Characteristics

#### **Electrical Characteristics: Diagnostics**

$V_{\rm S}$  = 12 V,  $T_{\rm j}$  = -40 °C to +150 °C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified) Typical values are given at  $T_{\rm i}$  = 25°C

| Pos.    | Parameter                | Symbol        | Limit values |      |          | Unit | Conditions      |

|---------|--------------------------|---------------|--------------|------|----------|------|-----------------|

|         |                          |               | Min.         | Тур. | Max.     |      |                 |

| INput p | oins characteristics     | <u>'</u>      | - 1          |      | <u> </u> |      | 1               |

| 8.2.1   | Low level input voltage  | $V_{IN(L)}$   | _            | _    | 1        | V    | _1)             |

| 8.2.2   | High level input voltage | $V_{IN(H)}$   | 2.5          | _    | _        | V    | 1)              |

| 8.2.3   | Input voltage hysteresis | $V_{IN(HYS)}$ | _            | 0.2  | _        | V    | _2)             |

| 8.2.4   | Low level input current  | $I_{IN(L)}$   | 5            | _    | 20       | μΑ   | $V_{IN} = 0.4V$ |

| 8.2.5   | High level input current | $I_{IN(H)}$   | 10           | _    | 60       | μA   | $V_{IN}$ = 5V   |

| 8.2.6   | Input resistance         | $R_{I}$       | 2.5          | 4    | 6        | kΩ   | See Figure 16   |

<sup>1)</sup> If ground resistor  $R_{\mathrm{GND}}$  is used, the voltage drop across this resistor has to be added

<sup>2)</sup> Not subject to production test, specified by design

**Application Information**

# 9 Application Information

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

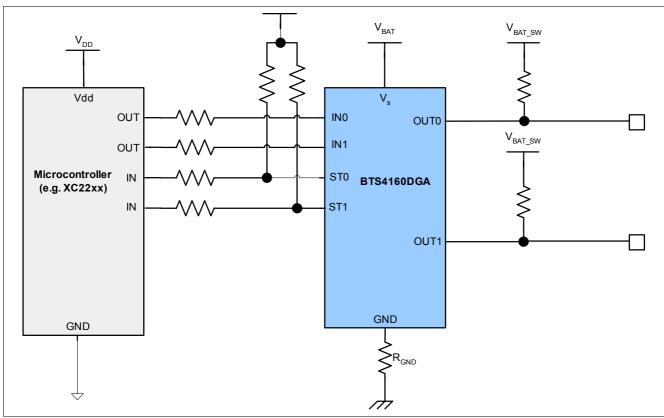

Figure 17 Application diagram with BTS4160DGA

Note: This is a very simplified example of an application circuit. The function must be verified in the real application.

#### 9.1 Further Application Information

For further information you may visit <a href="http://www.infineon.com/">http://www.infineon.com/</a>

**Package Outlines**

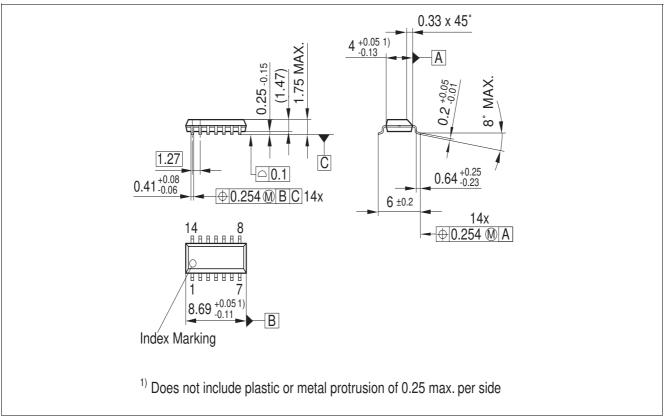

## 10 Package Outlines

Figure 18 PG-DSO-14-37 (Plastic Dual Small Outline Package)

#### **Green Product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

**Revision History**

# 11 Revision History

| Version | Date       | Changes                    |

|---------|------------|----------------------------|

| 1.0     | 2008-03-18 | Creation of the data sheet |