Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **Smart High-Side Power Switch**

## 1 Overview

#### **Features**

- One channel device

- Low Stand-by current

- 3.3 V to V<sub>s</sub> level capable input pin

- Electrostatic discharge protection (ESD)

- Optimized Electromagnetic Compatibility (EMC)

- · Logic ground independent from load ground

- · Very low leakage current at OUT pin

- Compatible to cranking pulse requirement (test pulse 4 of ISO 7637 and cold start pulse in LV124)

- · Embedded diagnostic functions

- · Embedded protection functions

- Green Product (RoHS compliant)

- · AEC Qualified

#### **Applications**

- Suitable for resistive, inductive and capacitive loads

- Replaces electromechanical relays, fuses and discrete circuits

- Most suitable for applications with high current loads, such as heating system, main switch for power distribution, start-stop power supply switch

- PWM applications with low frequencies

#### **Description**

The BTS50015-1TAD is a 1.5 m $\Omega$  single channel Smart High-Side Power Switch, embedded in a PG-TO-263-7-10 package, providing protective functions and diagnosis. It contains Infineon ReverSave functionality. The power transistor is built by a N-channel power MOSFET with charge pump. It is specially designed to drive high current loads up to 80 A, for applications like switched battery couplings, power distribution switches, heaters, glow plugs, in the harsh automotive environment.

1

## **Smart High-Side Power Switch**

#### **Overview**

#### **Table 1** Product Summary

| Parameter                                                                           | Symbol                | Values     |

|-------------------------------------------------------------------------------------|-----------------------|------------|

| Operating voltage range                                                             | $V_{S(OP)}$           | 8 V 18 V   |

| Extended supply voltage including dynamic undervoltage capability                   | $V_{S(DYN)}$          | 3.2 V 28 V |

| Maximum ON-state resistance ( $T_J = 150$ °C)                                       | R <sub>DS(ON)</sub>   | 3 mΩ       |

| Minimum nominal load current (T <sub>A</sub> = 85°C)                                | I <sub>L(NOM)</sub>   | 33 A       |

| Typical current sense differential ratio                                            | $dk_{ILIS}$           | 51500      |

| Minimum short circuit current threshold                                             | I <sub>CL(0)</sub>    | 135 A      |

| Maximum stand-by current for the whole device with load $(T_A = T_J = 85^{\circ}C)$ | I <sub>VS (OFF)</sub> | 18 μΑ      |

| Maximum reverse battery voltage ( $T_A = 25^{\circ}\text{C for 2 min}$ )            | -V <sub>S(REV)</sub>  | 16 V       |

#### **Embedded Diagnostic Functions**

- · Proportional load current sense

- Short circuit / Overtemperature detection

- Latched status signal after short circuit or overtemperature detection

#### **Embedded Protection Functions**

- Infineon® ReverSave™: Reverse battery protection by self turn ON of power MOSFET

- Infineon® Inversave: Inverse operation robustness capability

- · Secure load turn-OFF while device loss of GND connection

- Overtemperature protection with latch

- Short circuit protection with latch

- · Overvoltage protection with external components

- Enhanced short circuit operation

- Infineon® SMART CLAMPING

| Туре          | Package        | Marking         |

|---------------|----------------|-----------------|

| BTS50015-1TAD | PG-TO-263-7-10 | <u>S</u> 50015D |

# BTS50015-1TAD Smart High-Side Power Switch

# **Table of Contents**

| 1                | Overview                                                                      | 1  |

|------------------|-------------------------------------------------------------------------------|----|

|                  | Table of Contents                                                             | 3  |

|                  | List of Tables                                                                | 5  |

|                  | List of Figures                                                               | 6  |

| 2                | Block Diagram                                                                 | 7  |

| 3                | Pin Configuration                                                             | 8  |

| 3.1              | Pin Assignment                                                                | 8  |

| 3.2              | Pin Definitions and Functions                                                 | 8  |

| 3.3              | Voltage and Current Definition                                                | 9  |

| 4                | General Product Characteristics                                               | 10 |

| 4.1              | Absolute Maximum Ratings                                                      | 10 |

| 4.2              | Functional Range                                                              | 14 |

| 4.3              | Thermal Resistance                                                            | 15 |

| 5                | Functional Description                                                        | 16 |

| 5.1              | Power Stage                                                                   | 16 |

| 5.1.1            | Output ON-State Resistance                                                    | 16 |

| 5.1.2            | Switching Resistive Loads                                                     | 16 |

| 5.1.3            | Switching Inductive Loads                                                     | 16 |

| 5.1.3.1          | Output Clamping                                                               | 16 |

| 5.1.3.2          | Maximum Load Inductance                                                       | 17 |

| 5.1.4            | Switching Active Loads                                                        |    |

| 5.1.5            | Inverse Current Capability                                                    |    |

| 5.1.6            | PWM Switching                                                                 |    |

| 5.1.7            | Advanced switch-off behavior                                                  |    |

| 5.2              | Input Pins                                                                    |    |

| 5.2.1            | Input Circuitry                                                               |    |

| 5.2.2            | Input Pin Voltage                                                             |    |

| 5.3              | Protection Functions                                                          |    |

| 5.3.1            | Loss of Ground Protection                                                     |    |

| 5.3.2            | Protection during Loss of Load or Loss of $V_s$ Condition                     |    |

| 5.3.3            | Undervoltage Behavior                                                         |    |

| 5.3.4            | Overvoltage Protection                                                        |    |

| 5.3.5            | Reverse Polarity Protection                                                   |    |

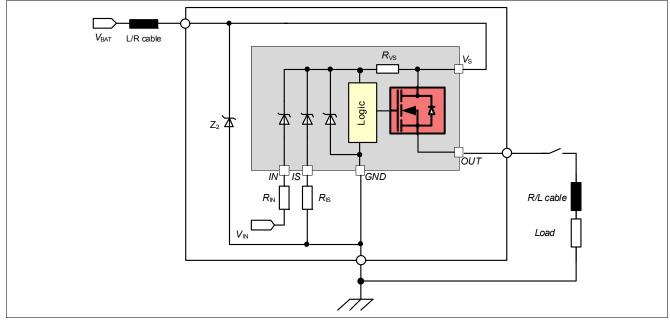

| 5.3.6<br>5.3.6.1 | Activation of the Switch into Short Circuit (Short Circuit Type 1)            |    |

| 5.3.6.2          | Short Circuit Appearance when the Device is already ON (Short Circuit Type 2) |    |

| 5.3.6.3          | Influence of the battery wire inductance                                      |    |

| 5.3.7            | Temperature Limitation in the Power DMOS                                      |    |

| 5.4              | Diagnostic Functions                                                          |    |

| 5.4.1            | IS Pin                                                                        |    |

| 5.4.2            | SENSE Signal in Different Operation Modes                                     |    |

| 5.4.3            | SENSE Signal in the Nominal Current Range                                     |    |

| 5.4.3.1          | SENSE Signal Variation and Calibration                                        |    |

| 5.4.3.2          | SENSE Signal Timing                                                           |    |

|                  | G                                                                             |    |

# **Smart High-Side Power Switch**

| 0       | Pavician History                         | EΛ |

|---------|------------------------------------------|----|

| 8       | Package Outlines                         | 49 |

| 7.1     | Further Application Information          | 48 |

| 7       | Application Information                  | 47 |

| 6.2     | Typical Performance Characteristics      | 41 |

| 6.1     | Electrical Characteristics Table         | 35 |

| 6       | Electrical Characteristics BTS50015-1TAD | 35 |

| 5.4.3.4 | SENSE Signal in Case of Over Load        | 34 |

| 5.4.3.3 |                                          | 34 |

# **Smart High-Side Power Switch**

# **List of Tables**

| Table 1 | Product Summary                           |    |

|---------|-------------------------------------------|----|

| Table 2 | Absolute Maximum Ratings                  |    |

| Table 3 | Functional Range                          |    |

| Table 4 | Thermal Resistance                        |    |

| Table 5 | Sense Signal, Function of Operation Mode  | 30 |

| Table 6 | Electrical Characteristics: BTS50015-1TAD | 35 |

| Table 7 | Bill of material                          | 48 |

5

# **Smart High-Side Power Switch**

# **List of Figures**

| Figure 1  | Block Diagram for the BTS50015-1TAD                                                                         | 7    |

|-----------|-------------------------------------------------------------------------------------------------------------|------|

| Figure 2  | Pin Configuration                                                                                           | 8    |

| Figure 3  | Voltage and Current Definition                                                                              | 9    |

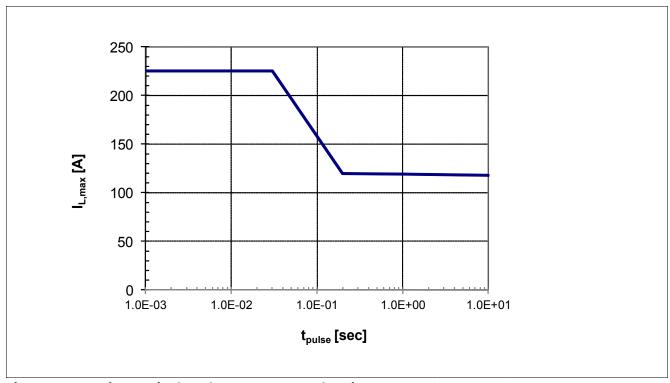

| Figure 4  | Maximum Single Pulse Current vs. Pulse Time, $T_J \le 150^{\circ}\text{C}$ , $T_{PIN} = 85^{\circ}\text{C}$ | . 12 |

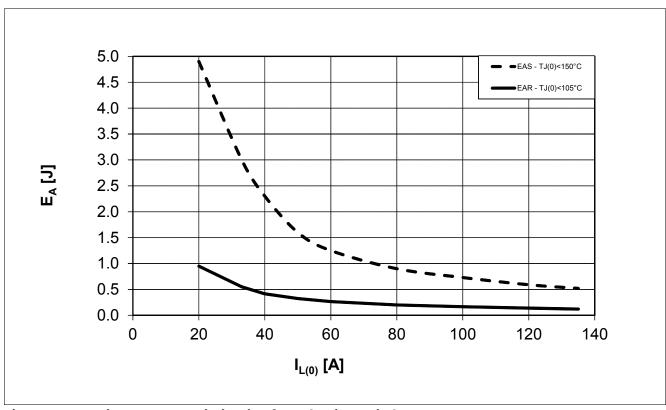

| Figure 5  | Maximum Energy Dissipation for Inductive Switch OFF, $E_A$ vs. $I_L$ at $V_S = 13.5 \text{ V}$              | . 13 |

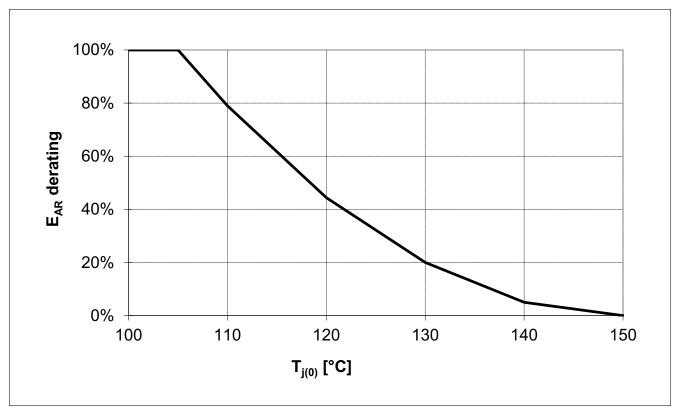

| Figure 6  | Maximum Energy Dissipation Repetitive Pulse temperature derating                                            | . 13 |

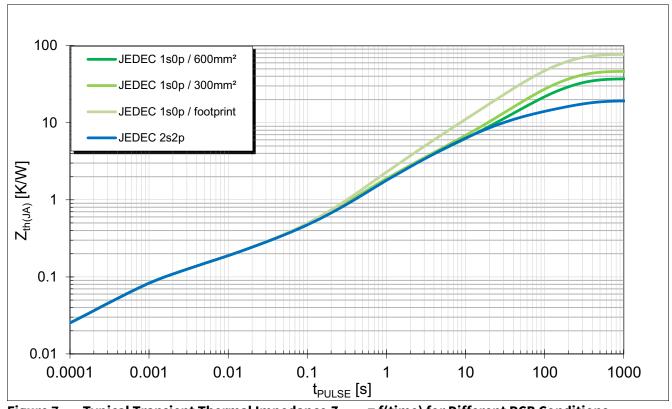

| Figure 7  | Typical Transient Thermal Impedance $Z_{th(JA)} = f(time)$ for Different PCB Conditions                     | . 15 |

| Figure 8  | Switching a Resistive Load: Timing                                                                          |      |

| Figure 9  | Output Clamp                                                                                                | . 17 |

| Figure 10 | Switching an Inductance                                                                                     |      |

| Figure 11 | Boundary conditions for switching active loads at low $V_S$ with low initial $V_{DS}$ voltage               | . 18 |

| Figure 12 | Inverse Current Circuitry                                                                                   | . 19 |

| Figure 13 | Inverse Behavior - Timing Diagram                                                                           | . 19 |

| Figure 14 | Switching in PWM                                                                                            | . 20 |

| Figure 15 | Input Pin Circuitry                                                                                         | . 21 |

| Figure 16 | Diagram of Diagnosis & Protection Block                                                                     | . 22 |

| Figure 17 | Loss of Ground Protection with External Components                                                          | . 22 |

| Figure 18 | Loss of $V_S$                                                                                               | . 23 |

| Figure 19 | Loss of Load                                                                                                |      |

| Figure 20 | Undervoltage Behavior                                                                                       | . 24 |

| Figure 21 | Overvoltage Protection with External Components                                                             | . 25 |

| Figure 22 | Reverse Polarity Protection with External Components                                                        | . 26 |

| Figure 23 | Oscillations at VS pin                                                                                      | . 27 |

| Figure 24 | Consecutive short circuit events                                                                            | . 27 |

| Figure 25 | RC Snubber circuits: between VS pin and module GND; between VS pin and device GND                           | . 28 |

| Figure 26 | Overload Protection                                                                                         | . 29 |

| Figure 27 | Diagnostic Block Diagram                                                                                    | . 30 |

| Figure 28 | Current Sense for Nominal and Overload Condition                                                            | . 31 |

| Figure 29 | Improved Current Sense Accuracy after 2-Point Calibration                                                   | . 33 |

| Figure 30 | Fault Acknowledgement                                                                                       | . 34 |

| Figure 31 | Application Diagram with BTS50015-1TAD                                                                      | . 47 |

| Figure 32 | PG-TO-263-7-10 (RoHS-Compliant)                                                                             | . 49 |

6

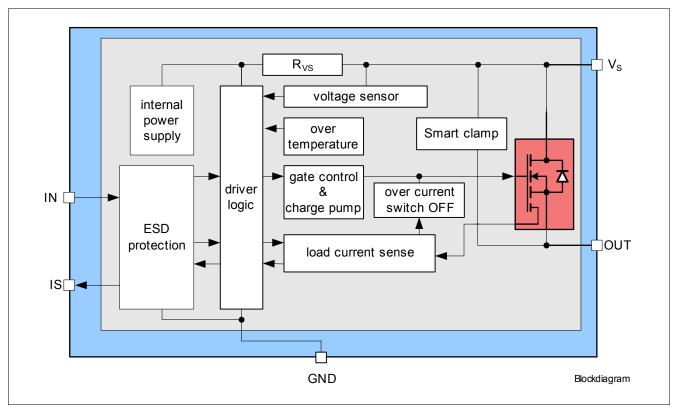

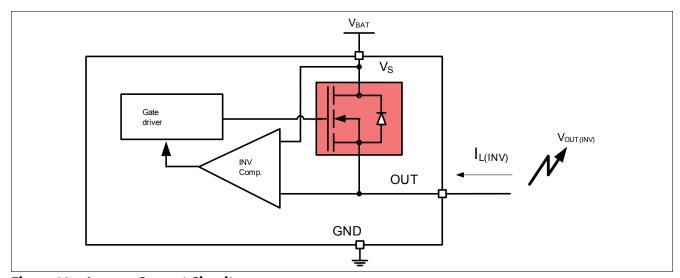

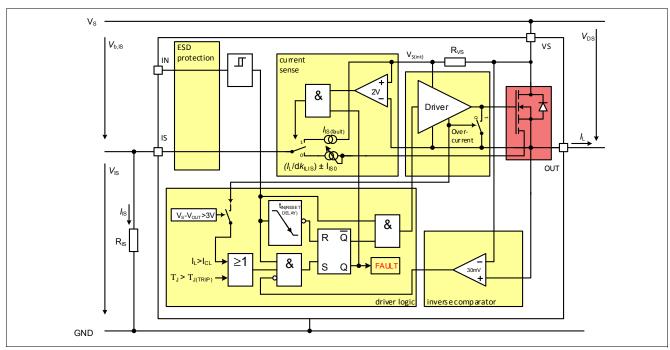

**Block Diagram**

# 2 Block Diagram

Figure 1 Block Diagram for the BTS50015-1TAD

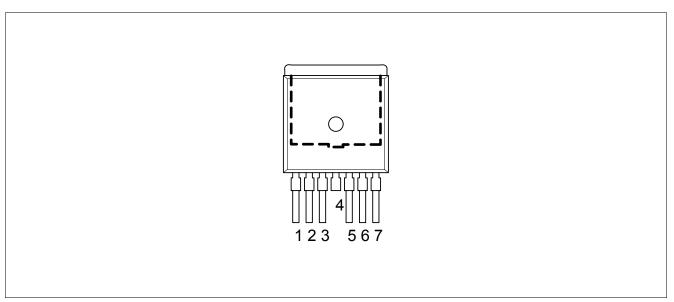

**Pin Configuration**

# 3 Pin Configuration

# 3.1 Pin Assignment

Figure 2 Pin Configuration

## 3.2 Pin Definitions and Functions

| Pin            | Symbol | Function                                                              |

|----------------|--------|-----------------------------------------------------------------------|

| 1              | GND    | GrouND; Signal Ground                                                 |

| 2              | IN     | INput; Digital signal to switch ON channel ("high" active)            |

| 3              | IS     | Sense; Analog/Digital signal for diagnosis, if not used: left open    |

| 4, Cooling tab | VS     | Supply Voltage; Battery voltage                                       |

| 5, 6, 7        | OUT    | <b>OUTput;</b> Protected high side power output channel <sup>1)</sup> |

<sup>1)</sup> All output pins are internally connected and they also have to be connected together on the PCB. Not shorting all outputs on PCB will considerably increase the ON-state resistance and decrease the current sense / overcurrent tripping accuracy. PCB traces have to be designed to withstand the maximum current.

**Pin Configuration**

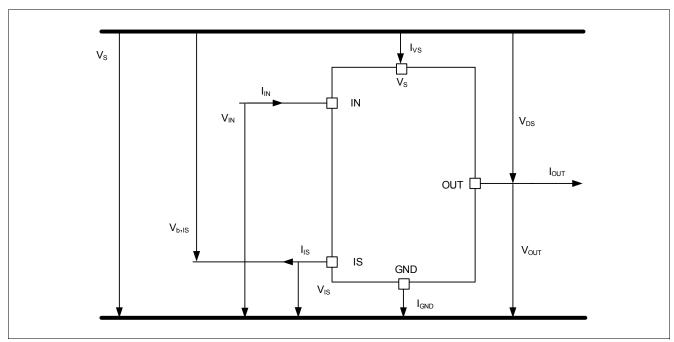

# 3.3 Voltage and Current Definition

Figure 3 shows all terms used in this Data Sheet, with associated convention for positive values.

Figure 3 Voltage and Current Definition

# infineon

#### **General Product Characteristics**

# **4** General Product Characteristics

# 4.1 Absolute Maximum Ratings

# Table 2 Absolute Maximum Ratings<sup>1)</sup>

$T_{\rm J}$  = -40°C to +150°C; (unless otherwise specified)

| Parameter                                                                  | Symbol                          |                        | Valu                                           | es                     | Unit | Note or<br>Test Condition                                                                                                                                                                                       | Number  |

|----------------------------------------------------------------------------|---------------------------------|------------------------|------------------------------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                            |                                 | Min.                   | Тур.                                           | Max.                   |      |                                                                                                                                                                                                                 |         |

| Supply Voltages                                                            |                                 |                        |                                                | ·                      |      |                                                                                                                                                                                                                 |         |

| Supply Voltage                                                             | V <sub>S</sub>                  | -0.3                   | _                                              | 28                     | V    | _                                                                                                                                                                                                               | P_4.1.1 |

| Reverse Polarity Voltage                                                   | -V <sub>S(REV)</sub>            | 0                      | -                                              | 16                     | V    | $^{2)}t < 2 \text{ min}$<br>$T_A = 25^{\circ}C$<br>$R_L \ge 0.5 \Omega$                                                                                                                                         | P_4.1.2 |

| Load Dump Voltage                                                          | $V_{\mathrm{BAT}(\mathrm{LD})}$ | _                      | _                                              | 45                     | V    | $^{3)}$ $R_{I} = 2 \Omega$<br>$R_{L} = 2.2 \Omega$<br>$R_{IS} = 1 k\Omega$<br>$R_{IN} = 4.7 k\Omega$                                                                                                            | P_4.1.5 |

| <b>Short Circuit Capability</b>                                            |                                 |                        |                                                |                        |      |                                                                                                                                                                                                                 |         |

| Supply Voltage for Short Circuit<br>Protection                             | V <sub>S(SC)</sub>              | 5                      | -                                              | 20                     | V    | $^{4)}R_{ECU} = 20 \text{ m}\Omega$<br>$L_{ECU} = 1 \text{ μH}$<br>$R_{cable} = 6 \text{ m}\Omega/\text{m}$<br>$L_{cable} = 1 \text{ μH/m}$<br>l = 0  to  5  m<br>R, C as shown in Figure 31<br>See Chapter 5.3 | P_4.1.3 |

| Short Circuit is Permanent: IN<br>Pin Toggles Short Circuit (SC<br>type 1) | $n_{RSC1}$                      | _                      | -                                              | 1 million<br>(Grade A) | _    | 5)                                                                                                                                                                                                              | P_4.1.4 |

| GND Pin                                                                    |                                 | 1                      | <u>,                                      </u> |                        |      |                                                                                                                                                                                                                 |         |

| Current through GND pin                                                    | I <sub>GND</sub>                | -15<br>_ <sup>6)</sup> | -                                              | 10 <sup>7)</sup><br>15 | mA   | -<br>t ≤ 2 min                                                                                                                                                                                                  | P_4.1.6 |

| Input Pin                                                                  |                                 | 1                      | <u>,                                      </u> |                        |      |                                                                                                                                                                                                                 |         |

| Voltage at IN pin                                                          | $V_{IN}$                        | -0.3                   | _                                              | $V_{S}$                | V    | _                                                                                                                                                                                                               | P_4.1.7 |

| Current through IN pin                                                     | I <sub>IN</sub>                 | -5<br>-5               | -                                              | 5<br>50 <sup>6)</sup>  | mA   | -<br>t ≤ 2 min                                                                                                                                                                                                  | P_4.1.8 |

| Maximum Retry Cycle Rate in Fault Condition                                | $f_{ m fault}$                  | -                      | -                                              | 1                      | Hz   | -                                                                                                                                                                                                               | P_4.1.9 |

#### **Smart High-Side Power Switch**

#### **General Product Characteristics**

## Table 2 Absolute Maximum Ratings<sup>1)</sup> (cont'd)

$T_1 = -40$ °C to +150°C; (unless otherwise specified)

| Parameter                                                                                   | Symbol                | Values                 |          |                        | Unit | Note or                                                                                                                                     | Number   |

|---------------------------------------------------------------------------------------------|-----------------------|------------------------|----------|------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                             |                       | Min.                   | Тур.     | Max.                   |      | <b>Test Condition</b>                                                                                                                       |          |

| Sense Pin                                                                                   |                       |                        |          |                        |      |                                                                                                                                             |          |

| Voltage at IS pin                                                                           | $V_{IS}$              | -0.3                   | -        | V <sub>S</sub>         | V    | _                                                                                                                                           | P_4.1.10 |

| Current through IS Pin                                                                      | I <sub>IS</sub>       | -15<br>_ <sup>6)</sup> | -        | 10 <sup>7)</sup><br>15 | mA   | -<br>t ≤ 2 min                                                                                                                              | P_4.1.11 |

| Power Stage                                                                                 | 1                     |                        |          |                        | II.  |                                                                                                                                             |          |

| Maximum Energy Dissipation by<br>Switching Off Inductive Load<br>Single Pulse over Lifetime | E <sub>AS</sub>       | -                      | -        | 3000                   | mJ   | $V_{\rm S} = 13.5 \text{ V}$<br>$I_{\rm L} = I_{\rm L(NOM)} = 33\text{A}$<br>$T_{\rm J(0)} \le 150 ^{\circ}\text{C}$<br>See <b>Figure 5</b> | P_4.1.12 |

| Maximum Energy Dissipation<br>Repetitive Pulse                                              | E <sub>AR</sub>       | -                      | -        | 550                    | mJ   | $^{8)}V_{S} = 13.5 \text{ V}$ $I_{L} = I_{L(NOM)} = 33\text{A}$ $T_{J(0)} \le 105^{\circ}\text{C}$ See <b>Figure 5</b>                      | P_4.1.13 |

| Maximum Energy Dissipation<br>Repetitive Pulse                                              | E <sub>AR</sub>       | -                      | -        | 200                    | mJ   | $^{8)}V_{S} = 13.5 \text{ V}$ $I_{L} = 80\text{A}$ $T_{J(0)} \le 105^{\circ}\text{C}$ See <b>Figure 5</b>                                   | P_4.1.14 |

| Average Power Dissipation                                                                   | $P_{TOT}$             | -                      | -        | 200                    | W    | T <sub>C</sub> = -40°C to<br>150°C                                                                                                          | P_4.1.15 |

| Voltage at OUT Pin                                                                          | $V_{OUT}$             | -64                    | -        | _                      | V    | _                                                                                                                                           | P_4.1.21 |

| Temperatures                                                                                |                       |                        |          |                        |      |                                                                                                                                             |          |

| Junction Temperature                                                                        | $T_{J}$               | -40                    | -        | 150                    | °C   | _                                                                                                                                           | P_4.1.16 |

| Dynamic Temperature Increase while Switching                                                | $\Delta T_{ m J}$     | _                      | -        | 60                     | K    | See Chapter 5.3                                                                                                                             | P_4.1.17 |

| Storage Temperature                                                                         | $T_{\rm STG}$         | -55                    | _        | 150                    | °C   | -                                                                                                                                           | P_4.1.18 |

| ESD Susceptibility                                                                          | •                     |                        | <u> </u> | ·                      |      |                                                                                                                                             |          |

| ESD Susceptibility (all Pins)                                                               | V <sub>ESD(HBM)</sub> | -2                     | -        | 2                      | kV   | HBM <sup>9)</sup>                                                                                                                           | P_4.1.19 |

| ESD Susceptibility OUT Pin vs. GND / $V_{\rm S}$                                            | V <sub>ESD(HBM)</sub> | -4                     | -        | 4                      | kV   | HBM <sup>9)</sup>                                                                                                                           | P_4.1.20 |

- 1) Not subject to production test, specified by design.

- 2) The device is mounted on a FR4 2s2p board according to Jedec JESD51-2,-5,-7 at natural convection.

- 3)  $V_{S(LD)}$  is setup without DUT connected to the generator per ISO 7637-1.

- 4) In accordance to AEC Q100-012, Figure-1 Test Circuit.

- 5) In accordance to AEC Q100-012, Chapter 3 conditions. Short circuit conditions deviating from AEC Q100-012 may influence the specified short circuit cycle number in the Data Sheet.

- 6) The total reverse current (sum of  $I_{GND}$ ,  $I_{IS}$  and  $I_{IN}$ ) is limited by  $I_{S(REV) \text{ max}}$  and  $I_{REV}$ .

- 7)  $T_{\rm C} \le 125^{\circ}{\rm C}$

- 8) Setup with repetitive EAR and superimposed TC conditions (like AEC-Q100-PTC,  $\leq 10^6$  pulses with E  $\leq E_{AR}$ ,  $\leq 10^3$  passive temperature cycles), parameter drift within datasheet limits possible

- 9) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS-001.

## **Smart High-Side Power Switch**

#### **General Product Characteristics**

#### **Notes**

- 1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- 2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the Data Sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

Figure 4 Maximum Single Pulse Current vs. Pulse Time,  $T_J \le 150$ °C,  $T_{PIN} = 85$ °C

Note:

Above diagram shows the maximum single pulse current that can be maintained by the internal power stage bond wires for a given pulse time  $t_{pulse}$ . The maximum reachable current may be smaller depending on the device current limitation level. The maximum reachable pulse time may be shorter due to thermal protection of the device.  $T_{PIN}$  is the temperature of pins 5, 6 and 7.

#### **General Product Characteristics**

Figure 5 Maximum Energy Dissipation for Inductive Switch OFF,  $E_A$  vs.  $I_L$  at  $V_S$  = 13.5 V

Figure 6 Maximum Energy Dissipation Repetitive Pulse temperature derating

## **Smart High-Side Power Switch**

#### **General Product Characteristics**

#### **Functional Range** 4.2

Table 3 **Functional Range**

| Parameter                                                                            | Symbol                  | Symbol Valu       |      | lues Unit |      | Note or                                                                                                                                    | Number  |

|--------------------------------------------------------------------------------------|-------------------------|-------------------|------|-----------|------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                      |                         | Min.              | Тур. | Max.      |      | <b>Test Condition</b>                                                                                                                      |         |

| Supply Voltage Range for Nominal Operation                                           | $V_{S(NOM)}$            | 8                 | -    | 18        | V    | -                                                                                                                                          | P_4.2.1 |

| Supply Voltage Range for Extended Operation                                          | V <sub>S(EXT)</sub>     | 5.3               | -    | 28        | V    | $I_{\text{IN}} \ge 2.2 \text{ V}$ $I_{\text{L}} \le I_{\text{L(NOM)}}$ $I_{\text{J}} \le 25^{\circ}\text{C}$ Parameter deviations possible | P_4.2.2 |

|                                                                                      | $V_{S(EXT)}$            | 5.5               | -    | 28        | V    | $I_{\rm IN} \ge 2.2 \rm V$ $I_{\rm L} \le I_{\rm L(NOM)}$ $I_{\rm J} = 150 \rm ^{\circ} \rm C$ Parameter deviations possible               |         |

| Supply Voltage Range for<br>Extended Operation<br>Dynamic Undervoltage<br>Capability | V <sub>S(EXT,DYN)</sub> | 3.2 <sup>2)</sup> | -    | -         | V    | <sup>1)</sup> acc. to ISO 7637                                                                                                             | P_4.2.3 |

| Supply Undervoltage<br>Shutdown                                                      | V <sub>S(UV)</sub>      | -                 | -    | 4.5       | V    | $^{1)}V_{IN} \ge 2.2 \text{ V}$ $R_L = 270 \Omega$ $V_S$ decreasing See <b>Figure 20</b>                                                   | P_4.2.4 |

| Slewrate at OUT                                                                      | $ dV_{DS}/dt $          | -                 | -    | 10        | V/µs | 1) V <sub>DS</sub>   < 3V<br>See <b>Chapter 5.1.4</b>                                                                                      | P_4.2.7 |

| Slewrate at OUT                                                                      | dV <sub>DS</sub> /dt    | -                 | -    | 0.2       | V/µs | $^{1)}V_{S(EXT)} < V_{S} < 8 \text{ V}$<br>$0 < V_{DS} < 1 \text{ V}$<br>$t < t_{ON(DELAY)}$<br>See <b>Chapter 5.1.4</b>                   | P_4.2.8 |

<sup>1)</sup> Not subject to production test. Specified by design

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

<sup>2)</sup>  $T_A = 25$ °C;  $R_L = 0.5 \Omega$ ; pulse duration 6 ms; cranking capability is depending on load and must be verified under application conditions

# infineon

#### **General Product Characteristics**

#### 4.3 Thermal Resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to **www.jedec.org**.

Table 4 Thermal Resistance

| Parameter           | Symbol                  | Values |      | Values |     | Values         |         | Unit | Note or | Number |

|---------------------|-------------------------|--------|------|--------|-----|----------------|---------|------|---------|--------|

|                     |                         | Min.   | Тур. | Max.   |     | Test Condition |         |      |         |        |

| Junction to Case    | R <sub>thJC</sub>       | -      | -    | 0.5    | K/W | 1)             | P_4.3.1 |      |         |        |

| Junction to Ambient | R <sub>thJA(2s2p)</sub> | -      | 20   | _      | K/W | 1)2)           | P_4.3.2 |      |         |        |

| Junction to Ambient | R <sub>thJA</sub>       | -      | 70   | _      | K/W | 1)3)           | P_4.3.3 |      |         |        |

- 1) Not subject to production test, specified by design.

- 2) Specified  $R_{\text{thJA}}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with 2 inner copper layers (2 × 70  $\mu$ m Cu, 2 × 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.  $T_A$  = 25°C. Device is dissipating 2 W power.

- 3) Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 1s0p board; the Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm board with only one top copper layer 1 × 70  $\mu$ m.  $T_A$  = 25°C. Device is dissipating 2 W power.

**Figure 7** is showing the typical thermal impedance of BTS50015-1TAD mounted according to JEDEC JESD51-2,-5,-7 at natural convection on FR4 1s0p and 2s2p boards.

Figure 7 Typical Transient Thermal Impedance  $Z_{th(JA)} = f(time)$  for Different PCB Conditions

# 5 Functional Description

#### 5.1 Power Stage

The power stage is built by a N-channel power MOSFET (DMOS) with charge pump.

#### **5.1.1** Output ON-State Resistance

The ON-state resistance  $R_{\rm DS(ON)}$  depends on the supply voltage as well as the junction temperature  $T_{\rm J}$ . Page 42 shows the dependencies in terms of temperature and supply voltage, for the typical ON-state resistance. The behavior in reverse polarity is described in **Chapter 5.3.5**.

A HIGH signal (see **Chapter 5.2**) at the input pin causes the power DMOS to switch ON with a dedicated slope, which is optimized in terms of EMC emission.

#### **5.1.2** Switching Resistive Loads

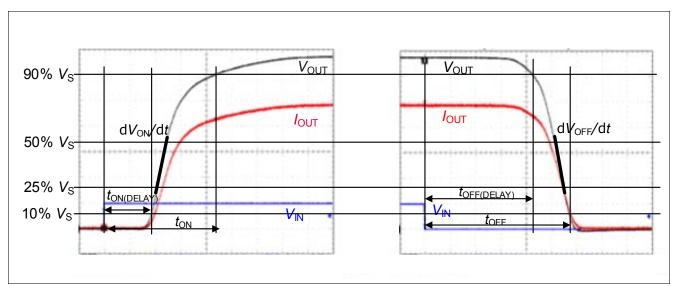

**Figure 8** shows the typical timing when switching a resistive load. The power stage has a defined switching behavior. Defined slew rates results in lowest EMC emission at minimum switching losses.

Figure 8 Switching a Resistive Load: Timing

## **5.1.3** Switching Inductive Loads

#### 5.1.3.1 Output Clamping

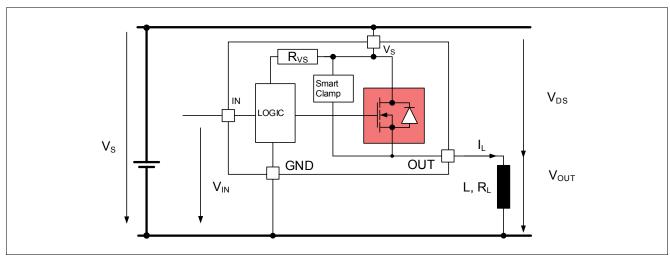

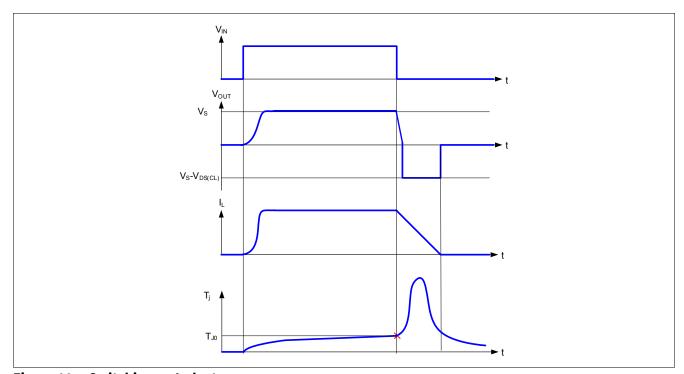

When switching OFF inductive loads with high side switches, the voltage  $V_{\text{OUT}}$  drops below ground potential, because the inductance intends to continue driving the current. To prevent the destruction of the device due to high voltages, there is a Infineon SMART CLAMPING mechanism implemented that keeps negative output voltage to a certain level ( $V_{\text{S}}$  -  $V_{\text{DS(CL)}}$ ). Please refer to **Figure 9** and **Figure 10** for details. Nevertheless, the maximum allowed load inductance remains limited.

Figure 9 Output Clamp

Figure 10 Switching an Inductance

The BTS50015-1TAD provides Infineon SMART CLAMPING functionality. To increase the energy capability, the clamp voltage  $V_{\rm DS(CL)}$  increases with junction temperature  $T_{\rm J}$  and with load current  $I_{\rm L}$ . Refer to Page 44.

#### 5.1.3.2 Maximum Load Inductance

During demagnetization of inductive loads, energy must be dissipated in the BTS50015-1TAD. This energy can be calculated with following equation:

$$E = V_{DS(CL)} \times \frac{L}{R_L} \times \left[ \frac{V_S - V_{DS(CL)}}{R_L} \times \ln \left( 1 - \frac{R_L \times I_L}{V_S - V_{DS(CL)}} \right) + I_L \right]$$

(5.1)

#### **Smart High-Side Power Switch**

#### **Functional Description**

Following equation simplifies under the assumption of  $R_1 = 0 \Omega$ .

$$E = \frac{1}{2} \times L \times I_L^2 \times \left(1 - \frac{V_S}{V_S - V_{DS(CL)}}\right)$$

(5.2)

The energy, which is converted into heat, is limited by the thermal design of the component. See **Figure 5** for the maximum allowed energy dissipation as function of the load current.

#### 5.1.4 Switching Active Loads

When switching generative or electronic loads such as motors or secondary ECUs which have the ability to feed back voltage disturbances to the OUT pins, special attention is required about the resulting absolute and dynamic voltage  $V_{DS}$  between VS pin and OUT pins.

To maintain device functionality it is required to limit the maximum positive or negative slew rate of  $V_{DS} = V_S - V_{OUT}$  below  $|dV_{DS}/dt|$  (parameter P\_4.2.7).

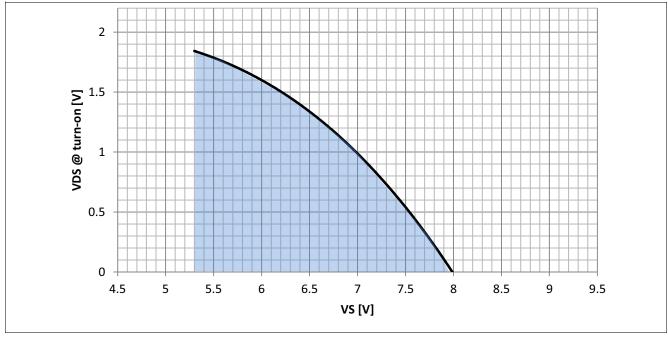

In case the device operates at low battery voltage ( $V_{\rm S} < V_{\rm S(NOM),\,Min}$ ) where the load feeds back a positive output voltage reaching almost VS potential ( $0 < V_{\rm DS} < 1$  V), it has to be ensured that for each activation (turn-on event), where the device is commanded on by applying  $V_{\rm IN(H)}$  at IN pin, a maximum positive or negative slew rate of  $V_{\rm DS}$  below  $|{\rm d}V_{\rm DS}/{\rm dt}|$  (parameter P\_4.2.8) will not be exceeded until  $t_{\rm ON(DELAY)}$  has expired.

Also in the case of low  $V_S$  and low  $V_{DS}$  during the rising edge of IN, the device might not turn on. **Figure 11** shows the worst case boundary condition. In such condition, if the device does not turn on, it will be latched.

Figure 11 Boundary conditions for switching active loads at low  $V_s$  with low initial  $V_{DS}$  voltage. (Not subject to production test, specified by design)

For loads that generate steady or dynamic voltage at the OUT pins which is higher than voltage at VS pin please consider **Chapter 5.1.5**.

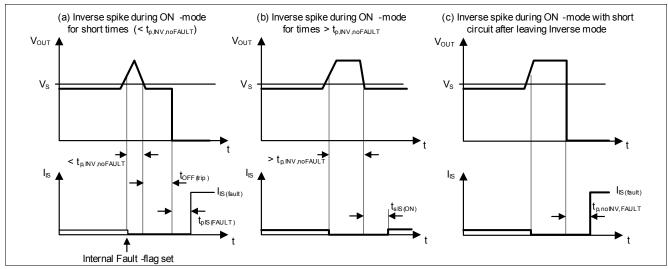

#### 5.1.5 Inverse Current Capability

In case of inverse current, meaning a voltage  $V_{\rm OUT(INV)}$  at the output higher than the supply voltage  $V_{\rm S}$ , a current  $I_{\rm L(INV)}$  will flow from output to  $V_{\rm S}$  pin via the body diode of the power transistor (please refer to **Figure 12**). In case the IN pin is HIGH, the power DMOS is already activated and will continue to remain in ON state during the inverse event. In case, the input goes from "L" to "H", the DMOS will be activated even during an inverse event. Under inverse condition, the device is not overtemperature / overload protected. During inverse mode at ON the sense pin will provide a leakage current of less or equal to  $I_{\rm ISO}$ . Due to the limited speed of INV comparator, the inverse duration needs to be limited.

Figure 12 Inverse Current Circuitry

Figure 13 Inverse Behavior - Timing Diagram

#### **Smart High-Side Power Switch**

#### **Functional Description**

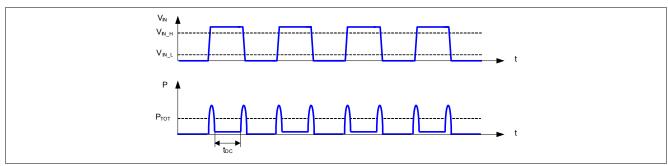

#### 5.1.6 PWM Switching

The switching losses during this operation should be properly considered (see following equation):

$P_{\text{TOTAL}} = \text{(switching\_ON\_energy + switching\_OFF\_energy + } I_{\text{L}}^2 \times R_{\text{DS(ON)}} \times t_{\text{DC}}) / \text{period}$

PWM switching application slightly above  $t_{\text{IN(RESETDELAY)}}$  parameter (see **Figure 26**) with calculated power dissipation  $P_{\text{TOTAL}} > P_{\text{TOT}}$  parameter limit causes an effective increase in  $T_{\text{J(TRIP)}}$  parameter.

In the event of a fault condition it has to be ensured, that the PWM frequency will not exceed a maximum retry frequency of  $f_{\text{FAULT}}$  (parameter P\_4.1.9). With this measure the short circuit robustness  $n_{\text{RSC1}}$  (parameter P\_4.1.4) can be utilized. Operation at nominal PWM frequency can only be restored, once the fault condition is overcome.

Figure 14 Switching in PWM

#### 5.1.7 Advanced switch-off behavior

In order to reduce device stress when switching OFF critical loads and/or critical load conditions, the device provides an advanced switch off functionality which results in a typically ten times faster switch off behavior. This fast switch off functionality is triggered by one the following conditions:

- The device is commanded off by applying  $V_{\text{IN(L)}}$  at the IN pin. During the switch OFF operation the OUT pins' voltage in respect to GND pin drops to typically -3 V or below (typically  $V_{\text{OUT}} V_{\text{GND}} \le -3$  V).

- The device is commanded on or is already in on-state. The device then detects a short circuit condition

(I<sub>L</sub> ≥ I<sub>CL(0)</sub>) and initiates a protective switch off. Please refer to Chapter 5.3.6.1 and Chapter 5.3.6.2 for details.

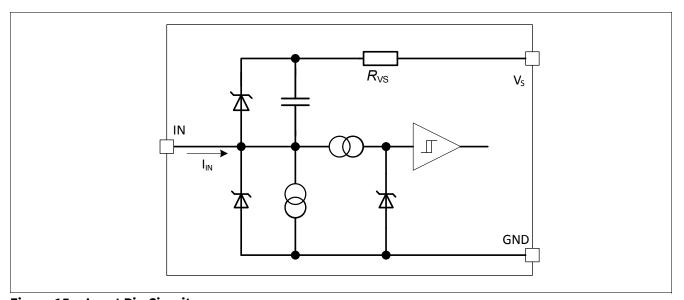

#### 5.2 Input Pins

#### 5.2.1 Input Circuitry

The input circuitry is compatible with 3.3 V and 5 V microcontrollers or can be directly driven by  $V_s$ . The concept of the input pin is to react to voltage threshold. With the Schmitt trigger, the output is either ON or OFF. **Figure 15** shows the electrical equivalent input circuitry.

Figure 15 Input Pin Circuitry

#### 5.2.2 Input Pin Voltage

The IN uses a comparator with hysteresis. The switching ON / OFF takes place in a defined region, set by the threshold  $V_{\rm IN(L)\,Max}$  and  $V_{\rm IN(H)\,Min.}$  The exact value where ON and OFF take place depends on the process, as well as the temperature. To avoid cross talk and parasitic turn ON and OFF, an hysteresis is implemented. This ensures immunity to noise.

#### **5.3** Protection Functions

The device provides embedded protective functions. Integrated protection functions are designed to prevent the destruction of the IC from fault conditions described in the Data Sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are designed neither for continuous nor for repetitive operation.

Figure 16 describes the typical functionality of the diagnosis and protection block.

Figure 16 Diagram of Diagnosis & Protection Block

#### 5.3.1 Loss of Ground Protection

In case of loss of module or device ground, where the load remains connected to ground, the device protects itself by automatically turning OFF (when it was previously ON) or remains OFF, regardless of the voltage applied at IN pin. It is recommended to use input resistors between the microcontroller and the BTS50015-1TAD to ensure switching OFF of channel. In case of loss of module or device ground, a current  $(I_{OUT(GND)})$  can flow out of the DMOS. **Figure 17** sketches the situation.

Figure 17 Loss of Ground Protection with External Components

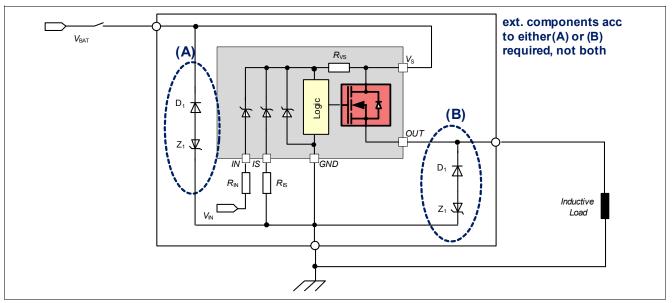

## 5.3.2 Protection during Loss of Load or Loss of $V_s$ Condition

In case of loss of load with charged primary inductances the supply voltage transient has to be limited. It is recommended to use a Zener diode, a varistor or  $V_S$  clamping power switches with connected loads in parallel. The voltage must be limited according to the minimum value of the parameter 6.1.33 indicated in **Table 6**.

#### **Smart High-Side Power Switch**

#### **Functional Description**

In case of loss of  $V_S$  connection with charged inductive loads, a current path with sufficient load current capability has to be provided, to demagnetize the charged inductances. It is recommended to protect the device using a Zener diode together with a diode ( $V_{Z1} + V_{D1} < 16 \text{ V}$ ), with path (A) or path (B) as shown in **Figure 18**.

For a proper restart of the device after loss of  $V_s$ , the input voltage must be delayed compared to the supply voltage ramp up. This can be realized by a capacitor between IN and GND (see **Figure 31**).

For higher clamp voltages, currents through all pins have to be limited according to the maximum ratings. Please see **Figure 18** and **Figure 19** for details.

Figure 18 Loss of  $V_s$

Figure 19 Loss of Load

#### 5.3.3 Undervoltage Behavior

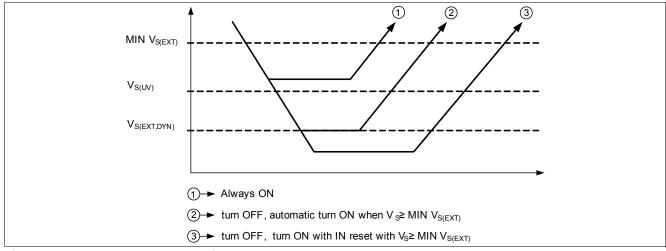

If the device is already ON and the power supply decreases but remains above the  $V_{S(UV)}$ , no effect is observed and the device keeps on working normally (case 1, **Figure 20**)

If the power supply falls below the  $V_{S(UV)}$  but remains above the  $V_{S(EXT,DYN)}$ , the device turns off, but it turns automatically on again when the power supply goes above Min.  $V_{S(EXT)}$  (case 2, **Figure 20**).

In case the power supply becomes lower than  $V_{S(EXT,DYN)}$ , the device turns off and can be switched on again only after a reset signal at the IN pin, provided that the power supply is higher than Min.  $V_{S(EXT)}$  (case 3, **Figure 20**).

Figure 20 Undervoltage Behavior

#### 5.3.4 Overvoltage Protection

In case  $V_{S(SC)_{max}} < V_S < V_{DS(CL)}$ , the device will switch ON/OFF normally as in the nominal voltage range.

Parameters may deviate from the specified limits and lifetime is reduced. This specially impacts the short circuit robustness, as well as the maximum energy  $E_{AS}$  and  $E_{AR}$  the device can handle.

The BTS50015-1TAD provides Infineon SMART CLAMPING functionality, which suppresses excessive transient overvoltage by actively clamping the overvoltage across the power stage and the load. This is achieved by controlling the clamp voltage  $V_{DS(CL)}$  depending on the junction temperature  $T_J$  and the load current  $I_L$  (see **Figure 21** for details).

Figure 21 Overvoltage Protection with External Components

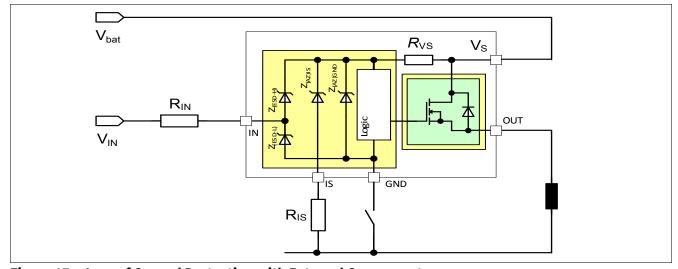

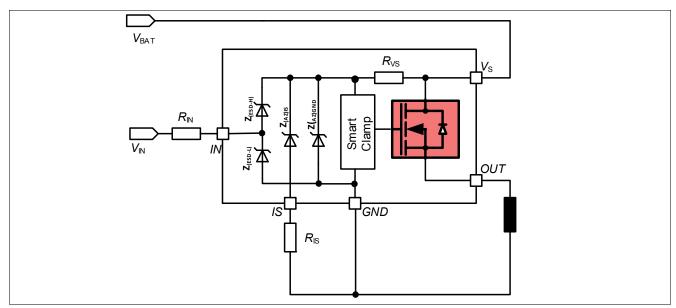

#### 5.3.5 Reverse Polarity Protection

In case of reverse polarity, the intrinsic body diode of the power DMOS causes power dissipation. To limit the risk of overtemperature, the device provides Infineon® ReverSave™ functionality. The power in this intrinsic body diode is limited by turning the DMOS ON. The DMOS resistance is then equal to  $R_{DS(REV)}$ .

Additionally, the current into the logic has to be limited. The device includes a  $R_{VS}$  resistor which limits the current in the diodes. To avoid overcurrent in the  $R_{VS}$  resistor, it is nevertheless recommended to use a  $R_{IN}$  resistor. Please refer to maximum current described in **Chapter 4.1**.

Figure 22 shows a typical application.

$R_{\rm IS}$  is used to limit the current in the sense transistor, which behaves as a diode.

The recommended typical value for  $R_{\rm IN}$  is 4.7 k $\Omega$  and for  $R_{\rm IS}$  1 k $\Omega$ .