Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## **DACs for Electronic Adjustment**

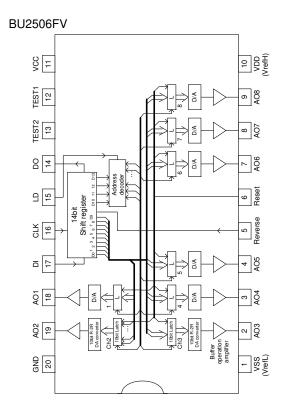

# High-precision 10bit 8ch/10ch D/A Converters

## BU2506FV,BU2505FV

No.11052EBT03

#### Description

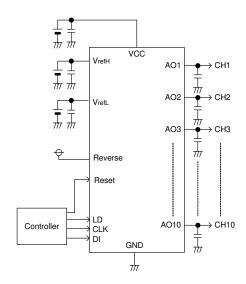

BU2506FV and BU2505FV ICs are high performance 10bit R-2R type DACs with 8ch and 10ch outputs, respectively. Cascade connection is possible, ensuring suitability with multi-channel applications. Each channel incorporates a full swing output-type buffer amplifier with high speed output response characteristics, resulting in a greatly shortened wait time. The ICs also utilize the TTL level input method, and with the RESET pin the output voltage can be kept in the lower reference voltage range.

#### Features

- 1) High performance, multi-channel R-2R-type 10bit D/A converter built-in (BU2506FV: 8 channels, BU2505FV: 10 channels)

- 2) Full swing output type buffer amplifier incorporated at each output channel

- 3) The RESET terminal can keep the output voltage at all channels within the lower reference voltage range

- 4) Digital input compatible with TTL levels

- 5) 14bit 3-line serial data + RESET signal input (address 4bit + data 10bit)

- 6) Cascade connection available

- 7) LSB first / MSB first of 10bit data can be changed by the REVERSE terminal

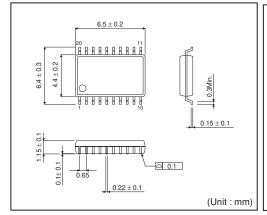

- 8) Compact package: 0.65mm pitch, 20 pins (SSOP-B20)

#### Applications

DVDs, CD-Rs, CD-RWs, Digital cameras

#### Lineup

| Parameter                        | BU2505FV    | BU2506FV    |

|----------------------------------|-------------|-------------|

| Power source voltage range       | 4.5 to 5.5V | 4.5 to 5.5V |

| Number of channels               | 10ch        | 8ch         |

| Differential non linearity error | ±1.0LSB     | ±1.0LSB     |

| Integral non linearity error     | ±3.5LSB     | ±3.5LSB     |

| Data transfer frequency          | 10MHz       | 10MHz       |

| Package                          | SSOP-B20    | SSOP-B20    |

#### ■Absolute Maximum Ratings(Ta=25°C)

| Parameter                            | Symbol | Ratings          | Unit |

|--------------------------------------|--------|------------------|------|

| Power source voltage                 | VCC    | -0.3 to 6.0      | V    |

| D/A converter upper standard voltage | VDD    | -0.3 to 6.0      | V    |

| Input voltage                        | VIN    | -0.3 to 6.0      | V    |

| Output voltage                       | VOUT   | -0.3 to 6.0      | V    |

| Storage temperature range            | Tstg   | -55 to 125       | °C   |

| Power dissipation                    | Pd     | 400 <sup>*</sup> | mW   |

<sup>\*</sup> Derated at 4mW/°C at Ta>25°C, mounted on a 70x70x1.6mm FR4 glass epoxy board (copper foil area less than 3%) Note: These products are not robust against radiation

#### ● Recommended Operating Conditions(Ta=25°C)

| Parameter                   | Symbol | Limits     | Unit |

|-----------------------------|--------|------------|------|

| Power supply voltage range  | VCC    | 4.5 to 5.5 | V    |

| Operating temperature range | Topr   | -30 to 85  | °C   |

● Electrical Characteristics (Unless otherwise specified, VCC=5V, VrefH=5V, VrefL=0V, Ta=25°C)

|                                                                                                        | Parameter                          |        |      | Limits |      | Unit               | Conditions                                                                                                                                                   |  |

|--------------------------------------------------------------------------------------------------------|------------------------------------|--------|------|--------|------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                        | Farameter                          | Symbol | MIN. | TYP.   | MAX. | Offic              | Conditions                                                                                                                                                   |  |

| <digital td="" un<=""><td>it&gt;</td><td></td><td></td><td></td><td></td><td></td><td>,</td></digital> | it>                                |        |      |        |      |                    | ,                                                                                                                                                            |  |

| Power sou                                                                                              | irce current                       | ICC    | -    | 0.85   | 2.8  | mA                 | At CLK=10MHz, IAO=0μA                                                                                                                                        |  |

| Input leak                                                                                             | current                            | IILK   | -5   | -      | 5    | μA                 | VIN=0 to VCC                                                                                                                                                 |  |

| Input volta                                                                                            | ge L                               | VIL    | -    | -      | 0.8  | V                  | -                                                                                                                                                            |  |

| Input volta                                                                                            | ge H                               | VIH    | 2.0  | -      | -    | V                  | -                                                                                                                                                            |  |

| Output vo                                                                                              | tage L                             | VOL    | 0    | -      | 0.4  | V                  | IOL=2.5mA                                                                                                                                                    |  |

| Output vo                                                                                              | tage H                             | VOH    | 4.6  | -      | 5    | V                  | IOH=-2.5mA                                                                                                                                                   |  |

| <analog td="" u<=""><td>nit&gt;</td><td></td><td></td><td></td><td></td><td></td><td></td></analog>    | nit>                               |        |      |        |      |                    |                                                                                                                                                              |  |

| Congumn                                                                                                | ion ourront                        | IrefH  | -    | 4.5    | 7.5  | mA                 | Data condition : at maximum                                                                                                                                  |  |

| Consump                                                                                                | ion current                        | пепп   | -    | 3.7    | 6.2  | mA <sup>(*1)</sup> | current                                                                                                                                                      |  |

| D/A conve<br>setting ran                                                                               | rter upper standard voltage<br>ige | VrefH  | 3.0  | -      | 5    | V                  | Outputs are not necessarily within the standard voltage setting range,                                                                                       |  |

| D/A conve<br>setting rar                                                                               | rter lower standard voltage<br>age | VrefL  | 0    | -      | 1.5  | V                  | but ARE within the buffer amplifier output voltage range (VO).                                                                                               |  |

| Dufferen                                                                                               | olifiar autout valtaga ranga       | VO     | 0.1  | -      | 4.9  | V                  | IO=±100μA                                                                                                                                                    |  |

| buller alli                                                                                            | olifier output voltage range       | VO     | 0.2  | -      | 4.75 | V                  | IO=±1.0mA                                                                                                                                                    |  |

| Buffer am                                                                                              | olifier output drive range         | Ю      | -2   | -      | 2    | mA                 | Upper side saturation voltage =0.35V (on full scale setting, current sourcing) Lower side saturation voltage =0.23V (on zero scale setting, current sinking) |  |

|                                                                                                        | Differential non-linearity error   | DNL    | -1.0 | -      | 1.0  | LSB                | VrefH =4.796V                                                                                                                                                |  |

| Precision                                                                                              | Integral non-linearity error       | INL    | -3.5 | -      | 3.5  | LOD                | VrefL=0.7V                                                                                                                                                   |  |

| 1 160131011                                                                                            | Zero point error                   | SZERO  | -25  | -      | 25   | mV                 | VCC=5.5V (4mV/LSB)                                                                                                                                           |  |

|                                                                                                        | Full scale error                   | SFULL  | -25  | -      | 25   | 111 V              | At no load (IO=+0mA)                                                                                                                                         |  |

| Buffer am                                                                                              | olifier output impedance           | RO     | -    | 5      | 15   | Ω                  | -                                                                                                                                                            |  |

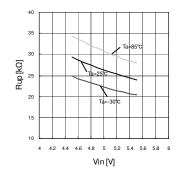

| Pull-up I/C                                                                                            | ) internal resistance value        | Rup    | 12.5 | 25     | 37.5 | kΩ                 | Input voltage 0V (Resistance value changes according to voltage supplied)                                                                                    |  |

<sup>\*1</sup> Value in the case where CH1 ~ CH8 are set to maximum current after reset

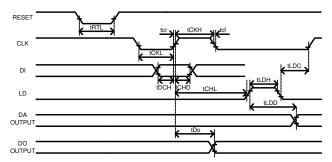

●Timing Characteristics(Unless otherwise specified, VCC=5V, VrefH=5V, VrefL=0V, Ta=25°C)

| Darameter               | Cumbal | Limits |      |      | Unit | Conditions                                                                             |  |  |

|-------------------------|--------|--------|------|------|------|----------------------------------------------------------------------------------------|--|--|

| Parameter               | Symbol | MIN.   | TYP. | MAX. | Unit | Judgment level is 80% / 20% of VCC.                                                    |  |  |

| Reset L pulse width     | tRTL   | 50     | -    | -    |      | -                                                                                      |  |  |

| Clock L pulse width     | tCKL   | 50     | -    | -    |      | -                                                                                      |  |  |

| Clock H pulse width     | tCKH   | 50     | -    | -    |      | -                                                                                      |  |  |

| Clock rise time         | tcr    | -      | -    | 50   |      | -                                                                                      |  |  |

| Clock fall time         | tcf    | -      | -    | 50   |      | -                                                                                      |  |  |

| Data setup time         | tDCH   | 20     | -    | -    | nS   | -                                                                                      |  |  |

| Data hold time          | tCHD   | 40     | -    | -    |      | -                                                                                      |  |  |

| Load setup time         | tCHL   | 50     | -    | -    |      | -                                                                                      |  |  |

| Load hold time          | tLDC   | 50     | -    | -    |      | -                                                                                      |  |  |

| Load H pulse width      | tLDH   | 50     | -    | -    |      | -                                                                                      |  |  |

| Data output delay time  | tDO    | -      | -    | 90   |      | CL=100pF                                                                               |  |  |

| DA output settling time | tLDD   | -      | 7    | 20   | μS   | CL≦100pF, VO: 0.5V⇔4.5V. Until output value deference from final value becomes 1/2LSB. |  |  |

(note) LD signal is level triggered. When LD input is on H level, internal shift-register state is loaded to DAC control latch. Clock transition during LD=H is inhibited.

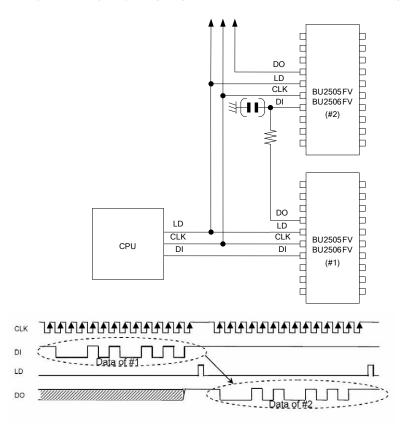

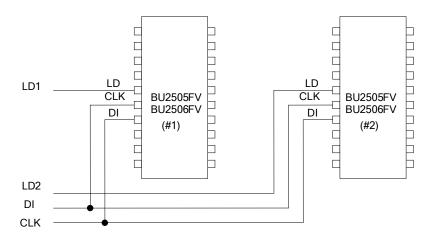

#### ● Cascade Connection

A data output terminal for cascade connection (DO) is available for reducing the number of parts when it is increased.

The DO terminal can be connected to a data input terminal (DI) of the next IC.

However, DO transition is synchronized with rising edge of clock signal, DO signal should be delayed, to keep a limit of data hold time

For example RC passive filter can be used.

Also in some cases, an operation frequency of logic signal have to be decreased to ensure a margin of data setup time.

Therefore, it is better to control LD port of each LSI separately, if extra CPU ports are available. In this case, more ports to control LD signals are needed, but a consideration described above doesn't have do be done.

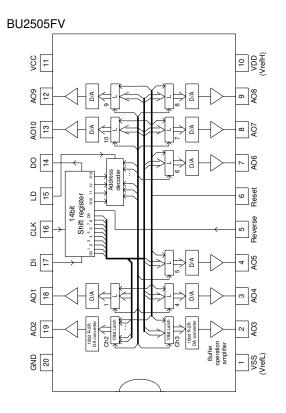

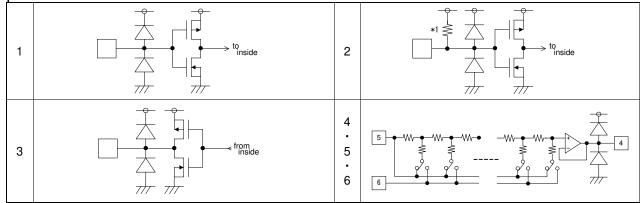

Terminal Descriptions

| No. | Terminal<br>Name | Analog /<br>Digital | I/O | Description                                                                                                            | Equivalent<br>Circuit |

|-----|------------------|---------------------|-----|------------------------------------------------------------------------------------------------------------------------|-----------------------|

| 1   | VSS              | Analog              | 1   | DA converter lower standard voltage (VrefL) input terminal                                                             | 6                     |

| 2   | AO3              | Analog              | 0   | 10bit D/A output(CH3)                                                                                                  | 4                     |

| 3   | AO4              | Analog              | 0   | 10bit D/A output(CH4)                                                                                                  | 4                     |

| 4   | AO5              | Analog              | 0   | 10bit D/A output(CH5)                                                                                                  | 4                     |

| 5   | Reverse          | Digital             | I   | The reverse LSB and MSB of data designation 10bit in 14bit.                                                            | 2                     |

| 6   | Reset            | Digital             | I   | All ch analog output L fixed                                                                                           | 2                     |

| 7   | AO6              | Analog              | 0   | 10bit D/A output(CH6)                                                                                                  | 4                     |

| 8   | AO7              | Analog              | 0   | 10bit D/A output(CH7)                                                                                                  | 4                     |

| 9   | AO8              | Analog              | 0   | 10bit D/A output(CH8)                                                                                                  | 4                     |

| 10  | VDD              | Analog              | -   | DA converter upper standard voltage (VrefH) input terminal                                                             | 5                     |

| 11  | VCC              | -                   | -   | Power source terminal                                                                                                  | -                     |

| 12  | AO9(TEST1)       | Analog              | 0   | 10bit D/A output(CH9) (BU2506FV : test terminal)                                                                       | 4                     |

| 13  | AO10(TEST2)      | Analog              | 0   | 10bit D/A output(CH10) (BU2506FV : test terminal)                                                                      | 4                     |

| 14  | DO               | Digital             | 0   | This outputs bit data of LSB of 14bit shift register.                                                                  | 3                     |

| 15  | LD               | Digital             | I   | LD terminal. When High level is input, the value of 14bit shift register is loaded to decoder and D/A output register. | 1                     |

| 16  | CLK              | Digital             |     | Shift clock input terminal. At rise of shift clock, the signal from DI terminal is input to 14bit shift register.      | 1                     |

| 17  | DI               | Digital             | ı   | Serial data input terminal. Serial data whose data length is 14bit (address 4bit + data 10bit) is input.               | 1                     |

| 18  | AO1              | Analog              | 0   | 10bit D/A output(CH1)                                                                                                  | 4                     |

| 19  | AO2              | Analog              | 0   | 10bit D/A output(CH2)                                                                                                  | 4                     |

| 20  | GND              | -                   | -   | GND terminal                                                                                                           | -                     |

<sup>\*</sup>In the case of BU2506FV, be sure to leave the TEST1 and TEST2 terminals open

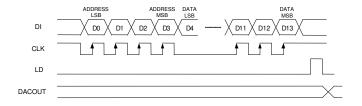

## **●**Command Transmission

- 1) Reverse = open (or VCC short-circuit) setting

- (1) Data format

| D13                              | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

|----------------------------------|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| For D/A converter output setting |     |     |     |    |    |    |    |    |    |    |    |    |    |

## (2) Data timing diagram

| Da | DΩ | D1 | DΛ | Address Calcation |

|----|----|----|----|-------------------|

| D3 | D2 | D1 | D0 | Address Selection |

| 0  | 0  | 0  | 0  | Inconsequential   |

| 0  | 0  | 0  | 1  | AO1 selection     |

| 0  | 0  | 1  | 0  | AO2 selection     |

| 0  | 0  | 1  | 1  | AO3 selection     |

| 0  | 1  | 0  | 0  | AO4 selection     |

| 0  | 1  | 0  | 1  | AO5 selection     |

| 0  | 1  | 1  | 0  | AO6 selection     |

| 0  | 1  | 1  | 1  | AO7 selection     |

| 1  | 0  | 0  | 0  | AO8 selection     |

| 1  | 0  | 0  | 1  | AO9 selection*1   |

| 1  | 0  | 1  | 0  | AO10 selection*1  |

| 1  | 0  | 1  | 1  | Inconsequential   |

| 1  | 1  | 0  | 0  | Inconsequential   |

| 1  | 1  | 0  | 1  | Inconsequential   |

| 1  | 1  | 1  | 0  | Inconsequential   |

| 1  | 1  | 1  | 1  | Inconsequential   |

| D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D/A output (VrefH=VDD, VrefL=VSS) |

|-----|-----|-----|-----|----|----|----|----|----|----|-----------------------------------|

| 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | VrefL                             |

| 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 1  | (VrefH-VrefL)/1024×1+VrefL        |

| 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 1  | 0  | (VrefH-VrefL)/1024×2+VrefL        |

| 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 1  | 1  | (VrefH-VrefL)/1024×3+VrefL        |

| :   | :   | :   | :   | :  | :  | :  | :  | :  | :  | :                                 |

| 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 0  | (VrefH-VrefL)/1024×1022+VrefL     |

| 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | (VrefH-VrefL)/1024×1023+VrefL     |

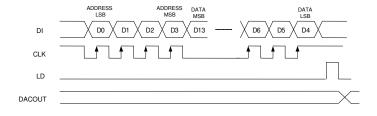

## 2) Reverse = L setting

## (1) Data format

|   | D4                                                       | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D3 | D2 | D1 | D0 |

|---|----------------------------------------------------------|----|----|----|----|----|-----|-----|-----|-----|----|----|----|----|

| Ì | For D/A converter output setting   For address selection |    |    |    |    |    |     |     |     |     |    |    |    |    |

## (2) Data timing diagram

| D3         D2         D1         D0         Address selection           0         0         0         Inconsequential           0         0         0         1         AO1 selection           0         0         1         0         AO2 selection           0         0         1         1         AO3 selection           0         1         0         0         AO4 selection           0         1         0         1         AO5 selection           0         1         1         AO7 selection           1         0         0         AO8 selection           1         0         0         AO9 selection           1         0         1         AO9 selection           1         0         1         AO10 selection |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0         0         0         1         AO1 selection           0         0         1         0         AO2 selection           0         0         1         1         AO3 selection           0         1         0         0         AO4 selection           0         1         0         1         AO5 selection           0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                          |

| 0         0         1         0         AO2 selection           0         0         1         1         AO3 selection           0         1         0         0         AO4 selection           0         1         0         1         AO5 selection           0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                          |

| 0         0         1         1         AO3 selection           0         1         0         0         AO4 selection           0         1         0         1         AO5 selection           0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                                                                                |

| 0         1         0         0         AO4 selection           0         1         0         1         AO5 selection           0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                                                                                                                                                |

| 0         1         0         1         AO5 selection           0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0         1         1         0         AO6 selection           0         1         1         1         AO7 selection           1         0         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0         1         1         1         AO7 selection           1         0         0         0         AO8 selection           1         0         0         1         AO9 selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1 0 0 0 AO8 selection<br>1 0 0 1 AO9 selection*1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 0 0 1 AO9 selection*1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 0 1 0 AO10 selection*1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 1 0 1 1 Inconsequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 1 0 0 Inconsequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 1 0 1 Inconsequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 1 1 0 Inconsequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 1 1 1 Inconsequential                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D4 | D5 | D6 | D7 | D8 | D9 | D10 | D11 | D12 | D13 | D/A output (VrefH=VDD, VrefL=VSS) |

|----|----|----|----|----|----|-----|-----|-----|-----|-----------------------------------|

| 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | VrefL                             |

| 1  | 0  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | (VrefH-VrefL)/1024×1+VrefL        |

| 0  | 1  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | (VrefH-VrefL)/1024×2+VrefL        |

| 1  | 1  | 0  | 0  | 0  | 0  | 0   | 0   | 0   | 0   | (VrefH-VrefL)/1024×3+VrefL        |

| •  | :  | :  | :  | :  | :  | :   | :   | :   | :   | :                                 |

| 0  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | (VrefH-VrefL)/1024×1022+VrefL     |

| 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1   | 1   | 1   | (VrefH-VrefL)/1024×1023+VrefL     |

<sup>\*1</sup> In the BU2506FV, this channel is for testing, therefore, do not designate.

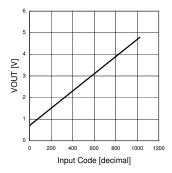

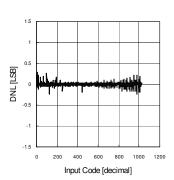

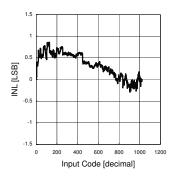

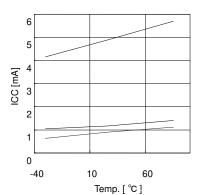

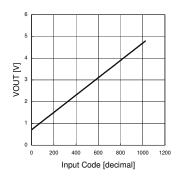

#### Electrical Characteristics Curves

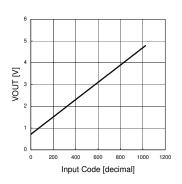

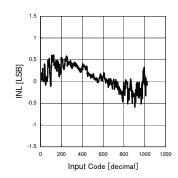

Fig.1 Output voltage linearity (-30°C)

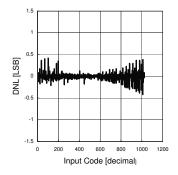

Fig.4 Differential linearity error (-30°C)

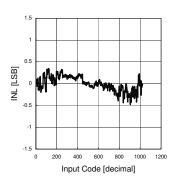

Fig.7 Integral linearity error (-30°C)

Fig.10 Circuit current temperature characteristic

Fig.2 Output voltage linearity (25°C)

Fig.5 Differential linearity error (25°C)

Fig.8 Integral linearity error (25°C)

Fig.11 Output load fluctuation characteristic (input code: 1FFh)

Fig.3 Output voltage linearity (85°C)

Fig.6 Differential linearity error (85°C)

Fig.9 Integral linearity error (85°C)

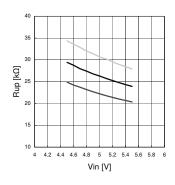

Fig.12 Pull-up built in resistance characteristic

● Equivalent Circuits

\*1  $25k\Omega$  at Vcc = 5.0V (changes according to voltage supplied)

## ● Standard Example Application Circuit

#### Operation Notes

- (1) The electrical characteristic and data on graphs for this datasheet, are typically evaluated value, and not guaranteed.

- (2) We suppose that application circuits are recommendable, but please make sufficient check for characteristics with the actual application. In case that value of external component for this LSI is changed, please check characteristic, not only static but also transient.

- (3) About absolute maximum ratings

If operation condition is over the absolute maximum ratings, supply voltage or other operation range, LSI will be broken. Please don't apply any voltage or temperature over the absolute maximum ratings. If application have possibilities of become over the absolute maximum ratings, please take safety measures by using fuse and so on. Not to over absolute maximum ratings of LSI.

(4) GND voltage

Please keep GND voltage lowest of any other terminal of this LSI. Please confirm that other terminal voltages are not lower than GND.

- (5) Thermal design

- Please making a thermal design that allows for a sufficient margin in light of the power dissipation in actual operating condition.

- (6) About terminals short and wrong mounting

Please pay full attention to the LSI direction and displacement when mounting LSI on PCB. If you assemble them by mistake and electrify it, LSI might be destroyed. And it is happen to short among LSI terminals or terminals and power supply, by foreign substance.

- (7) About operation in strong electromagnetic field If you use it in strong electromagnetic field, please evaluate fully as there is a possibility of malfunction.

- (8) Place a bypass capacitor as close as possible between each power supply terminal and ground in order to prevent deterioration of the D/A conversion accuracy due to ripple and noise signals from power supply or GND.

- (9) A capacitor should be placed between the analog output and ground in order to eliminate noise. A capacitance up to 100pF is recommended (including the capacitance of the wire).

- (10) This IC is selectable to decode the 10bit DI data pattern using either LSB first or MSB first, depending on the conditions of the REVERSE terminal. Therefore the reverse terminal should be open or VDD voltage (LSB first) or GND voltage (MSB first)

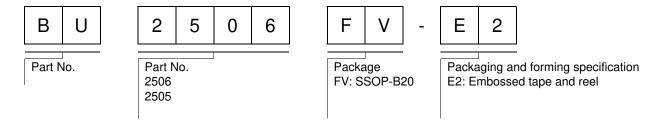

## Ordering part number

## SSOP-B20

#### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM Co.,Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

## ROHM Customer Support System

http://www.rohm.com/contact/