# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **Operational Amplifiers**

## Ultra Low Power CMOS Operational Amplifiers

BU7265G BU7265SG BU7266xxx BU7266Sxxx

### **General Description**

The BU7265G/BU7266xxx are ultra low supply current input output full swing CMOS operational amplifiers. The BU7265SG/BU7266Sxxx have an extended operating temperature range. They have low operating supply voltage and low input bias current. There are suitable for portable equipment and sensor amplifiers.

### Features

- Ultra Low Supply Current

- Low Operating Supply Voltage

- Wide operating temperature Range (BU7265SG/BU7266Sxxx)

- Low Input Bias Current

### Applications

- Battery-powered Equipment

- Portable Equipment

- Consumer Equipment

- Sensor Amplifiers

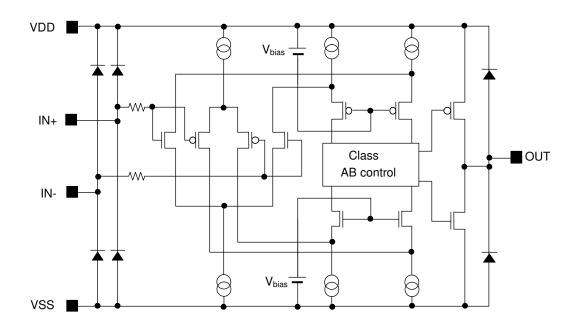

**Simplified Schematic**

### Key Specifications

Supply Voltage Range(single supply):

|                       | +1.8V to +5.5V  |

|-----------------------|-----------------|

| Supply Current:       |                 |

| BU7265/BU7265SG       | 0.35µA(Typ)     |

| BU7266xxx/BU7266Sxxx  | 0.7µA(Typ)      |

| Temperature Range:    |                 |

| BU7265G/BU7466xxx     | -40°C to +85°C  |

| BU7265SG/BU7266Sxxx   | -40°C to +105°C |

| Input Offset Current: | 1pA (Typ)       |

| Input Bias Current:   | 1pA (Typ)       |

|                       |                 |

### Packages

SSOP5 SOP8 SSOP-B8 MSOP8 W(Typ) x D(Typ) x H(Max) 2.90mm x 2.80mm x 1.25mm 5.00mm x 6.20mm x 1.71mm 3.00mm x 6.40mm x 1.35mm 2.90mm x 4.00mm x 0.90mm

Figure 1. Simplified Schematic

OProduct structure : Silicon monolithic integrated circuit OThis product has no designed protection against radioactive rays.

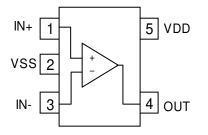

### **Pin Configuration**

BU7265G, BU7265SG: SSOP5

| Pin No. | Pin Name |

|---------|----------|

| 1       | IN+      |

| 2       | VSS      |

| 3       | IN-      |

| 4       | OUT      |

| 5       | VDD      |

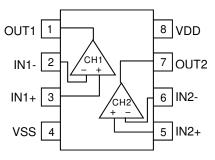

BU7266F, BU7266SF: SOP8 BU7266FV, BU7266SFV: SSOP-B8 BU7266FVM, BU7266SFVM: MSOP8

| Pin No. | Pin Name |  |  |  |  |

|---------|----------|--|--|--|--|

| 1       | OUT1     |  |  |  |  |

| 2       | IN1-     |  |  |  |  |

| 3       | IN1+     |  |  |  |  |

| 4       | VSS      |  |  |  |  |

| 5       | IN2+     |  |  |  |  |

| 6       | IN2-     |  |  |  |  |

| 7       | OUT2     |  |  |  |  |

| 8       | VDD      |  |  |  |  |

| Package             |                     |                       |                         |  |  |  |  |

|---------------------|---------------------|-----------------------|-------------------------|--|--|--|--|

| SSOP5               | SOP8                | SSOP-B8               | MSOP8                   |  |  |  |  |

| BU7265G<br>BU7265SG | BU7266F<br>BU7266SF | BU7266FV<br>BU7266SFV | BU7266FVM<br>BU7266SFVM |  |  |  |  |

### **Ordering Information**

| BU7265G         G         : SSOP5         F           BU7265SG         F         : SOP8         ()           BU7266xxx         FV         : SSOP-B8         () | В                 | U                       | 7 | 2 | 6 | Х | х            | х                    | х           | Х | - |                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------|---|---|---|---|--------------|----------------------|-------------|---|---|-------------------|

| BU7266Sxxx FVM : MSOP8 (                                                                                                                                       | BU7<br>BU7<br>BU7 | 265G<br>265SG<br>266xxx |   |   |   |   | G<br>F<br>FV | : SS<br>: SC<br>: SS | P8<br>OP-B8 |   | = | P<br>E<br>((<br>T |

X X

Packaging and forming specification E2: Embossed tape and reel (SOP8/SSOP-B8) TR: Embossed tape and reel (SSOP5/MSOP8)

### Line-up

| T <sub>opr</sub> | Channels | Pac     | ckage        | Orderable Part Number |

|------------------|----------|---------|--------------|-----------------------|

|                  | 1ch      | SSOP5   | Reel of 3000 | BU7265G-TR            |

| -40°C to +85°C   |          | SOP8    | Reel of 2500 | BU7266F-E2            |

|                  | 2ch      | SSOP-B8 | Reel of 2500 | BU7266FV-E2           |

|                  |          | MSOP8   | Reel of 3000 | BU7266FVM-TR          |

|                  | 1ch      | SSOP5   | Reel of 3000 | BU7265SG-TR           |

| -40°C to +105°C  | 2ch      | SOP8    | Reel of 2500 | BU7266SF-E2           |

|                  |          | SSOP-B8 | Reel of 2500 | BU7266SFV-E2          |

|                  |          | MSOP8   | Reel of 3000 | BU7266SFVM-TR         |

### Absolute Maximum Ratings (T<sub>A</sub>=25°C)

| Deverseter                                        |                  | Cumbal            | Rating                   |                 |                 |                            |      |  |  |  |

|---------------------------------------------------|------------------|-------------------|--------------------------|-----------------|-----------------|----------------------------|------|--|--|--|

| Parameter                                         |                  | Symbol            | BU7265G                  | BU7266xxx       | BU7265SG        | BU7266Sxxx                 | Unit |  |  |  |

| Supply Voltage                                    | VDD-VSS          |                   |                          | 4               | -7              |                            | V    |  |  |  |

|                                                   |                  | SSOP5             | 0.54 (Note 1,5)          | -               | 0.54 (Note 1,5) | -                          |      |  |  |  |

|                                                   | _                | SOP8              | -                        | 0.55 (Note 2,5) | -               | 0.55 <sup>(Note 2,5)</sup> |      |  |  |  |

| Power Dissipation                                 | PD               | SSOP-B8           | -                        | 0.50 (Note 3,5) | -               | 0.50 (Note 3,5)            | W    |  |  |  |

|                                                   |                  | MSOP8             | -                        | 0.47 (Note 4,5) | -               | 0.47 (Note 4,5)            |      |  |  |  |

| Differential Input<br>Voltage <sup>(Note 6)</sup> | V <sub>ID</sub>  |                   | VDD - VSS                |                 |                 |                            |      |  |  |  |

| Input Common-mode<br>Voltage Range                |                  | V <sub>ICM</sub>  | (VSS - 0.3) to VDD + 0.3 |                 |                 |                            |      |  |  |  |

| Input Current (Note 7)                            |                  | I <sub>I</sub>    | ±10                      |                 |                 |                            |      |  |  |  |

| Operating Supply Voltage                          | V <sub>opr</sub> |                   | +1.8 to +5.5             |                 |                 |                            |      |  |  |  |

| Operating Temperature                             | T <sub>opr</sub> |                   | -40 to +85 -40 to +105   |                 |                 |                            |      |  |  |  |

| Storage Temperature                               | T <sub>stg</sub> |                   | -55 to +125              |                 |                 |                            |      |  |  |  |

| Maximum<br>Junction Temperature                   |                  | T <sub>Jmax</sub> | +125                     |                 |                 |                            |      |  |  |  |

(Note 1) To use at temperature above  $T_A{=}25^\circ C$  reduce  $5.4 mW/^\circ C.$

(Note 2) To use at temperature above  $T_A=25^{\circ}C$  reduce 5.5mW/°C.

(Note 3) To use at temperature above  $T_A=25^{\circ}C$  reduce 5.0mW/°C.

(Note 4) To use at temperature above  $T_A=25^{\circ}C$  reduce 4.7mW/°C.

(Note 5) Mounted on a FR4 glass epoxy PCB 70mm×70mm×1.6mm (Copper foil area less than 3%).

(Note 6) The voltage difference between inverting input and non-inverting input is the differential input voltage.

Then input pin voltage is set to more than VSS.

(Note 7) An excessive input current will flow when input voltages of more than VDD+0.6V or less than VSS-0.6V are applied. The input current can be set to less than the rated current by adding a limiting resistor.

Caution: Operating the IC over the absolute maximum ratings may damage the IC. The damage can either be a short circuit between pins or an open circuit between pins and the internal circuitry. Therefore, it is important to consider circuit protection measures, such as adding a fuse, in case the IC is operated over the absolute maximum ratings.

### **Electrical Characteristics**

OBU7265G, BU7265SG (Unless otherwise specified VDD=+3V, VSS=0V, T<sub>A</sub>=25°C)

| Parameter                          | Symbol              | Temperature |         | Limit |         | Unit | Conditions                                 |

|------------------------------------|---------------------|-------------|---------|-------|---------|------|--------------------------------------------|

| Parameter                          | Symbol              | Range       | Min     | Тур   | Max     | Unit | Conditions                                 |

| Input Offset Voltage (Note 8)      | V <sub>IO</sub>     | 25°C        | -       | 1     | 8.5     | mV   | VDD=1.8V to 5.5V                           |

| Input Offset Current (Note 8)      | l <sub>iO</sub>     | 25°C        | -       | 1     | -       | pА   | -                                          |

| Input Bias Current (Note 8)        | I <sub>B</sub>      | 25°C        | -       | 1     | -       | pА   | -                                          |

| Supply Current (Note 9)            | 1                   | 25°C        | -       | 0.35  | 0.9     | μA   | R <sub>L</sub> =∞, A <sub>V</sub> =0dB     |

| Supply Current                     | I <sub>DD</sub>     | Full range  | -       | -     | 1.3     | μΛ   | IN+ =1.5V                                  |

| Maximum Output Voltage (High)      | V <sub>OH</sub>     | 25°C        | VDD-0.1 | -     | -       | V    | $R_L=10k\Omega$                            |

| Maximum Output Voltage (Low)       | V <sub>OL</sub>     | 25°C        | -       | -     | VSS+0.1 | V    | $R_L=10k\Omega$                            |

| Large Signal Voltage Gain          | Av                  | 25°C        | 60      | 95    | -       | dB   | $R_L=10k\Omega$                            |

| Input Common-mode<br>Voltage Range | VICM                | 25°C        | 0       | -     | 3       | V    | VSS to VDD                                 |

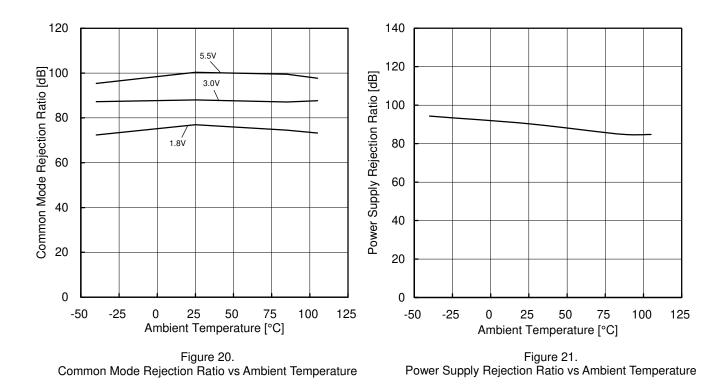

| Common-mode Rejection Ratio        | CMRR                | 25°C        | 45      | 60    | -       | dB   | -                                          |

| Power Supply Rejection Ratio       | PSRR                | 25°C        | 60      | 80    | -       | dB   | -                                          |

| Output Source Current (Note 10)    | I <sub>SOURCE</sub> | 25°C        | 1       | 2.4   | -       | mA   | OUT=VDD-0.4V                               |

| Output Sink Current (Note 10)      | I <sub>SINK</sub>   | 25°C        | 2       | 4     | -       | mA   | OUT=VSS+0.4V                               |

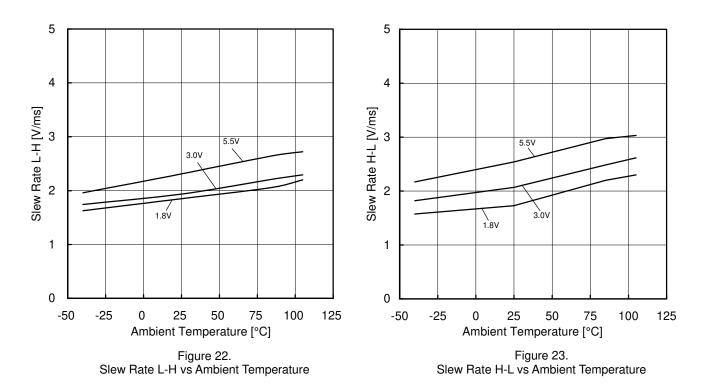

| Slew Rate                          | SR                  | 25°C        | -       | 2.4   | -       | V/ms | C <sub>L</sub> =25pF                       |

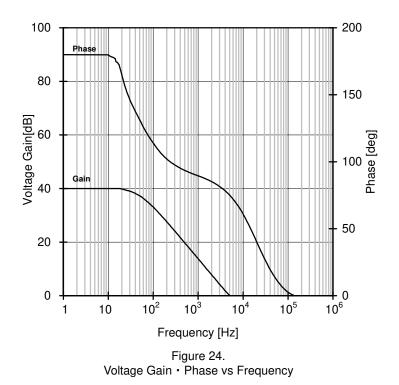

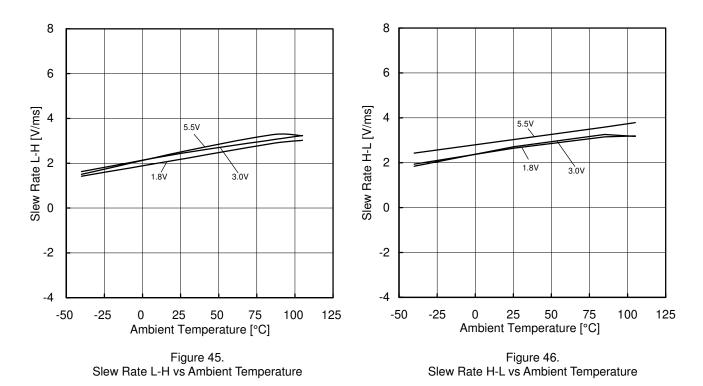

| Unity Gain Frequency               | f⊤                  | 25°C        | -       | 4     | -       | kHz  | $C_L=25pF, A_V=40dB$                       |

| Phase Margin                       | θ                   | 25°C        | -       | 60    | -       | deg  | C <sub>L</sub> =25pF, A <sub>V</sub> =40dB |

(Note 8) Absolute value

(Note 9) Full range BU7265:  $T_A$ =-40°C to +85°C BU7265S:  $T_A$ =-40°C to +105°C

(Note 10) Under the high temperature environment, consider the power dissipation of IC when selecting the output current.

When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

### **Electrical Characteristics - continued**

OBU7266xxx, BU7266Sxxx (Unless otherwise specified VDD=+3V, VSS=0V, T<sub>A</sub>=25°C)

| Parameter                          | Symbol            | Temperature |         | Limit |         | Unit | Conditions                                 |

|------------------------------------|-------------------|-------------|---------|-------|---------|------|--------------------------------------------|

| Falameter                          | Symbol            | Range       | Min     | Тур   | Max     | Unit | Conditions                                 |

| Input Offset Voltage (Note 11)     | V <sub>IO</sub>   | 25°C        | -       | 1     | 8.5     | mV   | VDD=1.8V to 5.5V                           |

| Input Offset Current (Note 11)     | I <sub>IO</sub>   | 25°C        | -       | 1     | -       | pА   | -                                          |

| Input Bias Current (Note 11)       | Ι <sub>Β</sub>    | 25°C        | -       | 1     | -       | pА   | -                                          |

| Supply Current (Note 12)           | I <sub>DD</sub>   | 25°C        | -       | 0.7   | 1.55    | μA   | R <sub>L</sub> =∞, All Op-Amps             |

| Supply Current                     | סטי               | Full range  | -       | -     | 2.1     | μΑ   | A <sub>V</sub> =0dB, IN+=1.5V              |

| Maximum Output Voltage (High)      | V <sub>OH</sub>   | 25°C        | VDD-0.1 | -     | -       | V    | $R_L=10k\Omega$                            |

| Maximum Output Voltage (Low)       | V <sub>OL</sub>   | 25°C        | -       | -     | VSS+0.1 | V    | $R_L=10k\Omega$                            |

| Large Signal Voltage Gain          | Av                | 25°C        | 60      | 95    | -       | dB   | $R_L=10k\Omega$                            |

| Input Common-mode<br>Voltage Range | V <sub>ICM</sub>  | 25°C        | 0       | -     | 3       | V    | VSS to VDD                                 |

| Common-mode Rejection Ratio        | CMRR              | 25°C        | 45      | 60    | -       | dB   | -                                          |

| Power Supply Rejection Ratio       | PSRR              | 25°C        | 60      | 80    | -       | dB   | -                                          |

| Output Source Current (Note 13)    | ISOURCE           | 25°C        | 1       | 2.4   | -       | mA   | OUT=VDD-0.4V                               |

| Output Sink Current (Note 13)      | I <sub>SINK</sub> | 25°C        | 2       | 4     | -       | mA   | OUT=VSS+0.4V                               |

| Slew Rate                          | SR                | 25°C        | -       | 2.4   | -       | V/ms | C <sub>L</sub> =25pF                       |

| Unity Gain Frequency               | f <sub>T</sub>    | 25°C        | -       | 4     | -       | kHz  | C <sub>L</sub> =25pF, A <sub>V</sub> =40dB |

| Phase Margin                       | θ                 | 25°C        | -       | 60    | -       | deg  | C <sub>L</sub> =25pF, A <sub>V</sub> =40dB |

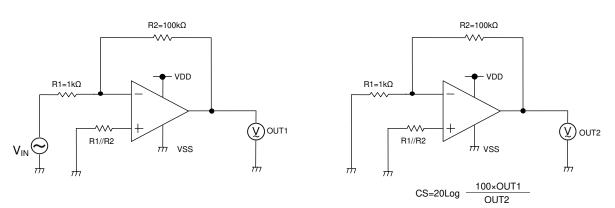

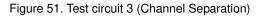

| Channel Separation                 | CS                | 25°C        | -       | 100   | -       | dB   | A <sub>v</sub> =40dB,<br>OUT=1Vrms         |

(Note 11) Absolute value

(Note 12) Full range BU7266: T<sub>A</sub>=-40°C to +85°C BU7266S: T<sub>A</sub>=-40°C to +105°C

(Note 13) Under the high temperature environment, consider the power dissipation of IC when selecting the output current. When the terminal short circuits are continuously output, the output current is reduced to climb to the temperature inside IC.

### **Description of Electrical Characteristics**

Described below are descriptions of the relevant electrical terms used in this datasheet. Items and symbols used are also shown. Note that item name and symbol and their meaning may differ from those on another manufacturer's document or general document.

### 1. Absolute maximum ratings

Absolute maximum rating items indicate the condition which must not be exceeded. Application of voltage in excess of absolute maximum rating or use out of absolute maximum rated temperature environment may cause deterioration of characteristics.

- Supply Voltage (VDD/VSS) Indicates the maximum voltage that can be applied between the VDD terminal and VSS terminal without deterioration or destruction of characteristics of internal circuit.

- (2) Differential Input Voltage (V<sub>ID</sub>)

Indicates the maximum voltage that can be applied between non-inverting and inverting terminals without damaging the IC.

- (3) Input Common-mode Voltage Range (V<sub>ICM</sub>) Indicates the maximum voltage that can be applied to the non-inverting and inverting terminals without deterioration or destruction of electrical characteristics. Input common-mode voltage range of the maximum ratings does not assure normal operation of IC. For normal operation, use the IC within the input common-mode voltage range characteristics.

- (4) Power Dissipation (P<sub>D</sub>) Indicates the power that can be consumed by the IC when mounted on a specific board at the ambient temperature 25°C (normal temperature). As for package product, P<sub>D</sub> is determined by the temperature that can be permitted by the IC in the package (maximum junction temperature) and the thermal resistance of the package.

### 2. Electrical characteristics

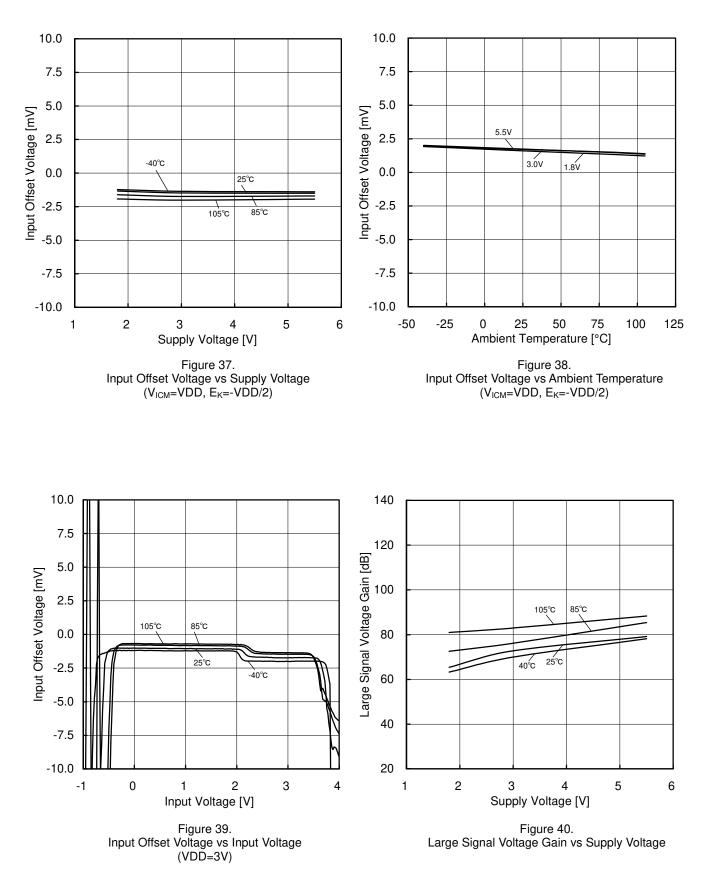

- Input Offset Voltage (V<sub>IO</sub>)

Indicates the voltage difference between non-inverting terminal and inverting terminals. It can be translated into the input voltage difference required for setting the output voltage at 0 V.

- (2) Input Offset Current (I<sub>IO</sub>) Indicates the difference of input bias current between the non-inverting and inverting terminals.

- (3) Input Bias Current (I<sub>B</sub>) Indicates the current that flows into or out of the input terminal. It is defined by the average of input bias currents at the non-inverting and inverting terminals.

- Supply Current (I<sub>DD</sub>)

Indicates the current that flows within the IC under specified no-load conditions.

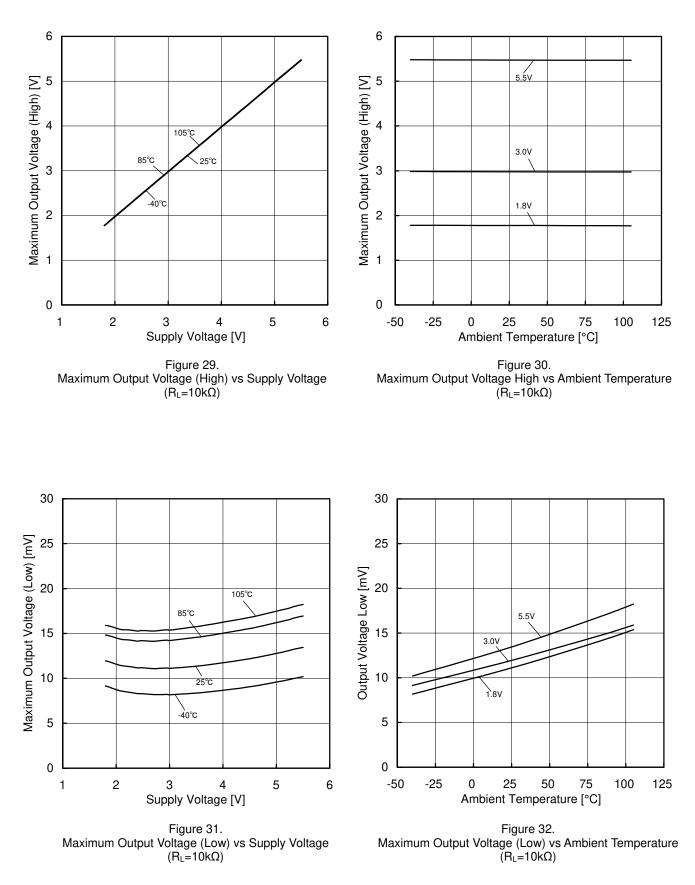

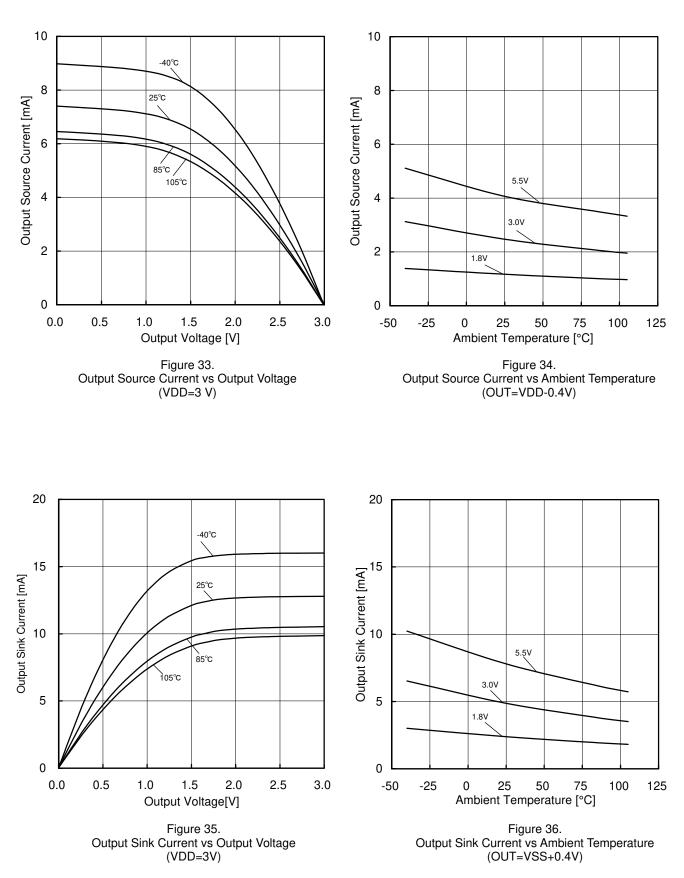

- (5) Maximum Output Voltage(High) / Maximum Output Voltage(Low) (V<sub>OH</sub>/V<sub>OL</sub>) Indicates the voltage range of the output under specified load condition. It is typically divided into maximum output voltage High and low. Maximum output voltage high indicates the upper limit of output voltage. Maximum output voltage low indicates the lower limit.

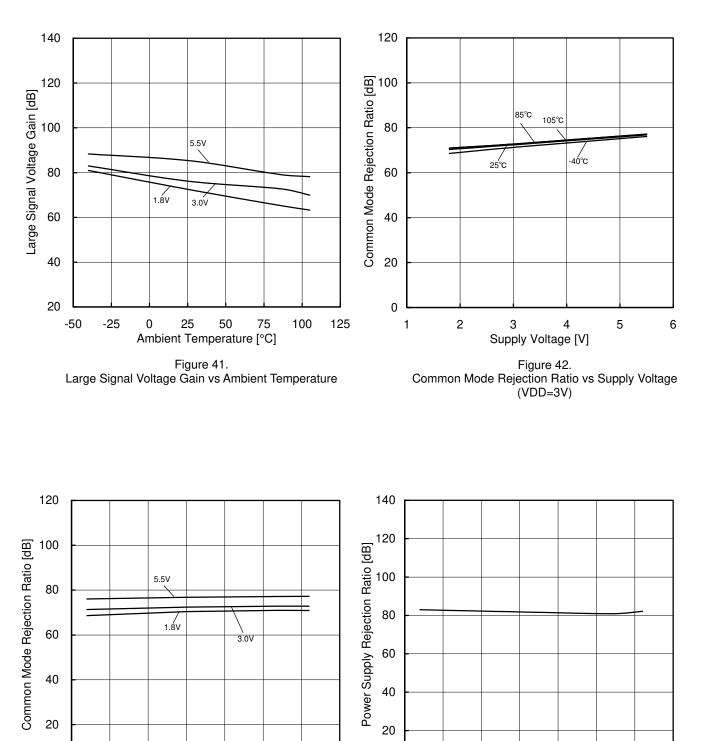

- (6) Large Signal Voltage Gain (A<sub>V</sub>)

Indicates the amplifying rate (gain) of output voltage against the voltage difference between non-inverting terminal and inverting terminal. It is normally the amplifying rate (gain) with reference to DC voltage.

Av = (Output voltage) / (Differential Input voltage)

- Input Common-mode Voltage Range (V<sub>ICM</sub>)

Indicates the input voltage range where IC normally operates.

- (8) Common-mode Rejection Ratio (CMRR) Indicates the ratio of fluctuation of input offset voltage when the input common mode voltage is changed. It is normally the fluctuation of DC. CMRR = (Change of Input common-mode voltage)/(Input offset fluctuation)

- (9) Power Supply Rejection Ratio (PSRR) Indicates the ratio of fluctuation of input offset voltage when supply voltage is changed. It is normally the fluctuation of DC. PSRR= (Change of power supply voltage)/(Input offset fluctuation)

- (10) Output Source Current/ Output Sink Current (I<sub>SOURCE</sub> / I<sub>SINK</sub>) The maximum current that can be output from the IC under specific output conditions. The output source current indicates the current flowing out from the IC, and the output sink current indicates the current flowing into the IC.

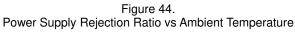

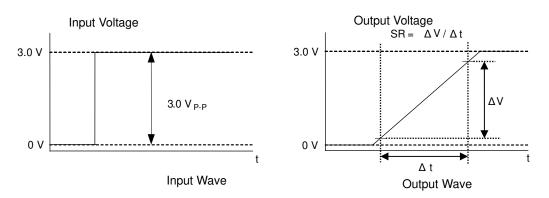

- (11) Slew Rate (SR) Indicates the ratio of the change in output voltage with time when a step input signal is applied.

- (12) Unity Gain Frequency (f<sub>T</sub>) Indicates a frequency where the voltage gain of operational amplifier is 1.

(13) Phase Margin (θ)

- Indicates the margin of phase from 180 degree phase lag at unity gain frequency.

- (14) Channel Separation (CS) Indicates the fluctuation in the output voltage of the driven channel with reference to the change of output voltage of the channel which is not driven.

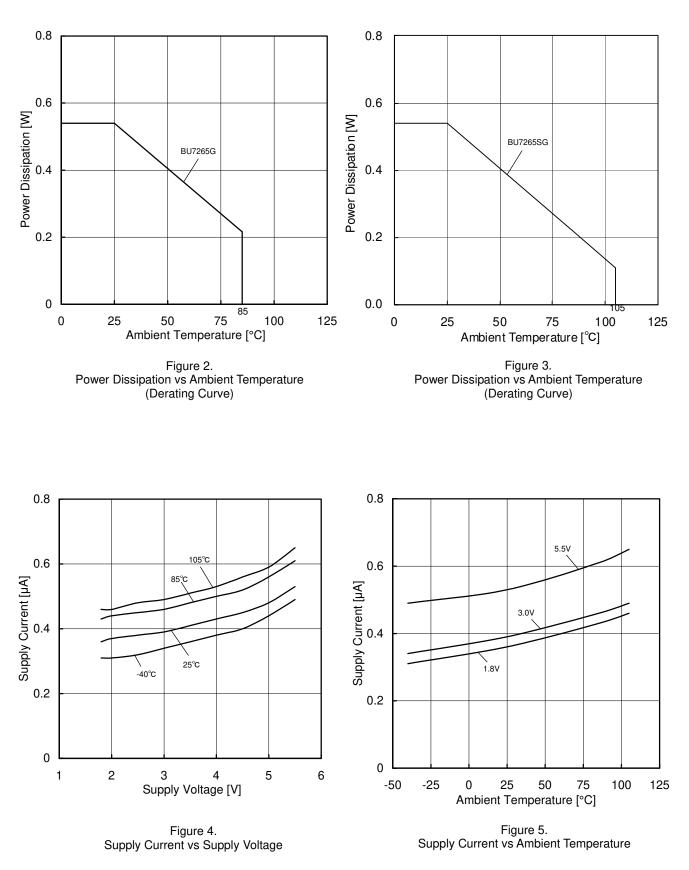

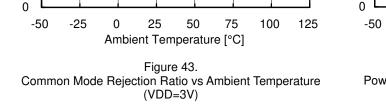

### **Typical Performance Curves**

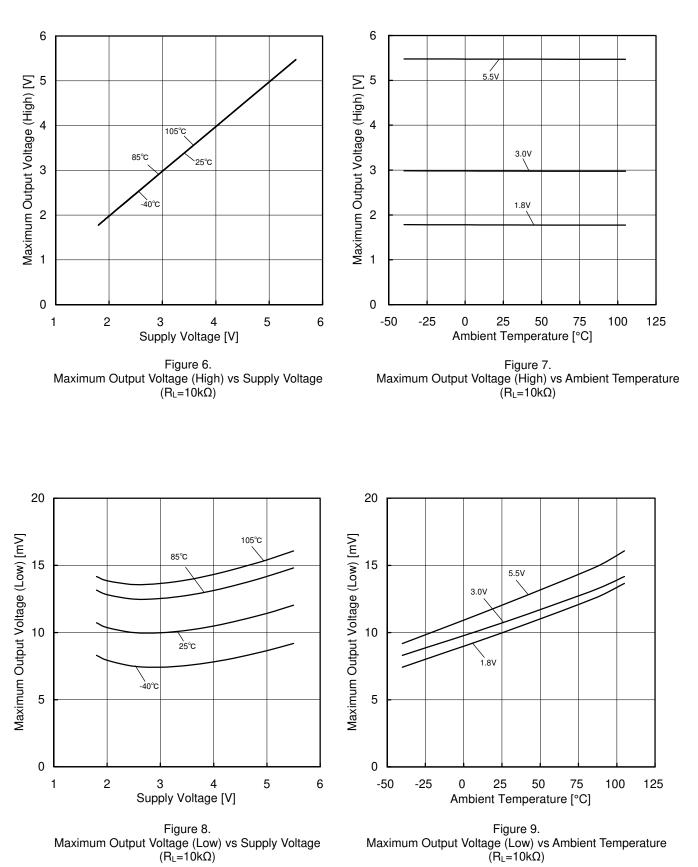

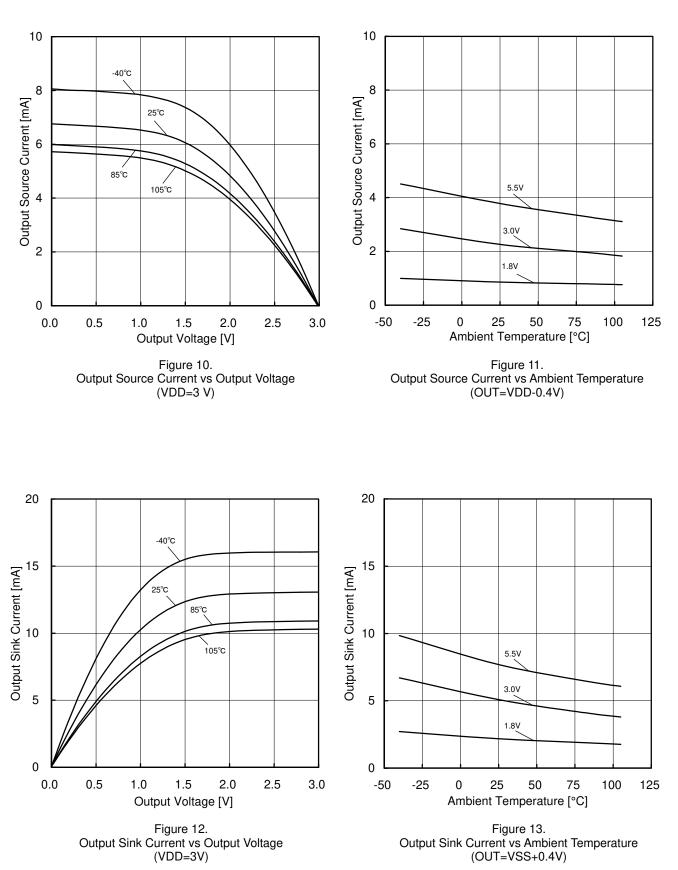

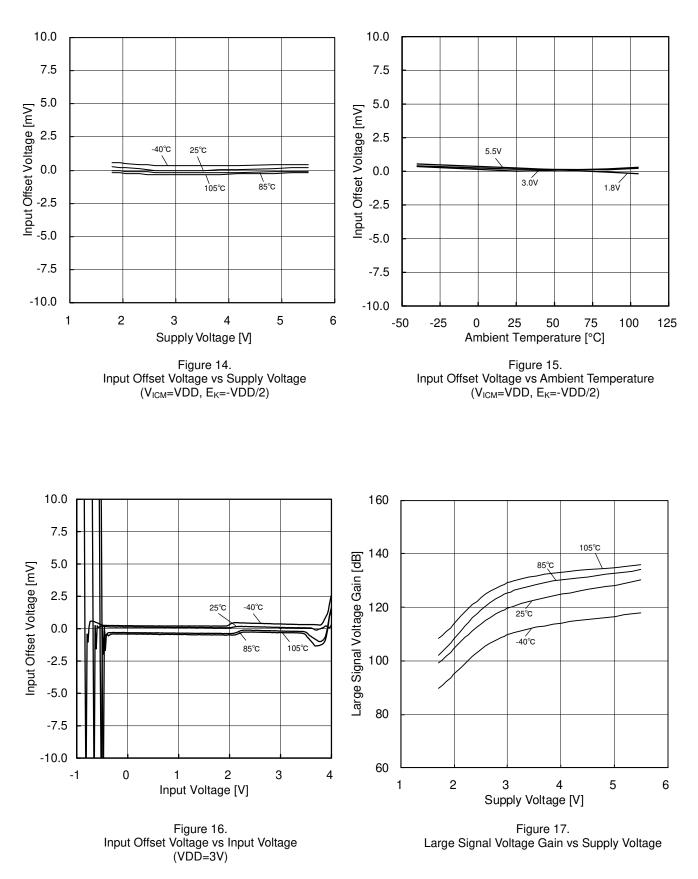

OBU7265G, BU7265SG

OBU7265G, BU7265SG

OBU7265G, BU7265SG

OBU7265G, BU7265SG

OBU7265G, BU7265SG

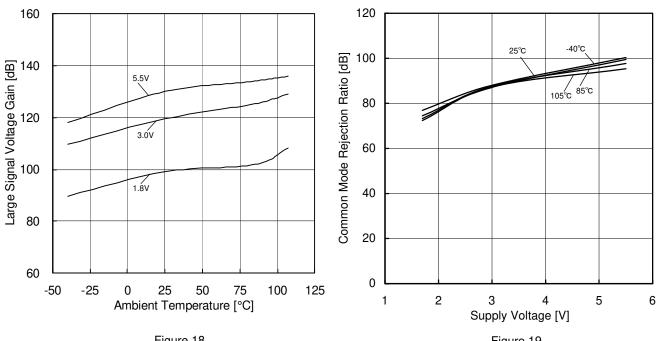

Figure 18. Large Signal Voltage Gain vs Ambient Temperature

Figure 19. Common Mode Rejection Ratio vs Supply Voltage

OBU7265G, BU7265SG

OBU7266xxx, BU7266Sxxx

OBU7266xxx, BU7266Sxxx

OBU7266xxx, BU7266Sxxx

OBU7266xxx, BU7266Sxxx

OBU7266xxx, BU7266Sxxx

Ambient Temperature [°C]

25

50

75

100

125

-25

0

O BU7266xxx, BU7266Sxxx

Voltage Gain • Phase vs Frequency

### Application Information

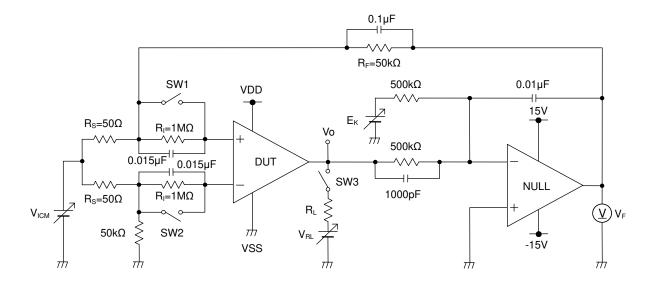

NULL method condition for Test circuit1

|                                   |                 |    |    |       |     | V   | DD, VSS | 5, E <sub>κ</sub> , V <sub>I</sub> | <sub>ICM</sub> Unit:V |

|-----------------------------------|-----------------|----|----|-------|-----|-----|---------|------------------------------------|-----------------------|

| Parameter                         | VF              | S1 | S2 | S3    | VDD | VSS | Eκ      | VICM                               | Calculation           |

| Input Offset Voltage              | $V_{\text{F1}}$ | ON | ON | OFF   | 3   | 0   | -1.5    | 3                                  | 1                     |

| Large Signal Voltage Gain         | V <sub>F2</sub> |    | ON | ON    | 3   | 0   | -0.5    | 1.5                                | 2                     |

|                                   | $V_{F3}$        | ON |    |       |     |     | -2.5    | 1.5                                |                       |

| Common-mode Rejection Ratio       | $V_{F4}$        | ON | ON | OFF   | 3   | 0   | -1.5    | 0                                  | 3                     |

| (Input Common-mode Voltage Range) | $V_{F5}$        | ON | ON | OFF   | 3   | 0   | -1.5    | 3                                  | 3                     |

| Power Supply Pajaction Patio      | $V_{F6}$        | ON | ON | OFF   | 1.8 | 0   | -0.9    | 0                                  | Λ                     |

| Power Supply Rejection Ratio      | $V_{F7}$        |    |    | N OFF | 5.5 |     | -0.9    | 0                                  | 4                     |

- Calculation -

1. Input Offset Voltage (V<sub>IO</sub>)

$$V_{IO} = \frac{|V_{F1}|}{1 + R_F/R_S} \quad [V]$$

$Av = 20Log \quad \frac{\Delta E_{\rm K} \times (1 + R_{\rm F}/R_{\rm S})}{|V_{\rm F2}{}^{-}V_{\rm F3}|} \quad [dB] \label{eq:average}$

3. Common-mode Rejection Ratio (CMRR)

$\label{eq:CMRR} CMRR = 20 Log \; \frac{\Delta \, V_{ICM} \times \, (1 + R_F/R_S)}{|V_{F4} - V_{F5}|} \quad [dB]$

4. Power Supply Rejection Ratio (PSRR)

$$\label{eq:PSRR} \begin{split} \text{PSRR} = 20 \text{Log} \; \frac{\Delta \, \text{VDD} \times (1 + \, R_{\text{F}}/R_{\text{S}})}{|V_{\text{F6}} - V_{\text{F7}}|} \quad [\text{dB}] \end{split}$$

Figure 48. Test Circuit 1 (One Channel Only)

### Application Information - continued

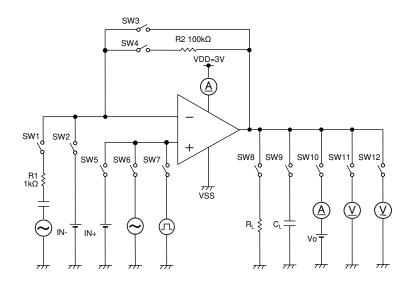

Switch Condition for Test circuit2

| SW No.                 | SW1 | SW2 | SW3 | SW4 | SW5 | SW6 | SW7 | SW8 | SW9 | SW10 | SW11 | SW12 |

|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|

| Supply Current         | OFF | OFF | ON  | OFF | ON  | OFF | OFF | OFF | OFF | OFF  | OFF  | OFF  |

| Maximum Output Voltage | OFF | ON  | OFF | OFF | ON  | OFF | OFF | ON  | OFF | OFF  | ON   | OFF  |

| Output Current         | OFF | ON  | OFF | OFF | ON  | OFF | OFF | OFF | OFF | ON   | OFF  | OFF  |

| Slew Rate              | OFF | OFF | ON  | OFF | OFF | OFF | ON  | OFF | ON  | OFF  | OFF  | ON   |

| Unity Gain Frequency   | ON  | OFF | OFF | ON  | ON  | OFF | OFF | OFF | ON  | OFF  | OFF  | ON   |

### Figure 49. Test Circuit 2

### Figure 50. Slew Rate Input and Output Wave

### **Examples of Circuit**

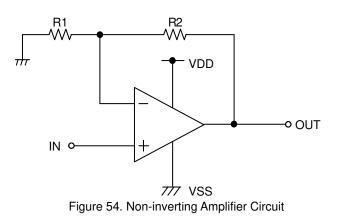

OVoltage Follower

Figure 52. Voltage Follower Circuit

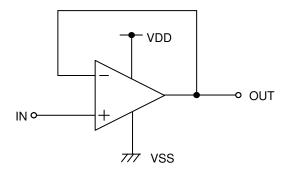

OInverting Amplifier

Figure 53. Inverting Amplifier Circuit

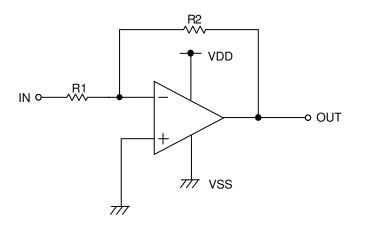

**ONon-inverting Amplifier**

Voltage gain is 0dB.

Using this circuit, the output voltage (OUT) is configured to be equal to the input voltage (IN). This circuit also stabilizes the output voltage (OUT) due to high input impedance and low output impedance. Computation for output voltage (OUT) is shown below.

OUT=IN

For inverting amplifier, input voltage (IN) is amplified by a voltage gain and depends on the ratio of R1 and R2. The out-of-phase output voltage is shown in the next expression

OUT=-(R2/R1) · IN

This circuit has input impedance equal to R1.

For non-inverting amplifier, input voltage (IN) is amplified by a voltage gain, which depends on the ratio of R1 and R2. The output voltage (OUT) is in-phase with the input voltage (IN) and is shown in the next expression.

$$OUT=(1 + R2/R1) \cdot IN$$

Effectively, this circuit has high input impedance since its input side is the same as that of the operational amplifier.

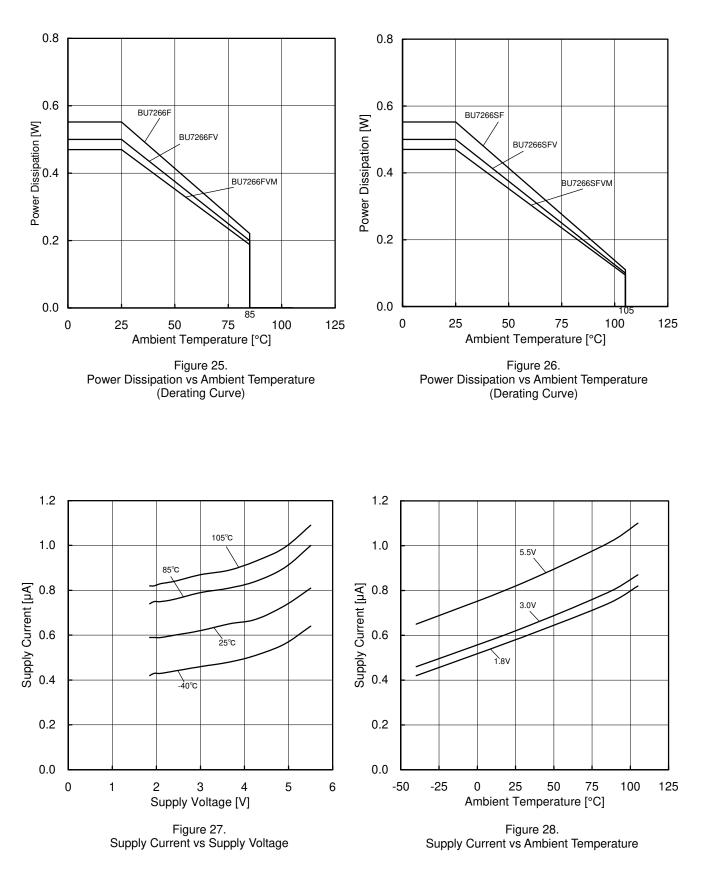

### **Power Dissipation**

Power dissipation (total loss) indicates the power that the IC can consume at  $T_A=25$ °C (normal temperature). As the IC consumes power, it heats up, causing its temperature to be higher than the ambient temperature. The allowable temperature that the IC can accept is limited. This depends on the circuit configuration, manufacturing process, and consumable power.

Power dissipation is determined by the allowable temperature within the IC (maximum junction temperature) and the thermal resistance of the package used (heat dissipation capability). Maximum junction temperature is typically equal to the maximum storage temperature. The heat generated through the consumption of power by the IC radiates from the mold resin or lead frame of the package. Thermal resistance, represented by the symbol  $\theta_{JA}$ °C/W, indicates this heat dissipation capability. Similarly, the temperature of an IC inside its package can be estimated by thermal resistance.

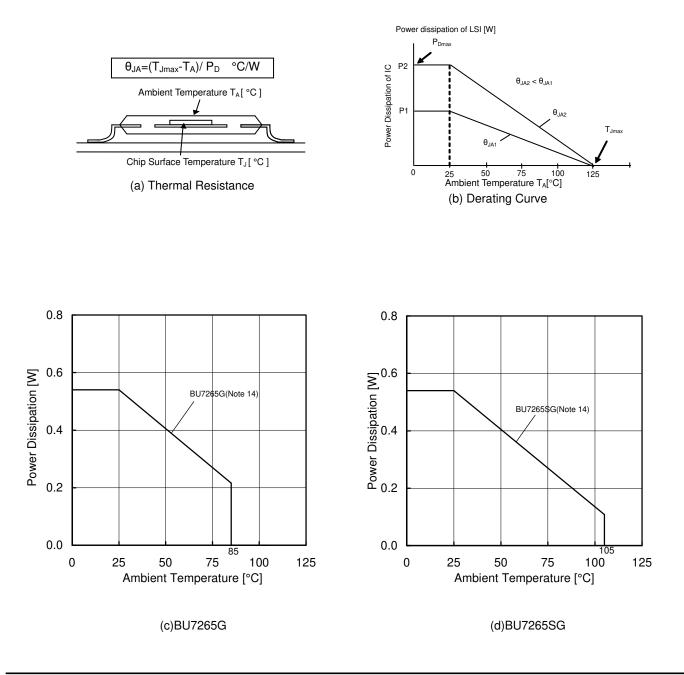

Figure 55 (a) shows the model of the thermal resistance of a package. The equation below shows how to compute for the Thermal resistance ( $\theta_{JA}$ ), given the ambient temperature ( $T_A$ ), maximum junction temperature ( $T_{Jmax}$ ), and power dissipation ( $P_D$ ).

$$\theta_{JA} = (T_{Jmax} - T_A) / P_D \circ C/W$$

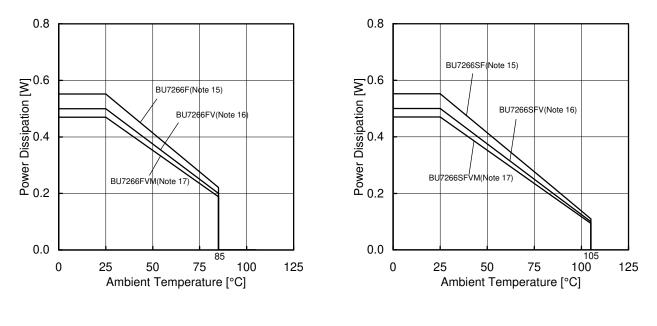

The derating curve in Figure 55 (b) indicates the power that the IC can consume with reference to ambient temperature. Power consumption of the IC begins to attenuate at certain temperatures. This gradient is determined by Thermal resistance ( $\theta_{JA}$ ), which depends on the chip size, power consumption, package, ambient temperature, package condition, wind velocity, etc. This may also vary even when the same of package is used. Thermal reduction curve indicates a reference value measured at a specified condition. Figure 55(c) to 55(f) shows an example of the derating curve for BU7265SG, BU7265SSG, BU7266Sxxx.

(e)BU7266F/FV/FVM

(f)BU7266SF/SFV/SFVM

| (Note 14) | (Note 15) | (Note 16) | (Note 17) | Unit  |

|-----------|-----------|-----------|-----------|-------|

| 5.4       | 5.5       | 5.0       | 4.7       | mW/°C |

| When using the unit above $T_A=25^{\circ}C$ , subtract the value above per Celsius degree. Power dissipation is the value |

|---------------------------------------------------------------------------------------------------------------------------|

| when FR4 glass epoxy board 70mm × 70mm × 1.6mm (copper foil area less than 3%) is mounted.                                |

Figure 55. Thermal Resistance and Derating Curve

### **Operational Notes**

### 1. Reverse Connection of Power Supply

Connecting the power supply in reverse polarity can damage the IC. Take precautions against reverse polarity when connecting the power supply, such as mounting an external diode between the power supply and the IC's power supply pins.

### 2. Power Supply Lines

Design the PCB layout pattern to provide low impedance supply lines. Separate the ground and supply lines of the digital and analog blocks to prevent noise in the ground and supply lines of the digital block from affecting the analog block. Furthermore, connect a capacitor to ground at all power supply pins. Consider the effect of temperature and aging on the capacitance value when using electrolytic capacitors.

### 3. Ground Voltage

Ensure that no pins are at a voltage below that of the ground pin at any time, even during transient condition.

### 4. Ground Wiring Pattern

When using both small-signal and large-current ground traces, the two ground traces should be routed separately but connected to a single ground at the reference point of the application board to avoid fluctuations in the small-signal ground caused by large currents. Also ensure that the ground traces of external components do not cause variations on the ground voltage. The ground lines must be as short and thick as possible to reduce line impedance.

### 5. Thermal Consideration

Should by any chance the power dissipation rating be exceeded the rise in temperature of the chip may result in deterioration of the properties of the chip. The absolute maximum rating of the  $P_D$  stated in this specification is when the IC is mounted on a 70mm x 70mm x 1.6mm glass epoxy board. In case of exceeding this absolute maximum rating, increase the board size and copper area to prevent exceeding the  $P_D$  rating.

### 6. Recommended Operating Conditions

These conditions represent a range within which the expected characteristics of the IC can be approximately obtained. The electrical characteristics are guaranteed under the conditions of each parameter.

### 7. Inrush Current

When power is first supplied to the IC, it is possible that the internal logic may be unstable and inrush current may flow instantaneously due to the internal powering sequence and delays, especially if the IC has more than one power supply. Therefore, give special consideration to power coupling capacitance, power wiring, width of ground wiring, and routing of connections.

### 8. Operation Under Strong Electromagnetic Field

Operating the IC in the presence of a strong electromagnetic field may cause the IC to malfunction.

### 9. Testing on Application Boards

When testing the IC on an application board, connecting a capacitor directly to a low-impedance output pin may subject the IC to stress. Always discharge capacitors completely after each process or step. The IC's power supply should always be turned off completely before connecting or removing it from the test setup during the inspection process. To prevent damage from static discharge, ground the IC during assembly and use similar precautions during transport and storage.

### 10. Inter-pin Short and Mounting Errors

Ensure that the direction and position are correct when mounting the IC on the PCB. Incorrect mounting may result in damaging the IC. Avoid nearby pins being shorted to each other especially to ground, power supply and output pin. Inter-pin shorts could be due to many reasons such as metal particles, water droplets (in very humid environment) and unintentional solder bridge deposited in between pins during assembly to name a few.

### 11. Unused Input Pins

Input pins of an IC are often connected to the gate of a MOS transistor. The gate has extremely high impedance and extremely low capacitance. If left unconnected, the electric field from the outside can easily charge it. The small charge acquired in this way is enough to produce a significant effect on the conduction through the transistor and cause unexpected operation of the IC. So unless otherwise specified, unused input pins should be connected to the power supply or ground line.

### **Operational Notes – continued**

### 12. Regarding the Input Pin of the IC

In the construction of this IC, P-N junctions are inevitably formed creating parasitic diodes or transistors. The operation of these parasitic elements can result in mutual interference among circuits, operational faults, or physical damage. Therefore, conditions which cause these parasitic elements to operate, such as applying a voltage to an input pin lower than the ground voltage should be avoided. Furthermore, do not apply a voltage to the input pins when no power supply voltage is applied to the IC. Even if the power supply voltage is applied, make sure that the input pins have voltages within the values specified in the electrical characteristics of this IC.

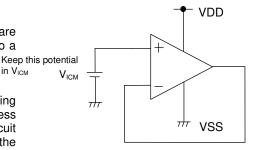

### 13. Unused circuits

When there are unused op-amps, it is recommended that they are connected as in Figure 58, setting the non-inverting input terminal to a potential within the in-phase input voltage range ( $V_{ICM}$ ).

### 14. Input Voltage

Applying VDD+0.3V to the input terminal is possible without causing deterioration of the electrical characteristics or destruction, regardless of the supply voltage. However, this does not ensure normal circuit operation. Please note that the circuit operates normally only when the input voltage is within the common mode input voltage range of the electric characteristics.

Figure 58. Example of Application Circuit for Unused Op-amp

### 15. Power supply(single/dual)

The operational amplifier operates when the voltage supplied is between VDD and VSS. Therefore, the single supply operational amplifiers can be used as dual supply operational amplifiers as well.

### 16. Output capacitor

If a large capacitor is connected between the output pin and VSS pin, current from the charged capacitor will flow into the output pin and may destroy the IC when the VDD pin is shorted to ground or pulled down to 0V. Use a capacitor smaller than 0.1uF between output pin and VSS pin.

### 17. Oscillation by output capacitor

Please pay attention to the oscillation by output capacitor and in designing an application of negative feedback loop circuit with these ICs.

#### 18. Latch Up

Be careful of input voltage that exceed the VDD and VSS. When CMOS device have sometimes occur latch up and protect the IC from abnormaly noise.

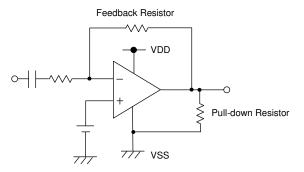

### 19. Crossorver distortion

Inverting amplifier generates crossover distortion when feedback resistance value is small. To suppress the crosover distortion, connect a resistor between the output terminal and VSS.

Figure 56. To Suppress the Crosover Distortion