Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Audio digital delay (KARAOKE echo) BU9252S / BU9252F

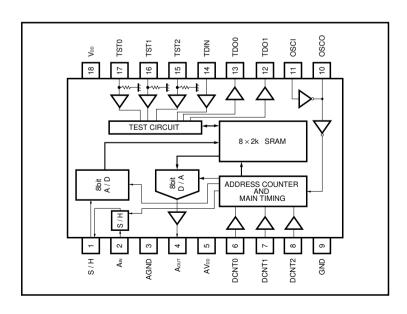

The BU9252S and BU9252F are digital delays specifically for Karaoke systems. Each has an internal sample hold circuit, an 8-bit A / D and D / A converter and 2kB SRAM, and allows for the selection of one of eight delay times just by attaching an inexpensive ceramic resonator.

A digital echo system can be formed by using either of these ICs together with the BA7725S or BA7725FS.

#### Applications

Karaoke echo system

Electronic circuits that require signal delays

#### Features

- 1) Internal digital delay circuit.

- 2) Internal 8-bit A / D converter. Sample rate. (14.22kHz when fosc = 455kHz).

- 3) Internal 2k bytes data SRAM.

- 4) Internal 8-bit D / A converter.

- 5) CMOS design for low power consumption.

- 6) Internal sample hold circuit.

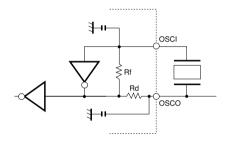

- Internal feedback resistors and capacitors for oscillator circuits.

#### Block diagram

# Pin descriptions

| Pin No. | Pin name         | Function                                | Pin No. | Pin name        | Function                     |

|---------|------------------|-----------------------------------------|---------|-----------------|------------------------------|

| 1       | S/H              | For attaching sample-and-hold capacitor | 10      | osco            | Oscillator pin 2             |

| 2       | Aın              | Analog input                            | 11      | OSCI            | Oscillator pin 1             |

| 3       | AGND             | Analog circuit ground                   | 12      | TDO1            | Test pin (output)            |

| 4       | Аоит             | Analog output                           | 13      | TDO0            | Test pin (output)            |

| 5       | AV <sub>DD</sub> | Analog circuit power supply             | 14      | TDIN            | Test pin (input)             |

| 6       | DCNT0            | Delay setting input                     | 15      | TST2            | Test mode setting            |

| 7       | DCNT1            | Delay setting input                     | 16      | TST1            | Test mode setting            |

| 8       | DCNT2            | Delay setting input                     | 17      | TST0            | Test mode setting            |

| 9       | GND              | Digital circuit ground                  | 18      | V <sub>DD</sub> | Digital circuit power supply |

# •Input / output circuits

| Pin name               | Pin No.           | Internal equivalent circuit | Pin name     | Pin No.  | Internal equivalent circuit                       |  |

|------------------------|-------------------|-----------------------------|--------------|----------|---------------------------------------------------|--|

| S/H                    | 1                 |                             |              |          | Т                                                 |  |

| Ain                    | 2                 |                             | OSCI<br>OSCO | 11<br>10 |                                                   |  |

| TDIN DCNT0 DCNT1 DCNT2 | 14<br>6<br>7<br>8 |                             |              |          |                                                   |  |

| TDO0<br>TDO1           | 13<br>12          |                             | Аоит         | 4        | D/A                                               |  |

| TST0<br>TST1<br>TST2   | 17<br>16<br>15    |                             |              |          | Built-in 0.875x<br>amplifier as<br>output buffer. |  |

# • Absolute maximum ratings (Ta = 25°C)

| Parameter            |         | Symbol          | Limits                        | Unit |

|----------------------|---------|-----------------|-------------------------------|------|

| Power supply voltage |         | V <sub>DD</sub> | <b>−</b> 0.3 ~ <b>+</b> 7.0   | V    |

| Power dissipation    | BU9252S | Dd              | 600*1                         | \/   |

|                      | BU9252F | Pd              | 450*²                         | mW   |

| Storage temperature  |         | Tstg            | <b>−</b> 55 ~ + 125           | °C   |

| Input voltage        |         | Vin             | - 0.3 ~ V <sub>DD</sub> + 0.3 | V    |

| Output voltage       |         | Vоит            | - 0.3 ~ V <sub>DD</sub> + 0.3 | V    |

<sup>\*1</sup> IC only. Reduce by – 6mW / °C for each in Ta of 1°C over 25°C.

# Recommended operating conditions

| Parameter                   | Symbol          | Limits                               | Unit |

|-----------------------------|-----------------|--------------------------------------|------|

| Power supply voltage        | V <sub>DD</sub> | 4.5 ~ 5.5                            | V    |

| Analog power supply voltage | AVDD            | V <sub>DD</sub>                      | V    |

| Input "L" voltage           | VIL             | 0.0 ~ 0.2V <sub>DD</sub>             | V    |

| Input "H" voltage           | ViH             | 0.8V <sub>DD</sub> ~ V <sub>DD</sub> | V    |

| Analog input voltage        | Vain            | 0 ~ AVDD                             | V    |

| Clock frequency             | fosc            | 200 ~ 1000                           | kHz  |

| Operating temperature       | Topr            | <b>−</b> 10 ~ + 70                   | °C   |

# ● Electrical characteristics (unless otherwise noted, Ta = 25°C, VDD = AVDD = 5V)

| Parameter                  | Symbol | Min. | Тур. | Max. | Unit | Conditions                 |

|----------------------------|--------|------|------|------|------|----------------------------|

| Supply current             | ldd    | _    | 3.5  | 12   | mA   | Vain = AVDD, fosc = 455kHz |

| Analog output current      | Іаоит  | 1    | 4    | _    | mA   | VAOUT = 1V, VAIN = 0V      |

| Analog output current      |        | 0.3  | 0.8  | _    | mA   | VAOUT = 0.5VDD, VAIN = VDD |

| Analog input impedance     | Rain   | 12   | 25   | 60   | kΩ   | *                          |

| A / D to D / A precision   | RES    | _    | 2    | _    | LSB  |                            |

| OSCO output "L" voltage    | VLOSC  | _    | 0.6  | 1.2  | V    | IoL = 100μA                |

| OSCO output "H" voltage    | VHOSC  | 3.8  | 4.4  | _    | V    | Ioн = - 100μA              |

| OSCI feedback loop current | losci  | 1    | 6    | 20   | μΑ   | Vosci = VDD                |

| Oscillation capacity       | _      | _    | 150  | _    | pF   |                            |

st The bias circuit is impedance.

<sup>\*2</sup> IC only. Reduce by -4.5mW / °C for each in Ta of 1°C over 25°C.

#### Circuit operation

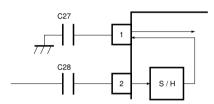

### (1) External capacitor for signal input pin

Audio signals compressed by the BA7725S or BA7725FS have their DC component removed by an AC coupling capacitor and are then input to pin 2 of BU9252S or BU9252F. At this stage, level deviations occur because the input signal is capacitor-divided by this AC coupling capacitor C28 and by sampling hold capacitor C27 connected to pin 1.

To prevent this, make sure that C27 is much lower than C28.

(Note: The numbers of external components are the numbers used in the system application example.)

The sample-held analog signal is converted to digital by the serial 8-bit A / D converter and then temporarily stored in the internal SRAM (2k bytes).

(2) Relationship between oscillation frequency (CLK) and delay time

Sample rate F = fosc / 32 (fosc: oscillation frequency)

F = 14.22kHz at fosc = 455kHz

Sample period T = 1 / F

Delay time Dtime =  $T \times$  number of counts

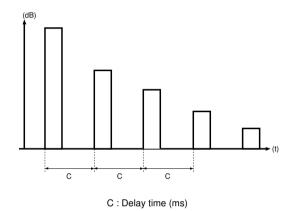

### (3) Delay timer settings

The delay time (i.e., the length of time the signal is stored in the SRAM) can be set to any of eight settings between the maximum and minimum delay times by setting pins 6, 7 and 8 to the combination of logic signal inputs that results in the corresponding number of counts. The maximum and minimum delay times are determined by the oscillation frequency of the attached ceramic resonator.

The delay time can be set to any of the eight settings shown below by setting the logic inputs of terminals DCNT0 through DCNT2.

|       | Logic input |       | Count       | Delay time (ms) (when fosc = 455kHz) |

|-------|-------------|-------|-------------|--------------------------------------|

| DCNT1 | DCNT2       | DCNT0 | BU9252S / F | BU9252S / F                          |

| 0     | 0           | 0     | 256         | 18.00                                |

| 0     | 0           | 1     | 512         | 36.01                                |

| 0     | 1           | 0     | 768         | 54.01                                |

| 0     | 1           | 1     | 1024        | 72.02                                |

| 1     | 0           | 0     | 1280        | 90.02                                |

| 1     | 0           | 1     | 1536        | 108.03                               |

| 1     | 1           | 0     | 1792        | 126.03                               |

| 1     | 1           | 1     | 2048        | 144.04                               |

Maximum and minimum delay times when using 300kHz, 375kHz and 455kHz ceramic oscillators

| Delay time (ms) |           |        |       |        |       |  |  |  |

|-----------------|-----------|--------|-------|--------|-------|--|--|--|

| 300             | kHz       | 375    | kHz   | 455kHz |       |  |  |  |

| Max.            | Max. Min. |        | Min.  | Max.   | Min.  |  |  |  |

| 218.45          | 27.30     | 174.76 | 21.85 | 144.04 | 18.00 |  |  |  |

(4) Peripheral components of the ceramic oscillator An oscillator circuit can be configured simply by attaching a 455kHz ceramic resonator.

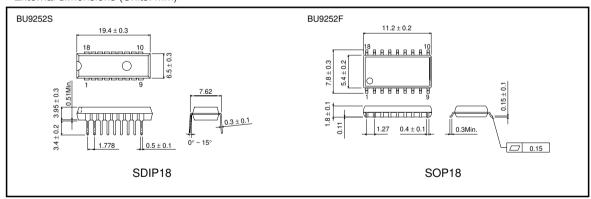

## External dimensions (Units: mm)