Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Structure Silicon Monolithic Integrated Circuit

Product Name IrDA Controller LSI built-in Ir remote control

Model name BU92747GUW

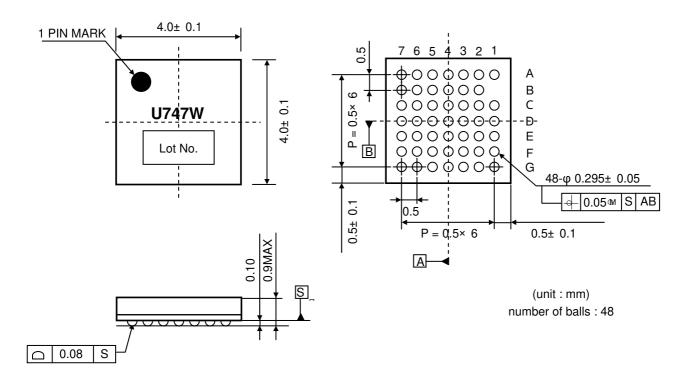

Outer Dimension Figure 1 Outer Dimensions

Features • Data transfer speed (bps)

IrDA SIR: 2.4kbps, 9.6kbps, 19.2kbps, 38.4kbps, 57.6kbps and 115.2kbps

IrDA MIR: 0.576Mbps, 1.152Mbps

IrDA FIR: 4Mbps

IrSimple

Interface

16-bit data bus ,  $Address A_{0-3}$

- Built-in 2560 × 2byte FIFO buffer (for transmission and reception)

- · Accessible as a memory device connected to the bus

- · Power down mode setting possible for transmission and reception

- Input clock of 48MHz for external input clock and crystal input clock

- Ir remote control function Serial 2-lines SDA, and SCL

# • Absolute Maximum Rating

Ta=25°C unless otherwise stated

| Item                                    | Symbol           | Minimum | Maximum                  | Unit |

|-----------------------------------------|------------------|---------|--------------------------|------|

| Supply voltage <sup>*1</sup>            | $V_{DD}$         | -0.3    | 2.5                      | V    |

| Interface supply voltage1*1             | V <sub>IO1</sub> | -0.3    | 4.5                      | V    |

| Interface supply voltage2 <sup>*1</sup> | V <sub>IO2</sub> | -0.3    | 4.5                      | V    |

| Input voltage <sup>*1</sup>             | V <sub>IN</sub>  | -0.3    | V <sub>IO1, 2</sub> +0.3 | V    |

| Power dissipation*2                     | Pd               | -       | 800                      | mW   |

| Operating temperature range             | T <sub>OPR</sub> | -40     | 85                       | °C   |

| Storage temperature range               | T <sub>STG</sub> | -55     | 125                      | °C   |

<sup>\*1</sup> It applies to all pins based on the GND pin.

# Operation Range

| Item                                   | Symbol           | Minimum | Standard | Maximum | Unit |

|----------------------------------------|------------------|---------|----------|---------|------|

| Supply voltage                         | $V_{DD}$         | 1.62    | 1.8      | 1.98    | V    |

| Interface supply voltage1              | V <sub>IO1</sub> | 1.62    | 1.8      | 3.6     | V    |

| Interface supply voltage2 <sup>3</sup> | $V_{IO2}$        | 1.62    | 1.8      | 3.6     | V    |

<sup>\*3</sup>  $V_{IO2}$  is connected with XIN/CLK48M, XOUT,  $\overline{PWDN}$ ,  $\overline{NIRQ}$  and  $\overline{RESET}$ .

Status of this document

The Japanese version of this document is the formal specification.

A customer may use this translation version only for a reference to help reading the formal version.

If there are any differences in translation version of this document, formal version takes priority.

<sup>\*</sup>This LSI chip is not subject to radiation-proof design.

<sup>\*2</sup> measured value with conformity substrate to SEMI (114.3mm× 76.2mm× 1.6mm、 4layer) 8.0mW/°C decrease over Ta=25°C use

# • Electrical Characteristics (DC Characteristics)

Ta=25°C,  $V_{DD}$ =1.8V,  $V_{IO1}$ =1.8V,  $V_{IO2}$ =1.8V and GND=0V unless otherwise stated

| Item                                | Symbol            | Standard value       |     |                      | Unit | Remarks                                                                         |  |

|-------------------------------------|-------------------|----------------------|-----|----------------------|------|---------------------------------------------------------------------------------|--|

| цеш                                 | Symbol            | MIN                  | TYP | MAX                  | Uill | nemarks                                                                         |  |

| Dissipation current 1               | I <sub>DD</sub> 1 | -                    | 0.1 | 10                   | μΑ   | For input with no output load = 0V                                              |  |

| Dissipation current 2               | I <sub>DD</sub> 2 | -                    | 10  | 30                   | mA   | For XIN = 48MHz                                                                 |  |

| Digital high-level input voltage    | V <sub>IH</sub>   | $0.75 \times V_{IO}$ | -   | -                    | V    |                                                                                 |  |

| Digital low-level input voltage     | V <sub>IL</sub>   | -                    | -   | $0.25 \times V_{IO}$ | V    |                                                                                 |  |

| District bink level in the contract | I <sub>IH</sub>   | -                    | -   | 10                   | μΑ   | Input voltage level 1.8V                                                        |  |

| Digital high-level input current    |                   | -                    | -   | 100                  | μΑ   | Input voltage level 1.8V TEST1-3                                                |  |

| Digital low-level input current     | I <sub>IL</sub>   | -                    | -   | 10                   | μΑ   | Input voltage level GND                                                         |  |

| Digital high-level output voltage   | V <sub>OH</sub>   | V <sub>IO</sub> -0.6 | -   | -                    | V    | INTR, D <sub>0-15</sub> , IrDAPWDOWN,<br>IrTX, IrRC, NIRQ, CTLA<br>IOH=-1mA     |  |

| Digital low-level output voltage    | V <sub>OL</sub>   | -                    | -   | 0.6                  | V    | INTR, D <sub>0-15</sub> , IrDAPWDOWN,<br>IrTX, IrRC, SDA, NIRQ, CTLA<br>IOL=1mA |  |

# • Pin Description

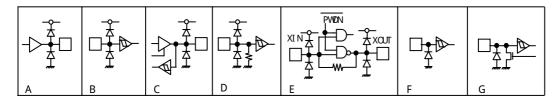

| Pin name          | I/O | Condition<br>of after<br>reset | Pin Function                                                                                                                                                                                                                                                                                                                                                                             | Circuit<br>Diagram |  |  |  |

|-------------------|-----|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|--|

| IrRX              | I   | -                              | IrDA Receive Input Pin                                                                                                                                                                                                                                                                                                                                                                   | В                  |  |  |  |

| EXTIR             | ı   | -                              | Signal Input Pin in SM2="H" (Input Signal is outputted to IrTX or IrRC)                                                                                                                                                                                                                                                                                                                  | В                  |  |  |  |

| IrTX              | 0   | L                              | IrDA and remote control Transmission Output Pin Transmission IrDA when RC_EN= "L" Transmission remote control when RC_EN="H", RC_MODE="H"                                                                                                                                                                                                                                                | Α                  |  |  |  |

| D <sub>0-15</sub> | 1/0 | Input                          | Data I/O Pin                                                                                                                                                                                                                                                                                                                                                                             | С                  |  |  |  |

| A <sub>0-3</sub>  | I   | -                              | Address Input Pin                                                                                                                                                                                                                                                                                                                                                                        | В                  |  |  |  |

| CS                | I   | -                              | Chip Select Pin. Low (L) Active The read/write signal goes "Active" in a Low period.                                                                                                                                                                                                                                                                                                     | В                  |  |  |  |

| RD                | I   | -                              | Read Signal Input Pin. Low (L) Active                                                                                                                                                                                                                                                                                                                                                    | В                  |  |  |  |

| WR                | I   | -                              | Write Signal Input Pin. Low (L) Active                                                                                                                                                                                                                                                                                                                                                   | В                  |  |  |  |

| ĪNTR              | 0   | Н                              | CPU Interrupt Request Output Pin (IrDA controller) The signal goes "Low" when an interrupt condition takes place.                                                                                                                                                                                                                                                                        | Α                  |  |  |  |

| RESET             | I   | -                              | Reset Input Pin. Low (L) Active The signal causes the internal register settings, etc. to be initialized.                                                                                                                                                                                                                                                                                | В                  |  |  |  |

| PWDN              | I   | -                              | Power Down Mode Setting. Low (L) Active When set to Low (L), this signal causes the wait status and sets the low dissipation current mode. After the power down mode is removed, RESET=L must set to Low until crystal clock oscillation becomes stable (about 2 or 3 ms). After that RESET must set to High. Take it into consideration that this period depends on the crystal in use. |                    |  |  |  |

| IrRC              | 0   | L                              | Remote control transmission Output pin Transmission remote control when RC_EN= "H", RC_MODE= "L"                                                                                                                                                                                                                                                                                         | Α                  |  |  |  |

| CTLA              | 0   | L                              | Control Signal Output Pin                                                                                                                                                                                                                                                                                                                                                                | Α                  |  |  |  |

| SCL               | I   | -                              | Serial clock                                                                                                                                                                                                                                                                                                                                                                             | F                  |  |  |  |

| SDA               | I/O | Input                          | Serial data I/O Pin                                                                                                                                                                                                                                                                                                                                                                      | G                  |  |  |  |

| NIRQ              | 0   | Н                              | CPU Interrupt Request Output Pin (Ir remote control) The signal goes "Low" when an interrupt condition takes place.                                                                                                                                                                                                                                                                      | Α                  |  |  |  |

| XIN/CLK48M        | I   | ı                              | Crystal IN / External CLK Input                                                                                                                                                                                                                                                                                                                                                          | Е                  |  |  |  |

| XOUT              | 0   | -                              | Crystal OUT (N.C when external input clock is used)                                                                                                                                                                                                                                                                                                                                      | Е                  |  |  |  |

| TEST1-3           | I   | 1                              | Test pins (These pins must be GND during normal operation.)                                                                                                                                                                                                                                                                                                                              | D                  |  |  |  |

| IrDA<br>PWDOWN    | 0   | Н                              | IrDA module control signal output pin These pins must be OPEN for IrDA modules having no power-down pin.                                                                                                                                                                                                                                                                                 | Α                  |  |  |  |

| $V_{DD}$          | -   |                                | Power supply pin                                                                                                                                                                                                                                                                                                                                                                         | -                  |  |  |  |

| $V_{IO1}$         | -   | -                              | Interface power supply voltage1                                                                                                                                                                                                                                                                                                                                                          | -                  |  |  |  |

| $V_{IO2}$         | -   | -                              | Interface power supply voltage2                                                                                                                                                                                                                                                                                                                                                          | -                  |  |  |  |

| GND               | -   | -                              | Ground pin                                                                                                                                                                                                                                                                                                                                                                               | -                  |  |  |  |

# • Equivalent Circuit Diagram

# • Outer Dimensions

Figure 1 Outer Dimensions (VBGA048W040)

VBGA048W040 Land Matrix Table

| BGA040W040 Land Matrix Table |          |                    |           |                    |                       |                    |          |  |  |

|------------------------------|----------|--------------------|-----------|--------------------|-----------------------|--------------------|----------|--|--|

| Land<br>Matrix No.           | Pin Name | Land<br>Matrix No. | Pin Name  | Land<br>Matrix No. | Pin Name              | Land<br>Matrix No. | Pin Name |  |  |

| A1                           | PWDN     | C1                 | $V_{IO2}$ | E1                 | $A_2$                 | G1                 | GND      |  |  |

| A2                           | XOUT     | C2                 | NIRQ      | E2                 | <b>A</b> <sub>1</sub> | G2                 | $D_5$    |  |  |

| A3                           | SCL      | C3                 | RESET     | E3                 | $A_0$                 | G3                 | $D_4$    |  |  |

| A4                           | IrRC     | C4                 | (NC)      | E4                 | D <sub>15</sub>       | G4                 | $D_3$    |  |  |

| <b>A</b> 5                   | IrTX     | C5                 | EXTIR     | E5                 | D <sub>14</sub>       | G5                 | $D_2$    |  |  |

| A6                           | IrRX     | C6                 | $V_{IO1}$ | E6                 | D <sub>13</sub>       | G6                 | $D_1$    |  |  |

| A7                           | GND      | C7                 | RD        | E7                 | D <sub>12</sub>       | G7                 | $D_0$    |  |  |

| (NC)                         | (NC)     | D1                 | $V_{IO1}$ | F1                 | D <sub>11</sub>       |                    |          |  |  |

| B2                           | XIN      | D2                 | $A_3$     | F2                 | $V_{DD}$              |                    |          |  |  |

| B3                           | SDA      | D3                 | TEST1     | F3                 | D <sub>10</sub>       |                    |          |  |  |

| B4                           | CTLA     | D4                 | TEST2     | F4                 | $D_9$                 |                    |          |  |  |

| B5                           | IrDAPWDN | D5                 | TEST3     | F5                 | D <sub>8</sub>        |                    |          |  |  |

| B6                           | $V_{DD}$ | D6                 | INTR      | F6                 | $D_7$                 |                    |          |  |  |

| B7                           | WR       | D7                 | CS        | F7                 | D <sub>6</sub>        |                    |          |  |  |

#### Notes for use

# (1) Absolute maximum ratings

Use of the IC in excess of absolute maximum ratings such as the applied voltage or operating temperature range may result in IC damage. Assumptions should not be made regarding the state of the IC (short mode or open mode) when such damage is suffered. A physical safety measure such as a fuse should be implemented when use of the IC in a special mode where the absolute maximum ratings may be exceeded is anticipated.

## (2) Mutual impedance

Use short and wide wiring tracks for the power supply and ground to keep the mutual impedance as small as possible .Use a capacitor to keep ripple to a minimum.

# (3) GND potential

Ensure a minimum GND pin potential in all operating conditions.

# (4) Short circuit mode between terminals and wrong mounting

In order to mount the IC on a set PCB, pay thorough attention to the direction and offset of the ICs. Erroneous mounting can destroy the IC. Furthermore, if a short circuit occurs due to foreign matters entering between terminals or between the terminal and the power supply or the GND terminal, the IC can destroy

#### (5) Setting of heat

Use a thermal design that allows for a sufficient margin in light of the power dissipation (Pd) in actual operating conditions.

## (6) Actions in strong magnetic field

Use caution when using the IC in the presence of a strong magnetic field as doing so may cause the IC to malfunction.

# (7) Ground Wiring Pattern

When using both small signal and large current GND patterns, it is recommended to isolate the two ground patterns, placing a single ground point at the application's reference point so that the pattern wiring resistance and voltage variations caused by large currents do not cause variations in the small signal ground voltage. Be careful not to change the GND wiring pattern of any external components, either.

(8) When power is first supplied the CMOS IC, it is possible that the internal logic may be unstable and rush current may flow instantaneously.

Therefore, give special consideration to power coupling capacitance, power wiring, width of GND wiring, and routing of connections.

(9) For ICs with more than one power, it is possible than rush current many flow instantaneously due to the internal powering sequence and delays.

Therefore, give special consideration to power coupling capacitance, power wiring, width of GND wiring, and routing of wiring.

### Notes

No copying or reproduction of this document, in part or in whole, is permitted without the consent of ROHM CO LTD

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing ROHM's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from ROHM upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, ROHM shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM and other parties. ROHM shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products are not designed to be radiation tolerant.

While ROHM always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. ROHM shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). ROHM shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Thank you for your accessing to ROHM product informations.

More detail product informations and catalogs are available, please contact your nearest sales office.

**ROHM** Customer Support System

THE AMERICAS / EUROPE / ASIA / JAPAN

www.rohm.com

Contact us : webmaster@rohm.co.jp

Copyright © 2008 ROHM CO.,LTD.

ROHM CO., LTD. 21 Saiin Mizosaki-cho, Ukyo-ku, Kyoto 615-8585, Japan

TEL:+81-75-311-2121 FAX:+81-75-315-0172