# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **ON Semiconductor®**

## CAT25C128/256

OGENFR

FAD FRE RoHS Compliance

## 128K/256K-Bit SPI Serial CMOS EEPROM

- 5 MHz SPI Compatible

- 1.8 to 5.5 Volt Operation

- Hardware and Software Protection

- Low Power CMOS Technology

- SPI Modes (0,0 &1,1)

- Industrial and Automotive **Temperature Ranges**

- Self-Timed Write Cycle

- 64-Byte Page Write Buffer

- Block Write Protection

- Protect 1/4, 1/2 or all of EEPROM Array

- 100,000 Program/Erase Cycles

- 100 Year Data Retention

- RoHS-compliant packages

#### DESCRIPTION

The CAT25C128/256 is a 128K/256K-Bit SPI Serial CMOS EEPROM internally organized as 16Kx8/32Kx8 bits. Catalyst's advanced CMOS Technology substantially reduces device power requirements. The CAT25C128/256 features a 64-byte page write buffer. The device operates via the SPI bus serial interface and is enabled through a Chip Select ( $\overline{CS}$ ). In addition to the Chip Select, the clock input (SCK), data in (SI) and data out (SO) are required to access the device.

#### **PIN CONFIGURATION**

|                                                                                                        | -                                                                                                   |                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOIC Package                                                                                           | TSSOP Pa                                                                                            | ckage (Y14)**                                                                                                                                         |

| (V**, X)     CS   -1   8   V <sub>CC</sub> SO   2   7   HOLD     WP   3   6   SCK     VSS   4   5   SI | CS                                                                                                  | 14 77 V <sub>CC</sub><br>13 77 HOLD<br>12 77 NC<br>11 77 NC<br>10 77 NC<br>9 77 SCK<br>8 77 SI                                                        |

| DIP Package (L)                                                                                        | TSSOP Pa                                                                                            | ckage (Y20)**                                                                                                                                         |

| CS -1 8 V <sub>CC</sub> 2 7 HOLD   WP 3 6 SCK   SS 4 5 SI   **CAT25C128 only.                          | NC 1 2<br>SO 1 4<br>NC 1 5<br>NC 1 6<br>WP 1 6<br>WP 1 7<br>VSS 1 8<br>NC 1 9<br>SO 1 9<br>SO 1 1 6 | 20 \[ \] NC<br>19 \[ \] V <sub>CC</sub><br>18 \[ \] HOLD<br>17 \[ \] HOLD<br>16 \[ \] NC<br>15 \[ \] SCK<br>13 \[ \] SI<br>12 \[ \] NC<br>11 \[ \] NC |

| PIN FUNCTIONS                                                                                          | NC 🗔 10                                                                                             |                                                                                                                                                       |

#### PIN FUNCTIONS Pin Name Function SO Serial data Output SCK Serial Clock WP Write Protect $V_{cc}$ Power Supply $\overline{\mathsf{V}}_{\mathsf{s}}$ Ground CS Chip Select SI Serial Data Input HOLD Suspends Serial Input NC No Connect

The HOLD pin may be used to suspend any serial communication without resetting the serial sequence. The CAT25C128/256 is designed with software and hardware write protection features including Block Lock protection. The device is available in 8-pin DIP, 8-pin SOIC, 14-pin TSSOP and 20-pin TSSOP packages.

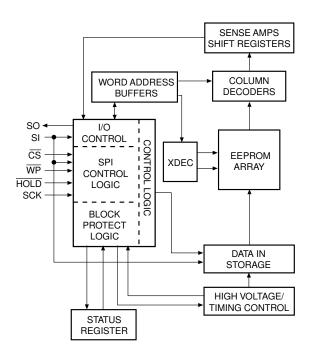

#### **BLOCK DIAGRAM**

For Ordering Information details, see page 11.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias –55°C to +125°C                                                  |

|-----------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                       |

| Voltage on any Pin with Respect to $V_{SS}{}^{1)}\ldots\ldots -2.0V$ to $+V_{CC}$ +2.0V |

| $V_{CC}$ with Respect to $V_{SS}$                                                       |

| Package Power Dissipation<br>Capability (Ta = 25°C)1.0W                                 |

| Lead Soldering Temperature (10 secs) 300°C                                              |

| Output Short Circuit Current <sup>(2)</sup> 100 mA                                      |

#### **RELIABILITY CHARACTERISTICS**

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions outside of those listed in the operational sections of this specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability.

| Symbol                             | Parameter          | Min.    | Max. | Units       |

|------------------------------------|--------------------|---------|------|-------------|

| N <sub>END</sub> <sup>(3)</sup>    | Endurance          | 100,000 |      | Cycles/Byte |

| T <sub>DR</sub> <sup>(3)</sup>     | Data Retention     | 100     |      | Years       |

| VZAP <sup>(3)</sup>                | ESD Susceptibility | 2000    |      | Volts       |

| I <sub>LTH</sub> <sup>(3)(4)</sup> | Latch-Up           | 100     |      | mA          |

#### **D.C. OPERATING CHARACTERISTICS**

$V_{CC} = +1.8V$  to +5.5V, unless otherwise specified.

|                                |                                           |                       | Limits |                            |       |                                                                                  |  |

|--------------------------------|-------------------------------------------|-----------------------|--------|----------------------------|-------|----------------------------------------------------------------------------------|--|

| Symbol                         | Parameter                                 | Min.                  | Тур.   | Max.                       | Units | Test Conditions                                                                  |  |

| Icc1                           | Power Supply Current<br>(Operating Write) |                       |        | 10                         | mA    | V <sub>CC</sub> = 5V @ 5MHz<br>SO=open; CS=Vss                                   |  |

| I <sub>CC2</sub>               | Power Supply Current (Operating Read)     |                       |        | 2                          | mA    | V <sub>CC</sub> = 5.0V<br>F <sub>CLK</sub> = 5MHz                                |  |

| I <sub>SB</sub> <sup>(5)</sup> | Power Supply Current (Standby)            |                       |        | 1                          | μA    | $\overline{CS} = V_{CC}$<br>V <sub>IN</sub> = V <sub>SS</sub> or V <sub>CC</sub> |  |

| ILI                            | Input Leakage Current                     |                       |        | 2                          | μA    |                                                                                  |  |

| ILO                            | Output Leakage Current                    |                       |        | 3                          | μA    | $V_{OUT} = 0V$ to $V_{CC}$ , $CS = 0V$                                           |  |

| VIL <sup>(3)</sup>             | Input Low Voltage                         | -1                    |        | Vcc x 0.3                  | V     |                                                                                  |  |

| V <sub>IH</sub> <sup>(3)</sup> | Input High Voltage                        | V <sub>CC</sub> x 0.7 |        | V <sub>CC</sub> + 0.5      | V     |                                                                                  |  |

| V <sub>OL1</sub>               | Output Low Voltage                        |                       |        | 0.4                        | V     | 4.5V≤V <sub>CC</sub> <5.5V                                                       |  |

| V <sub>OH1</sub>               | Output High Voltage                       | V <sub>CC</sub> - 0.8 |        |                            | V     | V I <sub>OL</sub> = 3.0mA<br>I <sub>OH</sub> = -1.6mA                            |  |

| V <sub>OL2</sub>               | Output Low Voltage                        | 0.2 V 1.8V≤V          |        | 1.8V≤V <sub>CC</sub> <2.7V |       |                                                                                  |  |

| V <sub>OH2</sub>               | Output High Voltage                       | V <sub>CC</sub> -0.2  |        |                            | V     | I <sub>OL</sub> = 150μΑ<br>I <sub>OH</sub> = -100μΑ                              |  |

Note:

(1) The minimum DC input voltage is -0.5V. During transitions, inputs may undershoot to -2.0V for periods of less than 20 ns. Maximum DC voltage on output pins is V<sub>CC</sub> +0.5V, which may overshoot to V<sub>CC</sub> +2.0V for periods of less than 20 ns.

(2) Output shorted for no more than one second. No more than one output shorted at a time.

(3) This parameter is tested initially and after a design or process change that affects the parameter according to appropriate AEC-Q100 and JEDEC test methods.

(4) Latch-up protection is provided for stresses up to 100 mA on address and data pins from -1V to  $V_{CC} + 1V$ .

(5) Maximum standby current ( $I_{SB}$ ) = 10µA for the Automotive and Extended Automotive temperature range.

### PIN CAPACITANCE (1)

| Symbol | Test Conditions                           | Max. | Units | Conditions           |

|--------|-------------------------------------------|------|-------|----------------------|

| Соит   | Output Capacitance (SO)                   | 8    | pF    | V <sub>OUT</sub> =0V |

| CIN    | Input Capacitance (CS, SCK, SI, WP, HOLD) | 6    | pF    | V <sub>IN</sub> =0V  |

Applicable over recommended operating range from  $T_A=25$ °C, f=1.0 MHz, VCC= $\pm 5.0$ V (unless otherwise noted).

#### A.C. CHARACTERISTICS (CAT25C128)

|                                  |                                               | Limits            |      |                                |      |                                |      |                |                       |

|----------------------------------|-----------------------------------------------|-------------------|------|--------------------------------|------|--------------------------------|------|----------------|-----------------------|

|                                  |                                               | Vcc=<br>1.8V-5.5V |      | V <sub>CC</sub> =<br>2.5V-5.5V |      | V <sub>CC</sub> =<br>4.5V-5.5V |      |                | Test                  |

| SYMBOL                           | PARAMETER                                     | Min.              | Max. | Min.                           | Max. | Min.                           | Max. | UNITS          | Conditions            |

| tsu                              | Data Setup Time                               | 100               |      | 70                             |      | 35                             |      | ns             |                       |

| t <sub>H</sub>                   | Data Hold Time                                | 100               |      | 70                             |      | 35                             |      | ns             |                       |

| twH                              | SCK High Time                                 | 250               |      | 150                            |      | 80                             |      | ns             |                       |

| t <sub>WL</sub>                  | SCK Low Time                                  | 250               |      | 150                            |      | 80                             |      | ns             |                       |

| f <sub>SCK</sub>                 | Clock Frequency                               | DC                | 1    | DC                             | 3    | DC                             | 5    | MHz            |                       |

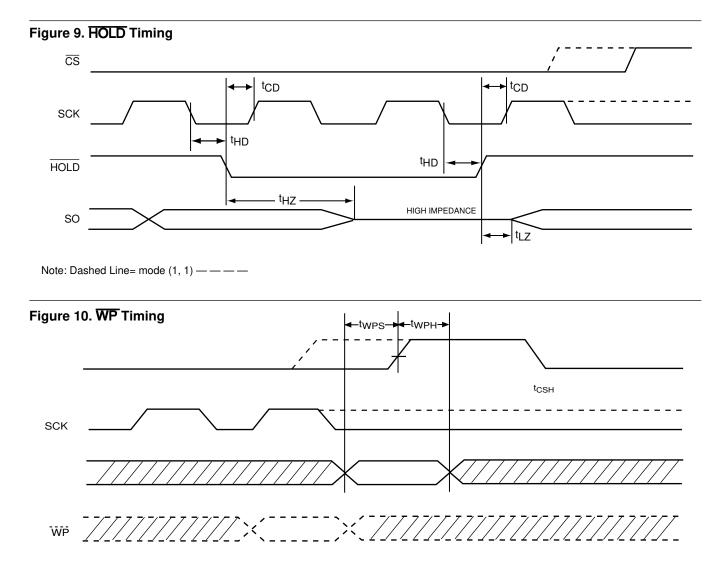

| t <sub>LZ</sub>                  | HOLD to Output Low Z                          |                   | 50   |                                | 50   |                                | 50   | ns             |                       |

| t <sub>RI</sub> <sup>(1)</sup>   | Input Rise Time                               |                   | 2    |                                | 2    |                                | 2    | μs             |                       |

| t <sub>FI</sub> <sup>(1)</sup>   | Input Fall Time                               |                   | 2    |                                | 2    |                                | 2    | μs             |                       |

| t <sub>HD</sub>                  | HOLD Setup Time                               | 250               |      | 250                            |      | 40                             |      | ns             | C <sub>L</sub> = 50pF |

| t <sub>CD</sub>                  | HOLD Hold Time                                | 250               |      | 250                            |      | 40                             |      | ns             |                       |

| twc                              | Write Cycle Time                              |                   | 10   |                                | 10   |                                | 5    | ms             |                       |

| tv                               | Output Valid from Clock Low                   |                   | 250  |                                | 250  |                                | 80   | ns             |                       |

| t <sub>HO</sub>                  | Output Hold Time                              | 0                 |      | 0                              |      | 0                              |      | ns             |                       |

| t <sub>DIS</sub>                 | Output Disable Time                           |                   | 250  |                                | 250  |                                | 100  | ns             |                       |

| t <sub>HZ</sub>                  | HOLD to Output High Z                         |                   | 150  |                                | 150  |                                | 50   | ns             |                       |

| tcs                              | CS High Time                                  | 1000              |      | 250                            |      | 200                            |      | ns             | 1                     |

| tcss                             | CS Setup Time                                 | 1000              |      | 250                            |      | 100                            |      | ns             | 1                     |

| t <sub>CSH</sub><br>twps<br>twpн | CS Hold Time<br>WP Setup Time<br>WP Hold Time | 500<br>50<br>50   |      | 250<br>50<br>50                |      | 100<br>50<br>50                |      | ns<br>ns<br>ns |                       |

NOTE:

(1) This parameter is tested initially and after a design or process change that affects the parameter.

#### A.C. CHARACTERISTICS (CAT25C256)

|                                |                                               | Limits          |                   |                 |                                |                 |                                |                 |               |                |            |

|--------------------------------|-----------------------------------------------|-----------------|-------------------|-----------------|--------------------------------|-----------------|--------------------------------|-----------------|---------------|----------------|------------|

|                                |                                               |                 | Vcc=<br>1.8V-5.5V |                 | V <sub>CC</sub> =<br>2.5V-5.5V |                 | V <sub>CC</sub> =<br>2.7V-5.5V |                 | CC=<br>/-5.5V |                | Test       |

| SYMBOL                         | PARAMETER                                     | Min.            | Max.              | Min.            | Max.                           | Min.            | Max.                           | Min.            | Max.          | UNITS          | Conditions |

| ts∪                            | Data Setup Time                               | 500             |                   | 100             |                                | 70              |                                | 35              |               | ns             |            |

| tн                             | Data Hold Time                                | 500             |                   | 100             |                                | 70              |                                | 35              |               | ns             |            |

| twн                            | SCK High Time                                 | 2500            |                   | 250             |                                | 150             |                                | 80              |               | ns             |            |

| tw∟                            | SCK Low Time                                  | 2500            |                   | 250             |                                | 150             |                                | 80              |               | ns             |            |

| fscк                           | Clock Frequency                               | DC              | 0.2               | DC              | 2.0                            | DC              | 2.5                            | DC              | 5             | MHz            |            |

| tLZ                            | HOLD to Output Low Z                          |                 | 100               |                 | 50                             |                 | 50                             |                 | 50            | ns             |            |

| t <sub>RI</sub> <sup>(3)</sup> | Input Rise Time                               |                 | 2                 |                 | 2                              |                 | 2                              |                 | 2             | μs             |            |

| t <sub>FI</sub> <sup>(3)</sup> | Input Fall Time                               |                 | 2                 |                 | 2                              |                 | 2                              |                 | 2             | μs             |            |

| t <sub>HD</sub>                | HOLD Setup Time                               | 250             |                   | 100             |                                | 100             |                                | 40              |               | ns             | C∟ = 50pF  |

| t <sub>CD</sub>                | HOLD Hold Time                                | 250             |                   | 100             |                                | 100             |                                | 40              |               | ns             |            |

| twc                            | Write Cycle Time                              |                 | 10                |                 | 10                             |                 | 10                             |                 | 5             | ms             |            |

| t <sub>V</sub>                 | Output Valid from Clock Low                   |                 | 250               |                 | 200                            |                 | 200                            |                 | 80            | ns             |            |

| t <sub>HO</sub>                | Output Hold Time                              | 0               |                   | 0               |                                | 0               |                                | 0               |               | ns             |            |

| t <sub>DIS</sub>               | Output Disable Time                           |                 | 250               |                 | 200                            |                 | 200                            |                 | 100           | ns             |            |

| tнz                            | HOLD to Output High Z                         |                 | 150               |                 | 100                            |                 | 100                            |                 | 50            | ns             |            |

| t <sub>CS</sub>                | CS High Time                                  | 100             |                   | 100             |                                | 100             |                                | 100             |               | ns             |            |

| tcss                           | CS Setup Time                                 | 100             |                   | 100             |                                | 100             |                                | 100             |               | ns             |            |

| tcsн<br>twps<br>twpн           | CS Hold Time<br>WP Setup Time<br>WP Hold Time | 100<br>50<br>50 |                   | 100<br>50<br>50 |                                | 100<br>50<br>50 |                                | 100<br>50<br>50 |               | ns<br>ns<br>ns |            |

NOTE:

(3) This parameter is tested initially and after a design or process change that affects the parameter.

### FUNCTIONAL DESCRIPTION

The CAT25C128/256 supports the SPI bus data transmission protocol. The synchronous Serial Peripheral Interface (SPI) helps the CAT25C128/256 to interface directly with many of today's popular microcontrollers. The CAT25C128/256 contains an 8-bit instruction register. (The instruction set and the operation codes are detailed in the instruction set table)

After the device is selected with  $\overline{CS}$  going low, the first byte will be received. The part is accessed via the SI pin, with data being clocked in on the rising edge of SCK. The first byte contains one of the six op-codes that define the operation to be performed.

### **PIN DESCRIPTION**

#### SI: Serial Input

SI is the serial data input pin. This pin is used to input all opcodes, byte addresses, and data to be written to the 25C32/64. Input data is latched on the rising edge of the serial clock.

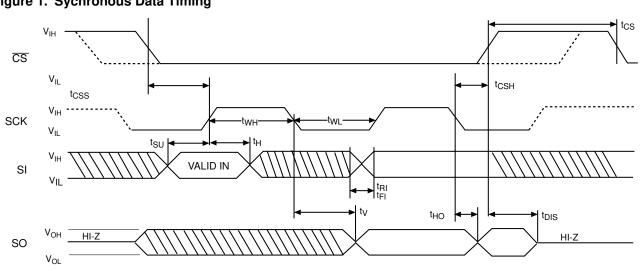

#### Figure 1. Sychronous Data Timing

#### SO: Serial Output

SO is the serial data output pin. This pin is used to transfer data out of the CAT25C128/256. During a read cycle, data is shifted out on the falling edge of the serial clock.

#### SCK: Serial Clock

SCK is the serial clock pin. This pin is used to synchronize the communication between the microcontroller and the CAT25C128/256. Opcodes, byte addresses, or data present on the SI pin are latched on the rising edge of the SCK. Data on the SO pin is updated on the falling edge of the SCK.

#### CS: Chip Select

CS is the Chip select pin. CS low enables the CAT25C128/ 256 and CS high disables the CAT25C128/256. CS high takes the SO output pin to high impedance and forces the devices into a Standby Mode (unless an internal write operation is underway). The CAT25C128/256 draws ZERO current in the Standby mode. A high to low transition on CS is required prior to any sequence being initiated. A low to high transition on CS after a valid write sequence is what initiates an internal write cycle.

Note: Dashed Line= mode (1, 1)

#### **INSTRUCTION SET**

| Instruction | Opcode    | Operation                |

|-------------|-----------|--------------------------|

| WREN        | 0000 0110 | Enable Write Operations  |

| WRDI        | 0000 0100 | Disable Write Operations |

| RDSR        | 0000 0101 | Read Status Register     |

| WRSR        | 0000 0001 | Write Status Register    |

| READ        | 0000 0011 | Read Data from Memory    |

| WRITE       | 0000 0010 | Write Data to Memory     |

#### WP: Write Protect

$\overline{\text{WP}}$  is the Write Protect pin. The Write Protect pin will allow normal read/write operations when held high. When  $\overline{\text{WP}}$  is tied low and the WPEN bit in the status register is set to "1", all write operations to the status register are inhibited.  $\overline{\text{WP}}$  going low while  $\overline{\text{CS}}$  is still low will interrupt a write to the status register. If the internal write cycle has already been initiated,  $\overline{\text{WP}}$  going low will have no effect on any write operation to the status register. The  $\overline{\text{WP}}$  pin function is blocked when the WPEN bit is set to 0.

#### HOLD: Hold

The  $\overline{\text{HOLD}}$  pin is used to pause transmission to the CAT25C128/256 while in the middle of a serial sequence without having to re-transmit entire sequence at a later time. To pause,  $\overline{\text{HOLD}}$  must be brought low while SCK is low. The SO pin is in a high impedance state during the time the part is paused, and transitions on the SI pins will be ignored. To resume communication,  $\overline{\text{HOLD}}$  is brought high, while SCK is low. ( $\overline{\text{HOLD}}$  should be held high any time this function is not being used.)  $\overline{\text{HOLD}}$  may be tied high directly to V<sub>cc</sub> or tied to V<sub>cc</sub> through a resistor. Figure

9 illustrates hold timing sequence.

## STATUS REGISTER

The Status Register indicates the status of the device.

The  $\overline{\text{RDY}}$  (Ready) bit indicates whether the CAT25C128/ 256 is busy with a write operation. When set to 1 a write cycle is in progress and when set to 0 the device indicates it is ready. This bit is read only.

The WEL (Write Enable) bit indicates the status of the write enable latch. When set to 1, the device is in a Write Enable state and when set to 0 the device is in a Write Disable state. The WEL bit can only be set by the WREN instruction and can be reset by the WRDI instruction.

The BP0 and BP1 (Block Protect) bits indicate which blocks are currently protected. These bits are set by the user issuing the WRSR instruction. The user is allowed to protect quarter of the memory, half of the memory or the entire memory by setting these bits. Once protected the user may only read from the protected portion of the array. These bits are non-volatile.

#### STATUS REGISTER

| 7    | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|------|---|---|---|-----|-----|-----|-----|

| WPEN | Х | Х | Х | BP1 | BP0 | WEL | RDY |

#### **BLOCK PROTECTION BITS**

| Status F | Register Bits | Array Address                          | Protection               |

|----------|---------------|----------------------------------------|--------------------------|

| BP1      | BP0           | Protected                              |                          |

| 0        | 0             | None                                   | No Protection            |

| 0        | 1             | 25C128: 3000-3FFF<br>25C256: 6000-7FFF | Quarter Array Protection |

| 1        | 0             | 25C128: 2000-3FFF<br>25C256: 4000-7FFF | Half Array Protection    |

| 1        | 1             | 25C128: 0000-3FFF<br>25C256: 0000-7FFF | Full Array Protection    |

#### WRITE PROTECT ENABLE OPERATION

| WPEN | WP   | WEL | Protected<br>Blocks | Unprotected<br>Blocks | Status<br>Register |

|------|------|-----|---------------------|-----------------------|--------------------|

| 0    | X    | 0   | Protected           | Protected             | Protected          |

| 0    | Х    | 1   | Protected           | Writable              | Writable           |

| 1    | Low  | 0   | Protected           | Protected             | Protected          |

| 1    | Low  | 1   | Protected           | Writable              | Protected          |

| Х    | High | 0   | Protected           | Protected             | Protected          |

| Х    | High | 1   | Protected           | Writable              | Writable           |

The WPEN (Write Protect Enable) is an enable bit for the  $\overline{WP}$  pin. The  $\overline{WP}$  pin and WPEN bit in the status register control the programmable hardware write protect feature. Hardware write protection is enabled when  $\overline{WP}$  is low and WPEN bit is set to high. The user cannot write to the status register (including the block protect bits and the WPEN bit) and the block protected sections in the memory array when the chip is hardware write protected. Only the sections of the memory array that are not block protected can be written. Hardware write protection is disabled when either WP pin is high or the WPEN bit is zero.

### **DEVICE OPERATION**

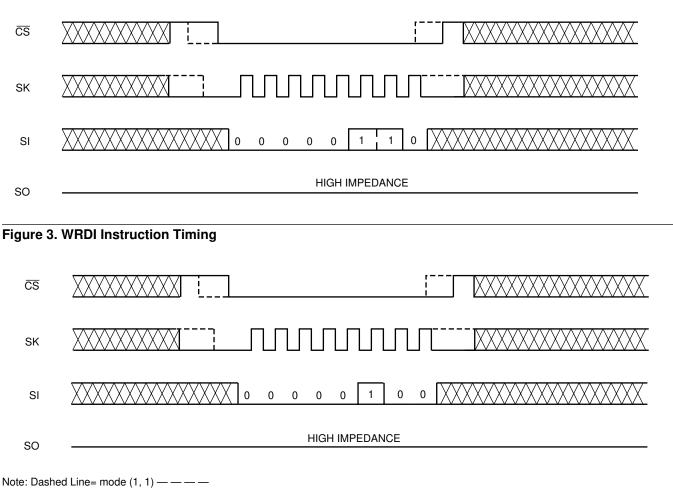

#### Write Enable and Disable

The CAT25C128/256 contains a write enable latch. This latch must be set before any write operation. The device powers up in a write disable state when  $V_{cc}$  is applied. WREN instruction will enable writes (set the latch) to the device. WRDI instruction will disable writes (reset the

#### Figure 2. WREN Instruction Timing

latch) to the device. Disabling writes will protect the device against inadvertent writes.

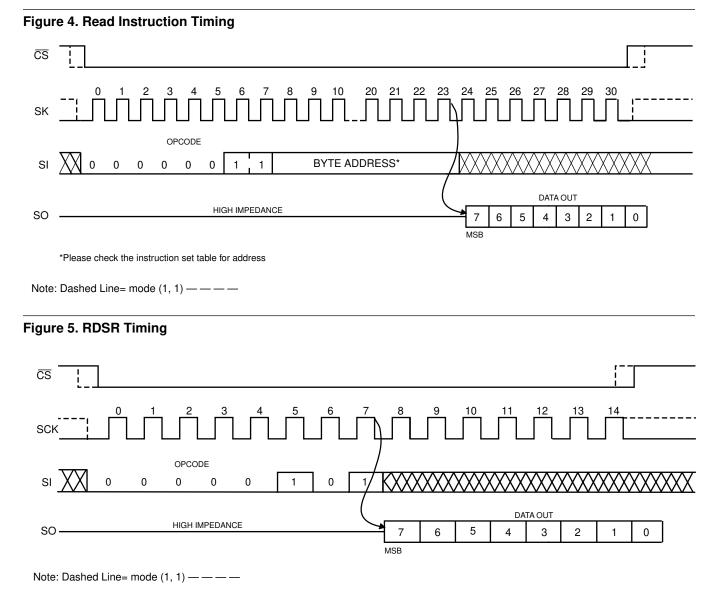

#### **READ Sequence**

The part is selected by pulling  $\overline{CS}$  low. The 8-bit read instruction is transmitted to the CAT25C128/256, followed by the 16-bit address (the three Most Significant Bit is don't care for 25C256 and four most significant bits are don't care for 25C128).

After the correct read instruction and address are sent, the data stored in the memory at the selected address is shifted out on the SO pin. The data stored in the memory at the next address can be read sequentially by continuing to provide clock pulses. The internal address pointer is automatically incremented to the next higher address after each byte of data is shifted out. When the highest address (7FFFh for 25C256 and 3FFFh for 25C128) is reached, the address counter rolls over to 0000h allowing the read cycle to be continued indefinitely. The readoperation is terminated by pulling the  $\overline{CS}$  high.

To read the status register, RDSR instruction should be sent. The contents of the status register are shifted out on the SO line. The status register may be read at any time even during a write cycle. Read sequece is illustrated in Figure 4. Reading status register is illustrated in Figure 5.

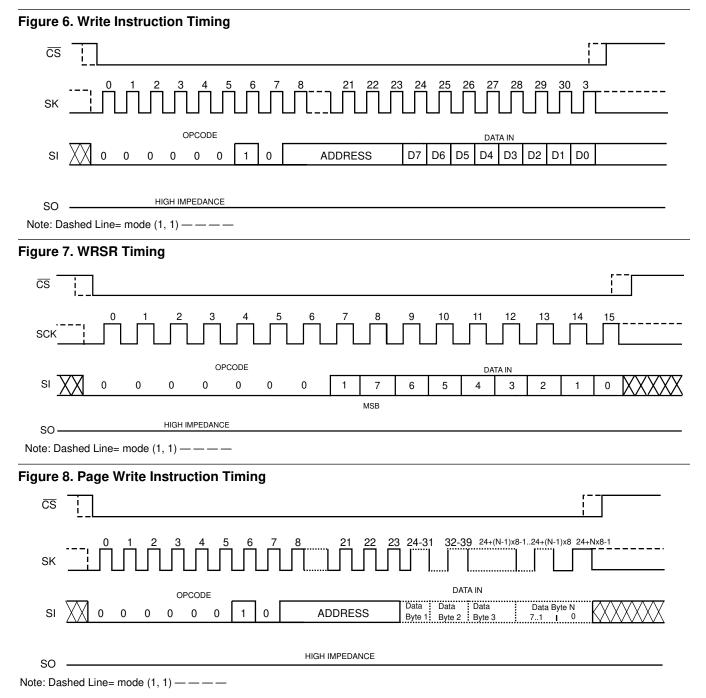

#### WRITE Sequence

The CAT25C128/256 powers up in a Write Disable state. Prior to any write instructions, the WREN instruction must be sent to CAT25C128/256. The device goes into Write enable state by pulling the  $\overline{CS}$  low and then clocking the WREN instruction into CAT25C128/256. The  $\overline{CS}$  must be brought high after the WREN instruction to enable writes to the device. If the write operation is initiated immediately after the WREN instruction without  $\overline{CS}$  being brought high, the data will not be written to the array because the write enable latch will not have been

properly set. Also, for a successful write operation the address of the memory location(s) to be programmed must be outside the protected address field location selected by the block protection level.

#### **Byte Write**

Once the device is in a Write Enable state, the user may proceed with a write sequence by setting the  $\overline{CS}$  low, issuing a write instruction via the SI line, followed by the 16-bit address (the three Most Significant Bits are don't care for 25C256 and four most significant bits are don't care for 25C128), and then the data to be written. Programming will start after the  $\overline{CS}$  is brought high. Figure 6 illustrates byte write sequence.

During an internal write cycle, all commands will be ignored except the RDSR (Read Status Register) instruction.

The Status Register can be read to determine if the write cycle is still in progress. If Bit 0 of the Status Register is set at 1, write cycle is in progress. If Bit 0 is set at 0, the device is ready for the next instruction.

#### Page Write

The CAT25C128/256 features page write capability. After the first initial byte the host may continue to write up to 64 bytes of data to the CAT25C128/256. After each byte of data is received, six lower order address bits are internally incremented by one; the high order bits of address will remain constant. The only restriction is that the 64 bytes must reside on the same page. If the address counter reaches the end of the page and clock continues, the counter will "roll over" to the first address of the page and overwrite any data that may have been written. The CAT25C128/256 is automatically returned to the write disable state at the completion of the write cycle. Figure 8 illustrates the page write sequence.

To write to the status register, the WRSR instruction should be sent. Only Bit 2, Bit 3 and Bit 7 of the status register can be written using the WRSR instruction. Figure 7 illustrates the sequence of writing to status register.

#### **DESIGN CONSIDERATIONS**

The CAT25C128/256 powers up in a write disable state and in a low power standby mode. A WREN instruction must be issued to perform any writes to the device after power up. Also,on power up  $\overline{CS}$  should be brought low to enter a ready state and receive an instruction. After a successful byte/page write or status register write the CAT25C128/256 goes into a write disable mode.  $\overline{CS}$ must be set high after the proper number of clock cycles to start an internal write cycle. Access to the array during an internal write cycle is ignored and program-ming is continued. On power up, SO is in a high impedance. If an invalid op code is received, no data will be shifted into the CAT25C128/256, and the serial output pin (SO) will remain in a high impedence state until the falling edge of  $\overline{CS}$  is detected again.

When powering down, the supply should be taken down to 0V, so that the CAT25C128/256 will be reset when power is ramped back up. If this is not possible, then, following a brown-out episode, the CAT25C128/256 can be reset by refreshing the contents of the Status Register (See Application Note AN10).

Note: Dashed Line= mode (1, 1) - - - - -

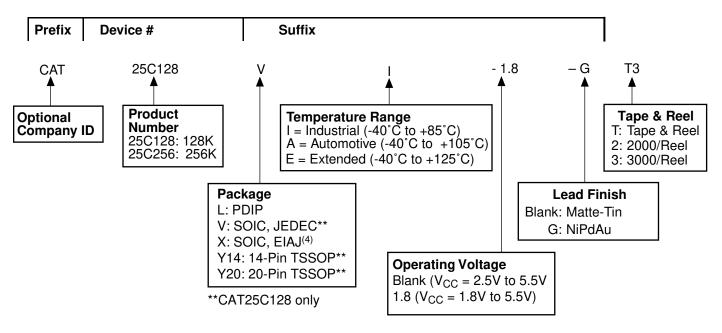

#### **ORDERING INFORMATION**

Notes:

- (1) All packages are RoHS-compliant (Lead-free, Halogen-free).

- (2) The standard finish is NiPdAu pre-plated (PPF).

- (3) The device used in the above example is a CAT25C128VI-1.8-GT3 (SOIC, Industrial Temperature, 1.8V to 5.5V Operating Voltage, NiPdAu, Tape & Reel).

- (4) For SOIC, EIAJ (X) package the standard finish is Matte-Tin. This package is available in 2000 pcs/reel, i.e. CAT25C256XI-T2.

- (5) For additional package and temperature options, please contact your nearest ON Semiconductor Sales office.

#### **REVISION HISTORY**

| Date      | Revision | Description                                                                                                                                                                                                                                            |

|-----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5-Aug-04  | F        | Updated Features<br>Updated DC Operating Characteristics table & notes                                                                                                                                                                                 |

| 17-Feb-05 | G        | Updated D.C. Operating Characteristics table                                                                                                                                                                                                           |

| 23-May-05 | Н        | Updated Reliability Characteristics table                                                                                                                                                                                                              |

| 13-Oct-06 | -        | Update Features<br>Update Description<br>Update Pin Configuration<br>Update Pin Funtions<br>Update D.C. Operating Characteristics (V <sub>CC</sub> Range)<br>Update A.C. Characteristics tables (V <sub>CC</sub> Range)<br>Update Ordering Information |

| 11-Nov-08 | J        | Change logo and fine print to ON Semiconductor                                                                                                                                                                                                         |

ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications and disting "update to support or sustain life, or for any soth unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, afflitates, and disting estimates against all claims, costs, damages, and expenses, and reasonable attomey fees arising out of, directly or indirectly, any claim of personal injury or deatting application is unauthorized used with such unintended or unauthorized use consonal solutions paraling the design or manufacture of the part. SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for reseale in any manner.

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center: Phone: 81-3-5773-3850

#### ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative