# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### USB Type-C High performance Crossbar Switch IC

Rev. 2 — 1 August 2016

**Product data sheet**

### 1. General description

CBTL08GP053 is a USB Type-C High Performance Crossbar Switch IC meant to be used for Type-C connector interface high speed passive switching applications. It provides switching of high speed differential signals that correspond to various interface standards: USB3.1 (10 Gbps), DP1.3 (8.1 Gbps), PCI Express 3.0 (8 Gbps), etc. It supports switching of single ended signals over Type-C interface. In addition, side band switching of AUX and other dedicated signals for transport over SBU1 and SBU2.

It provides the  $l^2$ C-bus interface for switch control, configuration and status update. It operates from a single platform power supply  $V_{DD}$ .

This IC is targeted for a wide range of platforms (PCs, tablets, convertibles, smart phones) and PC accessories (e.g. docks, monitors, etc.) applications.

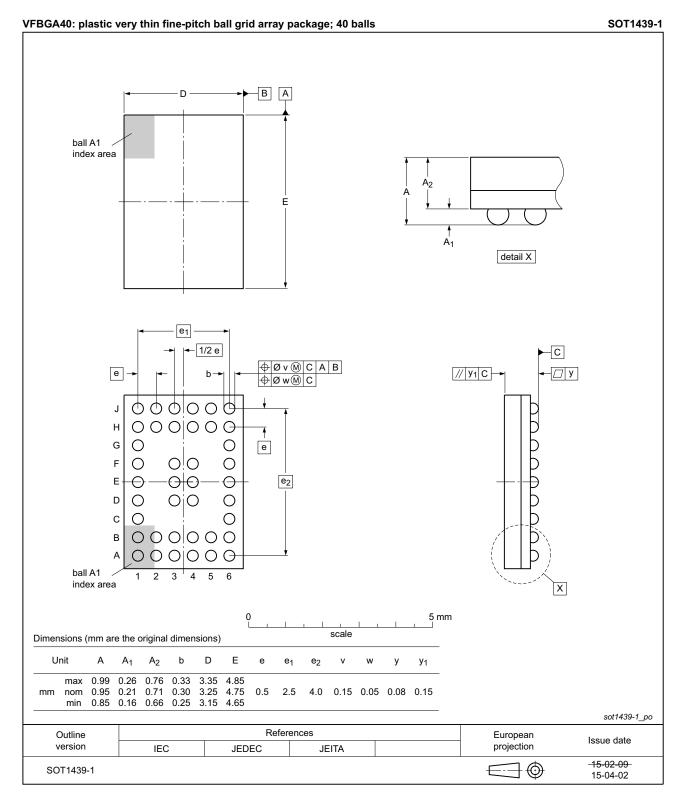

CBTL08GP053 is available in a small footprint package option: VFBGA40 4.75 mm  $\times$  3.25 mm, 0.5 mm pitch.

### 2. Features and benefits

### 2.1 High speed switch features

- Supports the following interface standards: USB3.1, DP1.3, DP++, PCIe 3.0

- Supports signaling rates up to 10 Gbps

- Performs multiplexing or switching of high speed differential signals or single ended signals

- All switches are direction agnostic

- Design based on both patented and patent pending high performance switch technology

- Target performance specification

- Differential signaling (peak to peak) of 1.4 V and common mode level over 0 V to 2.2 V

- 1.8 V single ended rail to rail signaling

- R<sub>on</sub>: 7 Ω (typ)

- Insertion loss: 1.2 dB at 2.7 GHz, 1.8 dB at 5.4 GHz, 3dB at 8.5 GHz (typ)

- Isolation: 23 dB at 2.7 GHz, 16.5 dB at 5.4 GHz (typ)

- Cross talk: 32 dB at 2.7 GHz, 24 dB at 5.4 GHz (typ)

- Return loss: 20 dB at 2.7 GHz, 16 dB at 5.4 GHz (typ)

- Very low intra pair skew

- Very low propagation delay (80 ps typical) and inter pair skew (35 ps typical)

#### USB Type-C High performance Crossbar Switch IC

Switch paths selectable through the I<sup>2</sup>C-bus interface (registers for atomic and sequential switch selection)

#### 2.2 Sideband auxiliary crossbar switch features

- Single ended 2:1 multiplexing/switching with single ended cross bar switching of both differential AUX or single ended UART or I2C or miscellaneous signals

- Switches are direction agnostic

- Switches are 5.5 V tolerant

- Target performance specification (typical values)

- $R_{on} 8 \Omega$  (typ) at  $V_{cm} = 0.5 V$  to 2.65 V

- Very low intra pair skew

- Very low propagation delay (80 ps typical)

- Switch paths selectable through the I<sup>2</sup>C-bus interface (registers for atomic and sequential switch selection)

#### 2.3 General

- Supports I2C slave interface Standard mode (100 kbit/s) and Fast mode (400 kbit/s)

- I2C slave address programmable up to 4 values

- Back current protection on control pins and exposed connector side I/O pins

- Single 3.3V power supply

- Current consumption

- Active mode (all switches are functional): 300 μA (typ)

- Standby mode (all switches in Hi-Z): 15 μA (max)

- Operating temperature: –40 to 105 °C

- ESD 2 kV HBM, 500 V CDM

- Package: VFBGA40 4.75 mm × 3.25 mm, 0.5 mm pitch

### 3. Applications

- PC platforms: notebook PCs, desktop PCs, ultrabooks

- Tablets, 2:1 convertibles, smartphones and portable devices

- PC accessories/peripherals: multi-function monitors, etc.

### 4. Ordering information

| Table 1. Ordering information |         |         |                                                                                                                |           |  |  |  |

|-------------------------------|---------|---------|----------------------------------------------------------------------------------------------------------------|-----------|--|--|--|

| Type number                   | •       | Package |                                                                                                                |           |  |  |  |

|                               | marking | Name    | Description                                                                                                    | Version   |  |  |  |

| CBTL08GP053EV <sup>[1]</sup>  | GP053   | VFBGA   | plastic, very fine-pitch ball grid array package; body 4.75 mm $\times$ 3.25 mm $\times$ 0.92 mm; 0.5 mm pitch | SOT1439-1 |  |  |  |

[1] Total height after printed-circuit board mounting ≤1 mm (maximum)

### 4.1 Ordering options

#### Table 2.Ordering options

| Type number   | Orderable<br>part number | Package | ,                                       | Minimum<br>order<br>quantity | Temperature                                        |

|---------------|--------------------------|---------|-----------------------------------------|------------------------------|----------------------------------------------------|

| CBTL08GP053EV | CBTL08GP053EVY           | VFBGA   | Reel 13" Q1/T1<br>*standard mark SMD DP | 5000                         | $T_{amb} = -40 \ ^{\circ}C \ to \ +85 \ ^{\circ}C$ |

#### USB Type-C High performance Crossbar Switch IC

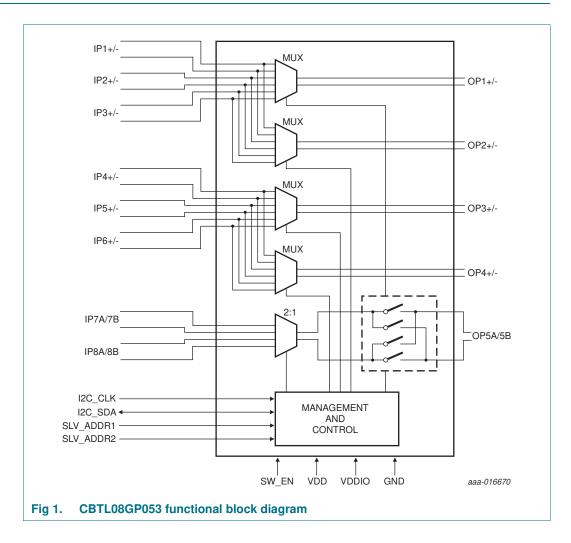

### 5. Block diagram

CBTL08GP053 Product data sheet

4 of 38

USB Type-C High performance Crossbar Switch IC

#### **Pinning information** 6.

### 6.1 Pinning

|        |                                                          | 1    | 2    | 3     | 4             | 5             | 6          |  |

|--------|----------------------------------------------------------|------|------|-------|---------------|---------------|------------|--|

|        | A                                                        | IP6+ | IP6- | IP7A  | IP7B          | OP5A          | OP5B       |  |

|        | В                                                        | IP5- | VDD  | IP8A  | IP8B          | GND           | OP4-       |  |

|        | С                                                        | IP5+ |      |       |               |               | OP4+       |  |

|        | D                                                        | IP4- |      | GND   | SLV_AD<br>DR2 |               | OP2+       |  |

|        | E                                                        | IP4+ |      | VDD   | VDDIO         |               | OP2-       |  |

|        | F                                                        | IP3+ |      | GND   | GND           |               | OP3-       |  |

|        | G                                                        | IP3- |      |       |               |               | OP3+       |  |

|        | н                                                        | IP2+ | GND  | VDDIO | I2C_SDA       | SLV_AD<br>DR1 | OP1+       |  |

|        | J                                                        | IP2- | IP1+ | IP1-  | I2C_SCL       | SW_EN         | OP1-       |  |

|        |                                                          |      |      |       |               |               | aaa-016671 |  |

| Fig 2. | ig 2. CBTL08GP053 pinning diagram (transparent top view) |      |      |       |               |               |            |  |

CBTL08GP053 **Product data sheet**

5 of 38

### USB Type-C High performance Crossbar Switch IC

### 6.2 Pin description

| Symbol    | Pin    | Туре             | Description                                                              |

|-----------|--------|------------------|--------------------------------------------------------------------------|

| IP1+      | J2     | Differential I/O | Six high-speed differential pairs for DisplayPort,                       |

| IP1-      | J3     | Differential I/O | PCI Express, USB3 on system side                                         |

| IP2+      | H1     | Differential I/O | _                                                                        |

| IP2-      | J1     | Differential I/O | _                                                                        |

| IP3+      | F1     | Differential I/O |                                                                          |

| IP3-      | G1     | Differential I/O |                                                                          |

| IP4+      | E1     | Differential I/O |                                                                          |

| IP4-      | D1     | Differential I/O |                                                                          |

| IP5+      | C1     | Differential I/O |                                                                          |

| IP5-      | B1     | Differential I/O |                                                                          |

| IP6+      | A1     | Differential I/O |                                                                          |

| IP6-      | A2     | Differential I/O |                                                                          |

| OP1+      | H6     | Differential I/O | Four high-speed differential pairs for                                   |

| OP1-      | J6     | Differential I/O | <ul> <li>DisplayPort, PCI Express, USB3 on connector<br/>side</li> </ul> |

| OP2+      | D6     | Differential I/O |                                                                          |

| OP2-      | E6     | Differential I/O |                                                                          |

| OP3+      | G6     | Differential I/O | _                                                                        |

| OP3-      | F6     | Differential I/O |                                                                          |

| OP4+      | C6     | Differential I/O |                                                                          |

| OP4-      | B6     | Differential I/O | _                                                                        |

| IP7A      | A3     | I/O              | Differential or Single ended signals on system side                      |

| IP7B      | A4     | I/O              |                                                                          |

| IP8A      | B3     | I/O              | _                                                                        |

| IP8B      | B4     | I/O              |                                                                          |

| OP5A      | A5     | I/O              |                                                                          |

| OP5B      | A6     | I/O              |                                                                          |

| I2C_SCL   | J4     | Control IN       | I2C slave address signal                                                 |

| I2C_SDA   | H4     | Control I/O      | I2C slave data signal                                                    |

| SLV_ADDR1 | H5     | Control IN       | Binary valued address selection pin for I2C slave address                |

| SW_EN     | J5     | Control IN       | Switch enable control input                                              |

| VDD       | B2, E3 | Power            | Supply pin                                                               |

CBTL08GP053 **Product data sheet**  © NXP Semiconductors N.V. 2016. All rights reserved.

#### **USB Type-C High performance Crossbar Switch IC**

| Table 3.         Pin descriptioncontinued |                      |             |                                                           |  |  |  |  |  |

|-------------------------------------------|----------------------|-------------|-----------------------------------------------------------|--|--|--|--|--|

| Symbol                                    | Pin                  | Туре        | Description                                               |  |  |  |  |  |

| VDDIO                                     | H3, E4               | I/O power   | I/O supply pin                                            |  |  |  |  |  |

| GND                                       | B5, D3,<br>F3,F4, H2 |             | Ground                                                    |  |  |  |  |  |

| SLV_ADDR2                                 | D4                   | Control I/O | Binary valued address selection pin for I2C slave address |  |  |  |  |  |

### 7. Functional description

CBTL08GP053 is a highly integrated Type-C switch targeting Type-C applications. All high speed signal paths are implemented using high-bandwidth pass-gate technology and are non-directional. The side band switches are designed to support 5.5 V tolerance. No clock or reset signal is needed for the multiplexer to function. The switching paths for all the switches can be selected using the I<sup>2</sup>C-bus interface.

CBTL08GP053 functionality can be categorized under three portions:

- High speed switch

- This has four sub networks of switches corresponding to four I/Os (OPx) connected to Type-C connector interface

- Each sub network consist of a multiplexer of three high speed I/Os (IPx) on the system side interface

- All switch paths handles differential signaling or 1.8 V rail to rail single ended signals

- All switch paths support up to 10 Gbps signaling

- All multiplexers I/Os are selectable through the I<sup>2</sup>C-bus interface

- The connector side I/Os can be put in Hi-Z through the I<sup>2</sup>C-bus interface. Default for the I/O is Hi-Z

- Sideband Auxiliary crossbar switch

- This has a 2:1 multiplexer followed by single ended selectable crossbar function

- Switch handles both 3.3 V single ended and differential signals

- Switch I/Os are 5.5 V tolerant

- Switch handles 5 V rail to rail signaling

- Crossbar function (normal or reversible) is selectable through the I<sup>2</sup>C-bus interface

- The connector side I/Os can be put in Hi-Z through the I<sup>2</sup>C-bus interface. Default for the I/O is Hi-Z

At power on, all switches are in Hi-Z condition. After the host platform identifies Type-C interface (including Alternate mode support), it configures the switches. Each individual switch output can be selectively activated and specific switch paths can be selected. Each switch output can also remain in Hi-Z individually.

The SW\_EN pin is used to enable or disable the switch paths only but the I2C register contents are not reset when SW\_EN toggles LOW. When SW\_EN is HIGH, the switches can be enabled and if it is LOW, the switches remain in Hi-Z condition irrespective of the register contents. This pin can toggle dynamically in real time in the application.

© NXP Semiconductors N.V. 2016. All rights reserved.

#### **USB Type-C High performance Crossbar Switch IC**

| SW_EN | SWITCH_EN<br>SYS_CTRL[7] | I2C register settings | Switch output                       | Power consumption condition |

|-------|--------------------------|-----------------------|-------------------------------------|-----------------------------|

| LOW   | 0                        | Remain unchanged      | Hi-Z                                | Standby                     |

| LOW   | 1                        | Remain unchanged      | Hi-Z                                | Standby                     |

| HIGH  | 0                        | Remain unchanged      | Hi-Z                                | Standby                     |

| HIGH  | 1                        | Remain unchanged      | Output (based on register settings) | Active                      |

#### Table 4. Truth table for SW\_EN and I2C register contents

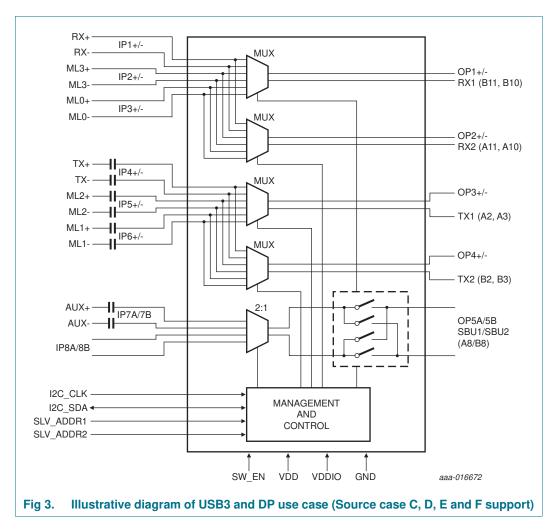

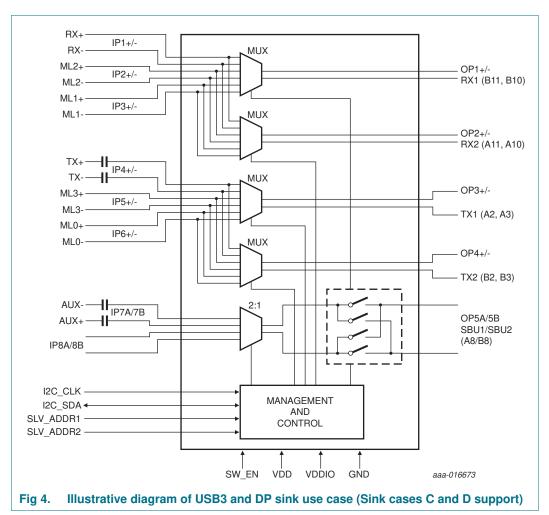

#### 7.1 CBTL08GP053 - Use case view

CBTL08GP053 is a versatile high performance switch with flexibility and programmability to route various signals on to Type-C connector interface. It is designed to work over a range of product categories, platform applications, use cases and usage modes. With its configurability, it can serve the needs of both general and custom applications.

The following subsections cover the use case illustrations of CBTL08GP053.

#### **USB Type-C High performance Crossbar Switch IC**

#### 7.1.1 System application examples

#### 7.1.1.1 CBTL08GP053 in Notebook/Ultrabook PC or Tablet - USB3, DP use

#### USB Type-C High performance Crossbar Switch IC

#### 7.1.1.2 CBTL08GP053 in display monitor use case

Other similar use cases can be constructed as well.

CBTL08GP053 Product data sheet

#### 7.2 Host interface

The host interface of CBTL08GP053 consists of following data/control signals:

- SLV\_ADDR1, SLV\_ADDR2

- I2C\_SCL

- I2C\_SDA

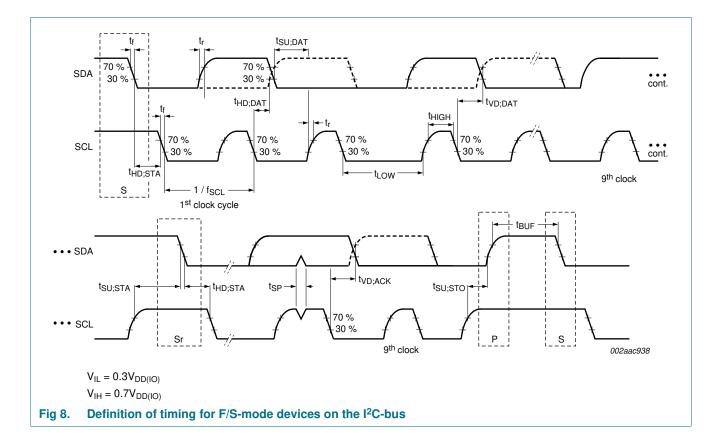

CBTL08GP053 implements I<sup>2</sup>C-bus slave interface and the host processor can issue commands, monitor status and receive response through this bus. A detailed description of the I<sup>2</sup>C-bus specification, with applications, is given in UM10204, "I<sup>2</sup>C-bus specification and user manual" [3]. It supports I<sup>2</sup>C-bus data transfers in both Standard-mode (100kbit/s)) and Fast-mode (400 kbit/s).

As an exception to the I<sup>2</sup>C-bus specification, CBTL08GP053 does not support the I<sup>2</sup>C-bus "General Call" address (and therefore does not issue an Acknowledge), clock stretching, Software Reset command, nor 10-bit address.

The various registers, address offsets and bit definition, as defined in this section and subsections later.

Referring to I<sup>2</sup>C-bus protocol, CBTL08GP053 positively acknowledges all 256 register offset addresses. CBTL08GP053 I<sup>2</sup>C-bus interface implements a special "Auto-Increment" feature that facilitates higher throughput realization by the host system. With this feature, the address wraps back to 0x00 from 0xFF on continuous reads and writes.

CBTL08GP053 supports up to a maximum of four I<sup>2</sup>C-bus slave address options. The address is selected through SLV\_ADDR1 and SLV\_ADDR2 pins. <u>Table 5</u> shows the different I<sup>2</sup>C-bus device address options selectable based on pin values.

Please refer to the CBTL08GP053 Programming Guide (AN11663) for more details.

| SLV_ADDR2 | SLV_ADDR1 | l <sup>2</sup> C-bus device<br>address |

|-----------|-----------|----------------------------------------|

| LOW       | LOW       | 0x60/0x61                              |

| LOW       | HIGH      | 0x64/0x65                              |

| HIGH      | LOW       | 0x68/0x69                              |

| HIGH      | HIGH      | 0x6C/0x6D                              |

Table 5.Device slave address

CBTL08GP053 Product data sheet

| CBTL08GP053                           | Table              | 6. Registe      | r bit n               | nap overview |                    |     |        |         |         |         |         |         |

|---------------------------------------|--------------------|-----------------|-----------------------|--------------|--------------------|-----|--------|---------|---------|---------|---------|---------|

| 3GP05                                 | Ś                  | Register        | Ξ                     | Default POR  |                    | Bit |        |         |         |         |         |         |

|                                       | Address            | name            | Access <sup>[1]</sup> | value        | 7                  | 6   | 5      | 4       | 3       | 2       | 1       | 0       |

| \$                                    | 0x01               | SYS_CTRL        | RW                    | b'00000000   | SWITCH_EN          |     |        |         |         |         |         |         |

|                                       | 0x02               | OP1 CTRL        | RW                    | b'00000000   |                    |     |        |         |         | IP3     | IP2     | IP1     |

|                                       | 0x03               | OP2 CTRL        | RW                    | b'00000000   |                    |     |        |         |         | IP3     | IP2     | IP1     |

|                                       | 0x04               | OP3 CTRL        | RW                    | b'00000000   |                    |     | IP6    | IP5     | IP4     |         |         |         |

|                                       | 0x05               | OP4 CTRL        | RW                    | b'00000000   |                    |     | IP6    | IP5     | IP4     |         |         |         |

|                                       | 0x06               | OP5 CTRL        | RW                    | b'00000000   | IP8                | IP7 |        |         |         |         |         |         |

| All in                                | 0x07               | CROSS5_<br>CTRL | RW                    | b'0000001    |                    |     |        |         |         |         | CROSS   | PASS    |

| format                                | 0x08               | SW_CTRL         | W                     | b'00000000   |                    |     | X5_SET | OP5_SET | OP4_SET | OP3_SET | OP2_SET | OP1_SET |

| on pro                                | 0x09               | REVISION        | R                     | b'10100000   | <b>REVISION ID</b> |     | ÷      |         |         | ·       |         |         |

| All information provided in this docu | 0x0A<br>to<br>0xFF | Reserved        | -                     | b'XXXXXXXXX  | RESERVED           |     |        |         |         |         |         |         |

[1] 'R' Read only register, 'W' Write only register, 'RW' Read/Write register

Product data sheet

provided in this document is subject to legal disclaimers Rev. 2 — 1 August 2016

© NXP Semiconductors N.V. 2016. All rights reserved. 12 of 38 CBTL08GP053

USB Type-C High performance Crossbar Switch IC

**NXP Semiconductors**

#### 7.2.1 SYS\_CTRL register

### Table 7. SYS\_CTRL register (address 0x01) bit description Default: b'00000000 b'00000000

| Bit | Symbol    | Access | Value   | Description                                                                                                         |

|-----|-----------|--------|---------|---------------------------------------------------------------------------------------------------------------------|

| 7   | SWITCH_EN | R/W    | 1       | CBTL08GP053 is in functional mode. The host shall write a '1' into this bit to put the device into functional mode. |

|     |           |        | 0       | CBTL08GP053 is in Shutdown mode. After POR, the device enters and remains in shutdown mode.                         |

|     |           |        |         | To put the device into shutdown mode, this host shall write a '0' into this register bit.                           |

| 6:0 | RESERVED  | R/W    | XXXXXXX | Reserved bit fields. Reads will be zeros and writes do not have any effect.                                         |

#### 7.2.2 OP1\_CTRL register

### Table 8. OP1\_CTRL register (address 0x02) bit description Default: b'00000000 b'00000000

| Bit | Symbol   | Access  | Value | Description                                                                 |

|-----|----------|---------|-------|-----------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W     | XXXXX | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

| 2   | IP3      | R/W     | 0     | Switch inputs IP3+/- are not selected                                       |

|     |          |         | 1     | Switch inputs IP3+/- are selected for connection to OP1+/-                  |

| 1   | IP2      | R/W     | 0     | Switch inputs IP2+/- are not selected                                       |

|     |          |         | 1     | Switch inputs IP2+/- are selected for connection to OP1+/-                  |

| 0   | IP1      | IP1 R/W |       | Switch inputs IP1+/- are not selected                                       |

|     |          |         | 1     | Switch inputs IP1+/- are selected for connection to OP1+/-                  |

[1] The only valid bit values are b'XXXXX001, b'XXXXX010 and b'XXXXX100. Any other bit combination of LS 3 bits will result in Hi-Z at the outputs OP1+/-.

#### 7.2.3 OP2\_CTRL register

| Table 9.     | OP2_  | CTRL | register | (address | 0x03) | bit | description |

|--------------|-------|------|----------|----------|-------|-----|-------------|

| Default: b'0 | 00000 | 000  |          |          |       |     |             |

| Bit | Symbol   | Access | Value | Description                                                                 |

|-----|----------|--------|-------|-----------------------------------------------------------------------------|

| 7:3 | RESERVED | R/W    | XX    | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

| 2   | IP3      | R/W    | 0     | Switch inputs IP3+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP3+/- are selected for connection to OP2+/-                  |

| 1   | IP2      | R/W    | 0     | Switch inputs IP2+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP2+/- are selected for connection to OP2+/-                  |

| 0   | IP1      | R/W    | 0     | Switch inputs IP1+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP1+/- are selected for connection to OP2+/-                  |

[1] The only valid bit values are b'XXXXX001, b'XXXXX010 and b'XXXXX100. Any other bit combination of LS 3 bits will result in Hi-Z at the outputs OP2+/-.

CBTL08GP053

#### 7.2.4 OP3\_CTRL register

### Table 10. OP3\_CTRL register (address 0x04) bit description Default: b'00000000 b'00000000

| Bit | Symbol   | Access | Value | Description                                                                 |

|-----|----------|--------|-------|-----------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W    | XX    | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

| 5   | IP6      | R/W    | 0     | Switch inputs IP6+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP6+/- are selected for connection to OP3+/-                  |

| 4   | IP5      | R/W    | 0     | Switch inputs IP5+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP5+/- are selected for connection to OP3+/-                  |

| 3   | IP4      | R/W    | 0     | Switch inputs IP4+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP4+/- are selected for connection to OP3+/-                  |

| 2:0 | RESERVED | R/W    | XX    | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

[1] The only valid bit values are b'XX100XXX, b'XX010XXX and b'XX001XXX. Any other bit combination of 3 bits (5:3) will result in Hi-Z at the outputs OP3+/-.

### 7.2.5 OP4\_CTRL register

### Table 11. OP4\_CTRL register (address 0x05) bit description Default: b'00000000 b'00000000

| Bit | Symbol   | Access | Value | Description                                                                 |

|-----|----------|--------|-------|-----------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W    | XX    | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

| 5   | IP6      | R/W    | 0     | Switch inputs IP6+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP6+/- are selected for connection to OP4+/-                  |

| 4   | IP5      | R/W    | 0     | Switch inputs IP5+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP5+/- are selected for connection to OP4+/-                  |

| 3   | IP4      | R/W    | 0     | Switch inputs IP4+/- are not selected                                       |

|     |          |        | 1     | Switch inputs IP4+/- are selected for connection to OP4+/-                  |

| 2:0 | RESERVED | R/W    | XXXX  | Reserved bit fields. Reads will be zeros and writes do not have any effect. |

[1] The only valid bit values are b'XX100XXX, b'XX010XXX and b'XX001XXX. Any other bit combination of 3 bits (5:3) will result in Hi-Z at the outputs OP4+/-.

#### 7.2.6 OP5\_CTRL register

#### Table 12. OP5 CTRL register (address 0x06) bit description Default: b'00000000

Bit Symbol Value Description Access 7 R/W IP8 0 Switch inputs IP8A/B are not selected 1 Switch inputs IP8A/B are selected for connection to OP5A/B 6 IP7 0 R/W Switch inputs IP7A/B are not selected Switch inputs IP7A/B are selected for connection to OP5A/B 1 5:0 RESERVED R/W XXXXX Reserved bit fields. Reads will be zeros and writes do not have any effect.

The only valid bit values are b'01XXXXXX and b'10XXXXXX. Any other bit combination of 2 bits (7:6) will result in Hi-Z at the outputs [1] OP5A/B.

#### 7.2.7 CROSS5\_CTRL register

#### Table 13. CROSS5\_CTRL register (address 0x07) bit description Default: b'00000001

| Bit | Symbol   | Access | Value  | Description                                                                      |

|-----|----------|--------|--------|----------------------------------------------------------------------------------|

| 7:2 | RESERVED | R/W    | XXXXXX | Reserved bit fields. Reads will be zeros and writes do not have any effect.      |

| 1   | CROSS    | R/W    | 0      | OP5A/B will be Hi-Z                                                              |

|     |          |        | 1      | OP5B is connected to either IP7A or IP8A depending on<br>OP5_CTRL register value |

|     |          |        |        | OP5A is connected to either IP7B or IP8B depending on<br>OP5_CTRL register value |

| 0   | PASS     | R/W    | 0      | OP5A/B will be Hi-Z                                                              |

|     |          |        | 1      | OP5B is connected to either IP7B or IP8B depending on<br>OP5_CTRL register value |

|     |          |        |        | OP5A is connected to either IP7A or IP8A depending on<br>OP5_CTRL register value |

The only valid bit field values are b'XXXXX10 and b'XXXXX01. The bit fields b'XXXXXX00 and b'XXXXXX11 will result in Hi-Z at the [1] outputs OP5A/B.

#### 7.2.8 SW CTRL register

#### Table 14. SW\_CTRL register (address 0x08) bit description

Default: b'00000000

| Bit | Symbol   | Access | Value | Description                                                                         |

|-----|----------|--------|-------|-------------------------------------------------------------------------------------|

| 7:6 | RESERVED | R/W    | XX    | Reserved bit fields. Reads will be zeros and writes do not have any effect.         |

| 5   | X5_SET   | R/W    | 0     | Prior output setting is unchanged                                                   |

|     |          |        | 1     | CROSS5_CTRL register value is used to select passing through or crossing the inputs |

| 4   | OP5_SET  | R/W    | 0     | Prior output setting is unchanged                                                   |

|     |          |        | 1     | OP5A/B is connected to one of the inputs based on OP5_CTRL register                 |

CBTL08GP053 Product data sheet

#### USB Type-C High performance Crossbar Switch IC

| Bit | Symbol  | Access | Value | Description                                                         |

|-----|---------|--------|-------|---------------------------------------------------------------------|

| 3   | OP4_SET | R/W    | 0     | Prior output setting is unchanged                                   |

|     |         |        | 1     | OP4+/- is connected to one of the inputs based on OP4_CTRL register |

| 2   | OP3_SET | R/W    | 0     | Prior output setting is unchanged                                   |

|     |         |        | 1     | OP3+/- is connected to one of the inputs based on OP3_CTRL register |

| 1   | OP2_SET | R/W    | 0     | Prior output setting is unchanged                                   |

|     |         |        | 1     | OP2+/- is connected to one of the inputs based on OP2_CTRL register |

| 0   | OP1_SET | R/W    | 0     | Prior output setting is unchanged                                   |

|     |         |        | 1     | OP1+/- is connected to one of the inputs based on OP1_CTRL register |

# Table 14. SW\_CTRL register (address 0x08) bit description ... continued Default: b'00000000 b'00000000

### 7.2.9 REVISION register

# Table 15. REVISION register (address 0x09) bit description Default: b'10100000 b'10100000

| Bit | Symbol      | Access | Value      | Description                |

|-----|-------------|--------|------------|----------------------------|

| 7:0 | REVISION ID | R      | b'10100000 | Revision ID                |

|     |             |        |            | A0 = First silicon version |

USB Type-C High performance Crossbar Switch IC

### 7.3 I<sup>2</sup>C read and write sequence

An example of an  $I^2C$  write and read sequence is shown in Figure 5.

| lame           | Size<br>(bits)                                      | Bit 7                                          | Bit 6      | Bit 5                                       | Bit 4                                                        | Bit 3                                                                                  | Bit 2                                                                         | Bit 1                             | Bit 0                 |

|----------------|-----------------------------------------------------|------------------------------------------------|------------|---------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------------|-----------------------|

| Slave address  | 8                                                   | 0                                              | 1          | 1                                           | 0                                                            | SLV_ADDR2                                                                              | SLV_ADDR1                                                                     | 0                                 | Write = 0<br>Read = 1 |

|                |                                                     |                                                |            |                                             |                                                              |                                                                                        |                                                                               |                                   |                       |

| Write 8 bits   |                                                     | 8 bits                                         | 8 bit      | S                                           |                                                              |                                                                                        |                                                                               |                                   |                       |

| S SLAVE ADDR W |                                                     | TER ADDR                                       |            |                                             | RITE DATA                                                    | K+1 A WRITE DAT                                                                        | A K+2 A WRITE DA                                                              | TA K+N-1                          | AP                    |

|                |                                                     |                                                |            |                                             |                                                              |                                                                                        |                                                                               |                                   |                       |

| Read 8 bits    |                                                     | 8 bits                                         |            | 8 bits                                      | 8                                                            | bits                                                                                   |                                                                               |                                   |                       |

|                |                                                     | ~                                              |            | ~                                           |                                                              | <u> </u>                                                                               |                                                                               |                                   |                       |

| S SLAVE ADDR W |                                                     | TER ADDR                                       | K A S SLAV |                                             |                                                              | DATA K A READ D                                                                        | ATA K+1 A READ D                                                              | DATA K+N                          | 1 NA P                |

|                | Idress to Read                                      |                                                |            | gle or multi b                              | oyte read ex                                                 | ecuted from current                                                                    | register location (Sing                                                       | le Byte re                        |                       |

| Register ad    | dress to Read                                       | d specified                                    | Sing       | gle or multi b<br>initiate                  | oyte read ex<br>ed by Maste                                  | ecuted from current i<br>er with NA immediate                                          | register location (Sing<br>ly following first data b                          | lle Byte re<br>oyte)              | ad is                 |

|                | dress to Read                                       | d specified                                    | Sing       | gle or multi b<br>initiate                  | oyte read ex<br>ed by Maste                                  | ecuted from current i<br>er with NA immediate                                          | register location (Sing<br>ly following first data b                          | lle Byte re<br>oyte)              | ad is                 |

| Register ad    | dress to Read                                       | d specified                                    | Sing       | gle or multi t<br>initiate<br>urrent regist | byte read ex<br>ed by Maste<br>er. In this ca                | ecuted from current i<br>er with NA immediate<br>ase only sequence sh                  | register location (Sing<br>ly following first data b                          | lle Byte re<br>oyte)              | ad is                 |

| Register ad    | Idress to Read<br>ot specified Ma<br>Glave <b>S</b> | d specified<br>aster will beg<br>Start Conditi | Sing       | gle or multi t<br>initiate<br>urrent regist | byte read ex<br>ed by Maste<br>er. In this ca<br>DT Acknowle | ecuted from current<br>or with NA immediate<br>ase only sequence sh<br>edge (SDA High) | register location (Sing<br>y following first data b<br>nown in Red bracket is | lle Byte re<br>oyte)<br>s needed. | ad is                 |

#### USB Type-C High performance Crossbar Switch IC

#### **Limiting values** 8.

| Symbol              | Parameter                   | Conditions                                                                                      | Min  | Max <sup>[2]</sup> | Unit |

|---------------------|-----------------------------|-------------------------------------------------------------------------------------------------|------|--------------------|------|

| V <sub>DD</sub>     | supply voltage              | on pin VDD                                                                                      | -0.5 | +4.6               | V    |

| V <sub>DD(IO)</sub> | input/output supply voltage | on pin VDDIO                                                                                    | -0.5 | +4.6               | V    |

|                     | input voltage               | IP1+/-, IP2+/-,<br>IP3+/-, IP4+/-,<br>IP5+/-, IP6+/-                                            | -0.5 | +2.6               | V    |

|                     |                             | OP1+/-, OP2+/-,<br>OP3+/-, OP4+/-                                                               | -0.5 | +2.6               | V    |

|                     |                             | IP7A/7B, IP8A/8B                                                                                | -0.5 | +6.0               | V    |

|                     |                             | OP5A/5B                                                                                         | -0.5 | +6.0               | V    |

|                     |                             | SLV_ADDR1,<br>SLV_ADDR2,<br>SW_EN                                                               | -0.5 | +4.6               | V    |

|                     |                             | I2C_SCL,<br>I2C_SDA<br>(external pull-up<br>needed on the<br>I <sup>2</sup> C-bus<br>interface) | -0.5 | +4.6               | V    |

| T <sub>stg</sub>    | storage temperature         |                                                                                                 | -65  | +150               | °C   |

| T <sub>amb</sub>    | ambient temperature         |                                                                                                 | -40  | +125               | °C   |

| V <sub>ESD</sub>    | electrostatic discharge     | HBM[3]                                                                                          | 2000 | -                  | V    |

|                     | voltage                     | CDM[4]                                                                                          | 500  | -                  | V    |

#### Table 17. Limiting values

[1] All voltage values, except differential voltages, are with respect to network ground terminal.

[2] Stresses above the absolute maximum ratings may damage the device. The device may not function or be operating above the Recommended Operating Conditions and it is strongly recommended not to exceed these levels. Also, the device reliability may get affected if it is subjected to stress levels above the Recommended Operating Conditions.

- [3] Human Body Model: ANSI/ESDA/JEDEC JDS-001-2012 (Revision of ANSI/ESDA/JEDEC JS-001-2011), ESDA/JEDEC Joint standard for ESD sensitivity testing, Human Body Model - Component level; Electrostatic Discharge Association, Rome, NY, USA; JEDEC Solid State Technology Association, Arlington, VA, USA.

- [4] Charged Device Model: JESD22-C101E December 2009 (Revision of JESD22-C101D, October 2008), standard for ESD sensitivity testing, Charged Device Model - Component level; JEDEC Solid State Technology Association, Arlington, VA, USA.

**USB Type-C High performance Crossbar Switch IC**

### 9. Recommended operating conditions

#### Table 18. Operating conditions

Over ambient temperature and power supply ranges (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted).

| Symbol              | Parameter                   | Conditions   | Min | Тур | Max  | Unit |

|---------------------|-----------------------------|--------------|-----|-----|------|------|

| V <sub>DD</sub>     | supply voltage              | on pin VDD   | 2.9 | -   | 3.6  | V    |

| V <sub>DD(IO)</sub> | input/output supply voltage | on pin VDDIO | 1.7 | -   | 3.6  | V    |

| T <sub>amb</sub>    | ambient temperature         |              | -40 | -   | +105 | °C   |

### **10. Characteristics**

### **10.1 Device characteristics**

#### Table 19. Device characteristics

Over ambient temperature and power supply ranges (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted).

| Symbol               | Parameter            | Conditions                                                                                                                                                                           | Min | Тур | Max | Unit |

|----------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| l <sub>act</sub>     | active current       | switches are enabled                                                                                                                                                                 | -   | 300 | -   | μA   |

| I <sub>stdby</sub>   | standby current      | all switches in Hi-Z                                                                                                                                                                 | -   | -   | 15  | μA   |

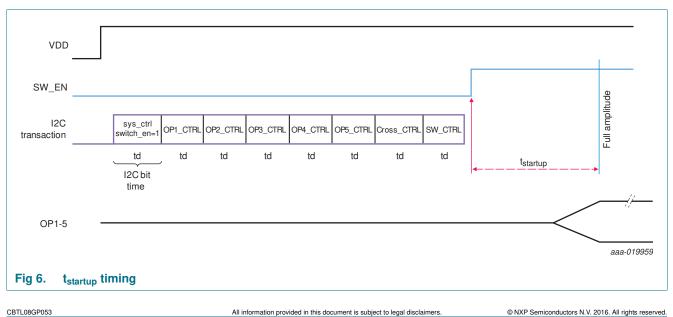

| t <sub>startup</sub> | start-up time        | SW_EN going LOW $\rightarrow$ HIGH<br>to switches functioning as per<br>specified operating<br>characteristics; with a<br>non-zero and valid switch<br>selection (refer to Figure 6) | -   | 60  | 300 | μS   |

| t <sub>rcfg</sub>    | reconfiguration time | Time interval between end of<br>I2C ACK response last bit<br>and switches functioning as<br>per specified operating<br>characteristics                                               | -   | -   | 20  | μS   |

#### USB Type-C High performance Crossbar Switch IC

### 10.2 High speed switch characteristics

#### Table 20. High speed switch characteristics

Over ambient temperature and power supply ranges (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted).

| Symbol               | Parameter                                                  | Conditions                                                           | Min                     | Тур  | Max                     | Unit |

|----------------------|------------------------------------------------------------|----------------------------------------------------------------------|-------------------------|------|-------------------------|------|

| VI                   | input voltage                                              |                                                                      | -0.3                    | -    | +2.55                   | V    |

| V <sub>se, LO</sub>  | Single ended voltage<br>LOW level                          | Applicable for single ended signal switching use cases               | -                       | -    | $0.3 \times V_{DD(IO)}$ | V    |

| V <sub>se, HI</sub>  | Single ended voltage<br>HIGH level                         | Applicable for single ended signal switching use cases               | $0.7 \times V_{DD(IO)}$ | -    | 2.55                    | V    |

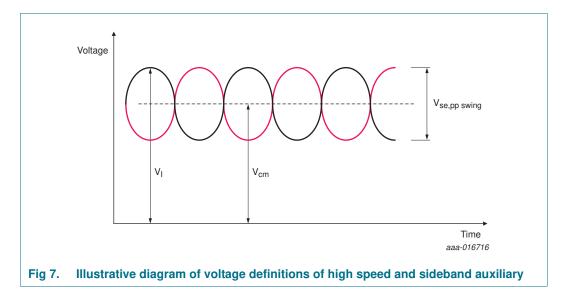

| $V_{se,pp\ swing}$   | Single ended peak to peak voltage swing                    | Applicable for differential signal switching use cases               | -                       | -    | 0.7                     | V    |

| V <sub>cm</sub>      | Common mode voltage                                        | Applicable for differential signal switching use cases               | 0                       | -    | 2.2                     | V    |

| R <sub>on</sub>      | ON-state resistance                                        | V <sub>cm</sub> = 0 V to 2.2 V, I = 15 mA                            | -                       | 7    | 10                      | Ω    |

| I <sub>max</sub>     | Maximum sustained DC current flow                          |                                                                      | -                       | -    | 15                      | mA   |

| t <sub>pd</sub>      | Propagation delay                                          | At mid-point of differential voltage transition                      | -                       | 80   | 120                     | ps   |

| t <sub>SK,diff</sub> | Intra pair skew                                            | Between mid points of<br>positive and negative<br>terminals of an IO | -                       | -    | 6                       | ps   |

| t <sub>SK</sub>      | Inter pair skew                                            | Skew between different lanes                                         | -                       | 35   | -                       | ps   |

| BW                   | –3 dB<br>Bandwidth                                         |                                                                      | -                       | 8.5  | -                       | GHz  |

| DDIL                 | Differential Insertion Loss<br>on both IPx ( $x = 1$ to 6) | Switch path is disabled                                              |                         |      |                         |      |

|                      |                                                            | f = 5.4 GHz                                                          | -                       | 16.5 | -                       | dB   |

|                      | and OPy+/- $(y = 1 \text{ to } 4)$                         | f = 2.7 GHz                                                          | -                       | 23   | -                       | dB   |

|                      |                                                            | Switch path is enabled                                               |                         |      |                         |      |

|                      |                                                            | f = 5.4 GHz                                                          | -                       | 1.8  | -                       | dB   |

|                      |                                                            | f = 2.7 GHz                                                          | -                       | 1.2  | -                       | dB   |

|                      |                                                            | f = 1.35 GHz                                                         | -                       | 0.9  | -                       | dB   |

|                      |                                                            | f = 100 MHz                                                          | -                       | 0.8  | -                       | dB   |

| DDRL                 | Differential return loss on                                | f = 5.4 GHz                                                          | -                       | 16   | -                       | dB   |

|                      | IPx (x = 1 to 6)                                           | f = 2.7 GHz                                                          | -                       | 20   | -                       | dB   |

|                      |                                                            | f = 1.35 GHz                                                         | -                       | 23   | -                       | dB   |

| DDRL                 | Differential return loss on                                | f = 5.4 GHz                                                          | -                       | 16   | -                       | dB   |

|                      | OPx (x = 1 to 4)                                           | f = 2.7 GHz                                                          | -                       | 20   | -                       | dB   |

|                      |                                                            | f = 1.35 GHz                                                         | -                       | 23   | -                       | dB   |

| DDXTLK               | Differential Crosstalk on                                  | f = 5.4 GHz                                                          | -                       | 24   | -                       | dB   |

|                      | IPx+/-(x = 1  to  6)                                       | f = 2.7 GHz                                                          | -                       | 32   | -                       | dB   |

|                      |                                                            | f = 1.35 GHz                                                         | -                       | 37   | -                       | dB   |

| DDXTLK               | Differential crosstalk on                                  | f = 5.4 GHz                                                          | -                       | 24   | -                       | dB   |

|                      | OPx+/-(x = 1  to  4)                                       | f = 2.7 GHz                                                          | -                       | 32   | -                       | dB   |

|                      |                                                            | f = 1.35 GHz                                                         | -                       | 37   | -                       | dB   |

**USB Type-C High performance Crossbar Switch IC**

All S-parameter measurements are with respect to 100  $\Omega$  differential impedance reference and 50  $\Omega$  single-ended impedance reference.

### **10.3 Sideband Auxiliary Crossbar switch characteristics**

#### Table 21. Sideband Auxiliary Crossbar switch characteristics

Over ambient temperature and power supply ranges (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted).

| Symbol                   | Parameter                                        | Conditions                                             | Min                                                     | Тур | Max                                                     | Unit |

|--------------------------|--------------------------------------------------|--------------------------------------------------------|---------------------------------------------------------|-----|---------------------------------------------------------|------|

| VI                       | input voltage                                    |                                                        | -0.3                                                    | -   | +5.3                                                    | V    |

| V <sub>se, LO</sub>      | Single ended voltage LOW level                   | Applicable for single ended signal switching use cases | -                                                       | -   | $\begin{array}{c} 0.3 \times \\ V_{DD(IO)} \end{array}$ | V    |

| V <sub>se, HI</sub>      | Single ended voltage HIGH level                  | Applicable for single ended signal switching use cases | $\begin{array}{c} 0.7 \times \\ V_{DD(IO)} \end{array}$ | -   | 5.3                                                     | V    |

| V <sub>se,pp swing</sub> | Single ended peak to peak                        | Up to 75 MHz                                           | -                                                       | -   | 5.3                                                     | V    |

|                          | voltage swing (diff. signal switching use cases) | 75 MHz to 500 MHz                                      | 0.075                                                   | -   | 0.575                                                   | V    |

| V <sub>cm</sub>          | Common mode voltage (diff.                       | Up to 75 MHz                                           | 0.8                                                     | -   | 2.65                                                    | V    |

|                          | signal switching use cases)                      | 75 MHz to 500 MHz                                      | -0.05                                                   | -   | +0.5                                                    | V    |

| R <sub>on</sub>          | ON-state resistance                              | $V_{cm}$ = $-0.05$ V to 2.65 V, I = 20 mA              | -                                                       | 7.1 | 10                                                      | Ω    |

| I <sub>max</sub>         | Maximum sustained DC current flow                |                                                        | -                                                       | -   | 20                                                      | mA   |

| t <sub>pd</sub>          | Propagation delay                                | At mid-point of differential voltage transition        | -                                                       | 80  | 100                                                     | ps   |

| t <sub>SK</sub>          | Intra pair skew                                  |                                                        | -                                                       | -   | 5                                                       | ps   |

| BW                       | –3 dB bandwidth                                  |                                                        | -                                                       | 750 | -                                                       | MHz  |

| DDDIL                    | Differential Insertion Loss                      | Switch path is not enabled                             |                                                         |     |                                                         |      |

|                          |                                                  | f = 500 MHz                                            | -                                                       | 20  | -                                                       | dB   |

|                          |                                                  | f = 250 MHz                                            | -                                                       | 26  | -                                                       | dB   |

|                          |                                                  | Switch path is enabled                                 |                                                         |     |                                                         |      |

|                          |                                                  | f = 750 MHz                                            | -                                                       | 3.0 | -                                                       | dB   |

|                          |                                                  | f = 500 MHz                                            | -                                                       | 1.5 | -                                                       | dB   |

|                          |                                                  | f = 375 MHz                                            | -                                                       | 1.2 | -                                                       | dB   |

|                          |                                                  | f = 250 MHz                                            | -                                                       | 1.0 | -                                                       | dB   |

| DDRL                     | Differential return loss                         | f = 500 MHz                                            | -                                                       | 11  | -                                                       | dB   |

|                          |                                                  | f = 375 MHz                                            | -                                                       | 13  | -                                                       | dB   |

|                          |                                                  | f = 250 MHz                                            | -                                                       | 16  | -                                                       | dB   |

All S-parameter measurements are with respect to 100  $\Omega$  differential impedance reference and 50  $\Omega$  single-ended impedance reference.

#### **USB Type-C High performance Crossbar Switch IC**

### **10.4 Control I/O characteristics**

#### Table 22. Control I/O characteristics

Over ambient temperature and power supply ranges (unless otherwise noted). Typical values are specified at 27 °C (unless otherwise noted).

| CMOC interface nine (CM/                      | I                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e Gwos Interface pins (SW_I                   | EN, SLV_ADDR1, SLV_ADDR2)                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                              |

| HIGH-level input voltage                      |                                                                                                                                                                                                                   | $0.7\times V_{DD(IO)}$                                                                                                                                                                                                                                                                                                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>DD(IO)</sub> + 0.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                                                                                            |