## imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

### Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# CD4724BC 8-Bit Addressable Latch

#### FAIRCHILD

SEMICONDUCTOR TM

#### CD4724BC 8-Bit Addressable Latch

#### **General Description**

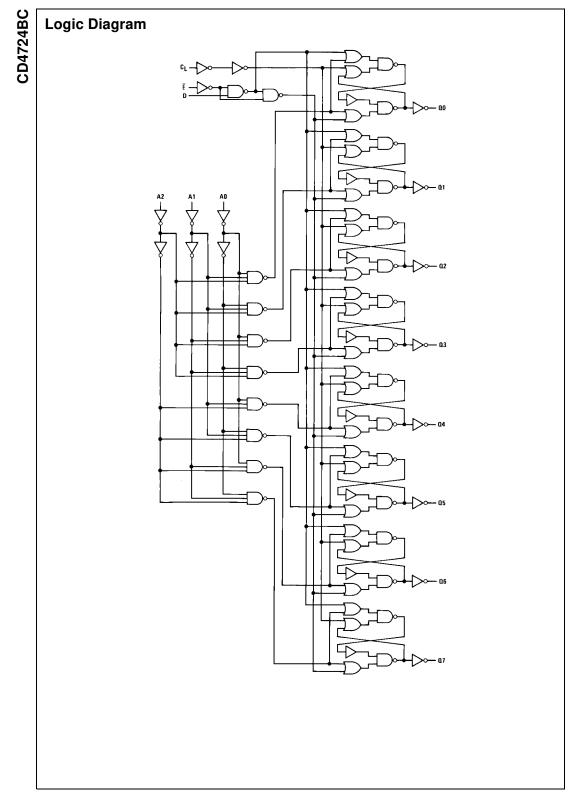

The CD4724BC is an 8-bit addressable latch with three address inputs (A0–A2), an active low enable input ( $\overline{E})$ , active high clear input (C<sub>L</sub>), a data input (D) and eight outputs (Q0–Q7).

Data is entered into a particular bit in the latch when that is addressed by the address inputs and the enable  $(\overline{E})$  is LOW. Data entry is inhibited when enable  $(\overline{E})$  is HIGH.

When clear (C<sub>L</sub>) and enable ( $\overline{E}$ ) are HIGH, all outputs are LOW. When clear (C<sub>L</sub>) is HIGH and enable ( $\overline{E}$ ) is LOW, the channel demultiplexing occurs. The bit that is addressed has an active output which follows the data input while all unaddressed bits are held LOW. When operating in the addressable latch mode ( $\overline{E} = C_L = LOW$ ), changing more than one bit of the address could impose a transient wrong address. Therefore, this should only be done while in the memory mode ( $\overline{E} = HIGH, C_L = LOW$ ).

#### Features

- Wide supply voltage range: 3.0V to 15V

- High noise immunity: 0.45 V<sub>DD</sub> (typ.)

- Low power TTL compatibility:

- fan out of 2 driving 74L or 1 driving 74LS ■ Serial to parallel capability

- Storage register capability

- Random (addressable) data entry

- Active high demultiplexing capability

- Common active high clear

#### **Ordering Code:**

| Order Number                                                                                              | Package Number | Package Description                                                          |  |

|-----------------------------------------------------------------------------------------------------------|----------------|------------------------------------------------------------------------------|--|

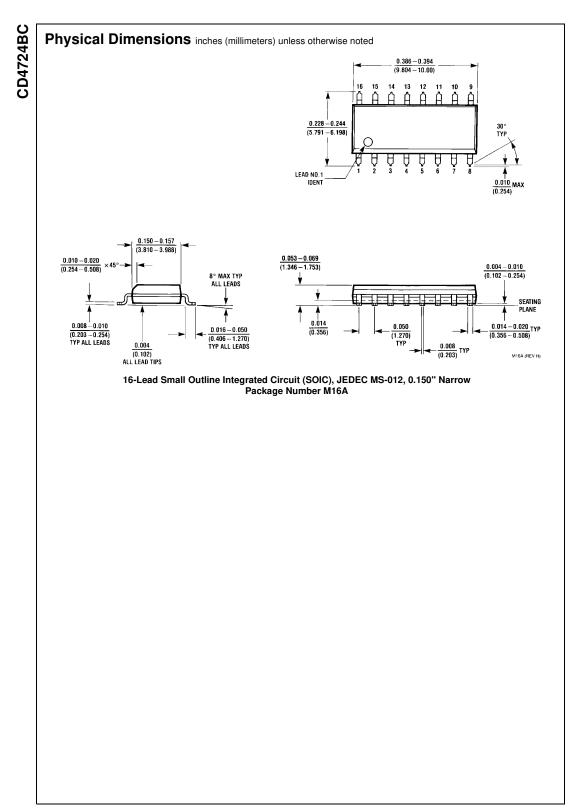

| CD4724BCM                                                                                                 | M16A           | 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow |  |

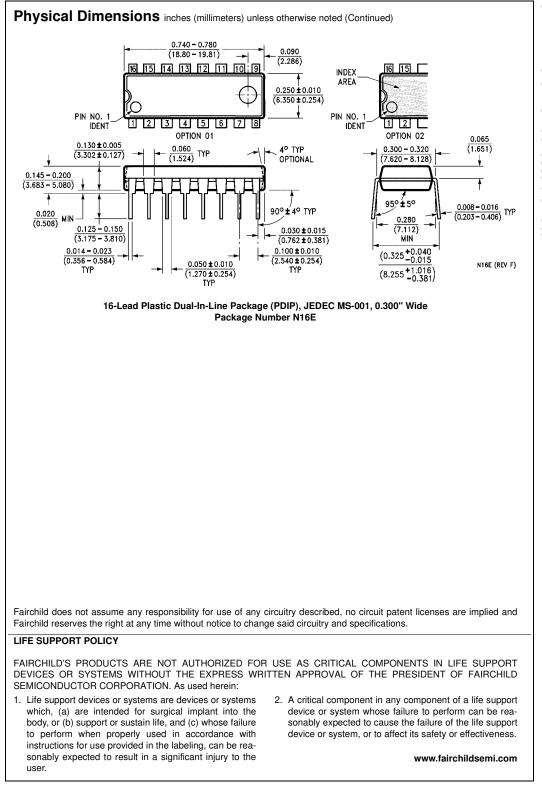

| CD4724BCN                                                                                                 | N16E           | 16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" Wide       |  |

| Devices also available in Tape and Reel. Specify by appending the suffix letter "X" to the ordering code. |                |                                                                              |  |

#### **Connection Diagram**

#### **Truth Table**

|   |       | Мо                    | Mode Selection         |                      |  |  |  |

|---|-------|-----------------------|------------------------|----------------------|--|--|--|

| E | $C_L$ | Addressed             | Unaddressed            | Mode                 |  |  |  |

|   |       | Latch                 | Latch                  |                      |  |  |  |

| L | L     | Follows Data          | Holds Previous<br>Data | Addressable<br>Latch |  |  |  |

| Н | L     | Hold Previous<br>Data | Holds Previous<br>Data | Memory               |  |  |  |

| L | н     | Follows Data          | Reset to "0"           | Demultiplexer        |  |  |  |

| Н | н     | Reset to "0"          | Reset to "0"           | Clear                |  |  |  |

© 2002 Fairchild Semiconductor Corporation DS006003

www.fairchildsemi.com

www.fairchildsemi.com

2

#### Absolute Maximum Ratings(Note 1)

| (Note 2)                              |                         | Conditions (Note 2)                                                                                                                                  |                                       |  |  |

|---------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|--|--|

| DC Supply Voltage (V <sub>DD</sub> )  | $-0.5V$ to +18 $V_{DC}$ | DC Supply Voltage (V <sub>DD</sub> )                                                                                                                 | 3.0V to 15 $\mathrm{V}_{\mathrm{DC}}$ |  |  |

| Input Voltage (V <sub>IN</sub> )      | –0.5V to V_DD +0.5 V_DC | Input Voltage (V <sub>IN</sub> )                                                                                                                     | 0V to $V_{DD} V_{DC}$                 |  |  |

| Storage Temperature (T <sub>S</sub> ) | -65°C to +150°C         | Operating Temperature Range (T <sub>A</sub> )                                                                                                        | -55°C to +125°C                       |  |  |

| Power Dissipation (P <sub>D</sub> )   |                         | Note 1: "Absolute Maximum Ratings" are those values beyond which the                                                                                 |                                       |  |  |

| Dual-In-Line                          | 700 mW                  | safety of the device cannot be guaranteed; they are not meant to imply that<br>the devices should be operated at these limits. The tables of "Recom- |                                       |  |  |

| Small Outline                         | 500 mW                  | mended Operating Conditions" and Electrical Characteristics" provide                                                                                 |                                       |  |  |

| Lead Temperature (T <sub>L</sub> )    |                         | ditions for actual device operation.<br><b>Note 2:</b> $V_{SS} = 0V$ unless otherwise specified.                                                     |                                       |  |  |

| (Soldering, 10 seconds)               | 260°C                   |                                                                                                                                                      |                                       |  |  |

#### **Recommended Operating** Conditions (Note 2)

# CD4724BC

DC Electrical Characteristics (Note 2) -55°C +25°C +125°C Units Symbol Parameter Conditions Min Max Min Max Min Тур Max  $V_{DD} = 5V$  $I_{DD}$ Quiescent Device 5 0.02 5 150 10 Current  $V_{DD} = 10V$ 0.02 10 300 μA V<sub>DD</sub> = 15V 20 0.02 20 600 VOL LOW Level |l<sub>O</sub>| ≤ 1 μA  $V_{DD} = 5V$ Output Voltage 0.05 0 0.05 0.05  $V_{DD} = 10V$ 0.05 0 0.05 0.05 ٧  $V_{DD} = 15V$ 0.05 0 0.05 0.05 HIGH Level |I<sub>O</sub>| ≤ 1 μA V<sub>OH</sub> Output Voltage  $V_{DD} = 5V$ 4 95 4 95 5.0 4 95 9.95 9.95 v 9.95  $V_{DD} = 10V$ 10  $V_{DD} = 15V$ 14.95 14.95 15 14.95 VIL LOW Level  $V_{DD} = 5V, V_{O} = 0.5V \text{ or } 4.5V$ 1.5 2.25 1.5 1.5 V Input Voltage  $V_{DD} = 10V, V_{O} = 1V \text{ or } 9V$ 3.0 4.5 3.0 3.0  $V_{DD} = 15V, V_{O} = 1.5V \text{ or } 13.5V$ 4.0 6.75 4.0 4.0  $V_{DD} = 5V, V_O = 0.5V \text{ or } 4.5V$  $V_{\text{IH}}$ HIGH Level 3.5 3.5 2.75 3.5  $V_{DD} = 10V, V_O = 1V \text{ or } 9V$ ٧ Input Voltage 7.0 7.0 5.5 7.0  $V_{DD} = 15V, V_O = 1.5V \text{ or } 13.5V$ 11.0 11.0 8.25 11.0 I<sub>OL</sub> LOW Level Output  $V_{DD} = 5V, V_{O} = 0.4V$ 0.64 0.51 0.88 0.36  $V_{DD} = 10V, V_{O} = 0.5V$ Current 2.25 0.9 1.6 1.3 mΑ  $V_{DD} = 15V, V_{O} = 1.5V$ (Note 3) 4.2 3.4 8.8 2.4 HIGH Level Output  $V_{DD} = 5V, V_{O} = 4.6V$ -0.64 -0.51 -0.88 -0.36 lон Current  $V_{DD} = 10V, V_{O} = 9.5V$ -1.3 -2.25 -0.9 mA -1.6  $V_{DD} = 15V, V_{O} = 13.5V$ (Note 3) -4.2 -3.4 -8.8 -2.4  $V_{DD} = 15V, V_{IN} = 0V$ Input Current -0.1 -10--0.1 -1.0  $I_{IN}$ μΑ V<sub>DD</sub> = 15V, V<sub>IN</sub> = 15V 10<sup>-5</sup> 0.1 0.1 1.0

Note 3: IOL and IOH are tested one output at a time

www.fairchildsemi.com

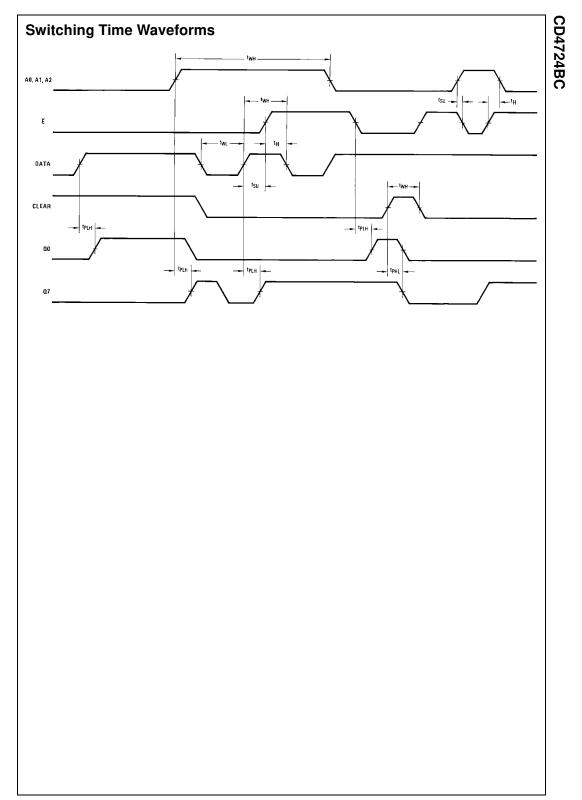

|                                     | $L = 50 \text{ pF}, \text{R}_{L} = 200 \text{k}, \text{Input}$ |                       |     | <b>T</b> | Maria | 11   |

|-------------------------------------|----------------------------------------------------------------|-----------------------|-----|----------|-------|------|

| Symbol                              | Parameter                                                      | Conditions            | Min | Тур      | Max   | Unit |

| <sup>t</sup> PHL, tPLH              | Propagation Delay                                              | $V_{DD} = 5V$         |     | 200      | 400   |      |

|                                     | Data to Output                                                 | $V_{DD} = 10V$        |     | 75       | 150   | ns   |

|                                     |                                                                | V <sub>DD</sub> = 15V |     | 50       | 100   |      |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay                                              | $V_{DD} = 5V$         |     | 200      | 400   |      |

|                                     | Enable to Output                                               | $V_{DD} = 10V$        |     | 80       | 160   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 60       | 120   |      |

| t <sub>PHL</sub>                    | Propagation Delay                                              | $V_{DD} = 5V$         |     | 175      | 350   |      |

|                                     | Clear to Output                                                | $V_{DD} = 10V$        |     | 80       | 160   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 65       | 130   |      |

| t <sub>PLH</sub> , t <sub>PHL</sub> | Propagation Delay                                              | $V_{DD} = 5V$         |     | 225      | 450   |      |

|                                     | Address to Output                                              | $V_{DD} = 10V$        |     | 100      | 200   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 75       | 150   |      |

| t <sub>THL</sub> , t <sub>TLH</sub> | Transition Time                                                | $V_{DD} = 5V$         |     | 100      | 200   |      |

|                                     | (Any Output)                                                   | $V_{DD} = 10V$        |     | 50       | 100   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 40       | 80    |      |

| T <sub>WH</sub> , T <sub>WL</sub>   | Minimum Data                                                   | $V_{DD} = 5V$         |     | 100      | 200   |      |

|                                     | Pulse Width                                                    | $V_{DD} = 10V$        |     | 50       | 100   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 40       | 80    |      |

| t <sub>WH</sub> , t <sub>WL</sub>   | Minimum Address                                                | $V_{DD} = 5V$         |     | 200      | 400   |      |

|                                     | Pulse Width                                                    | $V_{DD} = 10V$        |     | 100      | 200   | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 65       | 125   |      |

| t <sub>WH</sub>                     | Minimum Clear                                                  | $V_{DD} = 5V$         |     | 75       | 150   |      |

|                                     | Pulse Width                                                    | $V_{DD} = 10V$        |     | 40       | 75    | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 25       | 50    |      |

| t <sub>SU</sub>                     | Minimum Setup Time                                             | $V_{DD} = 5V$         |     | 40       | 80    |      |

|                                     | Data to E                                                      | $V_{DD} = 10V$        |     | 20       | 40    | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 15       | 30    |      |

| t <sub>H</sub>                      | Minimum Hold Time                                              | $V_{DD} = 5V$         |     | 60       | 120   |      |

| 11                                  | Data to E                                                      | $V_{DD} = 10V$        |     | 30       | 60    | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 25       | 50    |      |

| t <sub>SU</sub>                     | Minimum Setup Time                                             | $V_{DD} = 5V$         |     | -15      | 50    |      |

|                                     | Address to E                                                   | $V_{DD} = 10V$        |     | 0        | 30    | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | 0        | 20    |      |

| t <sub>н</sub>                      | Minimum Hold Time                                              | $V_{DD} = 5V$         |     | -50      | 15    |      |

|                                     | Address to E                                                   | $V_{DD} = 10V$        |     | -20      | 10    | ns   |

|                                     |                                                                | $V_{DD} = 15V$        |     | -15      | 5     |      |

| C <sub>PD</sub>                     | Power Dissipation                                              | Per Package           |     | 100      |       | pF   |

|                                     | Capacitance                                                    | (Note 5)              |     |          |       | •    |

| C <sub>IN</sub>                     | Input Capacitance                                              | Any Input             |     | 5.0      | 7.5   | pF   |

Note 4: AC Parameters are guaranteed by DC correlated testing.

Note 5: Dynamic power dissipation (P<sub>D</sub>) is given by:  $P_D = (C_{PD} + C_L) V_{CC}^2 f + P_Q$ ; where  $C_L = load$  capacitance; f = frequency of operation; for further details, see Application Note AN-90, "Family Characteristics".

CD4724BC 8-Bit Addressable Latch

www.fairchildsemi.com