Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

### **FEATURES**

- IEEE 802.3 compliant 10Base-T and 100Base-X Physical Interface.

- Media Supported:

- 10Base-T

- 100Base-TX

- 100Base-FX (with optional fiber transceiver installed)

- IEEE 802.3u MII Interface with extended register support.

- LED indicators for Power, Link Status, Collision, Full/Half Duplex, Transmit Activity, Receive Activity, 100 Mb/s Speed, and 10 Mb/s Speed.

- Hardware configurable through jumper settings, or software configurable through the MII interface.

- Operates from single 5 V supply, or may be optionally configured for interface to 3.3 V MII.

#### **ORDERING INFORMATION**

CS8952-CQ 0° to +70° C CDB8952 100-pin TQFP Evaluation Board

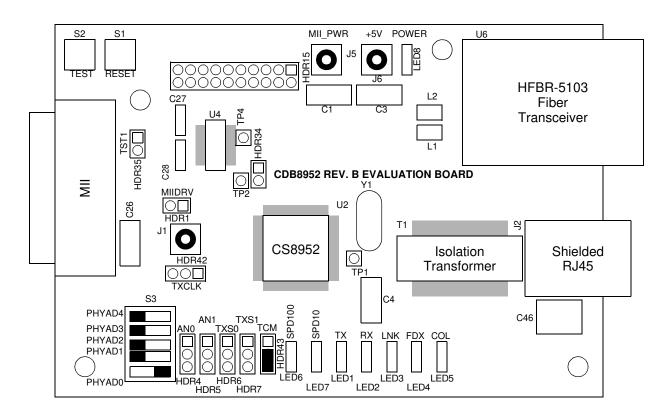

# Crystal LAN™ 10Base-T and 100Base-X Transceiver Evaluation Board

### DESCRIPTION

The CDB8952 Evaluation Board provides a platform for evaluating the CS8952 10Base-T and 100Base-X Transceiver. It is designed to plug into a transceiver test box via a standard 40-pin MII connector. System designers can use the CDB8952 to fully exercise the CS8952 without the time and expense of custom prototyping.

Though the CBD8952 is configured from the factory for 5 V operation with the power supplied from the test box, it may also be configured for 3.3 V MII systems.

The CDB8952 may be optionally configured with a fiber interface module for 100Base-FX testing.

#### CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

#### INTRODUCTION

This manual provides information specifically on the CDB8952 Evaluation board and generally on any design incorporating the CS8952 Crystal-LAN<sup>TM</sup> 10Base-T and 100Base-X Transceiver.

The reader should have a general knowledge of hardware design and Ethernet operation.

# **Background Information**

- IEEE Std 802.3u-1995 (ISO/IEC 8802.3:1996)

CSMA/CD Access Method and Physical Layer Specifications

- IEEE Std 802.3u-1995 Supplement Clause 28 (Auto-Negotiation)

- CS8952 CrystalLAN<sup>™</sup> 10Base-T and 100Base-X Transceiver Datasheet

#### **Evaluation Kit Contents**

The CDB8952 Evaluation Board Kit includes the following:

| Quantity | Item                     |  |

|----------|--------------------------|--|

| 1        | CDB8952 Evaluation Board |  |

| 1        | CS8952 Datasheet         |  |

| 1        | CDB8952 Reference Manual |  |

| 1        | CDB8952 Kit Packing List |  |

**Table 1. Evaluation Kit Contents**

#### **BOARD CONFIGURATION**

#### I/O Connectors

- J1 External TX\_CLK. This connector may be used to supply TX\_CLK when HDR42 and HDR43 are set appropriately.

- J2 RJ45, Twisted-pair Media (Table 2).

| Pin | Function |  |  |

|-----|----------|--|--|

| 1   | TD+      |  |  |

| 2   | TD-      |  |  |

| 3   | RD+      |  |  |

| 4   | -        |  |  |

| 5   | -        |  |  |

| 6   | RD-      |  |  |

| 7   | -        |  |  |

| 8   | -        |  |  |

Table 2. Twisted-pair Media

- J5 MII Power. When the board is connected to a system that does not supply power through the MII connector, +5 V or +3.3 V must be supplied here.

- J6 CS8952 Core Power. +5 V must be supplied here from either J5 (if +5 V is supplied through the MII connector) or an external power supply.

- J13 MII Connector (Table 3).

| Pin | Function   | Pin | Function  |

|-----|------------|-----|-----------|

| 1   | MII Power  | 21  | MII Power |

| 2   | MDIO       | 22  | Ground    |

| 3   | MDC        | 23  | Ground    |

| 4   | RXD3       | 24  | Ground    |

| 5   | RXD2       | 25  | Ground    |

| 6   | RXD1       | 26  | Ground    |

| 7   | RXD0       | 27  | Ground    |

| 8   | RX_DV      | 28  | Ground    |

| 9   | RX_CLK     | 29  | Ground    |

| 10  | RX_ER/RXD4 | 30  | Ground    |

| 11  | TX_ER/TXD4 | 31  | Ground    |

| 12  | TX_CLK     | 32  | Ground    |

| 13  | TX_EN      | 33  | Ground    |

| 14  | TXD0       | 34  | Ground    |

| 15  | TXD1       | 35  | Ground    |

| 16  | TXD2       | 36  | Ground    |

| 17  | TXD3       | 37  | Ground    |

| 18  | COL        | 38  | Ground    |

| 19  | CRS        | 39  | Ground    |

| 20  | MII Power  | 40  | MII Power |

Table 3. MII Connector

# **Configuration Jumpers and Switches**

- S1 Board Reset. Depressing this push-button switch will force the CS8952 into a reset state.

- S2 Test 1 (not populated). This switch is used to select a factory test mode, and should not be pressed during normal operation.

- S3 Physical Address Select. This 5-position switch is used to select the physical address to which the CS8952 will respond. "Open" or "Off" will set the corresponding physical address bit to ZERO, while "Closed" or "On" will set it to ONE. The CS8952 checks the positions of this switch only during power-up or reset. If any switch position is changed, a reset or power cycle is required before the new settings will take effect.

#### CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

NOTE: Physical address 00000 is a special broadcast address. All devices will respond to this address in addition to the one selected using S3. Setting S3 to 00000 will cause the CS8952 to set the ISOLATE bit in the Basic Mode Control Register, isolating itself from all MII signals except MDC and MDIO. It will remain isolated until this bit is cleared.

Care should be taken when reading from physical address 00000 when multiple devices reside on the same MII.

HDR1 - MII Drive Select. When this header is left open, the CS8952 MII drivers will conform to the IEEE 802.3u specification. When a shorting cap is installed, the CS8952 MII drivers will be reduced to 4mA.

The CS8952 checks the status of HDR1 only during power-on or reset. A reset or power cycle is required before any changes in this jumper setting will take effect.

HDR4, HDR5 - Auto-Negotiation Select 0 and 1. These headers are used to select the forced or advertised auto-negotiation modes as indicated in Table 4.

| HDR5     | HDR4     |        | Forced/ | Full/Hal  |

|----------|----------|--------|---------|-----------|

| (AN1)    | (AN0)    | Speed  | Auto    | f Duplex  |

| pins 2-3 | open     | 10     | Forced  | Half      |

| shorted  |          |        |         |           |

| pins 1-2 | open     | 10     | Forced  | Full      |

| shorted  |          |        |         |           |

| open     | pins 2-3 | 100    | Forced  | Half      |

|          | shorted  |        |         |           |

| open     | pins 1-2 | 100    | Forced  | Full      |

|          | shorted  |        |         |           |

| open     | open     | 100/10 | Auto    | Full/Half |

| pins 2-3 | pins 2-3 | 10     | Auto    | Half      |

| shorted  | shorted  |        |         |           |

| pins 2-3 | pins 1-2 | 10     | Auto    | Full      |

| shorted  | shorted  |        |         |           |

| pins 1-2 | pins 2-3 | 100    | Auto    | Half      |

| shorted  | shorted  |        |         |           |

| pins 1-2 | pins 1-2 | 100    | Auto    | Full      |

| shorted  | shorted  |        |         |           |

**Table 4. Auto-Negotiation Select**

The CS8952 checks the status of HDR4 and HDR5 only during power-on or reset. A reset or power cy-

cle is required before any changes in these jumper settings will take effect.

HDR6, HDR7 - Transmit Slew Rate Select 0 and 1. These headers are used to select the rise and fall times of the 100BASE-TX transmitter output waveform as indicated in Table 5.

| HDR7             | HDR6             | Rise/Fall |

|------------------|------------------|-----------|

| (TXSLEW1)        | (TXSLEW0)        | Time      |

| pins 2-3 shorted | pins 2-3 shorted | 0.5 ns    |

| open             | pins 2-3 shorted | 1.0 ns    |

| pins 1-2 shorted | pins 2-3 shorted | 1.5 ns    |

| pins 2-3 shorted | open             | 2.0 ns    |

| open             | open             | 2.5 ns    |

| pins 1-2 shorted | open             | 3.0 ns    |

| pins 2-3 shorted | pins 1-2 shorted | 3.5 ns    |

| open             | pins 1-2 shorted | 4.0 ns    |

| pins 1-2 shorted | pins 1-2 shorted | 4.5 ns    |

**Table 5. Transmit Slew Rate**

HDR15 - Table 6 describes the effect of shorting the listed pin pairs.

HDR34 - Test 0. This header is for factory test purposes only, and should be left open for normal operation.

HDR35 - Test 1. This header is for factory test purposes only, and should be left open for normal operation.

HDR42 - TX\_CLK Source Select. This header, in conjunction with HDR43, is used to select the TX\_CLK source. When pins 1 and 2 are selected, TX\_CLK is supplied from the CS8952 CLK25 output. When pins 2 and 3 are shorted, TX\_CLK is supplied externally from J1. When no shorting cap is installed, HDR43 must be configured so that TX\_CLK is an output from the CS8952.

**NOTE:** No shorting cap should be installed on this header when TX\_CLK is configured as an output (see HDR43).

HDR43 - TX\_CLK Mode Select. (Table 7)

The CS8952 checks the status of HDR43 only during power-on or reset. A reset or power cycle is required before any changes in this jumper setting will take effect.

#### CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

| Pins  | Function             | Description                                                                         |  |

|-------|----------------------|-------------------------------------------------------------------------------------|--|

| 1-2   | Low Power Start      | The CS8952 will enter a low power mode following reset. Only the circuitry          |  |

|       |                      | necessary to maintain media impedance and the MII Serial Management                 |  |

|       |                      | Interface will be operational. The CS8952 checks the status of these pins only      |  |

|       |                      | during power-on or reset. A reset or power cycle is required before any change      |  |

|       |                      | in this jumper setting will take effect.                                            |  |

| 3-4   | MII Receive Enable   | MII signals RXD[3:0], RX_CLK, RX_DV, and RX_ER are tristated.                       |  |

| 5-6   | Power Down           | The CS8952 is forced into a low power mode. Only the circuitry necessary to         |  |

|       |                      | maintain media impedance will be operational.                                       |  |

| 7-8   | CRS Mode Control     | The CRS pin will be asserted for receive activity only. The CS8952 checks the       |  |

|       |                      | status of these pins only during power-on or reset. A reset or power cycle is       |  |

|       |                      | required before any changes in this jumper setting will take effect.                |  |

| 9-10  | Bypass Scrambler     | The scrambler and descrambler are bypassed, and NRZI FX mode is enabled.            |  |

|       |                      | The CS8952 checks the status of these pins only during power-on or reset. A         |  |

|       |                      | reset or power cycle is required before any changes in this jumper setting will     |  |

|       |                      | take effect.                                                                        |  |

| 11-12 | Bypass 4B/5B Coders  | The 4B5B encoder and decoder are bypassed and 5-bit code groups are used.           |  |

|       |                      | RX_ER is used as the fifth receive bit, and TX_ER as the fifth transmit bit. The    |  |

|       |                      | CS8952 checks the status of these pins only during power-on or reset. A reset or    |  |

|       |                      | power cycle is required before any changes in this jumper setting will take effect. |  |

| 13-14 | Bypass Symbol        | 4B5B coders, scramblers, and NRZI coders are all bypassed, and the CS8952           |  |

|       | Alignment            | will make no attempt to identify code-group boundaries. Data on RXD[4:0] and        |  |

|       |                      | TXD[4:0] may contain bits from two code groups. The CS8952 checks the status        |  |

|       |                      | of these pins only during power-on or reset. A reset or power cycle is required     |  |

|       |                      | before any changes in this jumper setting will take effect.                         |  |

| 15-16 | Loopback             | The CS8952 will be placed in loopback mode. When operating in 100 Mb/s              |  |

|       |                      | mode, the loopback will be inside the PMD block, and scrambled NRZI data will       |  |

|       |                      | be routed directly to the NRZI input port on the descrambler. When in 10 Mb/s       |  |

|       |                      | mode, the CS8952 will perform a local ENDEC loopback.                               |  |

| 17-18 | MII Isolate          | The CS8952 will exit from reset with all MII signals tristated except MDIO and      |  |

|       |                      | MDC. The CS8952 checks the status of these pins only during power-on or reset.      |  |

|       |                      | A reset or power cycle is required before any changes in this jumper setting will   |  |

|       |                      | take effect.                                                                        |  |

| 19-20 | 10BASE-T Serial Mode | If the CS8952 is in 10 Mb/s mode, data is transferred serially on RXD0 and          |  |

|       |                      | TXD0, and the full MII interface is disabled. When the CS8952 is in 100Mb/s         |  |

|       |                      | mode, shorting these pins has no effect. The CS8952 checks the status of these      |  |

|       |                      | pins only during power-on or reset. A reset or power cycle is required before any   |  |

|       |                      | changes in this jumper setting will take effect.                                    |  |

Table 6. Effect of shorting the listed pin pairs

| HDR43            | TX_CLK pin | CLK25 pin    |

|------------------|------------|--------------|

| pins 1-2 shorted | input      | 25 MHz clock |

| open             | input      | not used     |

| pins 2-3 shorted | output     | not used     |

Table 7. TX\_CLK Mode Select

**NOTE:** When TX\_CLK is an input, a shorting cap must installed on HDR42 to supply TX\_CLK to the CS8952 (see HDR42).

### **LED Indicators**

LED1 - Transmitter Active Indicator.

LED2 - Receiver Active Indicator.

LED3 - Link OK Indicator.

LED4 - Full Duplex Indicator.

LED5 - Collision Indicator.

# CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

### 3.3V Power Supply Option

Outlined below are several different way to supply power to the CDB8952 evaluation board.

5 V Supplied Through the MII Connector - When the CDB8952 is connected to a system which supplies +5 V through the MII connector, J5 and J6 may be connected together via a short cable. Alternatively, J6 may be connected to an external +5 V supply and J5 left unconnected.

**NOTE:** Under no circumstances should J5 be connected to an external power supply if power is also supplied through the MII connector.

3.3V Supplied Through the MII Connector -When the CDB8952 is connected to a system which supplies +3.3 V through the MII connector, J6 must be connected to an external +5 V supply and J5 left unconnected.

No Power Supplied Through the MII Connector - When the CDB8952 is connected to a system which does not supply power through the MII connector, J5 and J6 may both be connected to a single external +5 V supply. Alternatively, J5 may be connected to an external +3.3V supply and J6 to an external +5 V supply.

# 100Base-FX Interface Option

The CDB8952 board has been designed to accommodate a Hewlett Packard HFBR-5103 Fiber Transceiver Module.

### **BOARD ASSEMBLY NOTES**

# **Magnetics Vendors**

| Vendor                  | Part Number  |

|-------------------------|--------------|

| Bel Fuse Inc.           | S558-5999-46 |

| 198 Van Vorst St.       |              |

| Jersey City, NJ 07302   |              |

| (201) 432-0463          |              |

| www.belfuse.com         |              |

| Halo Electronics, Inc.  | TG22-3506ND  |

| P.O.Box 5826            |              |

| Redwood City, CA 94063  |              |

| (650) 568-5800          |              |

| www.haloelectronics.com |              |

| Pulse Engineering, Inc. | PE-68515     |

| 12220 World Trade Dr.   |              |

| San Diego, CA 92128     |              |

| (619) 674-8100          |              |

| www.pulseeng.com        |              |

## **Crystal Vendors**

| Vendor                    | Part Number     |

|---------------------------|-----------------|

| Raltron Electronics Corp. | AS-25.000-15-F- |

| 10651 NW 19th St.         | EXT-SMD-TR-CIR  |

| Miami, FL 33172           |                 |

| (305) 593-6033            |                 |

| www.raltron.com           |                 |

# **Fiber Module Vendors**

| Vendor                     | Part Number |

|----------------------------|-------------|

| Hewlett Packard Components | HFBR-5103   |

| Sales Response Center      |             |

| (408) 654-8675             |             |

| www.hp.com/HP-COMP         |             |

### **NETCOM X-1000 TEST NOTE**

The Netcom X-1000 Fast Ethernet Tester has been known to assert TX\_EN during power up or when an MII transceiver is hot plugged into the device. This does not comply with the IEEE 802.3u-1995 specification, paragraph 22.2.2.3 TX\_EN (transmit enable). The CS8952 will fail to generate TX\_CLK following its power-on reset sequence under either of these conditions. This was intended to keep the CS8952 from sending runt packets onto the network at power-on.

CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

The X-1000 state machine is dependent on TX\_CLK resulting in a mutually exclusive condition. It will not de-assert TX\_EN without TX\_CLK present. This behavior has only been seen on Netcom X-1000 test hardware.

Work-around: Power on the X-1000 with the Netcom supplied transceivers. Remove one or both transceivers and replace with the CBD8952.

This incompatibility will be addressed in Rev C. of the CS8952.

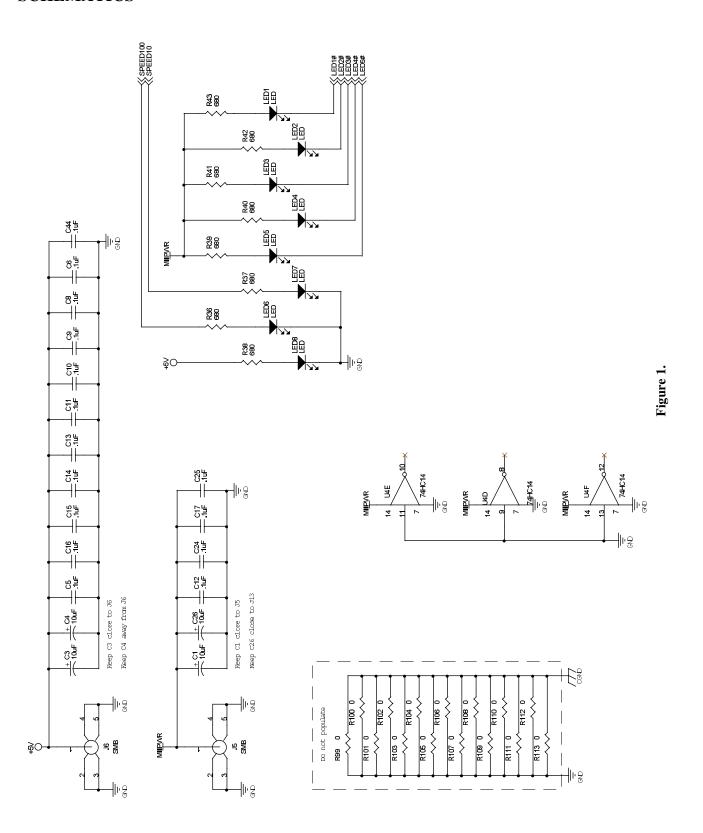

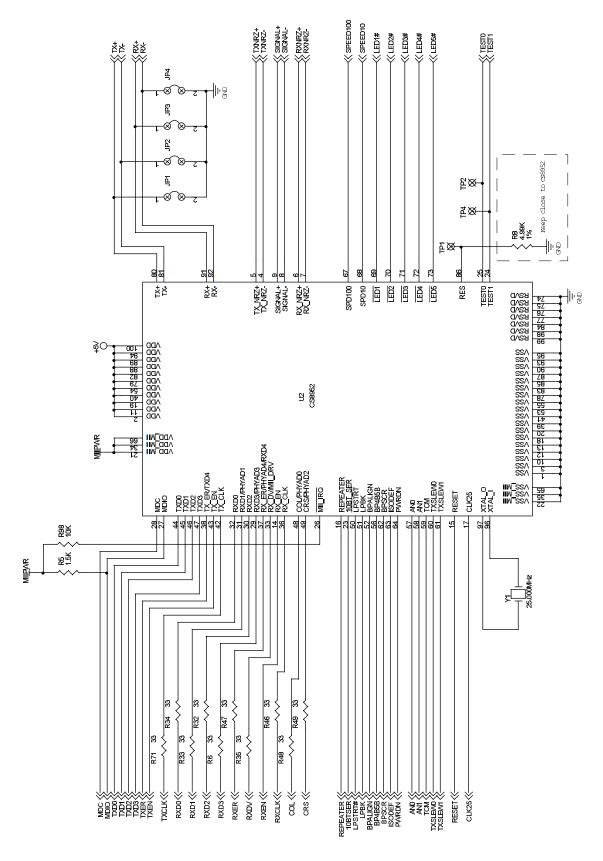

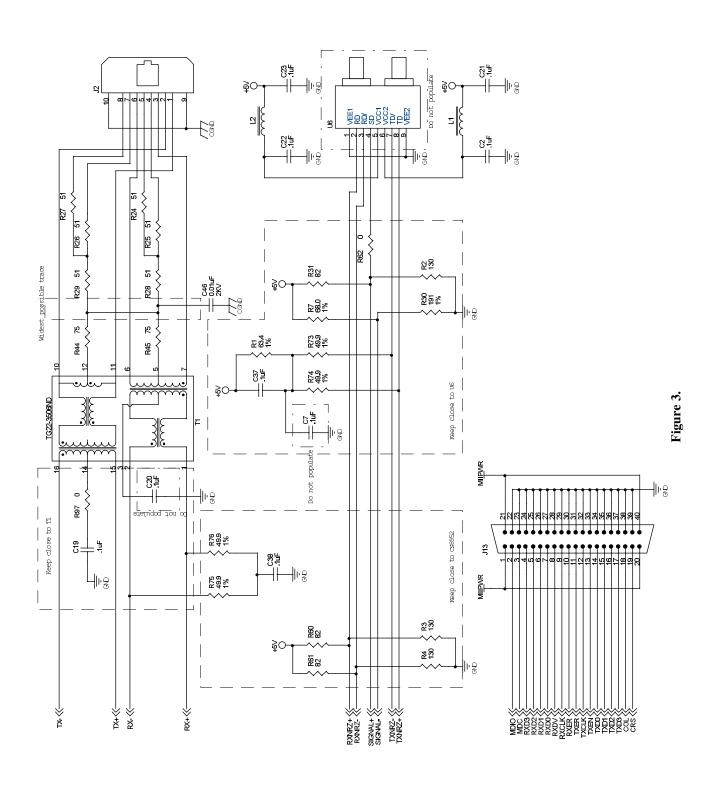

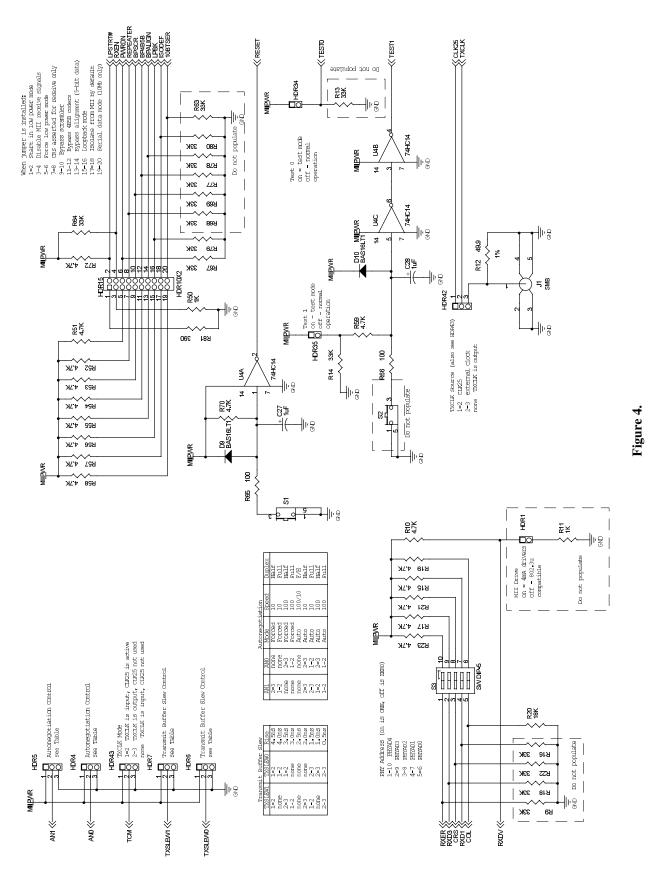

# **SCHEMATICS**

Figure 2.

CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

CIRRUS LOGIC ADVANCED PRODUCT DATABOOK

# **CDB8952 BILL OF MATERIALS**

| Ref. Des.                     | Description                      | Manufacturer | Part Number      |

|-------------------------------|----------------------------------|--------------|------------------|

| C1, C3, C4, C26               | Cap, Tant, 10uF, 20V, 20%, 6032  | Kemet        | T491C106M020AS   |

| C2, C5-C17, C19-C25, C37,     | Cap, X7R, 0.1uF, 50V, 10%, 0805  | Kemet        | C0805C104K5RAC   |

| C38, C44                      | ·                                |              |                  |

| C27, C28                      | Cap, Tant, 1uF, 20V, 20%, 3216   | Kemet        | T491A105M020AS   |

| C46                           | Cap, X7R, 0.01uF, 2KV, 20%, 2225 | AVX          | 2225GC103MA11A   |

| D9, D10                       | Diode, BAS16LT1, SOT23           | Motorola     | BAS16LT1         |

| HDR1, HDR34, HDR35            | Header, 2x1, 0.1" centers        |              |                  |

| HDR4-HDR7, HDR42, HDR43       | Header, 3x1, 0.1" centers        |              |                  |

| HDR15                         | Header, 10x2, 0.1" centers       |              |                  |

| J1, J5, J6                    | Conn, SMB                        | Amp          | 413990-1         |

| J2                            | Conn, RJ45, shielded             | Amp          | 558575-1         |

| J13                           | Conn, MII                        | Fujitsu      | FCN238P040-G/S   |

| LED1-LED8                     | LED, Green, SMT                  | Panasonic    | LN1351C-TR       |

| L1, L2                        | Ferrite Bead, 1206               | TDK          | CB70-1812        |

| R1                            | Res, 63.4Ω, 1%, 1/10W, 0805      | Bourns       | CR0805-FX-63R4-E |

| R2-R4                         | Res, 130Ω, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-131-E  |

| R5                            | Res, 1.5KΩ, 5%, 1/10W, 0805      | Bourns       | CR0805-JX-152-E  |

| R6, R32-R35, R46-R49, R71     | Res, 33Ω, 5%, 1/10W, 0805        | Bourns       | CR0805-JX-330-E  |

| R7                            | Res, 68Ω, 1%, 1/10W, 0805        | Bourns       | CR0805-FX-68R0-E |

| R8                            | Res, 4.99KΩ, 1%, 1/10W, 0805     | Bourns       | CR0805-FX-4991-E |

| R9, R13, R14, R16, R18, R22,  | Res, 33KΩ, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-333-E  |

| R63, R64, R67-R69, R77-R80    |                                  |              |                  |

| R10, R15, R17, R19, R21, R23, | Res, 4.7KΩ, 5%, 1/10W, 0805      | Bourns       | CR0805-JX-472-E  |

| R50-R59, R70, R72             |                                  |              |                  |

| R11                           | Res, 1KΩ, 5%, 1/10W, 0805        | Bourns       | CR0805-JX-102-E  |

| R12, R73-R76                  | Res, 49.9Ω, 1%, 1/10W, 0805      | Bourns       | CR0805-FX-49R9-E |

| R20                           | Res, 18KΩ, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-183-E  |

| R24-R29                       | Res, 51Ω, 5%, 1/10W, 0805        | Bourns       | CR0805-JX-510-E  |

| R30                           | Res, 191Ω, 1%, 1/10W, 0805       | Bourns       | CR0805-FX-1910-E |

| R31, R60, R61                 | Res, 82Ω, 5%, 1/10W, 0805        | Bourns       | CR0805-JX-820-E  |

| R36-R43                       | Res, 680Ω, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-681-E  |

| R44, R45                      | Res, 75Ω, 5%, 1/10W, 0805        | Bourns       | CR0805-JX-750-E  |

| R62, R97, R99-R113            | Res, 0Ω, 1A, 0805                | Bourns       | CR0805-JX-000-E  |

| R65, R66                      | Res, 100Ω, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-102-E  |

| R81                           | Res, 390Ω, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-391-E  |

| R98                           | Res, 10KΩ, 5%, 1/10W, 0805       | Bourns       | CR0805-JX-103-E  |

| S1, S2                        | Switch, NO Push-button           | C&K          | PTS645TL50       |

| S3                            | Switch, 5-position DIP           | CTS          | CTS208-5         |

| TP1, TP2, TP4                 | Testpoint                        |              |                  |

| T1                            | Transformer, Isolation           | See page 5   |                  |

| U2                            | IC, CS8952, TQFP100              | Cirrus       | CS8952-CQ        |

| U4                            | IC, 74HC14, SO14                 | TI           | SN74HC14D        |

| U6                            | IC, HFBR-5103                    | HP           | HFBR-5103        |

| Y1                            | Xtal, 25.00MHz, HC49U            | See page 5   |                  |