# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# CoreCIC v2.0

Handbook

### **Table of Contents**

| Introduction                                     | 3  |

|--------------------------------------------------|----|

| General Description                              | 3  |

| Key Features                                     | 5  |

| Supported Families                               |    |

| Core Version                                     |    |

| Utilization and Performance                      | 5  |

| Theory of Operations                             |    |

| Interface Description                            | 13 |

| Implementation Details                           |    |

| Decimation Filter Timing                         |    |

| Interpolation Filter Timing                      | 26 |

| References                                       |    |

| List of Changes                                  | 31 |

| Product Support                                  | 33 |

| Customer Service                                 |    |

| Customer Technical Support Center                |    |

| Technical Support                                | 33 |

| Website                                          |    |

| Contacting the Customer Technical Support Center | 33 |

| ITAR Technical Support                           |    |

### Introduction

### **General Description**

Microsemi<sup>®</sup> CoreCIC IP is a highly configurable RTL generator for the decimation or interpolation cascaded integrator-comb (CIC) filters. The CIC filters are widely used in multi-rate signal processing, particularly in up-converters and down-converters, modulators and demodulators, sigma-delta analog to digital converters, and so on. These filters are popular in decimation and interpolation filters where substantial rate change factor is required. The CIC filters provide a linear phase response.

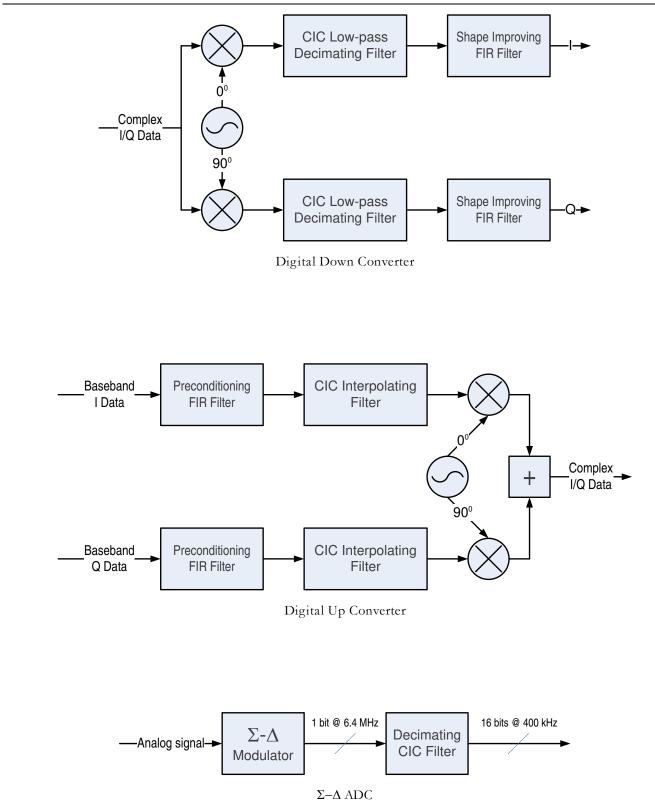

Figure 1 shows a few application examples of the CIC filter.

Figure 1 CIC Filter Application Examples

### Key Features

CoreCIC supports decimation and interpolation filter types. Following are the key features of CoreCIC filter:

- Fixed or programmable rate change from 2 to 1024

- One to eight integrator-comb stages

- Comb differential delay of one or two

- Signed 2's complement input data

- Input data width from 1 to 32 bits

- Output data width up to 100 bits

- · Choice of output data truncation and two rounding types

- Optional Hogenauer pruning

- Support for up to 64 channels

### **Supported Families**

CoreCIC supports the following families:

- SmartFusion<sup>®</sup>2

- IGLOO<sup>®</sup>2

- RTG4™

### Core Version

This handbook applies to CoreCIC v2.0.

### Utilization and Performance

The resource utilization and core performance are shown on Table 1 and Table 2 for SmartFusion2 M2S050 device, speed grade -1.

|                     | -                    | Config                | uration             |              |                 | Resource Utilization |       |           |          | Maximum               |

|---------------------|----------------------|-----------------------|---------------------|--------------|-----------------|----------------------|-------|-----------|----------|-----------------------|

| Input Data<br>Width | Output Data<br>Width | Rate Change<br>Factor | Number of<br>Stages | Number of IF | Channels per IF | 4rn1                 | DFF   | RAM 64x18 | RAM 1K18 | Clock<br>Rate,<br>MHz |

| RAM blo             | cks are no           | t used; Di            | fferential I        | Delay = 1    |                 |                      |       |           |          | -                     |

| 16                  | 16                   | 4                     | 3                   | 1            | 1               | 751                  | 730   | 0         | 0        | 385                   |

| 16                  | 16                   | 4                     | 3                   | 4            | 1               | 1,905                | 1,902 | 0         | 0        | 345                   |

| 16                  | 16                   | 4                     | 3                   | 1            | 5               | 1,452                | 1,706 | 0         | 0        | 314                   |

| 16                  | 16                   | 40                    | 3                   | 1            | 1               | 1,063                | 1,022 | 0         | 0        | 341                   |

| 16                  | 16                   | 40                    | 3                   | 4            | 1               | 2,713                | 2,702 | 0         | 0        | 331                   |

| 16                  | 16                   | 40                    | 3                   | 1            | 5               | 2,030                | 2,388 | 0         | 0        | 313                   |

| 16                  | 16                   | 4                     | 2                   | 1            | 1               | 511                  | 495   | 0         | 0        | 386                   |

| 16                  | 16                   | 4                     | 2                   | 4            | 1               | 1,241                | 1,224 | 0         | 0        | 366                   |

Table 1 CIC Decimator Resource Utilization and Performance

|                     | -                    | Config                | uration             |              | -               | Resource Utilization |         |           |          | Maximum               |

|---------------------|----------------------|-----------------------|---------------------|--------------|-----------------|----------------------|---------|-----------|----------|-----------------------|

| Input Data<br>Width | Output Data<br>Width | Rate Change<br>Factor | Number of<br>Stages | Number of IF | Channels per IF | 4LUT                 | DFF     | RAM 64x18 | RAM 1K18 | Clock<br>Rate,<br>MHz |

| 16                  | 16                   | 4                     | 2                   | 1            | 5               | 956                  | 1,023   | 0         | 0        | 358                   |

| RAM blo             | cks are no           | t used; Di            | fferential I        | Delay = 2    |                 |                      |         |           |          |                       |

| 16                  | 16                   | 4                     | 3                   | 1            | 5               | 1,989                | 2,217   | 0         | 0        | 317                   |

| 16                  | 16                   | 4                     | 5                   | 1            | 1               | 1,849                | 1,959   | 0         | 0        | 336                   |

| 16                  | 16                   | 4                     | 5                   | 4            | 1               | 4,749                | 4,803   | 0         | 0        | 306                   |

| 16                  | 16                   | 4                     | 5                   | 1            | 5               | 3,880                | 4,506   | 0         | 0        | 304                   |

| Use RAM             | l blocks is          | On; Maxi              | mum Micro           | oRAM Dep     | oth=64; Dif     | ferential De         | lay = 1 |           |          |                       |

| 12                  | 16                   | 4                     | 3                   | 4            | 14              | 2,232                | 2,090   | 15        | 0        | 250                   |

| 30                  | 18                   | 4                     | 3                   | 4            | 14              | 4,238                | 4,008   | 30        | 0        | 250                   |

| Use RAM             | l blocks is          | On; Maxi              | mum Micro           | oRAM Dep     | oth=0; Diffe    | erential Dela        | ay = 1  |           |          |                       |

| 12                  | 16                   | 4                     | 3                   | 4            | 16              | 2,244                | 2,096   | 0         | 15       | 287                   |

| 30                  | 18                   | 4                     | 3                   | 4            | 16              | 3,712                | 3,476   | 0         | 15       | 286                   |

| 12                  | 16                   | 4                     | 2                   | 4            | 16              | 1,466                | 1,355   | 0         | 10       | 317                   |

| 30                  | 18                   | 4                     | 2                   | 4            | 16              | 2,479                | 2,299   | 0         | 10       | 317                   |

| Use RAM             | l blocks is          | On; Maxi              | mum Micro           | oRAM Dep     | oth=0; Diffe    | erential Dela        | ay = 2  |           |          |                       |

| 12                  | 16                   | 4                     | 2                   | 4            | 16              | 1,558                | 1,433   | 0         | 10       | 315                   |

| 30                  | 18                   | 4                     | 2                   | 4            | 16              | 2,575                | 2,376   | 0         | 10       | 308                   |

#### Table 1 CIC Decimator Resource Utilization and Performance

| <b>Table 2</b> CIC Interpolator Resource Utilization and Performance |

|----------------------------------------------------------------------|

|----------------------------------------------------------------------|

| Configur            | ation                |                       |                     |              |                 | Resource Utilization |       |           |          | Maximum               |

|---------------------|----------------------|-----------------------|---------------------|--------------|-----------------|----------------------|-------|-----------|----------|-----------------------|

| Input Data<br>Width | Output Data<br>Width | Rate Change<br>Factor | Number of<br>Stages | Number of IF | Channels per IF | 4LUT                 | DFF   | RAM 64x18 | RAM 1K18 | Clock<br>Rate,<br>MHz |

| RAM blo             | cks are no           | t used; Di            | fferential I        | Delay = 1    |                 |                      |       |           |          | I                     |

| 16                  | 16                   | 4                     | 3                   | 1            | 1               | 639                  | 604   | 0         | 0        | 383                   |

| 16                  | 16                   | 4                     | 3                   | 4            | 1               | 1,756                | 1,756 | 0         | 0        | 345                   |

| 16                  | 16                   | 4                     | 3                   | 1            | 5               | 1,335                | 1,554 | 0         | 0        | 330                   |

| 16                  | 16                   | 40                    | 3                   | 1            | 1               | 716                  | 667   | 0         | 0        | 333                   |

| 16                  | 16                   | 40                    | 3                   | 4            | 1               | 1,905                | 1,886 | 0         | 0        | 327                   |

| 16                  | 16                   | 40                    | 3                   | 1            | 5               | 1,447                | 1,703 | 0         | 0        | 320                   |

| 16                  | 16                   | 4                     | 2                   | 1            | 1               | 441                  | 410   | 0         | 0        | 375                   |

| 16                  | 16                   | 4                     | 2                   | 4            | 1               | 1,179                | 1,168 | 0         | 0        | 329                   |

| Configu             | ation                | 1                     | 1                   | 1            | 1               | Resource Utilization |       |           |          | Maximum               |

|---------------------|----------------------|-----------------------|---------------------|--------------|-----------------|----------------------|-------|-----------|----------|-----------------------|

| Input Data<br>Width | Output Data<br>Width | Rate Change<br>Factor | Number of<br>Stages | Number of IF | Channels per IF | 4LUT                 | DFF   | RAM 64x18 | RAM 1K18 | Clock<br>Rate,<br>MHz |

| 16                  | 16                   | 4                     | 2                   | 1            | 5               | 891                  | 1,002 | 0         | 0        | 324                   |

| RAM blo             | cks are no           | t used; Di            | fferential I        | Delay = 2    |                 |                      |       |           |          |                       |

| 16                  | 16                   | 4                     | 3                   | 1            | 5               | 1,622                | 1,870 | 0         | 0        | 316                   |

| 16                  | 16                   | 4                     | 5                   | 1            | 1               | 1,335                | 1,377 | 0         | 0        | 334                   |

| 16                  | 16                   | 4                     | 5                   | 4            | 1               | 3,703                | 3,731 | 0         | 0        | 325                   |

| 16                  | 16                   | 4                     | 5                   | 1            | 5               | 2,927                | 3,478 | 0         | 0        | 301                   |

| Use RAM             | l blocks is          | On; Max               | MicroRAM            | Depth=64     | ; Different     | tial Delay =         | 1     |           |          |                       |

| 11                  | 16                   | 4                     | 3                   | 4            | 14              | 2,246                | 2,118 | 15        | 0        | 250                   |

| 29                  | 18                   | 4                     | 3                   | 4            | 14              | 4,157                | 3,996 | 30        | 0        | 250                   |

| Use RAM             | l blocks is          | On; Max               | MicroRAM            | Depth=0;     | Differentia     | al Delay = 1         |       |           |          |                       |

| 11                  | 16                   | 4                     | 3                   | 4            | 16              | 2,257                | 2,124 | 0         | 15       | 327                   |

| 29                  | 18                   | 4                     | 3                   | 4            | 16              | 3,627                | 3,462 | 0         | 15       | 307                   |

| 11                  | 16                   | 4                     | 2                   | 4            | 16              | 1,500                | 1,392 | 0         | 10       | 340                   |

| 29                  | 18                   | 4                     | 2                   | 4            | 16              | 2,441                | 2,310 | 0         | 10       | 320                   |

| Use RAM             | l blocks is          | On; Max               | MicroRAM            | Depth=0;     | Differentia     | al Delay = 2         |       |           |          |                       |

| 12                  | 16                   | 4                     | 2                   | 4            | 16              | 1,554                | 1,445 | 0         | 10       | 332                   |

| 30                  | 18                   | 4                     | 2                   | 4            | 16              | 2,489                | 2,351 | 0         | 10       | 312                   |

The results shown on Table 1 and Table 2 were achieved at the Operating Conditions COM. The following tools were used:

- Libero v11.4. Required Frequency = 400 MHz

- SynplifyPro H-2013.03M-SP1-1. Frequency = 300 MHz

The other core parameters were set as follows:

- Enable Variable Rate = No

- Apply Hogenauer Pruning = No

- Rounding Mode = Truncation

### Theory of Operations

### **Moving Average**

The moving average is one of the most common filters in digital signal processing (DSP) and also called a boxcar filter. As the name implies, it averages a number of L input samples to generate each output sample:

$$y(k) = \frac{1}{L} \sum_{j=0}^{L-1} X(k+j)$$

EQ1

The filter calculates a time domain convolution between an input signal and a boxcar function. A frequency domain counterpart for the boxcar is sin(X)/X, which describes the frequency response of the filter. Hence, sinc filter is another name for moving average and CIC filters.

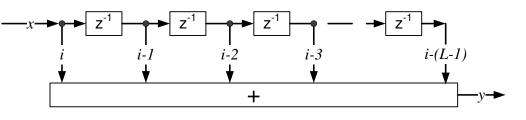

Figure 2 shows block diagram of the moving average filter except dividing the output by L.

Figure 2 Moving Average Block Diagram

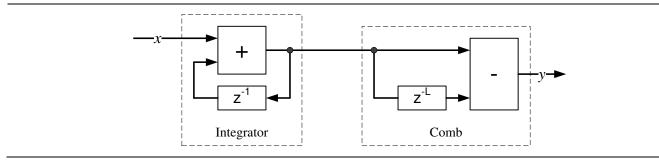

The same result can be obtained by using a recursive form of the boxcar filter as shown in Figure 3. An integrator accumulates input samples, while a comb adds a new accumulated sum and subtracts a delayed by L version of the sum.

Figure 3 Recursive Moving Average

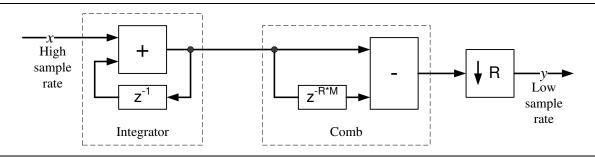

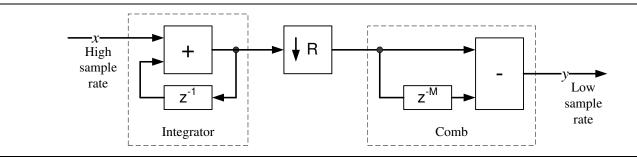

A recursive boxcar decimation filter adds a down-sampler by R where R is the decimation ratio. Figure 4 shows a non-optimized decimation filter assuming the delay L = M \* R, where, M is a constant coefficient called differential delay. M = 1 or 2. The down-sampler by R  $\downarrow$ R discards R-1 output samples from every R samples.

Figure 4 Non-optimized Boxcar Decimator Filter

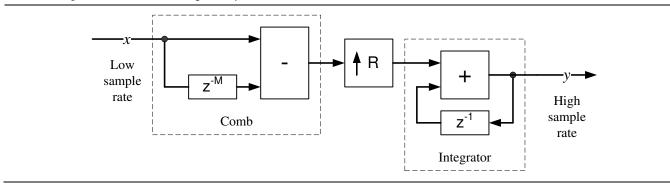

Figure 5 shows a non-optimized interpolation filter structure.

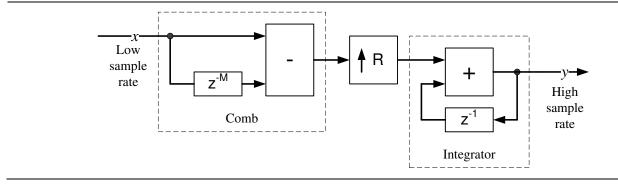

Figure 5 Boxcar Interpolation Filter (Non-optimized)

### **CIC Filter Structures**

A CIC decimation filter is based on an optimized structure obtained from the non-optimized boxcar decimator block diagram as shown in Figure 4 (see References, 1 and 2). Figure 6 shows a one-stage CIC filter block diagram after placing the downsampler between the integrator and comb filter.

Figure 6 One-Stage CIC Decimation Filter

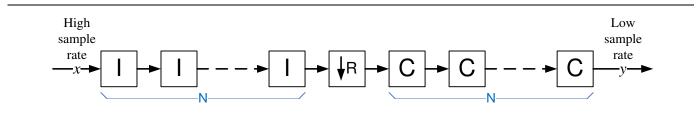

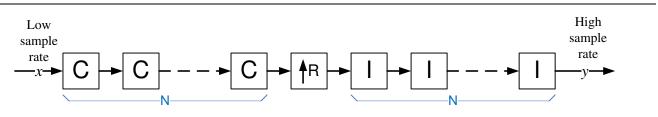

Figure 7 shows a cascaded N-stage decimation CIC filter where the integrators and combs are denoted as I and C, respectively. The filter contains N integrators and N combs. The frequency response is same as N cascaded boxcar filters.

Figure 7 N-Stage Decimation CIC filter

An interpolation CIC filter optimizes the structure, refer to Figure 5.

Figure 8 shows a one-stage interpolation CIC filter.

Figure 8 One-Stage CIC Interpolation Filter

Figure 9 shows an N-stage interpolation CIC filter.

Figure 9 N-Stage Interpolation CIC Filter

The CIC filter implementations are preferred over other rate changing filters because they only use adders and delays but not multipliers.

If the impulse response of a one- stage boxcar filter has a width of M \* R, the N cascades of identical boxcar filters have the overall Impulse Response Width of (M\*R-1)\*N+1.

EQ3 describes the system response of the CIC filter (see Reference 3):

$$H(z) = \left[\sum_{k=0}^{M*R-1} z^{-k}\right]^{N}$$

EQ2

### **Multiple Channel Support**

#### **Multiple Interfaces**

CIC filters of same configuration can share adders, subtractors, and other resources to process more channels, if the required data processing rate is relatively slow. This rate is always low for the CIC filter comb section where comb processing rate is R times lower than the processing rate of the integrator section, refer to Figure 7 and Figure 9. Thus a single comb can support up to R integrator sections. To fully utilize the comb section throughput, a CIC filter needs R integrator sections, each processing data at high sampling rate. In this handbook, such resource sharing is called comb sharing.

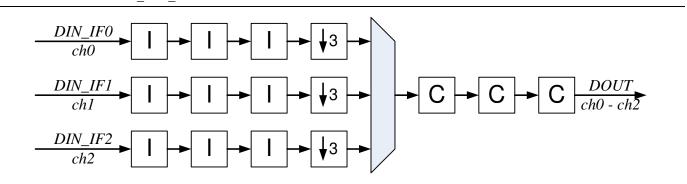

Figure 10 shows a 3-channel filter with a decimation factor,  $R_RATE = 3$ . The CIC filter has three integrator sections, and is capable of filtering three input samples per clock. The data samples from the channels are fed at each clock interval.

The downsampled data from integrator are multiplexed so that each channel data occupies a separate time slot of one clock cycle. The comb section utilizes the three clock intervals (obtained due to reduction in the rate by a factor of 3) to process the integrated data samples.

Figure 10 shows a structure that has three interfaces namely, DIN\_IF0, DIN\_IF1, DIN\_IF2 and one output for the time-multiplexed output samples. For the core to generate the structure of three interfaces, one channel per interface CIC decimator, set the parameters as follows:

- IF NUM = 3

- CLK PER SAMPLE = 1

Figure 10 Three Interfaces, One Channel per Interface CIC Decimator

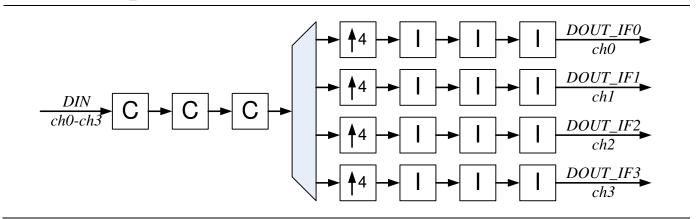

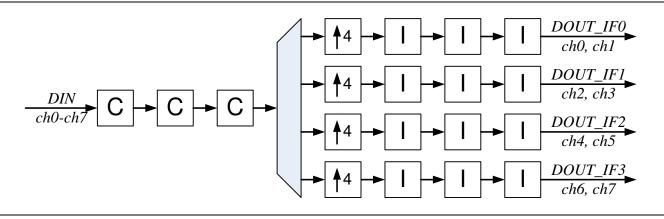

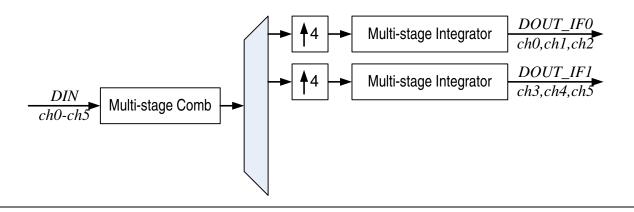

Similarly, the interpolation CIC filter can apply comb sharing to process more channels. Figure 11 shows an example of a 4-channel filter with interpolation rate factor of four. The low rate input channels are time-multiplexed, and the structure provides four output interfaces DOUT\_IF0 to DOUT\_IF3.

Set the parameter as:

- CLK PER SAMPLE = 1

- IF\_NUM = 4

Figure 11 Four Interfaces, One Channel per Interface CIC Interpolator

#### **Comb and Integrator Time Share**

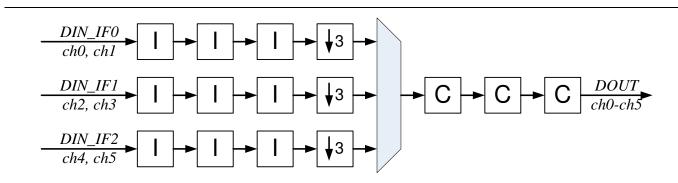

The input samples of each decimation channel can arrive at lower rate than the field programmable gate array (FPGA) clock rate, that is, there are idle clock intervals in between the samples of each input channel. Since they arrive at a lower rate, the integrator sections can be time shared as well. This handbook refers this as time sharing. Figure 12 shows a multi-channel CIC decimation example where input samples of every channel are separated by one idle clock cycle. If this instance is created when  $CLK_PER_SAMPLE = 2$ , each integrator can use two clock intervals, which is adequate to process two channels. The comb section has now six clock intervals, adequate to process all six channels. Every interface supports two channels totaling at  $CLK_PER_SAMPLE^*IF_NUM = 6$  channels.

Figure 12 Three Interfaces, Two Channels per Interface CIC Decimator

The time and comb sharing are independent of each other and can be combined as desired in decimation and interpolation CIC filter types. Figure 13 shows the CIC structure with four output interfaces and two channels per interface, totaling at CLK\_PER\_SAMPLE\*IF\_NUM = 8 channels.

The total number of channels processed by the CIC filter equals the product of the parameters IF\_NUM and CLK\_PER\_SAMPLE. If the product is more than the actual number of channels to be processed, use dummy channels.

CoreCIC automatically identifies multiple channel filters, if the product of IF\_NUM\*CLK\_PER\_SAMPLE > 1 and implements time and/or comb sharing based on the CLK\_PER\_SAMPLE and IF\_NUM parameter values.

Figure 13 Four Interfaces, Two Channels per Interface CIC Interpolator

### **Bit Growth**

Data path width of the CIC filter needs to grow from input to output to support valid processing. The core automatically provides the required bit width for every component of the design. Internally, the processing results are calculated with full precision. You can limit the output bit width by entering a desired value in the Output Data Width field of the IP user interface and select truncation or rounding from **Rounding Mode** drop-down list. The core supports truncation, round away from 0 and convergent rounding (rounding to nearest even number). Either type of rounding or truncation applies to a full precision internal result.

CoreCIC in Decimation mode also supports optional Hogenauer pruning, which limits the intermediate stage bit widths as described in the article by E.Hogenauer. The core does not calculate full precision results even internally but limits their bit width in accordance with the approach by Hogenauer. When the reduced precision internal result still exceeds the desirable output bit width, the truncation or rounding applies similar to the full precision results. The Hogenauer pruning may reduce resource utilization.

### Interface Description

### **Parameters and Generics**

Table 3 describes the CoreCIC parameters (Verilog) or generics (VHDL). All the parameters and generics are positive integer type numbers.

| Parameter Name | Valid<br>Range | Default | Description                                                                                                                                                                                                                                                                                                                       |

|----------------|----------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| N_STAGES       | 1-8            | 3       | Number of cascaded stages. There is always equal number of integrator and comb stages. Any selected number N_STAGES means the CIC filter has N_STAGES of integrators and N_STAGES of combs.                                                                                                                                       |

| M_DLY          | 1, 2           | 1       | Differential comb delay M.                                                                                                                                                                                                                                                                                                        |

| CIC_TYPE       | 0, 1           | 0       | 0: Decimation CIC filter.<br>1: Interpolation CIC filter.                                                                                                                                                                                                                                                                         |

| DIN_WIDTH      | 1-32           | 18      | Input data bit width.                                                                                                                                                                                                                                                                                                             |

| VAR_RATE       | 0, 1           | 0       | 0: Fixed rate change factor.<br>1: Variable programmable rate change factor.                                                                                                                                                                                                                                                      |

| R_RATE         | 2-1024         | 4       | Rate change factor R. If variable rate change is disabled VAR_RATE = 0, the R_RATE defines fixed rate change factor. Otherwise it defines an initial value of the variable factor set upon core configuration.                                                                                                                    |

| VAR_R_MIN      | 2-1023         | 4       | Minimal variable rate change factor. Available only if VAR_RATE is set.                                                                                                                                                                                                                                                           |

| VAR_R_MAX      | 3-1024         | 5       | Maximal variable rate change factor. Available only if VAR_RATE is set.                                                                                                                                                                                                                                                           |

| PRUNE          | 0-1            | 0       | 1: Apply Hogenauer pruning across decimation filter stages. Available for decimation filter only, that is when CIC_TYPE = 0.                                                                                                                                                                                                      |

|                |                |         | 0: Do not apply pruning.                                                                                                                                                                                                                                                                                                          |

| DOUT_WIDTH     | 2-100          | 18      | Output data bit width. If the width set is less than full output bit width, the core truncates or rounds the filtered data to the DOUT_WIDTH.                                                                                                                                                                                     |

| QUANTIZATION   | 0-2            | 0       | Output data quantization mode. Applies when the output data bit width selected is less than the automatic full precision processing bit width:                                                                                                                                                                                    |

|                |                |         | 0: Truncation mode.                                                                                                                                                                                                                                                                                                               |

|                |                |         | 1: Round away from 0.                                                                                                                                                                                                                                                                                                             |

|                |                |         | 2: Convergent rounding.                                                                                                                                                                                                                                                                                                           |

| IF_NUM         | 1-32           | 1       | Number of interfaces. For decimation filter, it is a number of input<br>interfaces; for interpolation filter it is a number of output interfaces. Each<br>interface is capable of accepting or generating one or more data channels.<br>In other words, IF_NUM indicates a number of physical integrator<br>cascades implemented. |

|                |                |         | IF_NUM cannot exceed the rate change factor R_RATE, that is IF_NUM ≤ R_RATE. In the case of variable rate (VAR_RATE=1), the IF_NUM cannot exceed the value of VAR_R_MIN, that is IF_NUM ≤ VAR_R_MIN.                                                                                                                              |

|                |                |         | Since the channel number of a multichannel filter equals<br>IF_NUM * CLK_PER_SAMPLE, and the maximum channel count is 64,<br>the IF_NUM must not exceed the value of 64/CLK_PER_SAMPLE.                                                                                                                                           |

| CLK_PER_SAMPLE | 1-64           | 1       | Number of FPGA clock cycles per sample of any channel.                                                                                                                                                                                                                                                                            |

|                |                |         | Indicates a number of time-multiplexed channels per interface.                                                                                                                                                                                                                                                                    |

|                |                |         | Since the channel number of a multichannel filter equals<br>IF_NUM * CLK_PER_SAMPLE, and the maximum channel count is 64,                                                                                                                                                                                                         |

#### Table 3 CoreCIC Parameter and Generic Descriptions

| Parameter Name | Valid<br>Range                                    | Default | Description                                                                                                                                                                                                                                                                                                                           |

|----------------|---------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                |                                                   |         | the CLK_PER_SAMPLE must not exceed the value of 64/IF_NUM.                                                                                                                                                                                                                                                                            |

| USE_RAM        | 0, 1                                              | 0       | Use RAM blocks to implement CIC registers.                                                                                                                                                                                                                                                                                            |

|                |                                                   |         | 0: Use only fabric-based register implementations.                                                                                                                                                                                                                                                                                    |

|                |                                                   |         | 1: Permission to use RAM blocks when appropriate.                                                                                                                                                                                                                                                                                     |

| URAM_MAX_DEPTH | 0, 4, 8, 16,<br>32, 64,<br>128, 256,<br>512, 1024 | 0       | Maximum depth of a RAM to be implemented using micro-RAM (uRAM) blocks. If USE_RAM is set, the core uses hard RAM blocks available on a selected FPGA device. When the uRAM blocks are available, the core uses them if the required memory depth does not exceed the URAM_DEPTH. Otherwise it builds the memory out of LSRAM blocks. |

#### Table 3 CoreCIC Parameter and Generic Descriptions

### **Ports**

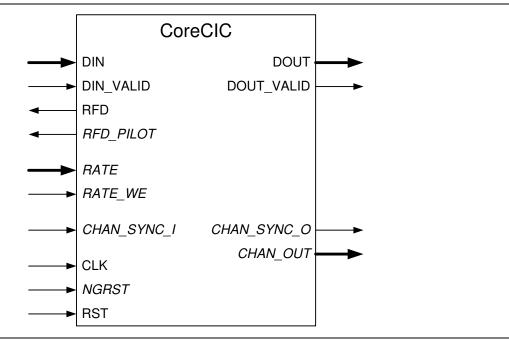

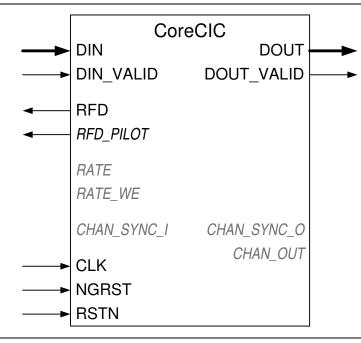

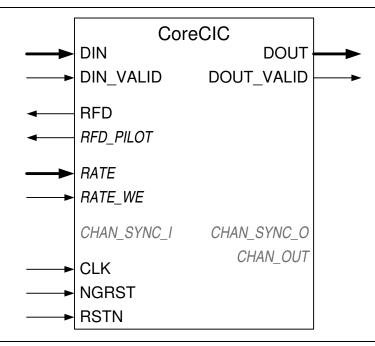

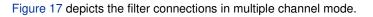

Figure 14 shows the CIC filter schematic representation where optional port names are in Italics.

Figure 14 I/O Ports

The pinout is a superset of all possible ports. Table 4 provides the port definitions for the core.

| Signal      | In/Out | Port Width Bits                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------|--------|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIN         | In     | DIN_WIDTH for<br>Interpolation CIC;<br>DIN_WIDTH*IF_NUM for<br>decimation filter   | Input data to be filtered. In case of interpolation filter or a single channel for any CIC type, the data width equals DIN_WIDTH. In case of decimation filter with multiple Interfaces, the input data width for each interface is DIN_WIDTH and the total input data width = DIN_WIDTH*IF_NUM.                                                                                                                |

| DIN_VALID   | In     | 1                                                                                  | Input data valid. Active High. When the signal is active, the input data sample is loaded into decimation CIC filter. If not used, the core assumes that every data sample is valid.                                                                                                                                                                                                                            |

|             |        |                                                                                    | For the interpolation CIC filter, the signal not only marks the valid input sample but also defines a rate for the interpolated output samples. For example, if DIN_VALID has a duty cycle of three, the output sample rate is three times less than the CLK rate. The input sample of the interpolator is valid, if it is accompanied by DIN_VALID and CHAN_SYNC_I signals. The signal must be one-clock wide. |

| RFD         | Out    | 1                                                                                  | Ready for input data. In case of interpolation filter, the RFD notifies a data source that the CIC filter is ready for a new input sample. In case of decimation filter, the signal goes Low only when integrator reset process is underway. Input data samples are ignored when RFD is Low.                                                                                                                    |

| RFD_PILOT   | Out    | 1                                                                                  | Optional pulse the CIC interpolator generates just before the RFD signal. The pulse width is one clock period. It can be used to let the data source more time to prepare another data sample.                                                                                                                                                                                                                  |

| DOUT        | Out    | DOUT_WIDTH for<br>Decimation CIC;<br>DOUT_WIDTH*IF_NUM<br>for Interpolation filter | Output filtered data. In case of decimation filter or a single<br>channel for any CIC type, the output data width equals<br>DOUT_WIDTH. In case of interpolation filter with multiple<br>Interfaces, the output data width for each interface is<br>DOUT_WIDTH and the total result data width =<br>DOUT_WIDTH*IF_NUM.                                                                                          |

| DOUT_VALID  | Out    | 1 for Decimation CIC;<br>IF_NUM for Interpolation<br>filter                        | Filtered data valid indicates that a new output data sample is present at the DOUT port. For the decimation filter as well as a single interface interpolation filter, the signal is one bit wide. In case of interpolation filter with multiple interfaces, the output data width for each interface is one and the total result signal width = IF_NUM.                                                        |

| RATE        | In     | 11                                                                                 | Variable rate value. The port is available when variable rate change mode is selected, VAR_RATE = 1.                                                                                                                                                                                                                                                                                                            |

| RATE_WE     | In     | 1                                                                                  | Register a new value of the variable RATE. The RATE_WE<br>must be a one-clock wide pulse. The port is available when<br>variable rate change mode is selected, VAR_RATE = 1. After<br>the RATE value is stored in the core, the effective rate factor<br>does not change yet. The new RATE value takes effect after<br>the core receives the synchronous reset RST pulse.                                       |

| CHAN_SYNC_I | In     | 1                                                                                  | Channel synchronization signal. For a decimation filter, it<br>provides an advanced identification for the first data channel<br>when CLK_PER_SAMPLE > 1. For an interpolation filter, the<br>signal is expected to come even if the filter has only one<br>channel. Then the signal marks a time slot when the input                                                                                           |

#### Table 4 CIC Filter In or Out Signals

| Signal      | In/Out | Port Width Bits | Description                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------|--------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |        |                 | sample is valid. For a multichannel interpolator, when<br>CLK_PER_SAMPLE > 1 the signal is supposed to mark the<br>valid input sample of the first time-share channel. The<br>CHAN_SYNC_I must be a one-clock wide pulse.                                                                                                                                                                                             |

| CHAN_SYNC_O | Out    | 1               | Output channel synchronization signal. This clock-wide pulse identifies the first channel data output sample.                                                                                                                                                                                                                                                                                                         |

| CHAN_OUT    | Out    | 6               | Output channel numerical ID.                                                                                                                                                                                                                                                                                                                                                                                          |

| CLK         | In     | 1               | The core master clock.                                                                                                                                                                                                                                                                                                                                                                                                |

| NGRST       | In     | 1               | Optional asynchronous reset. Active Low. The signal is<br>expected to follow the FPGA power-on. The signal initiates<br>reset of all internal registers. If RAM blocks are used to<br>implement integrator or comb registers, the actual reset can<br>take several clock cycles. Then on the rear edge of the<br>NGRST, the core automatically generates an internal reset<br>wide enough to reset all the registers. |

| RST         | In     | 1               | Synchronous reset. Active High. The signal initiates reset of all<br>internal registers. If RAM blocks are used to implement<br>integrator or comb registers, the actual reset can take several<br>clock cycles. Then the RST signal initiates an internal reset<br>wide enough to reset all the registers.                                                                                                           |

#### Table 4 CIC Filter In or Out Signals

Figure 15 and Figure 16 show examples of using the core in fixed and variable rate modes.

Figure 15 Fixed Rate Single Channel CIC Filter

Figure 16 Variable Rate Single Channel CIC Filter

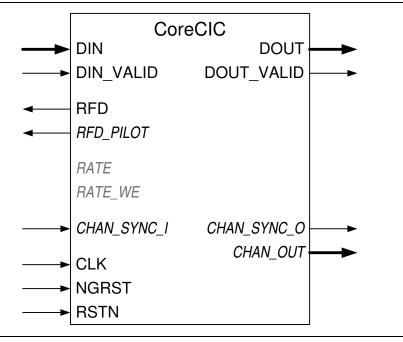

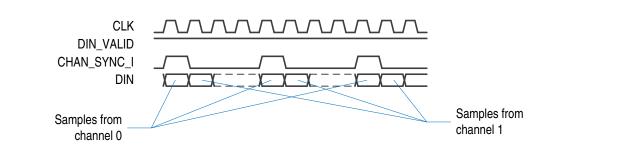

Figure 17 Fixed Rate Multiple Channel Mode

#### **Decimator Interface**

This section describes basics of the CIC decimation functionality. For more information, refer to Implementation Details section.

A decimation filter receives R\_RATE input samples to generate an output sample. The input data samples sequentially arrive at DIN port of a single channel decimator. Every input sample is accompanied by the DIN \_VALID pulse of one clock period. The filter accepts arbitrary gaps between the input samples. The data source indicates the break by de-asserting the DIN \_VALID signal. For maximum throughput, there must not be any gaps in between the input samples. If a data source can supply a new sample for every FPGA clock cycle, attach the DIN \_VALID to VCC. Once the decimator gets R\_RATE input samples, it posts an output filtered sample on the DOUT port after it finishes the sample processing. It also accompanies the valid output sample by the clock-wide DOUT\_VALID signal. The CIC filter introduces processing latency that is described below.

A time share multichannel decimator, where CLK\_PER\_SAMPLE > 1 expects the data samples to come in the natural order. For example, at CLK\_PER\_SAMPLE = 3 the first channel sample comes first, followed by a sample of the second channel and then third channel. Input sample of each channel is accompanied by the DIN\_VALID pulse. Similarly to the single channel, if there are no gaps in between the input samples the DIN\_VALID signal has to be permanently high. The data source identifies the first channel by the CHAN\_SYNC\_I pulse that accompanies the DIN sample of the first channel. In other words, the CHAN\_SYNC\_I pulse is a copy of the DIN\_VALID pulse for the first data channel. The decimator assigns the channels numerical IDs, from 0 to 2. On receiving R\_RATE input samples from all channels, the decimator outputs filtered DOUT data, one sample at a time for the channels 0 to 2. The output channels are accompanied by the DOUT\_VALID pulses. The DOUT output for the channel 0 is accompanied by the CHAN\_SYNC\_O pulse. The CHAN\_SYNC\_O is a copy of the channel 0 DOUT\_VALID signal. CHAN\_OUT provides the number of channels currently posted on the DOUT output. In this example, CHAN\_OUT sends the numbers 0, 1, 2 synchronized with valid output samples.

A multiple interface decimator, where IF\_NUM > 1 expects input data samples to come to each interface, simultaneously. A single DIN\_VALID pulse is used for all interfaces. It signifies another set of IF\_NUM input samples is ready to be received by all interfaces. Similarly to the single channel, if there are no gaps in between the input samples, the DIN\_VALID signal must be permanently High. If multiple interface decimator does not utilize time share, that is the parameter CLK\_PER\_SAMPLE=1, the CHAN\_SYNC\_I signal must replicate the DIN\_VALID pulse. Once the decimator receives R\_RATE input samples on all its interfaces, it starts placing output samples on the DOUT port one channel at a time: an output sample for the channel coming to the interface 0 and the channel coming to the interface 1, and so on. Each output sample is accompanied by the DOUT\_VALID pulse. CHAN\_SYNC\_O marks the channel of the interface 0. CHAN\_OUT supplies the numerical channel IDs synchronized with the output samples.

A multichannel decimator can combine time share and comb share when IF\_NUM > 1 and CLK\_PER\_SAMPLE > 1. The total number of channels processed by such filter equals IF\_NUM\*CLK\_PER\_SAMPLE. Consider an example of a decimator processing six channels: IF\_NUM = 2 and CLK\_PER\_SAMPLE = 3.

The data samples are expected to come to the interface 0 in the following order:

- Sample 0 of the channel 0

- Sample 0 of the channel 1

- Sample 0 of the channel 2

- Sample 1 of the channel 0

- Sample 1 of the channel 1, and so on

Simultaneously the following data is coming to the interface 1:

- Sample 0 of the channel 3

- Sample 0 of the channel 4

- Sample 0 of the channel 5

- Sample 1 of the channel 3

- Sample 1 of the channel 4, and so on

Every sample of the channel 0 to channel 2 is accompanied by DIN\_VALID pulses unless the data is coming without gaps. Samples of the channel 0 are accompanied by the CHAN\_SYNC\_I pulses. Since the data to interfaces 0 and 1 is coming simultaneously, the CHAN\_SYNC\_I pulse marks the channel 3 as well. The filter outputs samples of the channel 0 to 5 sequentially with every sample accompanied by the DOUT\_VALID pulse. The core generates the CHAN\_SYNC\_O pulse when the channel 0 filtered sample shows up at the DOUT output. CHAN\_OUT supplies channel IDs from 0 to 5 synchronized with valid output samples.

Upon reset signals, NGRST or RTS, the decimator enters the reset state. During the reset state, the decimator keeps the RFD signal Low.

Note: The DIN\_VALID pulses are expected to be present at this time but the core ignores any input data while the RFD signal is Low. In the decimation mode, only during the reset state the RFD signal goes Low.

#### **Interpolator Interface**

This section describes basics of the CIC interpolation functionality. For more information, refer to Implementation Details section.

An interpolation filter generates R\_RATE output samples for every input data sample. The input data samples arrive at DIN port of a single channel interpolator spaced by time intervals sufficient for the filter to output R\_RATE filtered samples. To assist a data source in providing minimal sufficient time intervals, the interpolator generates the handshake signals request for data (RFD) and RFD\_PILOT. The interpolator raises the RFD when it is ready to accept a new input sample. The RFD stays High until the data source provides a valid input sample.

Note: The functionality of the DIN\_VALID pulse differs from that of decimation CIC: the signal not only accompanies the valid input samples but also influences interpolated output sample rate. The DIN\_VALID pulse can direct the interpolator to output filtered samples at a fraction of clock rate. For example, it is required that the CIC interpolator generates output samples at every third clock interval. Then the DIN\_VALID duty cycle has to be 1/3, that is the DIN\_VALID pulse comes at every third clock cycle. Since the input sample rate of the interpolation filter is R\_RATE times lower, the valid input sample period of this example equals 3\*R\_RATE. It is accompanied by the CHAN\_SYNC\_I pulse. It means, the valid input sample is accompanied by CHAN\_SYNC\_I and DIN\_VALID pulses.

The RFD\_PILOT is a clock-wide pulse that precedes the RFD signal. The data source can use either or both handshake signals when generating another input data sample.

Note: The interpolator only accepts the data samples that are accompanied by the CHAN\_SYNC\_I signal while the RFD signal is High.

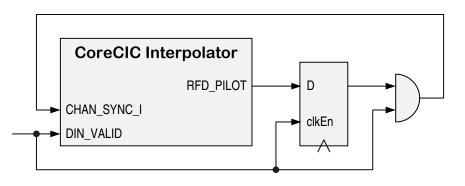

The filter tolerates gaps between the input samples that exceed the minimal time intervals. The filter raises the output RFD signal, and waits for the next valid input sample. For maximum throughput, the data source must supply a fresh input sample on the clock interval following the RFD\_PILOT signal. Then the DIN\_VALID signal must be connected to VCC. The RFD\_PILOT pulse can be used to achieve the highest throughput at any given DIN\_VALID rate, refer to Figure 18.

Figure 18 Using RFD\_PILOT Signal

A time share multichannel interpolator where CLK\_PER\_SAMPLE > 1 expects the data samples to come in the natural order. For example, at CLK PER SAMPLE = 3, the first channel sample comes first followed by a sample of the second channel and the third channel. Samples must be spaced so that the CIC has sufficient time to output interpolated samples at the rate of DIN VALID. It means, an interval between every two consecutive input samples must not be less than R RATE of DIN VALID time intervals. Every input sample is accompanied by the DIN VALID pulse. The data source identifies the first time share channel by the CHAN\_SYNC\_I pulse that accompanies the DIN sample of the first channel. It means, the CHAN\_SYNC\_I is a copy of the DIN\_VALID pulse for the first data channel. The interpolator assigns the channels numerical IDs from 0 to 2. On receiving an input sample from all three channels, the CIC outputs 3\*R\_RATE interpolated DOUT data, one sample at a time: a first interpolated sample for the channel 0, a first interpolated sample for the channel 1 and the first interpolated sample for the channel 2. Then it outputs the second interpolated sample for 0 to 2 channels, the third one and finally the R RATE-1 interpolated sample for the channels 0 to 2. The output channels are accompanied by the DOUT VALID pulses. Their rate equals the rate of DIN\_VALID pulses. If the DIN\_VALID signal is permanently High, the DOUT\_VALID signal also stays High permanently. The DOUT output for the channel 0 is accompanied by the CHAN SYNC O pulse. The CHAN\_OUT provides the number of a channel currently posted on the DOUT output. In this example, the CHAN OUT would output the numbers 0, 1, 2 synchronized with valid output samples.

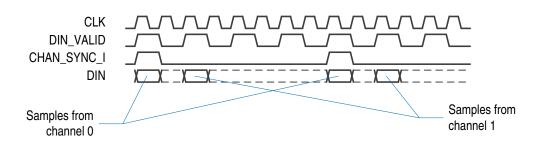

A multiple interface interpolator where IF\_NUM > 1 expects all the input data samples to come to a single data input DIN sequentially: samples 0 of the channels 0 to IF\_NUM-1, then samples 1 of the channels 0 to IF\_NUM-1, etc. Every input sample is accompanied by the DIN\_VALID pulse, and the samples of the channel 0 are additionally accompanied by the CHAN\_SYNC\_I pulses. Only the samples from the same channel have to provide sufficient time interval for the filter to generate interpolated samples. It means, samples from channels 0 to IF\_NUM-1 are supposed to come on every clock or spaced by DIN\_VALID period. Figure 19 shows an example of interpolator input signals when R\_RATE = 4, IF\_NUM = 2, and input data are permanently valid, that is DIN\_VALID = 1. The samples from channel 0 and 1 come without ant interval but the DIN waits for two clock cycles so, the consecutive samples of the same channel are spaced by R\_RATE-1 clock intervals.

Figure 19 Example of Interpolator Input Signals at DIN\_VALID Always Active

Figure 20 shows an example of the same interpolator configuration. The input data is valid on every other clock interval.

Figure 20 Example of Interpolator Input Signals at DIN\_VALID Active Every Other Clock

In both examples, on receiving an input sample from channels 0 and 1, the CIC outputs 4\*R\_RATE interpolated DOUT data, one sample at a time: a first interpolated sample for the channel 0 and a first interpolated sample for the channel 1, refer to Figure 19 and Figure 20. Then it outputs the second interpolated sample for the channels 0 and 1, etc and finally the forth interpolated sample for the channels 0 and 1. The output channels are accompanied by the DOUT\_VALID pulses. Their rate equals the rate of DIN\_VALID pulses. If the DIN\_VALID signal is permanently High, the DOUT\_VALID signal also stays High permanently. The DOUT output for the channel 0 is accompanied by the CHAN\_SYNC\_O pulse.

A multichannel interpolator can combine time share and comb share when IF\_NUM > 1 and CLK\_PER\_SAMPLE > 1. The total number of channels processed by such filter equals IF\_NUM \* CLK\_PER\_SAMPLE. For example, an interpolator processing six channels: IF\_NUM = 2, CLK\_PER\_SAMPLE = 3, and rate changing factor R\_RATE = 4. Figure 21 shows in/out channel mapping.

Figure 21 I/O Channel Mapping for an Interpolator Example

The data samples are expected to come to the interpolator DIN input in the following order: sample 0 of the channel 0, sample 0 of the channel 1, and sample 0 of the channel 5. The interpolated output samples appear on the interface 0 for the channels 0 to 2 and on the interface 1 for the channels 3 to 5.

### **Implementation Details**

### Reset

The CoreCIC filter must be reset to generate correct results. It gets reset automatically on powering ON an FPGA. The core initializes the reset based on positive edge of the NGRST signal that normally follows the power ON. The RST signal initiates the core reset. Depending on the core configuration, the reset state can take several clock cycles to properly initialize the core. Once initiated by NGRST or RST signals, the core ignores any data while the reset state takes place. When the reset state is over, the core raises the RFD signal and the core is ready for normal processing.

Note: The DIN\_VALID pulses are expected to be present during the reset state but the core ignores any input data while the RFD signal is Low.

### Latency

EQ3 describes the core latency expressed in clock CLK cycles when DIN\_VALID is not High permanently:

Latency = N\_STAGES\*(3\*DIN\_VALID+4)+2 Clock Cycles

EQ3

When DIN\_VALID is permanently active, the formula changes to:

Latency = 7\*N\_STAGES+2 Clock Cycles

EQ4

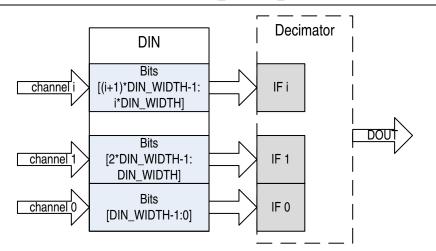

### **Multiple Interface Connections**

Both decimation and interpolation filters can have multiple interfaces (IF\_NUM > 1) to provide connections to high speed data source or data sink. Multiple interface decimator receives data from multiple channels simultaneously, refer to Figure 10 and Figure 12. The data from different channels must be concatenated to form a single DIN word, refer Figure 22. The concatenated DIN word width = IF\_NUM\*DIN\_WIDTH bits.

Figure 22 Data Concatenation for Multiple Interface Decimator

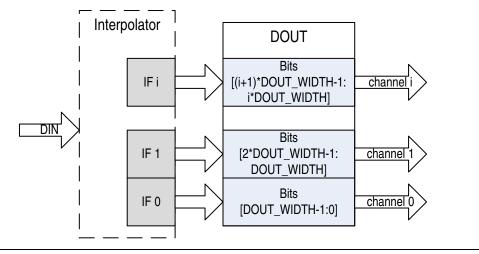

Similarly, the multiple interface interpolator provides parallel data for multiple channels by generating a concatenated DOUT word, refer to Figure 11 and Figure 13. Bits arrangement for the DOUT interpolation word is depicted on Figure 23. The concatenated DOUT word width = IF\_NUM\*DOUT\_WIDTH.

Figure 23 Output Concatenation of a Multiple Interface Interpolator

### **Variable Rate**

In addition, to a fixed upsampling or downsampling rate, the core supports programmable rate change factor. To enable the programmable rate mode, select **Enable Variable Rate** check box and enter the initial Rate Change Factor, Minimum, and Maximum programmable rate values. On power ON, the core automatically uses the Rate Change Factor value. To update the rate change value, you need to provide the desired rate change value on the RATE port of the core and issue a clock wide pulse on the RATE\_WE pin. Then the desired RATE value gets stored inside the core. The core uses the previously entered rate change value or initial Rate Change Factor until the synchronous reset pulse on the RST port is provided. When the core completes its internal reset, the new rate change value is used.

The minimum and maximum programmable rate values are used at the IP generation time to create RTL that can handle the indicated values.

Note: The wider the variable (programmable) rate range, the more FPGA resources will be utilized and potentially lower max clock rate will be achieved.

### **RAM Block Use**

The CIC filter components such as, delay line of the comb section and multiple channel accumulators of the integrator section can be implemented using hard RAM blocks available on FPGA. Such implementation reduces fabric resource utilization and can improve processing speed. The core automatically infers the RAM blocks, if the **Use RAM Blocks** check box is selected. You can decide the RAM blocks to be used, LSRAM or uRAM by providing **Max MicroRAM Depth** value. The core utilizes uRAM blocks whenever the RAM depth required does not exceed the value entered. Otherwise it uses the LSRAM blocks.

### **Decimation Filter Timing**

Figure 24 to Figure 27 show a few examples of decimator timing diagrams. The fixed downsampling rate  $R_RATE = 2$  for all the examples, that is the decimator outputs one sample for every two input samples. The timing diagrams show time intervals immediately after the RFD goes High in response to the NGRST or RST signals issued earlier. This is done to illustrate the Latency time. The timing relations between the signals stay the same indefinitely after.

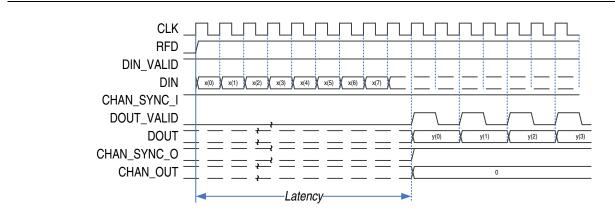

Figure 24 shows a timing diagram for a single channel decimator where data samples come at every clock cycle. It is assumed that the filter has been reset earlier so, that the RFD signal is active. Data samples x(0) and x(1) are coming to the DIN input at every clock cycle from when DIN\_VALID goes High. CHAN\_SYNC\_I for the example should be indefinitely active, as there is only a single channel.

Figure 24 Decimation CIC Timing - Single Channel, Data Permanently Valid

After the latency time of the filter expires, the decimator raises the DOUT\_VALID signal and outputs a decimated sample y(0) on the DOUT port. The DOUT\_VALID signal stays High for a single clock period and then goes Low for R\_RATE clock periods, in this case for one clock period. The DOUT port keeps the output sample until the next DOUT\_VALID pulse starts. Once the DOUT\_VALID pulse gest asserted for the first time since filter reset happened, the CHAN\_SYNC\_O goes High and stays in the active state indefinitely. The CHAN\_OUT outputs the channel number of 0.

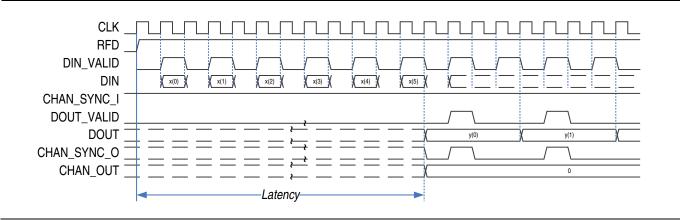

Figure 25 shows a timing diagram for the single channel decimator with data coming every other clock. The input samples x(0) and x(1) are accompanied by the DIN\_VALID pulses. CHAN\_SYNC\_I can be a copy of the DIN\_VALID pulses or just stay High indefinitely. After Latency, the core raises the DOUT\_VALID signal for one clock period and starts outputting the decimated sample y(0), y(1), etc. The DOUT\_VALID pulses are separated by four clock periods. The CHAN\_SYNC\_O signal replicates the DOUT\_VALID signal, and the CHAN\_OUT equals 0.

Figure 25 Decimation CIC Timing - Single Channel, Data Coming Every Other Clock

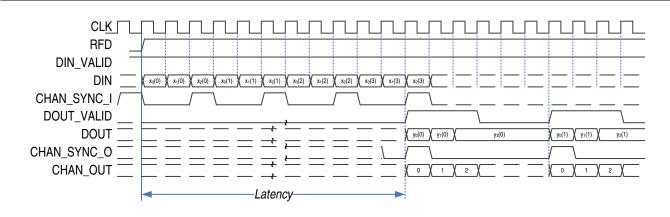

Figure 26 shows an example of a multi-channel decimator timing diagram. In this example, a data source is capable of providing a fresh input sample at every clock interval thus, the DIN\_VALID signal is High permanently. The data comes from three multiplexed time share channels x0, x1 and x2 on the same DIN bus. Multiplexing the three channels into a single bus is possible, as for this example the parameter CLK\_PER\_SAMPLE = 3. CHAN\_SYNC\_I marks every sample of the first channel data x0.

The CHAN\_SYNC\_I is supposed to provide advanced warning when the first channel data is coming, that is it must come immediately before the first channel data x0. Since the channels normally are cyclically multiplexed, it is recommended to raise the CHAN\_SYNC\_I signal when the last channel data is present on the core DIN input. Figure 26 shows the CHAN\_SYNC\_I signal active while the channel x2 data enter the filter.

Figure 26 Decimation CIC Timing - Three Time Share Channels, Data Permanently Valid

Once the decimator is ready to output the filtered samples, it raises the DOUT\_VALID signal that lasts for three clock intervals. Then the DOUT\_VALID signal goes inactive for (R\_RATE-1)\*CLK\_PER\_SAMPLE clock periods, that is for three periods in this example. CHAN\_SYNC\_O marks every output sample of the channel y0, and the CHAN\_OUT counts channels 0 to 2 while the DOUT\_VALID signal is active.

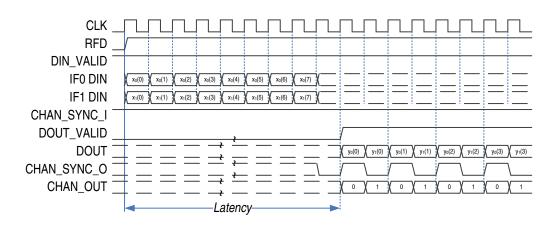

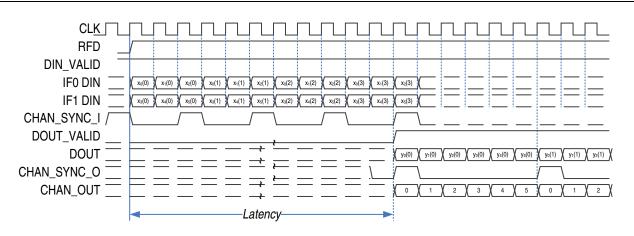

Figure 27 shows a timing diagram for the two-channel decimator that has two interfaces, IF\_NUM = 2. Data from the channel x0 comes to the lower bits of the DIN input (see section 8.3). It is called IF0 DIN, refer to Figure 27. Data from the channel x1 comes to the upper bits of the DIN input named IF1 DIN. For this example, CHAN\_SYNC\_I stays High, as each interface does not utilize time share (CLK\_PER\_SAMPLE = 1). After Latency interval, the core raises DOUT\_VALID and starts outputting the decimated samples: y0(0) is calculated based on the two samples x0(0) and x0(1), y0(1) is based on the samples x0(2) and x0(3), etc. Similarly, the decimated samples of the interface IF1 are calculated. The data from both interfaces appear on the port DOUT. The CHAN\_SYNC\_O signal marks the output samples originated at the interface IF0. The CHAN\_OUT signal indicates the channel that is currently being present at the DOUT port.

Figure 27 Decimation CIC Timing - Two Interfaces, Data Permanently Valid

Figure 28 shows a six-channel CIC decimator timing diagram. The decimator has two interfaces IF\_NUM = 2, with each interface processing three multiplexed channels at CLK\_PER\_SAMPLE = 3. CHAN\_SYNC\_I provides advance warning the first channel for each interface is about to come. The CHAN\_SYNC\_I signal coincides with the last time share channel, that is the channel x2 on the interface IF0 and the channel x5 of the interface IF1. Since the example implements the maximum number of interfaces IF\_NUM = 2 allowed at R\_RATE = 2, the comb section of the filter is busy all the time and the valid decimated samples are generated without breaks. This is signified by the DOUT\_VALID High permanently after initial Latency.

Figure 28 6-Channel Decimator Timing - Two Interfaces Three Time Share Channels Each, Data Always Valid

There is a subtle difference in processing parallel streams of data coming to multiple CIC interfaces. Figure 29 shows an example of a CIC decimator with IF\_NUM=2, R\_RATE=3, and CLK\_PER\_SAMPLE=1. The processing of the DIN\_IF1 data is shifted by one sample with regard to the input data of the DIN\_IF0.