Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **Features**

- μ-law and A-law ITU G.711 Companding Codec

- Operates on +3.3V Power

- Differential Analog Signal Paths

- Programmable Transmit and Receive Gain, +/-12dB in 0.1dB increments

- Transmit Path 60Hz Rejection Filter

- Differential amplifier drives +3.2dBm into  $600\Omega$

- Stable Gain over temperature

- PCM and IOM-2 GCI telecommunication interfaces

- Short and Long Frame Syncs Supported

- Independent Transmit and Receive Programmable Time Slots

- Accepts PCLK from 512kHz to 8.192MHz

- SPI Serial Interface for control in PCM Mode

- Programmable Power Down Mode,  $I_{DD} = 20\mu A$

- Analog and Digital Loopback Modes for testing

# **Description**

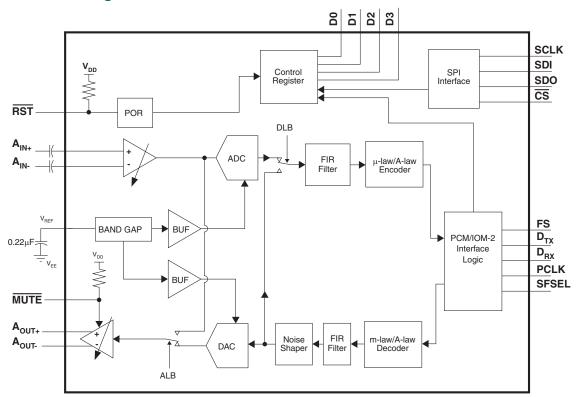

The CPC5750 is a voice-band CODEC with pin-selectable PCM or IOM-2 (GCI) digital interfaces. Clock frequencies for the PCM Mode range from 512kHz to 8.192MHz while the GCI interface allows clocking at 2.048MHz and 4.096MHz. While the GCI interface utilizes the integrated data link to read and write the control registers, a four-wire Serial Peripheral Interface (SPI) bus provides register access while in PCM Mode.

The CODEC provides the necessary A/D and D/A functions with pin-selectable  $\mu$ -law or A-law companding. A low-noise internal reference is used to keep signal gains well controlled over supply and temperature variations. Programmable gain of  $\pm 12 dB$  for both transmit and receive allow the CPC5750 to accept differential input signals as large as +8dBm, and to source +3.2dBm differential signals into  $600\Omega$  while operating from a single 3.3V supply.

# **Ordering Information**

| Part       | Description               |

|------------|---------------------------|

| CPC5750U   | SSOP-24 Package 50/Tube   |

| CPC5750UTR | SSOP-24 Package 2000/Reel |

# **CPC5750 Block Diagram**

|    | IKELIMINAKI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                      |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1. | Specifications  1.1 Pinout  1.2 Pin Descriptions  1.3 Absolute Maximum Ratings  1.4 Recommended Operating Conditions  1.5 Specifications: General Conditions  1.6 Analog Interface Characteristics  1.7 Digital Interface Characteristics  1.8 Transmit Path: Analog Inputs (A <sub>IN+</sub> and A <sub>IN-</sub> ) to Digital Output (D <sub>TX</sub> ) - AC Characteristics  1.9 Receive Path: Digital Input (D <sub>RX</sub> ) to Analog Outputs (A <sub>OUT+</sub> and A <sub>OUT-</sub> ) - AC Characteristics | . 3                                                  |

|    | 1.10 Power Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | . 9                                                  |

| 2. | Control Registers  2.1 Mode Control Register  2.2 TX Path Gain: ±1dB Steps Register  2.3 TX Path Gain: ±0.1dB Steps Register  2.4 RX Path Gain: ±1dB Steps Register  2.5 RX Path Gain: ±0.1dB Steps Register  2.6 PCM Interface D <sub>RX</sub> Time Slot Assignment Register.  2.7 PCM Interface D <sub>RX</sub> Bit Delay Register  2.8 PCM Interface D <sub>TX</sub> Time Slot Assignment Register.  2.9 PCM Interface D <sub>TX</sub> Bit Delay Register  2.10 Reserved Register  2.11 GPIO Control Register     | 111<br>122<br>133<br>133<br>134<br>144<br>144<br>144 |

| 3. | Digital Transmission Modes: PCM or IOM-2 GCI                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 15<br>15                                             |

| 4. | Functional Description - To Do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17                                                   |

| 5. | PCM Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 18                                                   |

| 6. | IOM-2 (GCI) Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                      |

| 7. | 4-Wire SPI (Serial Peripheral Interface)                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 35                                                   |

| 8. | Manufacturing Information  8.1 Moisture Sensitivity.  8.2 ESD Sensitivity.  8.3 Reflow Profile.                                                                                                                                                                                                                                                                                                                                                                                                                      | 36<br>36                                             |

# 1. Specifications

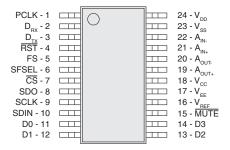

# 1.1 Pinout

# 1.2 Pin Descriptions

| Pin Name           | Pin #   | Pin Type                                            | Description                                                                                                                                                                                                                      |

|--------------------|---------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power an           | d Gro   | und                                                 |                                                                                                                                                                                                                                  |

| $V_{DD}$           | 24      | Power In                                            | Digital Supply Voltage                                                                                                                                                                                                           |

| $V_{SS}$           | 23      | Power In                                            | Digital Ground                                                                                                                                                                                                                   |

| $V_{CC}$           | 18      | Power In                                            | Analog Supply Voltage                                                                                                                                                                                                            |

| $V_{EE}$           | 17      | Power In                                            | Analog Ground                                                                                                                                                                                                                    |

| $V_{REF}$          | 16      | Power Out                                           | Analog Reference Voltage - C <sub>REF</sub> = 0.22μF (From V <sub>REF</sub> to V <sub>EE</sub> )                                                                                                                                 |

| Control I          | nterfa  | ce                                                  |                                                                                                                                                                                                                                  |

| RST                | 4       | Digital Input - PU                                  | Active low digital input with internal pull-up (PU). When asserted low, all logic is asynchronously reset.                                                                                                                       |

| CS                 | 7       | Digital Input<br>(Dual Purpose)                     | 1) Companding selection during Power-Up or RST. Hold for 40μs after Power-Up or RST: CS = low, Companding = μ-law; CS = high, Companding = A-law. Can be modified via programming. 2) PCM Mode: SPI bus Chip Select, active low. |

| D0                 | 11      | Digital Input/Output                                | General purpose input/output pin.                                                                                                                                                                                                |

| D1                 | 12      | Digital Input/Output                                | General purpose input/output pin.                                                                                                                                                                                                |

| D2                 | 13      | Digital Input/Output                                | General purpose input/output pin.                                                                                                                                                                                                |

| D3                 | 14      | Digital Input/Output                                | General purpose input/output pin.                                                                                                                                                                                                |

| MUTE               | 15      | Digital Input - PU                                  | Active low digital input with internal pull-up. When asserted low, the analog output amplifier is disabled and it's outputs $A_{OUT-}$ and $A_{OUT-}$ are held at a nominal ½ $V_{CC-}$                                          |

| SCLK               | 9       | Digital Input<br>(Dual Purpose)                     | PCM Mode: SPI bus clock.     GCI Mode: Input, MSB address bit to select sub-frame.                                                                                                                                               |

| SDI                | 10      | Digital Input<br>(Dual Purpose)                     | 1) Transmission Mode select during Power-Up or Reset. Hold for 40µs after Power-Up or RST: SDI = low, Mode = IOM-2 GCI; SDI = high, Mode = PCM. 2) PCM Mode: SPI bus data input. Connects to the SPI bus master SDO output.      |

| SDO                | 8       | Digital Input/Output<br>Tri-State<br>(Dual Purpose) | PCM Mode: SPI bus data output. Connects to the SPI bus master SDI input.     GCI Mode: Input, address bit to select sub-frame used.                                                                                              |

| SFSEL              | 6       | Digital Input                                       | GCI Mode: Input LSB address bit to select sub-frame. PCM Mode: Not used.                                                                                                                                                         |

| PCM/IOM            | -2 Dig  | itized Voice Interf                                 | ace                                                                                                                                                                                                                              |

| $D_{RX}$           | 2       | Digital Input                                       | Receive data for PCM Interface or GCI bus.                                                                                                                                                                                       |

| $D_{TX}$           | 3       | Digital Output Tri-State                            | Transmit data for PCM Interface or GCI bus.                                                                                                                                                                                      |

| FS                 | 5       | Digital Input                                       | Frame synchronization signal for GCI or PCM Interface bus.                                                                                                                                                                       |

| PCLK               | 1       | Digital Input                                       | Master clock signal for GCI or PCM Interface bus as well as signal processing.                                                                                                                                                   |

| Analog Ir          | nterfac | ce                                                  |                                                                                                                                                                                                                                  |

| A <sub>IN+</sub>   | 21      | Analog Input                                        | Differential amplifier Non-inverting input.                                                                                                                                                                                      |

| A <sub>IN</sub> -  | 22      | Analog Input                                        | Differential amplifier Inverting input.                                                                                                                                                                                          |

| A <sub>OUT+</sub>  | 19      | Analog Output                                       | Positive amplifier output, differential $600\Omega$ driver.                                                                                                                                                                      |

| A <sub>OUT</sub> - | 20      | Analog Output                                       | Negative amplifier output, differential $600\Omega$ driver.                                                                                                                                                                      |

#### 1.3 Absolute Maximum Ratings

Unless otherwise noted, Absolute Maximum Ratings are provided over the operational temperature range and all voltages are referenced to  $V_{EE} = V_{SS} = 0V$ .

| Parameter               | Symbol           | Min   | Max                   | Units |

|-------------------------|------------------|-------|-----------------------|-------|

| DC Supply Voltages      |                  |       |                       |       |

| Analog Supply           | $V_{CC}$         | - 0.4 | 3.7                   | V     |

| Digital Supply          | V <sub>DD</sub>  | - 0.4 | 3.7                   | v     |

| Input Voltage           |                  |       |                       |       |

| Analog Pins             | V <sub>IN</sub>  |       | V <sub>CC</sub> + 0.4 | V     |

| Digital Pins            | V IN             | - 0.4 | V <sub>DD</sub> + 0.4 | v     |

| Output Current          |                  |       |                       |       |

| Analog Pins             | Io               |       | ±10                   | mA    |

| Digital Pins            | 10               |       | ±10                   | ША    |

| Operational Temperature | T <sub>A</sub>   | - 40  | +85                   | °C    |

| Storage Temperature     | T <sub>STG</sub> | - 40  | +150                  | °C    |

Absolute maximum ratings are stress ratings. Stresses in excess of these ratings can cause permanent damage to the device. Functional operation of the device at conditions beyond those indicated in the operational sections of this data sheet is not implied. Exposure to absolute-maximum rated conditions for extended periods of time may affect device reliability.

#### 1.4 Recommended Operating Conditions

| Parameter           | Symbol          | Min  | Typical         | Max             | Units |

|---------------------|-----------------|------|-----------------|-----------------|-------|

| DC Supply Voltages  |                 |      |                 |                 |       |

| Analog Supply       | V <sub>CC</sub> | 3.0  | 3.3             | 3.6             | ٧     |

| Digital Supply      | $V_{DD}$        | 3.0  | 3.3             | 3.0             | V     |

| Input Voltage       |                 |      |                 |                 |       |

| Analog Pins         | V <sub>IN</sub> | 0    | V <sub>CC</sub> |                 | V     |

| Digital Pins        | V IN            | 0    |                 | V <sub>DD</sub> | v     |

| Ambient Temperature | T <sub>A</sub>  | - 40 |                 | +85             | °C    |

#### 1.5 Specifications: General Conditions

Unless otherwise specified:

The characteristics provided in the following tables cover the Operating Ambient Temperature Range -40°C to +85°C;  $V_{CC} = V_{DD} = 3.0V$  to 3.6V,  $V_{EE} = V_{SS} = 0V$ .

Additionally, transmission characteristics cover the programmable gain settings; analog input and output specifications are differential; the test signal and reference signal is 0dBm0 at 1020Hz; and the companding is set to  $\mu$ -law. Signal power given in dBm is referenced to 600 ohms.

NOTE: Characteristics over the transmission gain settings are bounded by the limitations of the companding and the analog amplifier's input and output capabilities.

Typical values are for 25°C with nominal supplies and are provided for reference purposes only.

# 1.6 Analog Interface Characteristics

| Parameter                                                      | Conditions                                | Symbol              | Minimum | Typical           | Maximum | Units           |

|----------------------------------------------------------------|-------------------------------------------|---------------------|---------|-------------------|---------|-----------------|

| Inputs                                                         |                                           |                     |         |                   |         |                 |

| Input Offset Voltage: A <sub>IN+</sub> and A <sub>IN-</sub>    | PD = 0                                    | V                   |         | ½ V <sub>CC</sub> |         | .,              |

|                                                                | PD = 1                                    | V <sub>IN</sub>     |         | 0                 |         | V               |

| Input Impedance                                                |                                           |                     |         |                   |         |                 |

| Differential                                                   | -                                         | R <sub>AIN+/-</sub> | 160     | 200               | 240     | kΩ              |

| Input to Ground (V <sub>EE</sub> )                             | -                                         | R <sub>AIN</sub>    | -       | 100               | -       | kΩ              |

| Maximum Differential Input Signal                              | Referenced to 600Ω                        | -                   | -       | -                 | +8      | dBm             |

| Differential Common Mode Rejection Ratio                       | Relative to -26dBm0, 0 to 3.6kHz          | -                   | 60      | -                 | -       | dB              |

| Differential Power Supply Rejection Ratio <sup>1</sup>         | R <sub>AIN+/-</sub> = Open<br>0 to 3.6kHz | -                   | 60      |                   |         | dB              |

| Outputs                                                        |                                           |                     |         |                   |         |                 |

| Output Offset Voltage: A <sub>OUT+</sub> and A <sub>OUT-</sub> | $PD = 0$ , $\overline{MUTE} = x$          |                     |         | ½ V <sub>CC</sub> |         |                 |

| 5 6611 661                                                     | PD = 1                                    | $V_{OUT}$           |         | 0                 |         | V               |

| Output drive                                                   | $R_L = 500\Omega$                         |                     | 3.2     |                   |         | mA <sub>p</sub> |

| Maximum Output Signal                                          | Referenced to 600Ω                        | -                   | -       | -                 | 3.2     | dBm             |

| Differential Load Impedance                                    | -                                         | -                   | 500     | 600               | -       | Ω               |

| Load Capacitance                                               |                                           |                     |         |                   |         |                 |

| Differential                                                   | -                                         | C <sub>LD</sub>     | -       | -                 | 250     | pF              |

| To GND                                                         | -                                         | C <sub>L</sub>      | -       | -                 | 50      | pF              |

| Differential Power Supply Rejection Ratio <sup>1</sup>         | 0 to 3.6kHz                               | -                   | 60      | -                 | -       | dB              |

<sup>&</sup>lt;sup>1</sup> Not tested, guaranteed by design. Power supply rejection is evaluated for sample parts.

# 1.7 Digital Interface Characteristics

| Parameter                                                                                                  | Conditions                    | Symbol          | Minimum              | Typical               | Maximum | Units |

|------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|----------------------|-----------------------|---------|-------|

| Inputs: All logic inputs and all GPIO provision                                                            | oned as inputs a              | re Schmi        | tt trigger i         | nputs.                |         |       |

| Input Voltage                                                                                              |                               |                 |                      |                       |         |       |

| Logic 1 Threshold                                                                                          | -                             | V <sub>IH</sub> | -                    | 1.65                  | 2       |       |

| Logic 0 Threshold                                                                                          | -                             | $V_{IL}$        | 0.8                  | 1.1                   | -       | V     |

| Hysteresis                                                                                                 | -                             | $V_{HYS}$       | 0.3                  | 0.55                  | 0.7     |       |

| Input Leakage (Inputs without Pull-Up Resistors and $\mathrm{D}_{\mathrm{X}}$ when provisioned as inputs.) | $V_{IN} = V_{SS}$ to $V_{DD}$ | I <sub>IN</sub> |                      |                       | ± 10    | μА    |

| Pull-Up Resistors: Pins RST & MUTE                                                                         |                               | R <sub>PU</sub> | 24                   | 33                    | 42      | kΩ    |

| Outputs                                                                                                    |                               |                 |                      |                       |         |       |

| Output Voltage                                                                                             |                               |                 |                      |                       |         |       |

| Logic 1                                                                                                    | I <sub>OH</sub> = -4mA        | $V_{OH}$        | V <sub>DD</sub> -0.3 | V <sub>DD</sub> -0.17 | -       |       |

| Logic 0                                                                                                    | I <sub>OL</sub> = 4mA         | $V_{OL}$        | -                    | 0.12                  | 0.3     | V     |

| Leakage: 3-State Off (Hi-Z)                                                                                | $V_{OZ} = V_{SS}$ to $V_{DD}$ | I <sub>OZ</sub> |                      |                       | ± 10    | μА    |

|                                                                                                            | 02 33 - 00                    | -02             |                      |                       |         |       |

# 1.8 Transmit Path: Analog Inputs (A $_{\rm IN+}$ and A $_{\rm IN-}$ ) to Digital Output (D $_{\rm TX}$ ) - AC Characteristics

| Parameter                                        | Conditions              | Symbol | Minimum  | Typical | Maximum | Units  |

|--------------------------------------------------|-------------------------|--------|----------|---------|---------|--------|

| Gain                                             |                         |        |          |         |         |        |

| Absolute                                         | 0 dBm0, 1020 Hz         |        | -0.3     | -       | 0.3     | dB     |

| Variation with Frequency (Frequency Response)    | Relative to 0 dBm0, 102 | 20 Hz  |          |         |         | ,      |

| variation with requestoy (requestoy resoperate)  | ≤ 60 Hz                 |        | -        | -       | - 29    |        |

|                                                  | < 200 Hz                |        | -        | -       | 0       |        |

|                                                  | 200 Hz to 300 Hz        |        | -        |         | 0.25    |        |

|                                                  | 300 Hz to 3000 Hz       |        | -0.25    | -       | 0.25    | -      |

|                                                  | 3000 Hz to 3400 Hz      |        | - 0.9    | -       | 0.25    | dB     |

|                                                  | 3400 Hz to 3600 Hz      |        | -        | -       | 0.25    |        |

|                                                  | 3600 Hz to 4600 Hz      |        | -        | -       | 0       |        |

|                                                  | > 4.6kHz                |        | -        | -       | - 25    | -      |

| Variation with Signal Level (Amplitude Tracking) | Relative to 0 dBm0, 102 | 20Hz   |          |         |         |        |

| Tananan man enginar 2010. (hampinado masianig)   | +3 dBm0 to -40 dBm0     |        |          |         |         |        |

|                                                  | -40 dBm0 to -50 dBm0    |        |          |         |         | dB     |

|                                                  | -50 dBm0 to -55 dBm0    |        |          |         |         |        |

| Idle Channel Noise                               |                         |        |          |         |         |        |

| C Message Weighted, μ-law                        |                         |        | -        | -       | 12      | dBrnC0 |

| P Message Weighted, A-law                        | Transmit Gain = 0dB     |        | -        | -       | 12      | dBm0p  |

| Signal to Total Distortion                       | 3.2 dBm0                |        | 00       |         |         |        |

| Signal to lotal distortion                       | 0dBm0 to -30dBm0        |        | 30       | -       | -       | -ID    |

|                                                  | - 40 dBm0               | -      | 36<br>30 | -       | -       | dB     |

|                                                  | - 45 dBm0               |        | 25       | -       | -       |        |

|                                                  |                         |        | 23       | -       | -       |        |

| Single Frequency Distortion:                     | Any frequency 300 Hz    |        |          |         | -46     | dB     |

| Receive any single frequency distortion product. | to 3400 Hz              |        |          |         | 10      | QD.    |

| Intermodulation Distortion                       | 300 Hz to 3400 Hz,      |        |          |         | 44      | dB     |

|                                                  | any two frequencies.    |        |          |         | -41     | UD     |

| Envelope Delay Distortion                        |                         |        |          |         |         |        |

| Absolute                                         | 1600 Hz                 |        |          |         | 315     | μS     |

| Variation with Frequency                         | Relative to 1600 Hz     |        |          |         |         |        |

| ' '                                              | 500 Hz to 600 Hz        |        |          |         | 210     |        |

|                                                  | 600 Hz to 800 Hz        |        |          |         | 130     | -      |

|                                                  | 800 Hz to 1000 Hz       |        |          |         | 70      |        |

|                                                  | 1000 Hz to 1600 Hz      |        |          |         | 35      | μS     |

|                                                  | 1600 Hz to 2600 Hz      |        |          |         | 70      |        |

|                                                  | 2600 Hz to 2800 Hz      |        |          |         | 95      |        |

|                                                  | 2800 Hz to 3000 Hz      |        |          |         | 145     |        |

| Crosstalk - Receive Path to Transmit Path        | 0dBm0,                  |        |          |         |         |        |

| - Cookan Troops Fall to Hallottic Fall           | 300 Hz to 3400 Hz,      |        |          |         | -75     | dB     |

|                                                  | ,                       |        |          |         |         |        |

# 1.9 Receive Path: Digital Input ( $D_{RX}$ ) to Analog Outputs ( $A_{OUT+}$ and $A_{OUT-}$ ) - AC Characteristics

| Conditions                     | Symbol                  | Minimum                    | Typical                    | Maximum                    | Units                      |

|--------------------------------|-------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

|                                |                         |                            |                            |                            |                            |

| 0 dBm0 @1020Hz                 |                         | -0.3                       | -                          | 0.3                        | dB                         |

|                                | 2011                    | 0.0                        |                            | 0.0                        |                            |

|                                | 20HZ                    |                            |                            |                            |                            |

|                                | -                       | -                          | -                          | _                          |                            |

|                                |                         | -                          | -                          |                            |                            |

|                                |                         |                            | -                          |                            |                            |

|                                |                         | - 0.9                      | -                          |                            |                            |

|                                |                         | -                          | •                          |                            | dB                         |

|                                |                         | -                          | •                          | _                          | _                          |

| > 4.0KПZ                       |                         | -                          | -                          | - 25                       |                            |

| Relative to 0 dBm0, 102        | 20Hz                    |                            |                            |                            |                            |

| +3 dBm0 to -40 dBm0            |                         |                            |                            |                            |                            |

|                                |                         |                            |                            |                            | dB                         |

| -50 dBm0 to -55 dBm0           |                         |                            |                            |                            |                            |

| Transmit Gain = 0dB            |                         | <u>"</u>                   |                            |                            |                            |

|                                |                         |                            |                            |                            |                            |

|                                |                         | _                          | -                          | 12                         | dBrnC0                     |

| codes                          |                         |                            |                            |                            |                            |

| Positive zero PCM              |                         |                            |                            |                            | ID 0                       |

| code                           |                         | -                          | -                          |                            | dBm0p                      |

| 3.2 dRm0                       |                         | 20                         |                            |                            |                            |

|                                |                         |                            |                            | _                          | dB                         |

|                                | -                       |                            |                            | _                          | ub ub                      |

|                                |                         |                            |                            | _                          |                            |

|                                |                         | 25                         |                            |                            |                            |

|                                |                         |                            |                            | -46                        | dB                         |

| to 3400 Hz                     |                         |                            |                            |                            |                            |

| 300 Hz to 3400 Hz,             |                         |                            |                            | 44                         | ٩D                         |

| any two frequencies.           |                         |                            |                            | -41                        | dB                         |

|                                |                         |                            |                            |                            |                            |

| 1600 Hz                        |                         |                            |                            | 200                        | μS                         |

|                                |                         |                            |                            | 200                        | μο                         |

|                                |                         | -40                        |                            |                            |                            |

|                                |                         |                            |                            |                            |                            |

|                                |                         | 00                         |                            | 90                         | μS                         |

|                                |                         |                            |                            |                            |                            |

| 2800 Hz to 3000 Hz             |                         |                            |                            |                            |                            |

|                                | \                       |                            |                            | 1                          | 1                          |

|                                | HZ                      |                            |                            |                            | i.e.                       |

|                                |                         |                            |                            |                            | dB                         |

|                                |                         |                            |                            |                            |                            |

|                                |                         |                            |                            |                            |                            |

| -                              |                         |                            |                            |                            |                            |

| 1                              |                         |                            |                            | 75                         | dB                         |

| PCM D <sub>RX</sub> = Positive |                         |                            |                            | -/5                        | UD                         |

| zero code                      |                         |                            |                            |                            |                            |

|                                |                         |                            |                            |                            | •                          |

|                                | Relative to 0 dBm0, 102 | Relative to 0 dBm0, 1020Hz |

| Parameter              | Conditions                                                       | Symbol           | Minimum | Typical | Maximum | Units |

|------------------------|------------------------------------------------------------------|------------------|---------|---------|---------|-------|

| Noise Single Frequency | Tie $D_{TX}$ to $D_{RX}$ , 0 Hz to 100kHz, $V_{IN} = 1V_{rms}$ , | V <sub>OUT</sub> |         |         | -53     | dB    |

# 1.10 Power Characteristics

$I_{DC} = I_{CC} + I_{DD}$

| Parameter                                                 | Conditions                 | Symbol           | Minimum | Typical | Maximum | Units |

|-----------------------------------------------------------|----------------------------|------------------|---------|---------|---------|-------|

| Power-On Reset                                            |                            |                  |         |         |         |       |

| Power-On Reset Voltage (Voltage at Which Reset is Active) | V <sub>DD</sub> Rising     | V <sub>POR</sub> | -       | 1.3     | 2       | ٧     |

| Reference Voltage                                         |                            | $V_{REF}$        |         |         |         | V     |

| Power Supply Current                                      |                            |                  |         |         |         |       |

| Total Supply Current, Device Shut Down                    | PD = 1                     | I <sub>DC</sub>  | -       | 1       | 20      | μА    |

| Total Supply Current, Device Active                       | PD = 0, No AC transmission | I <sub>DC</sub>  | -       | 7.5     |         | mA    |

# 1.11 Power-On Reset

| Parameter             | Conditions | Symbol           | Minimum | Typical | Maximum | Units |

|-----------------------|------------|------------------|---------|---------|---------|-------|

| Power-On Reset Period | -          | T <sub>POR</sub> | -       | 20      | 40      |       |

| De-Bounce Time        | -          | T <sub>RST</sub> | -       | 20      | -       | μ\$   |

NOTE: With  $V_{DD}$  rising,  $V_{IH} = V_{DD}$  for  $V_{DD} < V_{POR\_MAX}$ .

# 2. Control Registers

The control registers are used to set up operating characteristics, transmit/receive gains, PCM time slot assignments and GPIO control. Access to these registers is dependent on the transmission mode set by the logical state of SDI (pin 10) during a Reset or Power-Up event. With SDI held at a logic high, the device is configured for PCM Mode and register access is only available via the SPI bus. When SDI is held at a logic low, the device is configured for IOM-2 GCI Mode and register access is only available through the GCI data link.

NOTE: PCLK and FS must be active before a write command is issued to the control registers, otherwise the written values will not be retained.

Power Up and Reset events set the device's Power Down bit (PD) to a logic high which disables the input and output analog amplifiers and if configured for PCM Mode, disables the upstream digital signal and places the  $D_{TX}$  output into a high impedance state. After provisioning the control registers and if necessary, assigning the PCM interface to the proper time slot, PD can be set low to begin operation. The GCI Mode does not allow changing the time slot of the digitized voice data.

The table below shows the CPC5750 control register names, the bit names, and the register address. Access to the registers is only available via read or write commands. The structure of a register command consists of two parts; first is the command type nibble which is followed immediately by the register address nibble. Write commands will be followed by the data word to be stored in the addressed register. The first four bits (nibble) of a read command are 1010 (0xA) while the write command's first four bits (nibble) are 1011 (0xB). Following the command type nibble is the register address nibble as provided in the table below. As an example, the command to read back the value provisioned into the PCM Transmit Time Slot register is: 0xA7. Detailed discussions of each register are provided in the following sections.

**Table 1: Control Registers**

| Register Name                 | (MSB)      |          |        | В      | its   |       |      | (LSB) | Add | ress |

|-------------------------------|------------|----------|--------|--------|-------|-------|------|-------|-----|------|

|                               | 7          | 6        | 5      | 4      | 3     | 2     | 1    | 0     | Dec | Hex  |

| Mode Control                  | Companding | Not Used | ALB    | DLB    | PD    | CPB   | TXZ  | TM    | 0   | 0x0  |

| TX Gain: ±1dB Steps           | Not Used   |          |        | [4:0]  |       |       |      |       | 1   | 0x1  |

| TX Gain: ±0.1dB Steps         | Not Used   |          |        |        | [3:0] |       |      |       | 2   | 0x2  |

| RX Gain: ±1dB Steps           | Not Used   |          |        | [4:0]  |       |       |      |       | 3   | 0x3  |

| RX Gain: ±0.1dB Steps         | Not Used   |          |        |        | [3:0] |       |      |       | 4   | 0x4  |

| PCM D <sub>RX</sub> Time Slot | Not Used   | [6:0]    |        |        |       |       |      |       | 5   | 0x5  |

| PCM D <sub>RX</sub> Bit Delay | Not Used   |          |        |        |       | [2:0] |      |       | 6   | 0x6  |

| PCM D <sub>TX</sub> Time Slot | Not Used   | [6:0]    |        |        |       |       |      |       | 7   | 0x7  |

| PCM D <sub>TX</sub> Bit Delay | Not Used   |          |        |        |       | [2:0] |      |       | 8   | 0x8  |

| Reserved                      | 0          | 0        | 0      | 0      | 0     | 0     | 0    | 0     | 9   | 0x9  |

| GPIO Control                  | DIR(3)     | DIR(2)   | DIR(1) | DIR(0) | D(3)  | D(2)  | D(1) | D(0)  | 10  | 0xA  |

NOTE: All registers are Read / Write and all user defined bits are Read / Write.

CPC5750

**PRELIMINARY**

#### 2.1 Mode Control Register

This register allows the programmable control of the Companding, analog and digital loop backs for debug testing, Power Down mode, and custom control of the PCM interface.

| Register     | 7                   | 6        | 5   | 4   | 3  | 2   | 1   | 0  | Address |

|--------------|---------------------|----------|-----|-----|----|-----|-----|----|---------|

| Mode Control | Companding          | Not Used | ALB | DLB | PD | CPB | TXZ | TM | 0x0     |

| Default      | (CS Level at Reset) | 0        | 0   | 0   | 1  | 0   | 0   | 0  | -       |

#### 2.1.1 Companding (bit 7)

This bit determines the data compression method to be used. The value of this bit during Power Up or Reset is determined by the level on  $\overline{CS}$  (pin 7) when the chip reset goes inactive. During either of these events the logical level on  $\overline{CS}$  must be maintained for a minimum duration of  $40\mu s$ . For Power Up, the hold time begins with a valid  $V_{DD}$  level and a logic high at  $\overline{RST}$  (pin 4). For an external reset ( $\overline{RST}=0$ ) the hold time begins with a logic high at  $\overline{RST}$ . Once active, this bit can be modified using the SPI interface (PCM Mode) or the GCI link (IOM-2 GCI Mode). The bit values to set the compression method are:

Logic '0': μ-law Logic '1': A-law

#### 2.1.2 ALB (bit 5)

The Analog Loop Back (ALB) bit is used to test the analog interface of the CPC5750 by connecting the output of the analog input amplifier to the input of the analog output amplifier. To prevent received digital information from interfering with the test, the connection between the DAC and the input of the analog output amplifier is opened. This provides an all-analog test path from the  $A_{IN+}$  and  $A_{IN-}$  inputs to the  $A_{OUT+}$  and  $A_{OUT-}$  outputs. Additionally the analog to digital transmit path remains intact, allowing the means to monitor the analog input gain. The bit values to activate and de-activate the Analog Loop Back are:

Logic '0': Normal Operation (Analog Loop Back disabled)

Logic '1': Analog Loop Back Mode

# 2.1.3 DLB (bit 4)

The Digital Loop Back (DLB) bit is used to test the digital interfaces, (PCM or GCI) and the DSP sections of the CPC5750 by separating the transmit path analog input section and ADC from the transmit DSP section and connecting the digital output of the receive path DSP to the digital input of the transmit path DSP. This provides an all-digital test path through the receive path's DAC filters and Noise Shaper and back out through ADC digital filters. The DLB configuration retains the connection between the receive path's digital and analog sections providing the means to monitor the converted receive digital signal at the A<sub>OUT+</sub> and A<sub>OUT-</sub> analog outputs. The bit values to control the Digital Loop Back function are:

Logic '0': Normal Operation (Digital Loop Back disabled)

Logic '1': Digital Loop Back Mode

#### 2.1.4 PD (bit 3)

The Power-Down (PD) bit is used to put the CPC5750 in a standby mode where it draws very little current.

Logic '0': Normal Operation

Logic '1': Device is Powered Down. The SPI bus interface (PCM Mode) and GCI link (GCI Mode) are still functional to allow enabling the part. The GCI interface will draw current if clocked externally. In PCM Mode, D<sub>TX</sub> is set to high impedance (Hi-Z).

#### 2.1.5 CPB (bit 2)

The Clocks Per Bit (CPB) selection bit is used to set the number of PCM clock cycles per bit of transmit and receive data transfer at either 1 clock-per-bit or 2 clocks-per-bit. This programmable option is only used in PCM Mode as the clock rate is auto-detected in GCI Mode.

Logic '0': 1 Clock cycle Per data Bit Logic '1': 2 Clock cycles Per data Bit

#### 2.1.6 TXZ (bit 1)

The PCM data Tri-state (TXZ) selection bit is used to set when the PCM transmit output driver,  $D_{TX}$ , goes high impedance.

Logic '0': Tri-State on the first PCLK Rising Edge following the LSB of the time slot.

Logic '1': Tri-State on the PCLK Falling Edge during the LSB of the time slot. (The second falling edge of PCLK when CPB = 1.)

#### 2.1.7 TM (bit 0)

Reserved: This bit is not user defined and it's value should not be modified. The default power up and reset value of this bit is 0 and must not be changed.

# 2.2 TX Path Gain: ±1dB Steps Register

Flve bits of this register determine the analog input amplifier gain in 1 dB steps as shown in the following table.

| Register                 | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      | Address |

|--------------------------|---|---|---|--------|--------|--------|--------|--------|---------|

| TX Path Gain: ±1dB Steps | - | - | - | TXG(4) | TXG(3) | TXG(2) | TXG(1) | TXG(0) | 0x1     |

| Default Value            | 0 | 0 | 0 | 0      | 0      | 0      | 0      | 0      | -       |

#### 2.2.1 TXG (bits [4:0])

TXG is a 5-bit, 2's complement number between -12 and 12. This value sets the transmit path gain in 1 dB increments. Values of TXG larger than +12 set a gain of +12dB. Values of TXG less than -12 set a gain of -12dB.

#### 2.3 TX Path Gain: +0.1dB Steps Register

Four bits of this register determine the analog input amplifier gain in 0.1 dB steps as shown in the following table.

| Register                   | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      | Address |

|----------------------------|---|---|---|---|--------|--------|--------|--------|---------|

| TX Path Gain: +0.1dB Steps | - | - | - | - | TXB(3) | TXB(2) | TXB(1) | TXB(0) | 0x2     |

| Default Value              | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      | -       |

#### 2.3.1 TXB (bits [3:0])

TXB is a 4-bit number between 0 and +9. This value increases the transmit path gain in 0.1dB increments. These bits are used in conjunction with the TXG bits to define a 9-bit gain value from -12dB to +12.9dB in 0.1dB steps. For example, to set the transmit gain to -0.1dB, the TXG bits are set for -1dB (11111) and the TXB bits are set for +0.9dB (1001). The nine bit value 111111001(binary) provides for a transmit gain = -1dB + 0.9dB = -0.1dB; EX2: 111110000 = -1dB; EX3: 001110011 = +7.3dB. Values of TXB are always positive and values greater than 9 continue to define the gain as +0.9dB.

ECPATED CIPCUITS DIVISION CPC5750

**PRELIMINARY**

#### 2.4 RX Path Gain: ±1dB Steps Register

Flve bits of this register determine the analog output amplifier gain in 1 dB steps as shown in the following table.

| Register                 | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      | Address |

|--------------------------|---|---|---|--------|--------|--------|--------|--------|---------|

| RX Path Gain: ±1dB Steps | - | - | - | RXG(4) | RXG(3) | RXG(2) | RXG(1) | RXG(0) | 0x3     |

| Default Value            | 0 | 0 | 0 | 0      | 0      | 0      | 0      | 0      | -       |

#### 2.4.1 RXG (bits [4:0])

RXG is a 5-bit, 2's complement number between -12 and 12. This value sets the receive path gain in 1dB increments. Values of RXG larger than +12 set a gain of +12dB. Values of RXG less than -12 set a gain of -12dB.

#### 2.5 RX Path Gain: +0.1dB Steps Register

Four bits of this register determine the analog output amplifier gain 0.1 dB steps as shown in the following table.

| Register                   | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      | Address |

|----------------------------|---|---|---|---|--------|--------|--------|--------|---------|

| RX Path Gain: +0.1dB Steps | - | - | - | - | RXB(3) | RXB(2) | RXB(1) | RXB(0) | 0x4     |

| Default Value              | 0 | 0 | 0 | 0 | 0      | 0      | 0      | 0      | -       |

#### 2.5.1 RXB (bits [3:0])

RXB is a 4-bit number between 0 and +9. This value increases the receive path gain in 0.1 dB increments. These bits are used in conjunction with the RXG bits to define a 9-bit gain value from -12 to +12.9dB in 0.1 steps. For example, to set the receive gain to -3.1dB, the RXG bits are set for -4dB (11100) and the RXB bits are set for +0.9dB (1001). The nine bit value 111001001(binary) provides for a receive gain = -4dB + 0.9dB = -3.1dB; EX2: 110110011 = -5dB + 0.3dB = -4.7dB; EX3: 010011000 = +9.8dB. Values of RXB are always positive and values greater than 9 continue to define the gain as +0.9dB.

# 2.6 PCM Interface D<sub>RX</sub> Time Slot Assignment Register

The lower seven bits of this register determine which of the available 8-bit time slots the CPC5750 uses to receive data when in the PCM Mode.

| Register                      | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      | Address |

|-------------------------------|---|--------|--------|--------|--------|--------|--------|--------|---------|

| PCM D <sub>RX</sub> Time Slot | - | PRC(6) | PRC(5) | PRC(4) | PRC(3) | PRC(2) | PRC(1) | PRC(0) | 0x5     |

| Default Value                 | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | -       |

#### 2.7 PCM Interface D<sub>RX</sub> Bit Delay Register

The lower three bits of this register delay the receiver from reading the selected time slot by 0 to 7 bits.

| Register                | 7 | 6 | 5 | 4 | 3 | 2      | 1     | 0      | Address |

|-------------------------|---|---|---|---|---|--------|-------|--------|---------|

| PCM D <sub>RX</sub> Bit | - | - | - | - | - | PRB(2) | PRB1) | PRB(0) | 0x6     |

| Default Value           | 0 | 0 | 0 | 0 | 0 | 0      | 0     | 0      | -       |

ECPATED CIPCUITS DIVISION CPC5750

#### 2.8 PCM Interface D<sub>TX</sub> Time Slot Assignment Register

The lower seven bits of this register determine which of the available 8-bit time slots the CPC5750 uses to transmit data when in the PCM Mode.

**PRELIMINARY**

| Register                    | 7 | 6      | 5      | 4      | 3      | 2      | 1      | 0      | Address |

|-----------------------------|---|--------|--------|--------|--------|--------|--------|--------|---------|

| PCM D <sub>TX</sub> Channel | - | PTC(6) | PTC(5) | PTC(4) | PTC(3) | PTC(2) | PTC(1) | PTC(0) | 0x7     |

| Default Value               | 0 | 0      | 0      | 0      | 0      | 0      | 0      | 0      | -       |

# 2.9 PCM Interface D<sub>TX</sub> Bit Delay Register

The lower three bits of this register delay the transmit data in the selected time slot by 0 to 7 bits.

| Register                | 7 | 6 | 5 | 4 | 3 | 2      | 1     | 0      | Address |

|-------------------------|---|---|---|---|---|--------|-------|--------|---------|

| PCM D <sub>TX</sub> Bit | - | - | - | - | - | PTB(2) | PTB1) | PTB(0) | 0x8     |

| Default Value           | 0 | 0 | 0 | 0 | 0 | 0      | 0     | 0      | -       |

#### 2.10 Reserved Register

The Reserved register is not user defined and it's value should not be modified. The default power up and reset value of this register is 0 and must not be changed.

| Register | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Address |

|----------|---|---|---|---|---|---|---|---|---------|

| Reserved | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0x9     |

#### 2.11 GPIO Control Register

The CPC5750 has four General Purpose I/O pins that can be programmed as inputs or outputs and whose values can be examined or controlled by the user. This register allows for control and monitoring of external digital nets using these I/O pins.

| Register      | 7      | 6      | 5      | 4      | 3    | 2    | 1    | 0    | Address |

|---------------|--------|--------|--------|--------|------|------|------|------|---------|

| GPIO Control  | DIR(3) | DIR(2) | DIR(1) | DIR(0) | D(3) | D(2) | D(1) | D(0) | 0xA     |

| Default Value | 0      | 0      | 0      | 0      | 0    | 0    | 0    | 0    | -       |

#### 2.11.1 DIR(x) (bits [3:0])

Setting a DIR(x) bit to 1, configures the corresponding CPC5750 I/O pin as an output. When the DIR(x) bits are cleared, i.e. DIR(x) = 0, the corresponding I/O pin will be configured as an input. Following a Power Up or Reset the CPC5750 configures all four I/O pins as inputs thereby eliminating any possibility of an I/O pin back driving another output.

#### 2.11.2 D(x) (bits [3:0])

When an I/O is configured as an input, then reading the corresponding D(x) bit of this register gives the logical state of that input pin. Writing to the D(x) bits of inputs performs no function while writing to the D(x) bit of an I/O configured as an output determines the state of that output pin. Reading this register returns the current value of the bits. For an I/O pin configured as an output, reading this register returns the last value written to it's D(x) bit.

CPC5750

**PRELIMINARY**

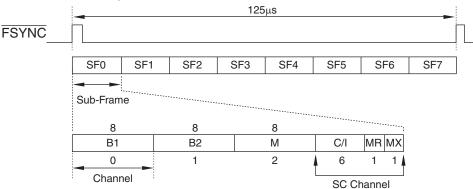

# 3. Digital Transmission Modes: PCM or IOM-2 GCI

The CPC5750 was designed to be used in communication systems utilizing either the traditional PCM bus method of digital transmission flow or the newer IOM-2 GCI bus. Both operational modes make use of the 4-wire digital transmission bus consisting of the data clock (PCLK), an 8kHz Frame Synchronization clock (FS), an upstream transmit data signal ( $D_{TX}$ ) and a downstream receive data signal ( $D_{RX}$ ). Although both modes use this 4-wire bus, the data structure within the digital transmit and receive streams is dissimilar.

One major difference between the PCM Mode and the GCI Mode of operation is how provisioning, control and status is implemented. When operating in the PCM Mode a serial (SPI) bus is utilized to perform these functions. In the GCI Mode these functions are embedded in the transmit and receive data streams, thereby eliminating the need for an additional bus for command and control.

#### 3.1 Digital Transmission Mode Selection

Configuring the CPC5750 to operate in PCM or GCI Mode is performed during either a Power Up or Reset event using the level at the SDI input pin to determine the mode. Holding SDI high will cause the CPC5750 to be placed into the PCM Mode of operation while holding SDI low will result in the GCI Mode.

For PCM applications, the voltage available at SDI during power up may not satisfy the specified logic high threshold voltage stated in **Section 1.7 Digital Interface Characteristics on page 6**. To ensure a logic high is recognized at the SDI input during power up, the input should be biased to  $V_{DD}$ . As the  $V_{DD}$  supply rises towards the Power On Reset threshold, the CPC5750 will accept the  $V_{DD}$  voltage level at SDI as a logic high.

Because the GCI Mode does not utilize the SPI bus, those applications should tie the SDI input low and the  $\overline{CS}$  input to the appropriate logic level dependent on the desired companding. The companding method set by  $\overline{CS}$  during Power Up or Reset can be overridden by provisioning bit 7 of the Mode Control register.

# 3.2 PCLK Frequencies and Time Slot Selection

The clocking circuits use the Frame Sync (FS) signal from the PCM or IOM-2 bus to automatically determine the PCLK frequency and divides or multiplies the clock as necessary to generate an on-chip 1.024MHz clock.

The table below shows the allowed PCLK frequencies for both the PCM and GCI Modes and the time slot allocations. For the PCM Mode there are eight allowed PCLK frequencies while the IOM-2 GCI Mode has only two. When using the PCM Mode, the maximum number of available time slots is dependent on the number of eight bit channels that can be transferred within one period of the 8kHz Frame Sync clock. For all systems, the maximum number of time slots is the PCLK frequency divided by the Frame Sync frequency divided by the number of clock bits (pulses) per channel. A system that uses one clock bit for each transmission bit, the number of time slots is the PCLK frequency divided by 8kHz divided by 8 clock pulses which is PCLK / 64kHz. PCM systems using two PCLK pulses per transmission bit will need to set bit 2 of the Mode Control register to a logic 1. Calculating the number of time slots is now PCLK frequency / 128kHz. The table below provides a quick reference.

Assignment of the specific time slot to be used when in PCM Mode is done by provisioning the PCM transmit and receive time slot assignment registers described in **Section 2.8** and **Section 2.6 beginning on page 13**.

Only two PCLK frequencies are allowed for the IOM-2 GCI Mode and the number of available time slots is independent of the clock frequency. Because the number of time slots in GCI Mode is fixed and the higher allowed frequency is twice the lower allowed frequency, the CPC5750 will use two PCLK bits per transmission bit when it detects the higher allowed PCLK frequency. This is shown in the following table.

Available time slots for the IOM-2 GCI Mode is based on the number of available sub-frames. The IOM-2 GCI definition provides for eight sub-frames within a single frame defined by the time period of the Frame Sync clock.

CPC5750

Although the IOM-2 specification provides for two digitized voice time slots per sub-frame, the CPC5750 only uses the B1 time slot. This allows for a total of eight available time slots when operating in the GCI Mode.

**PRELIMINARY**

Selection of the sub-frame is not a provisioning option. It is done by applying the appropriate logic levels at pins: SCLK, SDO, and SFSEL. See **Section 6 IOM-2 (GCI) Interface beginning on page 23** and **Table 4 on page 23** for more details.

**Table 2: PCLK Frequencies and Available PCM Time Slots**

| Frequency | Available PCM Time Slots<br>CPB = 0<br>(1 Clock per bit) | Available PCM Time Slots<br>CPB = 1<br>(2 Clocks per bit) | GCI Frequency         |

|-----------|----------------------------------------------------------|-----------------------------------------------------------|-----------------------|

| 512kHz    | 8                                                        | 4                                                         | No                    |

| 1.024MHz  | 16                                                       | 8                                                         | No                    |

| 1.536MHz  | 24                                                       | 12                                                        | No                    |

| 2.048MHz  | 32                                                       | 16                                                        | Yes: 1 Clock per bit  |

| 3.072MHz  | 48                                                       | 24                                                        | No                    |

| 4.096MHz  | 64                                                       | 32                                                        | Yes: 2 Clocks per bit |

| 6.144MHz  | 96                                                       | 48                                                        | No                    |

| 8.192MHz  | 128                                                      | 64                                                        | No                    |

#### 3.3 Hardware Configuration For Transmission Mode Selection

To ensure correct initialization of the CPC5750 following a Power Up or Reset event, the appropriate inputs must be properly conditioned.

PCM Mode: SDI = 1 and  $\overline{CS} = x$ GCI Mode: SDI = 0 and  $\overline{CS} = x$ ;

Also, the sub-frame selection using SCLK, SDO, and SFSEL must be made at this time.

Failure to condition and hold these inputs at the appropriate logic level for the specified duration during Power Up or Reset will require a Reset to re-initialize the device.

While the input  $\overline{\text{CS}}$  may be conditioned to configure the CPC5750 for the desire companding method, this can be modified via provisioning once the part becomes active.

#### Special Notes:

- 1) SDI and  $\overline{\text{CS}}$  are not used in normal operation of the GCI Mode, therefore it is recommended that these unused inputs be fixed to a stable logic level.

- 2) For the PCM Mode, SFSEL is an unused input and should be fixed to a stable logic level.

# 4. Functional Description - To Do

CPC5750

**PRELIMINARY**

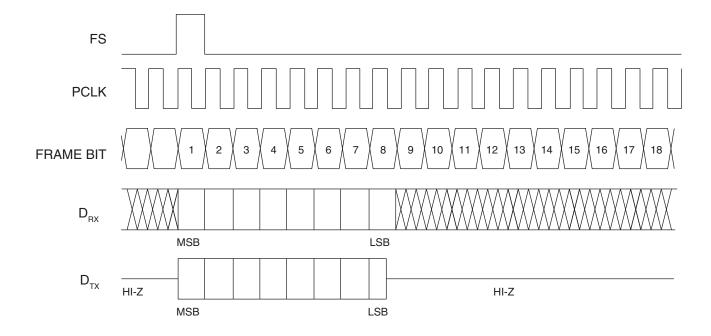

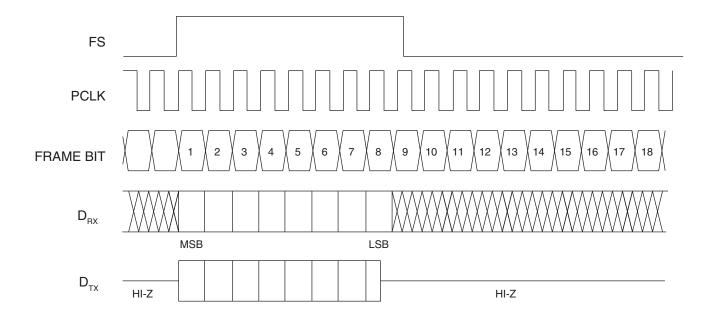

#### 5. PCM Bus Interface

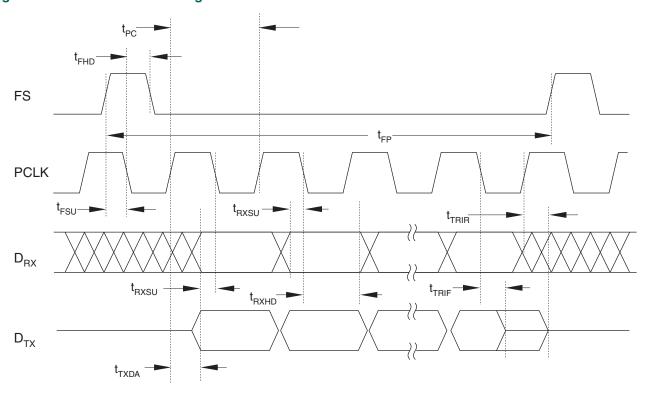

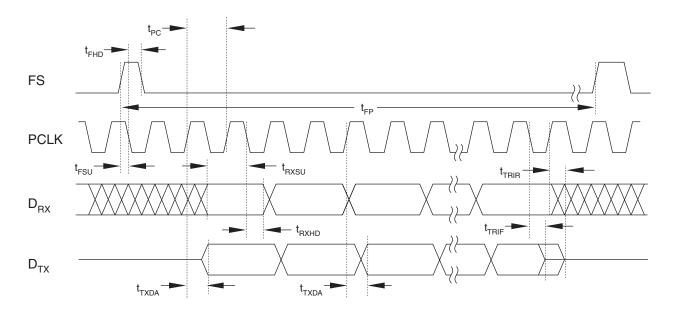

The PCM bus consists of four signals: PCLK, FS,  $D_{TX}$ , and  $D_{RX}$  which are used to transmit and receive one byte each (eight bits) of  $\mu$ -law or A-law companded audio data every cycle of the 8kHz Frame Sync (FS) clock. This provides for a 64k bit per second data rate in each direction. Provided within each frame (cycle of the FS clock) are a number of 8-bit time slots determined by the frequency of PCLK and the value assigned to the CPB bit in the Mode Control register. The number of available time slots is calculated as the PCLK frequency (variable) divided by the FS frequency (fixed at 8kHz) divided by the number of PCLK cycles per data byte (variable, 8 or 16 controlled by CPB). The relationship between the PCLK frequency and CPB to the number of available PCM time slots is shown in Table 2: PCLK Frequencies and Available PCM Time Slots.

Capable of transmitting (upstream) and receiving (downstream) in separate time slots, the CPC5750 PCM upstream and downstream data paths can be provisioned independently to any of the available time slots within the frame. Additionally, the upstream and downstream paths can be provisioned independently for bit delays within the time slot. While the non-delayed timing mode does not have bit delays, the delayed timing mode does. To provide for bit delays within the system, the CPC5750 allows the user to provision the time slot starting point to any of the possible bits within the 125µs frame. This requires 10 bits to accommodate the device's 128 maximum time slots. The lower 3 bits used to modify the start bit (MSB) position within a time slot is in a separate register from the time slot assignment register to ease provisioning for applications that require setting only the 8-bit time slot or just the bit delay, allowing the other register to be ignored.

The CPC5750 PCM bus is a 4-wire full duplex digital transmission medium using two data wires,  $D_{TX}$  and  $D_{RX}$ , so data can be transmitted and received simultaneously. The  $D_{TX}$  transmit signal used to send data upstream is output onto a common bus. Since other devices assigned to different time slots transmit their upstream data onto this same bus, the CPC5750 must tri-state  $D_{TX}$  during all non-assigned time slots. Determination of when  $D_{TX}$  tri-states after it outputs 8-bits of data is contingent upon the value set in the Mode Control register's TXZ bit. For provisioning details see **Section 2.1.6 TXZ** (bit 1) and **Section 2.1.5 CPB** (bit 2) beginning on page 12.

Time slot locations within the transmit and receive data bit streams are defined by the location of the Frame Synchronization (FS) pulse and the value set in bit delay registers as described in Section 2.9 PCM Interface DTX Bit Delay Register and Section 2.7 PCM Interface DRX Bit Delay Register beginning on page 13. Historically, timing of data bit streams was defined by two modes, Non-delayed Timing Mode and Delayed Timing Mode by means of a Long Frame Sync pulse and a Short Frame Sync pulse to establish a reference point for the first bit of the first time slot of the frame.

The Non-delayed Timing Mode used the Long Frame Sync as an enable to define the location of the time slot. The first data bit of the Long Frame Sync time slot was defined as the first concurrent logic high of the PCM clock and the frame sync pulse. In this configuration there is no requirement for the rising edge of the clock or the sync pulse to precede the other. Because the Long Frame Sync pulse is an enable, the width of pulse needs to be sufficient to ensure data transfer of all eight bits.

The Delayed Timing Mode used the Short Frame Sync to establish the beginning of the first time slot within the frame. This method used the first falling edge of the PCM clock to register the frame synchronization pulse marking the end of the current frame. With the conclusion of the current frame, the first bit of the next frame begins with the next rising edge of the PCM clock. Because this method provides an indicator prior to the beginning of the frame it is ideal for use in systems wishing to delay data transfer.

The CPC5750 uses a timing mode that is compatible with both of these legacy techniques. Interoperability is assured by the internal timing circuitry and the device's ability to access the data bit stream at any point within the frame. In the CPC5750, the first bit of the frame is defined as coincident with the PCLK rising edge preceding the falling PCLK edge used to detect the active FS pulse.

Because the first transmitted data bit is in the same bit time as the FS pulse, the  $D_{TX}$  driver must be enabled with the correct data before the FS signal is detected. For this to happen, the CPC5750 must count the PCLK cycles in the first complete frame to determine the number of 8-bit time slots per frame so it can predict when to drive the  $D_{TX}$  bus. If the FS pulse does not arrive as predicted, then the CPC5750 will re-synchronize, and recount the time slots in the frame. For this reason the data in the first two received frames after connection to a PCM bus will be ignored and no data will be transmitted upstream.

Detection of the FS pulse with the PCLK falling edge eliminates the rigid FS pulse width constraints and the required synchronization of the FS rising edge with the PCLK rising edge. The minimum FS pulse width is the sum of the setup and hold times while the maximum pulse width must allow for a minimum of one FS low detect by the falling PCLK edge.

Assuring the first upstream data bit is available with the rising edge of FS and allowing the FS pulse to persist for multiple PCLK cycles provides compatibility with the legacy Long Frame Sync, Non-delayed Timing Mode when the time slot and bit delay setting registers are configured for the first bit of the first time slot, (Time Slot 0 {zero} and no bit delay) of the frame. Additionally, since the CPC5750 is designed to accept small FS pulses and can be provisioned for the transfer of data delayed by one or more bits it is compatible with the legacy Short Frame Sync Delayed Timing Mode. As with the legacy data bit stream formats, the Most Significant Bit (MSB) will be the first bit received and the first bit transmitted in the data byte.

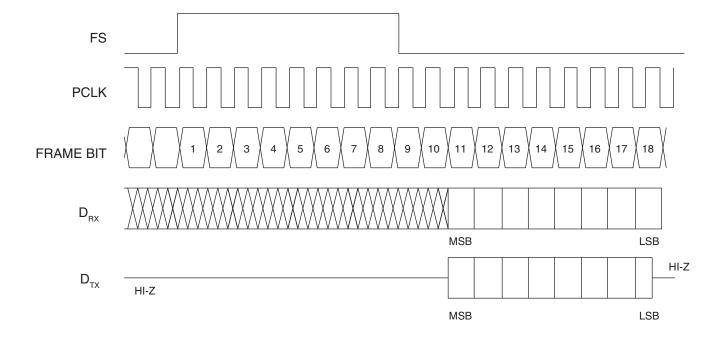

Figure 1: PCM Time Slot 0, Short FS, No Bit Delay (PTC=PRC=0, PTB=PRB=0, CPB=0, TXZ=1)

Figure 2: PCM Time Slot 0, Long FS, No Bit Delay (PTC=PRC=0, PTB=PRB=0, CPB=0, TXZ=1)

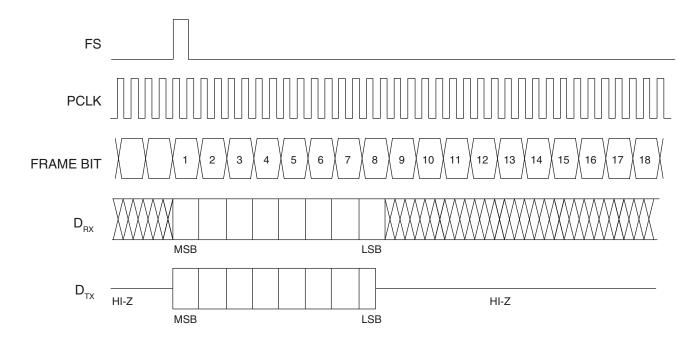

Figure 3: PCM Time Slot 1, Long FS, 2 Bit Delay (PTC=PRC=1, PTB=PRB=2, CPB=0, TXZ=1)

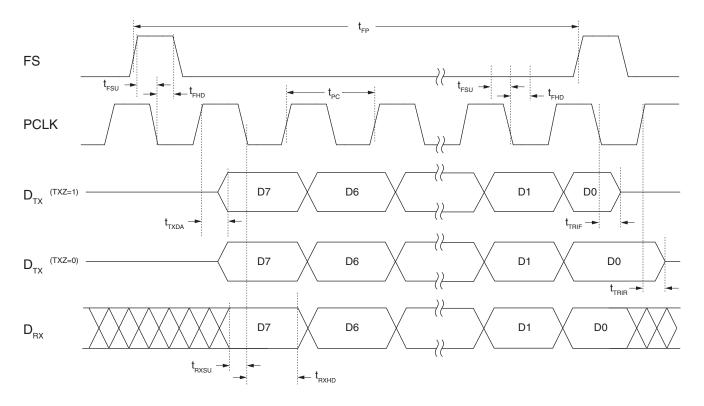

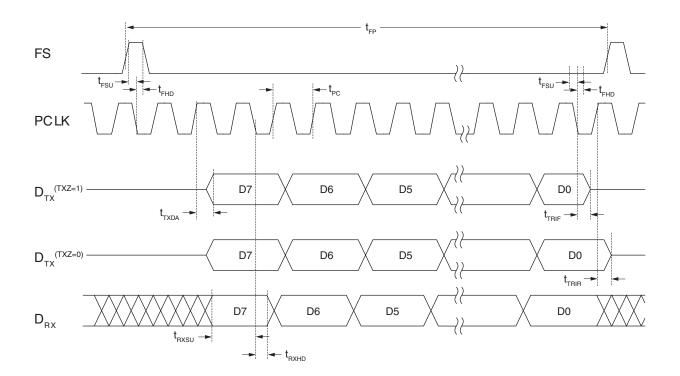

Figure 4: PCM Time Slot 0, Short FS, No Bit Delay, 2x PCLK (PTC=PRC=0, PTB=PRB=0, CPB=1, TXZ=1)

**Table 3: PCM Interface AC Characteristics**

Ambient temperature range -40°C to +85°C;  $V_{CC}$ = $V_{DD}$ =3V to 3.6V

| Parameter                                          | Test Condition | Symbol            | Min | Тур | Max  | Units |

|----------------------------------------------------|----------------|-------------------|-----|-----|------|-------|

| FS Period                                          | -              | t <sub>FP</sub>   | -   | 125 | -    | μS    |

| FS Jitter                                          | -              | t <sub>FJ</sub>   | -   | -   | 100  | ns    |