Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 4 In/4 Out Audio CODEC with PCM and TDM Interfaces

#### **DAC Features**

- ♦ Advanced multibit delta-sigma modulator

- ♦ 24-bit resolution

- ♦ Differential or single-ended outputs

- ♦ Dynamic range (A-weighted)

- -109 dB differential

- 105 dB single-ended

- ♦ THD+N

- -90 dB differential

- 88 dB single ended

- ♦ 2 Vrms full-scale output into 3-kΩ AC load

- ♦ Rail-to-rail operation

#### **ADC Features**

- ♦ Advanced multibit delta-sigma modulator

- ♦ 24-bit resolution

- ♦ Differential inputs

- ♦ -105 dB dynamic range (A-weighted)

- ♦ -88 dB THD+N

- ♦ 2 Vrms full-scale input

### System Features

- ♦ TDM, left justified, and I2S serial inputs and outputs

- ♦ I2C host control port

- ♦ Supports logic levels between 5 and 1.8 V

- ♦ Supports sample rates up to 96 kHz

## Common Applications

- ♦ Automotive audio systems

- ♦ AV, Blu-Ray<sup>®</sup> Disc, and DVD receivers

- Audio interfaces, mixing consoles, and effects processors

## **General Description**

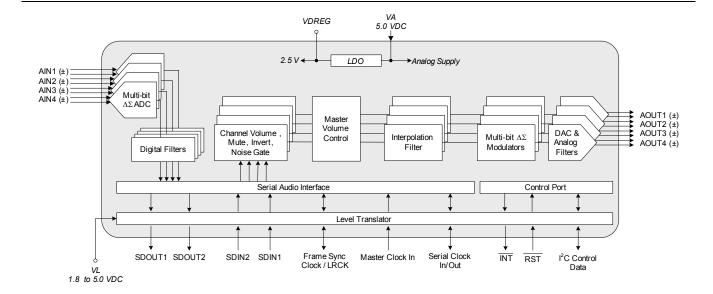

The CS4244 provides four multibit analog-to-digital and four multi-bit digital-to-analog  $\Delta$ - $\Sigma$  converters and is compatible with differential inputs and either differential or single-ended outputs. Digital volume control, noise gating, and muting is provided for each DAC path. A selectable high-pass filter is provided for the 4 ADC inputs. The CS4244 supports master and slave modes and TDM, left-justified, and l²S modes.

This product is available in a 40-pin QFN package in Automotive (-40°C to +85°C) and Commercial (0°C to +70°C) temperature grades. The CDB4244 Customer Demonstration Board is also available for device evaluation and implementation suggestions. See "Ordering Information" on page 64 for complete details.

# TABLE OF CONTENTS

| 1. PIN DESCRIPTIONS                                                     | 5    |

|-------------------------------------------------------------------------|------|

| 1.1 I/O Pin Characteristics                                             |      |

| 2. TYPICAL CONNECTION DIAGRAM                                           | _    |

| 3. CHARACTERISTICS AND SPECIFICATIONS                                   |      |

| RECOMMENDED OPERATING CONDITIONS                                        | 8    |

| ABSOLUTE MAXIMUM RATINGS                                                |      |

| DC ELECTRICAL CHARACTERISTICS                                           | 9    |

| TYPICAL CURRENT CONSUMPTION                                             | . 10 |

| ANALOG INPUT CHARACTERISTICS (COMMERCIAL GRADE)                         | . 11 |

| ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE GRADE)                         | . 12 |

| ADC DIGITAL FILTER CHARACTERISTICS                                      |      |

| ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL GRADE)                        |      |

| ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE GRADE)                        |      |

| COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE             |      |

| DIGITAL I/O CHARACTERISTICS                                             | . 18 |

| SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE                      |      |

| SWITCHING SPECIFICATIONS - CONTROL PORT                                 |      |

| 4. APPLICATIONS                                                         |      |

| 4.1 Power Supply Decoupling, Grounding, and PCB Layout                  |      |

| 4.2 Recommended Power-up & Power-down Sequence                          |      |

| 4.3 I <sup>2</sup> C Control Port                                       |      |

| 4.4 System Clocking                                                     |      |

| 4.5 Serial Port Interface                                               |      |

| 4.6 Internal Signal Path                                                |      |

| 4.7 Reset Line                                                          |      |

| 4.8 Error Reporting and Interrupt Behavior                              |      |

| 5. REGISTER QUICK REFERENCE                                             |      |

| 6. REGISTER DESCRIPTIONS                                                |      |

| 6.1 Device I.D. A–F (Address 01h–03h) (Read Only)                       |      |

| 6.2 Revision I.D. (Address 05h) (Read Only)                             |      |

| 6.3 Clock & SP Select (Address 06h)                                     |      |

| 6.4 Sample Width Select (Address 07h)                                   |      |

| 6.5 Serial Port Control (Address 08h)                                   |      |

| 6.6 Serial Port Data Select (Address 09h)                               |      |

| 6.7 ADC Control 1 (Address 0Fh)                                         |      |

| 6.8 ADC Control 2 (Address 10h)                                         |      |

| 6.9 DAC Control 1 (Address 12h)                                         |      |

| 6.10 DAC Control 2 (Address 13h)                                        |      |

| 6.11 DAC Control 3 (Address 14h)                                        |      |

| 6.12 DAC Control 4 (Address 15h)                                        |      |

| 6.13 Volume Mode (Address 16h)                                          |      |

| 6.15 Interrupt Control (Address 1Eh)                                    |      |

| 6.16 Interrupt Mask 1 (Address 1Fh)                                     |      |

| 6.17 Interrupt Mask 1 (Address 1Fn) 6.17 Interrupt Mask 2 (Address 20h) |      |

| 6.18 Interrupt Notification 1 (Address 21h) (Read Only)                 |      |

| 6.19 Interrupt Notification 2 (Address 22h) (Read Only)                 |      |

| 7. ADC FILTER PLOTS                                                     |      |

| 8. DAC FILTER PLOTS                                                     |      |

| 9. PACKAGE DIMENSIONS                                                   |      |

| 10. ORDERING INFORMATION                                                |      |

| 11. REVISION HISTORY                                                    |      |

|                                                                         |      |

## **LIST OF FIGURES**

| Figure 1.CS4244 Pinout                                                                                | 5  |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 2.Typical Connection Diagram                                                                   | 7  |

| Figure 3. Test Circuit for ADC Performance Testing                                                    | 13 |

| Figure 4.PSRR Test Configuration                                                                      | 13 |

| Figure 5.Equivalent Output Test Load                                                                  | 16 |

| Figure 6.TDM Serial Audio Interface Timing                                                            | 20 |

| Figure 7.PCM Serial Audio Interface Timing                                                            | 20 |

| Figure 8.I2C Control Port Timing                                                                      | 21 |

| Figure 9.System Level Initialization and Power-Up/Down Sequence                                       | 23 |

| Figure 10.DAC DC Loading                                                                              | 24 |

| Figure 11.Timing, I2C Write                                                                           | 25 |

| Figure 12.Timing, I <sup>2</sup> C Read                                                               | 25 |

| Figure 13.Master Mode Clocking                                                                        |    |

| Figure 14.TDM System Clock Format                                                                     | 28 |

| Figure 15.32-bit Receiver Channel Block                                                               |    |

| Figure 16. Serial Data Coding and Extraction Options within the TDM Streams                           |    |

| Figure 17.Left Justified Format                                                                       | 30 |

| Figure 18.I2S Format                                                                                  | 30 |

| Figure 19. Audio Path Routing                                                                         | 31 |

| Figure 20. Conventional SDOUT (Left) vs. Sidechain SDOUT (Right) Configuration                        |    |

| Figure 21.DAC1-4 Serial Data Source Selection                                                         | 33 |

| Figure 22.Example Serial Data Source Selection                                                        | 34 |

| Figure 23.ADC Path                                                                                    | 35 |

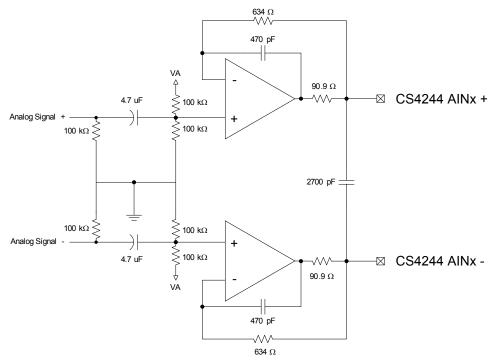

| Figure 24. Single-Ended to Differential Active Input Filter                                           |    |

| Figure 25. Single-Ended to Differential Active Input Filter - DC Coupled Input Signal (VA/2 Centered) | 36 |

| Figure 26.DAC1-4 Path                                                                                 |    |

| Figure 27.De-emphasis Curve                                                                           | 38 |

| Figure 28.Passive Analog Output Filter                                                                |    |

| Figure 29.Volume Implementation for the DAC1-4 Path                                                   | 39 |

| Figure 30.Soft Ramp Behavior                                                                          | 40 |

| Figure 31.Interrupt Behavior and Example Interrupt Service Routine                                    |    |

| Figure 32.ADC Stopband Rejection                                                                      | 59 |

| Figure 33.ADC Transition Band                                                                         |    |

| Figure 34.ADC Transition Band (Detail)                                                                | 59 |

| Figure 35.ADC Passband Ripple                                                                         |    |

| Figure 36.ADC HPF (48 kHz)                                                                            |    |

| Figure 37.ADC HPF (96 kHz)                                                                            | 59 |

| Figure 38.SSM DAC Stopband Rejection                                                                  | 60 |

| Figure 39.SSM DAC Transition Band                                                                     |    |

| Figure 40.SSM DAC Transition Band (Detail)                                                            |    |

| Figure 41.SSM DAC Passband Ripple                                                                     |    |

| Figure 42.DSM DAC Stopband Rejection                                                                  |    |

| Figure 43.DSM DAC Transition Band                                                                     |    |

| Figure 44.DSM DAC Transition Band (Detail)                                                            |    |

| Figure 45.DSM DAC Passband Ripple                                                                     |    |

| Figure 46 Packago Drawing                                                                             | 62 |

# LIST OF TABLES

| Table 1. Speed Modes                                     | 26 |

|----------------------------------------------------------|----|

| Table 2. Common Clock Frequencies                        |    |

| Table 3. Master Mode Left Justified and I2S Clock Ratios |    |

| Table 4. Slave Mode Left Justified and I2S Clock Ratios  | 27 |

| Table 5. Slave Mode TDM Clock Ratios                     | 27 |

| Table 6. Soft Ramp Rates                                 | 41 |

| Table 7. Noise Gate Bit Depth Settings                   | 41 |

| Table 8. Error Reporting and Interrupt Behavior Details  | 42 |

## 1. PIN DESCRIPTIONS

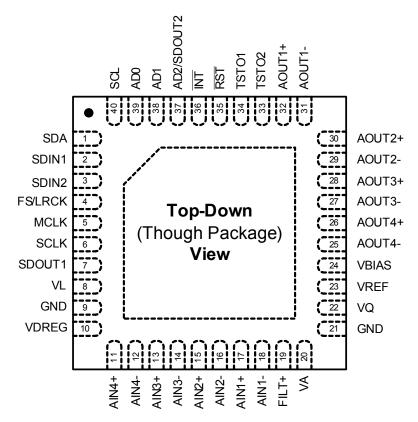

Figure 1. CS4244 Pinout

| Pin Name | Pin#            | Pin Description                                                                                                                                                                                                                    |

|----------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDA      | 1               | Serial Control Data (Input/Output) - Bi-directional data I/O for the I <sup>2</sup> C control port.                                                                                                                                |

| SDINx    | 2,3             | Serial Data Input (Input) - Input channels serial audio data.                                                                                                                                                                      |

| FS/LRCK  | 4               | Frame Synchronization Clock/Left/Right Clock (Input/Output) - Determines which channel or frame is currently active on the serial audio data line.                                                                                 |

| MCLK     | 5               | Master Clock (Input) -Clock source for the internal logic, processing, and modulators.                                                                                                                                             |

| SCLK     | 6               | Serial Clock (Input/Output) -Serial Clock for the serial data port.                                                                                                                                                                |

| SDOUT1   | 7               | Serial Data Output 1 (Output) - ADC data output into a multi-slot TDM stream or AIN1 and AIN2 ADC data output in Left Justified and I <sup>2</sup> S modes.                                                                        |

| VL       | 8               | Interface Power (Input) - Positive power for the digital interface level shifters.                                                                                                                                                 |

| GND      | 9,21            | Ground (Input) - Ground reference for the I/O and digital, analog sections.                                                                                                                                                        |

| VDREG    | 10              | Digital Power (Output) - Internally generated positive power supply for digital section.                                                                                                                                           |

| AINx+    | 11,13,15,<br>17 | <b>Positive Analog Input</b> ( <i>Input</i> ) - Positive input signals to the internal analog to digital converters. The full scale analog input level is specified in the Analog Input Characteristics tables on pages 12 and 13. |

| AINx-    | 12,14,16,<br>18 | <b>Negative Analog Input</b> ( <i>Input</i> ) - Negative input signals to the internal analog to digital converters. The full scale analog input level is specified in the Analog Input Characteristics tables on pages 12 and 13. |

| FILT+    | 19              | Positive Voltage Reference (Output) - Positive reference voltage for the internal ADCs.                                                                                                                                            |

| VA         | 20              | Analog Power (Input) - Positive power for the analog sections.                                                                                                                                                                                                                                                           |

|------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VQ         | 22              | Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.                                                                                                                                                                                                                                           |

| VREF       | 23              | Analog Power Reference (Input) - Return pin for the VBIAS cap.                                                                                                                                                                                                                                                           |

| VBIAS      | 24              | Positive Voltage Reference (Output) - Positive reference voltage for the internal DACs.                                                                                                                                                                                                                                  |

| AOUTx-     | 25,27,29,<br>31 | <b>Negative Analog Output</b> ( <i>Output</i> ) - Negative output signals from the internal digital to analog converters. The full scale analog output level is specified in the Analog Output Characteristics tables on pages 16 and 17.                                                                                |

| AOUTx+     | 26,28,30,<br>32 | <b>Positive Analog Output</b> ( <i>Output</i> ) - Positive output signals from the internal digital to analog converters. The full scale analog output level is specified in the Analog Output Characteristics tables on pages 16 and 17.                                                                                |

| TSTOx      | 33,34           | Test Outputs (Output) - Test outputs. These pins should be left unconnected.                                                                                                                                                                                                                                             |

| RST        | 35              | Reset (Input) - Applies reset to the internal circuitry when pulled low.                                                                                                                                                                                                                                                 |

| ĪNT        | 36              | Interrupt (Output) - Sent to DSP to indicate an interrupt condition has occurred.                                                                                                                                                                                                                                        |

| AD2/SDOUT2 | 37              | I²C Address Bit 2/Serial Data Output 2 ( <i>Input/Output</i> ) - Sets the I²C address bit 2 at reset. Functions as Serial Data Out 2 for AIN3 and AIN4 ADC data output in Left Justified and I²S modes. High impedance in TDM mode. See Section 4.3 I²C Control Port for more details concerning this mode of operation. |

| AD1        | 38              | I²C Address Bit 1 (Input) - Sets the I²C address bit 1.                                                                                                                                                                                                                                                                  |

| AD0        | 39              | I²C Address Bit 0 (Input) - Sets the I²C address bit 0.                                                                                                                                                                                                                                                                  |

| SCL        | 40              | Serial Control Port Clock (Input) - Serial clock for the I <sup>2</sup> C control port.                                                                                                                                                                                                                                  |

| GND        | -               | <b>Thermal Pad</b> - The thermal pad on the bottom of the device should be connected to the ground plane via an array of vias.                                                                                                                                                                                           |

### 1.1 I/O Pin Characteristics

Input and output levels and associated power supply voltage are shown in the table below. Logic levels should not exceed the corresponding power supply voltage.

| Power Supply | Pin Name   | I/O          | Driver             | Internal Connections<br>(Note 1) | Receiver                    |

|--------------|------------|--------------|--------------------|----------------------------------|-----------------------------|

|              | SCL        | Input        | -                  | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | SDA        | Input/Output | CMOS/Open<br>Drain | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | ĪNT        | Output       | CMOS/Open<br>Drain | (Note 2)                         | -                           |

|              | RST        | Input        | -                  | (Note 2)                         | 5.0 V CMOS, with Hysteresis |

| VL           | MCLK       | Input        | -                  | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | FS/LRCK    | Input/Output | 5.0 V CMOS         | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | SCLK       | Input/Output | 5.0 V CMOS         | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | SDOUT1     | Output       | 5.0 V CMOS         | Weak Pull-down (~500kΩ)          |                             |

|              | SDINx      | Input        | -                  | Weak Pull-down (~500kΩ)          | 5.0 V CMOS, with Hysteresis |

|              | AD0,1      | Input        | -                  | (Note 2)                         | 5.0 V CMOS                  |

|              | AD2/SDOUT2 | Input/Output | 5.0 V CMOS         | (Note 2)                         | 5.0 V CMOS                  |

#### Notes:

- 1. Internal connection valid when device is in reset.

- 2. This pin has no internal pull-up or pull-down resistors. External pull-up or pull-down resistors should be added in accordance with Figure 2.

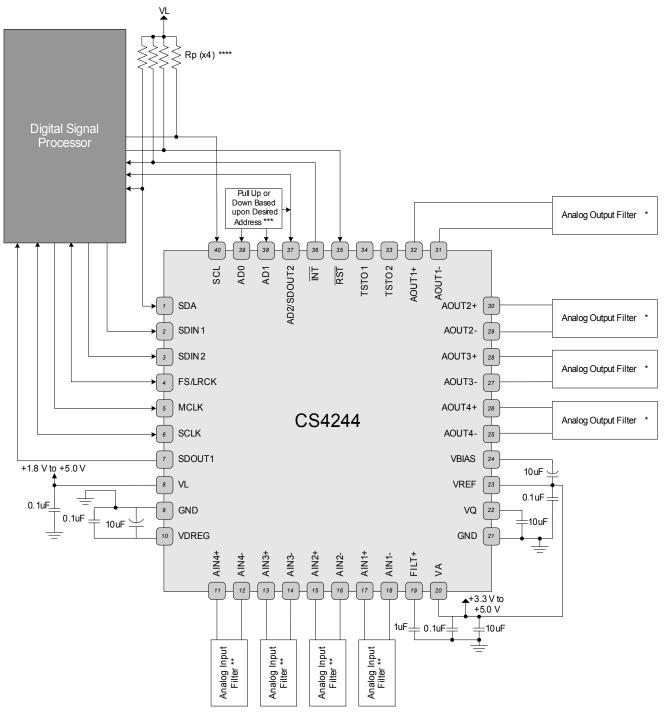

## 2. TYPICAL CONNECTION DIAGRAM

<sup>\*</sup> See Section 4.6.4

Figure 2. Typical Connection Diagram

<sup>\*\*</sup> See Section 4.6.2.2

<sup>\*\*\*</sup> See Section 4.3

<sup>\*\*\*\*</sup> See Switching Specifications - Control Port

### 3. CHARACTERISTICS AND SPECIFICATIONS

### RECOMMENDED OPERATING CONDITIONS

GND = 0 V; all voltages with respect to ground. (Note 3)

| Parameters                                    |                          | Symbol         | Min           | Тур      | Max           | Units    |

|-----------------------------------------------|--------------------------|----------------|---------------|----------|---------------|----------|

| DC Power Supply                               |                          |                | •             |          | •             |          |

| Analog Core                                   |                          | VA             | 3.135<br>4.75 | 3.3<br>5 | 3.465<br>5.25 | V<br>V   |

| Level Translator                              |                          | VL             | 1.71          | -        | 5.25          | V        |

| Temperature                                   | <u>.</u>                 |                |               |          |               |          |

| Ambient Operating Temperature - Power Applied | Automotive<br>Commercial | T <sub>A</sub> | -40<br>0      | -        | +85<br>+70    | °C<br>°C |

| Junction Temperature                          |                          | TJ             | -40           | -        | +150          | °C       |

**Notes:** 3. Device functional operation is guaranteed within these limits. Functionality is not guaranteed or implied outside of these limits. Operation outside of these limits may adversely affect device reliability.

### **ABSOLUTE MAXIMUM RATINGS**

GND = 0 V; all voltages with respect to ground.

| Parameters                                    |        | Symbol             | Min   | Max      | Units |

|-----------------------------------------------|--------|--------------------|-------|----------|-------|

| DC Power Supply                               |        |                    |       |          | •     |

| Analog Core                                   |        | VA                 | -0.3  | 5.5      | V     |

| Level Translator                              |        | VL                 | -0.3  | 5.5      | V     |

| VDREG Current (No                             | ote 4) | I <sub>VDREG</sub> | -     | 10       | μΑ    |

| Inputs                                        | •      |                    |       |          |       |

| Input Current (No                             | ote 5) | l <sub>in</sub>    | -     | ±10      | mA    |

| Analog Input Voltage (No                      | ote 6) | V <sub>INA</sub>   | - 0.3 | VA + 0.4 | V     |

| Logic Level Input Voltage (No                 | ote 6) | V <sub>IND</sub>   | -0.3  | VL + 0.4 | V     |

| Temperature                                   |        |                    |       |          |       |

| Ambient Operating Temperature - Power Applied |        | T <sub>A</sub>     | -55   | +125     | °C    |

| Storage Temperature                           |        | T <sub>stg</sub>   | -65   | +150     | °C    |

#### WARNING: OPERATION BEYOND THESE LIMITS MAY RESULT IN PERMANENT DAMAGE TO THE DEVICE.

Notes:

- 4. No external loads should be connected to the VDREG pin. Any connection of a load to this point may result in errant operation or performance degradation in the device.

- 5. Any pin except supplies. Transient currents of up to ±100 mA on the analog input pins will not cause SCR latch-up.

- 6. The maximum over/under voltage is limited by the input current.

## DC ELECTRICAL CHARACTERISTICS

GND = 0 V; all voltages with respect to ground.

| Parameters             | М        | lin | Тур    | Max | Units     |

|------------------------|----------|-----|--------|-----|-----------|

| VDREG (Note 7)         | <u>.</u> |     |        |     |           |

| Nominal Voltage        |          | -   | 2.5    | -   | V         |

| Output Impedance       |          | -   | 0.5    | -   | Ω         |

| FILT+                  |          |     |        | •   |           |

| Nominal Voltage        |          | -   | VA     | -   | V         |

| Output Impedance       |          | -   | 23     | -   | $k\Omega$ |

| DC Current Source/Sink |          | -   | -      | 1   | μΑ        |

| VQ                     |          |     |        | •   |           |

| Nominal Voltage        |          | -   | 0.5•VA | -   | V         |

| Output Impedance       |          | -   | 77     | -   | $k\Omega$ |

| DC Current Source/Sink |          | -   | -      | 0   | μΑ        |

### Notes:

7. No external loads should be connected to the VDREG pin. Any connection of a load to this point may result in errant operation or performance degradation in the device.

### TYPICAL CURRENT CONSUMPTION

This table represents the power consumption for individual circuit blocks within the CS4244. CS4244 is configured as shown in Figure 2 on page 8. VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC;  $F_S$  = 100 kHz; MCLK = 25.6 MHz; DAC load is 3 k $\Omega$ ; All input signals are zero (digital zero for SDINx inputs and AC coupled to ground for AINx inputs) .

|    |                                                                                         |       | (unless oth | urrent [mA]<br>erwise noted)<br>, (Note 12) |

|----|-----------------------------------------------------------------------------------------|-------|-------------|---------------------------------------------|

|    | Functional Block                                                                        | VA/VL | $i_{VA}$    | $i_{ m VL}$                                 |

| 1  | Reset Overhead                                                                          | 5     | 0.030       | 0.001                                       |

| Ι' | (All lines held static, RST line pulled low.)                                           | 3.3   | 0.020       | 0.001                                       |

| 2  | Power Down Overhead                                                                     | 5     | 5           | 0.101                                       |

| _  | (All lines clocks and data lines active, RST line pulled high, All PDNx bits set high.) | 3.3   | 5           | 0.101                                       |

| 3  | PLL (Note 10)                                                                           | 5     | 1           | -                                           |

| 3  | (Current drawn resulting from PLL being active. PLL is active for 256x and 384x)        | 3.3   | 1           | -                                           |

| 4  | DAC Overhead                                                                            | 5     | 50          | -                                           |

| -  | (Current drawn whenever any of the four DACs are powered up.)                           | 3.3   | 45          | -                                           |

| 5  | DAC Channel (Note 8)                                                                    | 5     | 5           | -                                           |

| 3  | (Current drawn per each DAC powered up.)                                                | 3.3   | 4           | -                                           |

| 6  | ADC Overhead                                                                            | 5     | 11          | -                                           |

| 0  | (Current drawn whenever any of the four ADCs are powered up.)                           | 3.3   | 11          | -                                           |

| 7  | ADC Group                                                                               | 5     | 2           | -                                           |

| '  | (Current drawn due to an ADC "group" being powered up. See (Note 11))                   | 3.3   | 2           | -                                           |

| 8  | ADC Channel                                                                             | 5     | 2           | 0.109                                       |

| 0  | (Current drawn per each ADC powered up.)                                                | 3.3   | 2           | 0.066                                       |

#### Notes:

- 8. Full-scale differential output signal.

- Current consumption increases with increasing F<sub>S</sub> and increasing MCLK. Values are based on F<sub>S</sub> of 100 kHz and MCLK of 25.6 MHz. Current variance between speed modes is small.

- PLL is activated by setting the MCLK RATE bit to either 000 (operating in 256x mode) or 001 (operating in 384kHz).

- 11. Internal to the CS4244, the analog to digital converters are grouped together in stereo pairs. ADC1 and ADC2 are grouped together as are ADC3 and ADC4. The ADC group current draw is the current that is drawn whenever one of these groups become active.

- 12. To calculate total current draw for an arbitrary amount of ADCs or DACs, the following equations apply:

<u>Total Running Current Draw from VA Supply</u> = Power Down Overhead + PLL (If Applicable) + DAC Current Draw + ADC Current Draw where

DAC Current Draw = DAC Overhead + (Number of DACs x DAC Channel)

ADC Current Draw = ADC Overhead + (Number of active ADC Group) + (Number of active ADC Channel)

and

<u>Total Running Current Draw from VL Supply</u> = PDN Overhead + (Number of active ADC Channels x ADC Channel)

## **ANALOG INPUT CHARACTERISTICS (COMMERCIAL GRADE)**

Test Conditions (unless otherwise specified): Device configured as shown in Section 2. on page 8. Input sine wave: 1 kHz;  $VA\_SEL = 0$  for VA = 3.3 VDC, 1 for VA = 5.0 VDC.;  $T_A = 25$  °C; Measurement Bandwidth is 20 Hz to 20 kHz unless otherwise specified; Sample Rate = 48 kHz; all Power Down ADCx bits = 0.

|                                   | VA,     | VREF = 3 | .3 V    | VA,     | .0 V    |         |              |

|-----------------------------------|---------|----------|---------|---------|---------|---------|--------------|

| Parameter                         | Min     | Тур      | Max     | Min     | Тур     | Max     | Unit         |

| Dynamic Range                     |         |          |         |         |         |         |              |

| A-weighted                        | 95      | 101      | -       | 99      | 105     | -       | dB           |

| unweighted                        | 92      | 98       | -       | 96      | 102     | -       | dB           |

| Total Harmonic Distortion + Noise |         |          |         |         |         |         |              |

| -1 dBFS                           | -       | -95      | -89     | -       | -88     | -82     | dB           |

| -60 dBFS                          | -       | -38      | -32     | -       | -42     | -36     | dB           |

| Other Analog Characteristics      |         |          |         |         |         |         |              |

| Interchannel Gain Mismatch        | -       | 0.2      | -       | -       | 0.2     | -       | dB           |

| Gain Drift                        | -       | ±100     | -       | -       | ±100    | -       | ppm/°C       |

| Offset Error (Note 13)            |         |          |         |         |         |         |              |

| High Pass Filter On               | -       | 0.0001   | -       | -       | 0.0001  | -       | % Full Scale |

| High Pass Filter Off              | -       | 0.25     | -       | -       | 0.25    | -       | % Full Scale |

| Interchannel Isolation            | -       | 90       | -       | -       | 90      | -       | dB           |

| Full-scale Input Voltage          |         |          |         |         |         |         |              |

| (Differential Inputs)             | 1.58•VA | 1.66•VA  | 1.74•VA | 1.58•VA | 1.66•VA | 1.74•VA | Vpp          |

| Input Impedance                   | -       | 40       | -       | -       | 40      | -       | kΩ           |

| Common Mode Rejection             | -       | 60       | -       | -       | 60      | -       | dB           |

| (Differential Inputs)             |         |          |         |         |         |         |              |

| PSRR (Note 14) 1 kHz              | -       | 45       | -       | -       | 45      | -       | dB           |

| 60 Hz                             | -       | 20       | -       | -       | 20      | -       | dB           |

## **ANALOG INPUT CHARACTERISTICS (AUTOMOTIVE GRADE)**

Test Conditions (unless otherwise specified): Device configured as shown in Section 2. on page 8. Input sine wave: 1 kHz; VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC.; T<sub>A</sub> = -40 to +85 °C; Measurement Bandwidth is 20 Hz to 20 kHz unless otherwise specified; Sample Rate = 48 kHz; all Power Down ADCx bits = 0.

|                                   | VA,     | VREF = 3 | .3 V    | VA,     | .0 V    |         |              |

|-----------------------------------|---------|----------|---------|---------|---------|---------|--------------|

| Parameter                         | Min     | Тур      | Max     | Min     | Тур     | Max     | Unit         |

| Dynamic Range                     |         |          |         |         |         |         |              |

| A-weighted                        | 93      | 101      | -       | 97      | 105     | -       | dB           |

| unweighted                        | 90      | 98       | -       | 94      | 102     | -       | dB           |

| Total Harmonic Distortion + Noise |         |          |         |         |         |         |              |

| -1 dBFS                           | -       | -95      | -87     | -       | -88     | -80     | dB           |

| -60 dBFS                          | -       | -38      | -30     | -       | -42     | -34     | dB           |

| Other Analog Characteristics      |         |          |         |         |         |         |              |

| Interchannel Gain Mismatch        | -       | 0.2      | -       | -       | 0.2     | -       | dB           |

| Gain Drift                        | -       | ±100     | -       | -       | ±100    | -       | ppm/°C       |

| Offset Error (Note 13)            |         |          |         |         |         |         |              |

| High Pass Filter On               | -       | 0.0001   | -       | -       | 0.0001  | -       | % Full Scale |

| High Pass Filter Off              | -       | 0.25     | -       | -       | 0.25    | -       | % Full Scale |

| Interchannel Isolation            | -       | 90       | -       | -       | 90      | -       | dB           |

| Full-scale Input Voltage          |         |          |         |         |         |         |              |

| (Differential Inputs)             | 1.58•VA | 1.66•VA  | 1.74•VA | 1.58•VA | 1.66•VA | 1.74•VA | Vpp          |

| Input Impedance                   | -       | 40       | -       | -       | 40      | -       | kΩ           |

| Common Mode Rejection             | -       | 60       | -       | -       | 60      | -       | dB           |

| (Differential Inputs)             |         |          |         |         |         |         |              |

| PSRR (Note 14) 1 kHz              | -       | 45       | -       | -       | 45      | -       | dB           |

| 60 Hz                             | -       | 20       | -       | -       | 20      | -       | dB           |

#### Notes:

- 13. AINx+ connected to AINx-.

- 14. Valid with the recommended capacitor values on FILT+ and VQ. See Figure 4 for test configuration.

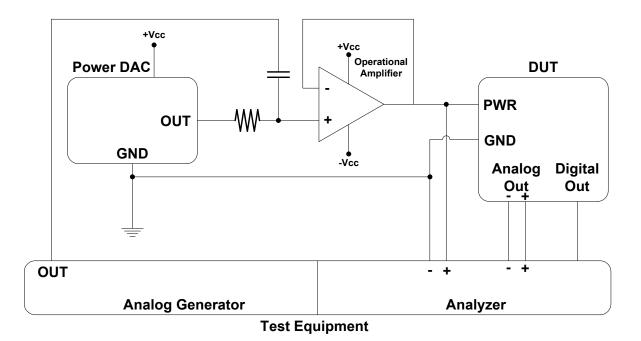

Figure 3. Test Circuit for ADC Performance Testing

Figure 4. PSRR Test Configuration

## **ADC DIGITAL FILTER CHARACTERISTICS**

Test Conditions (unless otherwise specified): Device configured as shown in Section 2. on page 8. Input sine wave: 1 kHz; VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC.; Measurement Bandwidth is 20 Hz to 20 kHz unless otherwise specified. See filter plots in Section 7. on page 60.

| Parameter (Note 15)                          |                | Min   | Тур      | Max    | Unit |

|----------------------------------------------|----------------|-------|----------|--------|------|

| Passband (Frequency Response) to             | -0.1 dB corner | 0     | -        | 0.4535 | Fs   |

| Passband Ripple                              |                | -0.09 | -        | 0.17   | dB   |

| Stopband                                     |                | 0.6   | -        | -      | Fs   |

| Stopband Attenuation                         |                | 70    | -        | -      | dB   |

| Single-Speed Mode                            | -              |       |          |        |      |

| ADC Group Delay (Note 16)                    |                | -     | 9.5/Fs   | -      | S    |

| High-Pass Filter Characteristics (48 kHz Fs) | -              |       |          |        |      |

| Frequency Response -3.0 dB                   |                | -     | 2        | -      | Hz   |

| -0.13 dB                                     |                | -     | 11       | -      | Hz   |

| Phase Deviation @ 20 Hz                      |                | -     | 10       | -      | Deg  |

| Passband Ripple                              |                | -0.09 | -        | 0.17   | dB   |

| Filter Settling Time (Note 17)               |                | -     | 25000/Fs | 0      | s    |

| Double-Speed Mode                            |                |       |          | •      |      |

| ADC Group Delay (Note 16)                    |                | -     | 9.5/Fs   | -      | S    |

| High-Pass Filter Characteristics (96 kHz Fs) |                |       |          | •      |      |

| Frequency Response -3.0 dB                   |                | -     | 4        | -      | Hz   |

| -0.13 dB                                     |                | -     | 22       | -      | Hz   |

| Phase Deviation @ 20 Hz                      |                | -     | 10       | -      | Deg  |

| Passband Ripple                              |                | -0.15 | -        | 0.17   | dB   |

| Filter Settling Time (Note 17)               |                | -     | 25000/Fs | 0      | S    |

#### Note:

- 15. Response is clock-dependent and will scale with Fs.

- 16. The ADC group delay is measured from the time the analog inputs are sampled on the AlNx pins to the FS/LRCK transition (rising or falling) after the last bit of that (group of) sample(s) has been transmitted on SDOUTx.

- 17. The amount of time from input of half-full-scale step function until the filter output settles to 0.1% of full scale.

## **ANALOG OUTPUT CHARACTERISTICS (COMMERCIAL GRADE)**

Test Conditions (unless otherwise specified). Device configured as shown in Section 2. on page 8. VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC.;  $T_A = 25 \text{ °C}$ ; Full-scale 1 kHz input sine wave; Sample Rate = 48 kHz; Measurement Bandwidth is 20 Hz to 20 kHz; Specifications apply to all channels unless otherwise indicated; all Power Down DACx bits = 0.8 See (Note 19) on page 17.

|                                      |              | VA, VREF= 3.3 V<br>(Differential/Single-ended) |          |          | VA<br>(Differer |          |          |        |

|--------------------------------------|--------------|------------------------------------------------|----------|----------|-----------------|----------|----------|--------|

| Parameter                            |              | Min                                            | Тур      | Max      | Min             | Тур      | Max      | Unit   |

| Dynamic Performance                  |              |                                                |          |          |                 |          |          |        |

| Dynamic Range                        |              |                                                |          |          |                 |          |          |        |

| 18 to 24-Bit                         | A-weighted   | 100/96                                         | 106/102  | -        | 103/99          | 109/105  | -        | dB     |

|                                      | unweighted   | 97/93                                          | 103/99   | -        | 100/96          | 106/102  | -        | dB     |

| 16-Bit                               | A-weighted   |                                                | 95       | -        | 89              | 95       | -        | dB     |

|                                      | unweighted   | 86                                             | 92       | -        | 86              | 92       | -        | dB     |

| Total Harmonic Distortion            | + Noise      | -                                              | -90/-88  | -84/-82  | -               | -90/-88  | -84/-82  | dB     |

| Full seeds Outset Vallage            |              | 1.48•VA/                                       | 1.56•VA/ | 1.64•VA/ | 1.48•VA/        | 1.56•VA/ | 1.64•VA/ | Vpp    |

| Full-scale Output Voltage            | ,            | 0.74•VA                                        | 0.78•VA  | 0.82•VA  | 0.74•VA         | 0.78•VA  | 0.82•VA  |        |

| Interchannel Isolation (1            | kHz)         | -                                              | 100      | -        | -               | 100      | -        | dB     |

| Interchannel Gain Misma              | tch          | -                                              | 0.1      | 0.25     | -               | 0.1      | 0.25     | dB     |

| Gain Drift                           |              | -                                              | ±100     | -        | -               | ±100     | -        | ppm/°C |

| AC-Load Resistance (RL)              | (Note 19)    | 3                                              | -        | -        | 3               | -        | -        | kΩ     |

| Load Capacitance (C <sub>L</sub> )(N | lote 19)     | -                                              | -        | 100      | -               | -        | 100      | pF     |

| Parallel DC-Load Resista             | nce(Note 20) | 10                                             | -        | -        | 10              | -        | -        | kΩ     |

| Output Impedance                     |              | -                                              | 100      | -        | -               | 100      | -        | Ω      |

| PSRR (Note 21)                       | 1 kHz        | -                                              | 60       | -        | -               | 60       | -        | dB     |

|                                      | 60 Hz        | -                                              | 60       | -        | -               | 60       | -        | dB     |

## **ANALOG OUTPUT CHARACTERISTICS (AUTOMOTIVE GRADE)**

Test Conditions (unless otherwise specified): Device configured as shown in Section 2. on page 8. VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC.;  $T_A = -40 \text{ to } +85 \text{ °C}$ ; Full-scale 1 kHz input sine wave; Sample Rate = 48 kHz; Measurement Bandwidth is 20 Hz to 20 kHz; Specifications apply to all channels unless otherwise indicated; all Power Down DACx bits = 0.5 See (Note 19).

|                                      |              | VA, VREF= 3.3 V<br>(Differential/Single-ended) |          | VA <sub>:</sub><br>(Differer |          |          |          |        |

|--------------------------------------|--------------|------------------------------------------------|----------|------------------------------|----------|----------|----------|--------|

| Parameter                            |              | Min                                            | Тур      | Max                          | Min      | Тур      | Max      | Unit   |

| Dynamic Performance                  |              |                                                |          |                              |          |          |          |        |

| Dynamic Range                        |              |                                                |          |                              |          |          |          |        |

| 18 to 24-Bit                         | A-weighted   | 98/94                                          | 106/102  | -                            | 101/97   | 109/105  | -        | dB     |

|                                      | unweighted   | 95/91                                          | 103/99   | -                            | 98/94    | 106/102  | -        | dB     |

| 16-Bit                               | A-weighted   | 87                                             | 95       | -                            | 87       | 95       | -        | dB     |

|                                      | unweighted   | 84                                             | 92       | -                            | 84       | 92       | -        | dB     |

| Total Harmonic Distortion            | + Noise      | -                                              | -90/-88  | -82/-80                      | -        | -90/-88  | -82/-80  | dB     |

| E. II. a. a. I.a. O. Annat Maltana   |              | 1.48•VA/                                       | 1.56•VA/ | 1.64•VA/                     | 1.48•VA/ | 1.56•VA/ | 1.64•VA/ | Vpp    |

| Full-scale Output Voltage            | ;            | 0.74•VA                                        | 0.78•VA  | 0.82•VA                      | 0.74•VA  | 0.78•VA  | 0.82•VA  |        |

| Interchannel Isolation (1            | kHz)         | -                                              | 100      | -                            | -        | 100      | -        | dB     |

| Interchannel Gain Misma              | tch          | -                                              | 0.1      | 0.25                         | -        | 0.1      | 0.25     | dB     |

| Gain Drift                           |              | -                                              | ±100     | -                            | -        | ±100     | -        | ppm/°C |

| AC-Load Resistance (R <sub>L</sub>   | )(Note 19)   | 3                                              | -        | -                            | 3        | -        | -        | kΩ     |

| Load Capacitance (C <sub>L</sub> )(N | lote 19)     | -                                              | -        | 100                          | -        | -        | 100      | pF     |

| Parallel DC-Load Resista             | nce(Note 20) | 10                                             | -        | -                            | 10       | -        | -        | kΩ     |

| Output Impedance                     |              | -                                              | 100      | -                            | -        | 100      | -        | Ω      |

| PSRR (Note 21)                       | 1 kHz        | -                                              | 60       | -                            | -        | 60       | -        | dB     |

|                                      | 60 Hz        | -                                              | 60       | -                            | -        | 60       | -        | dB     |

#### Notes:

- 18. One LSB of triangular PDF dither added to data.

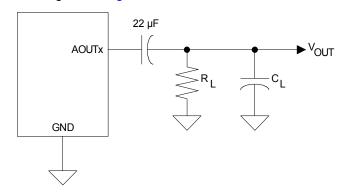

- 19. Loading configuration is given in Figure 5 below.

Figure 5. Equivalent Output Test Load

- 20. Parallel combination of all DAC DC loads. See Section 4.2.3.

- 21. Valid with the recommended capacitor values on FILT+ and VQ. See Figure 4 for test configuration.

## **COMBINED DAC INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE**

Test Conditions (unless otherwise specified):  $VA\_SEL = 0$  for VA = 3.3 VDC, 1 for VA = 5.0 VDC. The filter characteristics have been normalized to the sample rate ( $F_S$ ) and can be referenced to the desired sample rate by multiplying the given characteristic by  $F_S$ .

| Parameter                          |                    | Min    | Тур   | Max    | Unit           |

|------------------------------------|--------------------|--------|-------|--------|----------------|

| Single-Speed Mode                  |                    |        |       |        |                |

| Passband (Note 22)                 | to -0.05 dB corner | 0      | -     | 0.4780 | F <sub>S</sub> |

|                                    | to -3 dB corner    | 0      | -     | 0.4996 | F <sub>S</sub> |

| Frequency Response 20 Hz to 20 kHz |                    | -0.01  | -     | +0.12  | dB             |

| StopBand                           |                    | 0.5465 | -     | -      | F <sub>S</sub> |

| StopBand Attenuation               | (Note 23)          | 102    | -     | -      | dB             |

| DAC1-4 Group Delay (Note 24)       |                    | -      | 11/Fs | -      | S              |

| Double-Speed Mode                  |                    |        |       |        |                |

| Passband (Note 22)                 | to -0.1 dB corner  | 0      | -     | 0.4650 | F <sub>S</sub> |

|                                    | to -3 dB corner    | 0      | -     | 0.4982 | F <sub>S</sub> |

| Frequency Response 20 Hz to 20 kHz |                    | -0.05  | -     | +0.2   | dB             |

| StopBand                           |                    | 0.5770 | -     | -      | F <sub>S</sub> |

| StopBand Attenuation               | (Note 23)          | 80     | -     | -      | dB             |

| DAC1-4 Group Delay (Note 24)       |                    | -      | 7/Fs  | -      | S              |

#### Notes:

- 22. Response is clock-dependent and will scale with F<sub>S</sub>.

- 23. For Single-Speed Mode, the measurement bandwidth is 0.5465  $F_S$  to 3  $F_S$ . For Double-Speed Mode, the measurement bandwidth is 0.577  $F_S$  to 1.4  $F_S$ .

- 24. The DAC group delay is measured from the FS/LRCK transition (rising or falling) before the first bit of a (group of) sample(s) is transmitted on the SDINx pins to the time it appears on the AOUTx pins.

# DIGITAL I/O CHARACTERISTICS

| Parameters                                                                       |           | Symbol          | Min | Тур | Max | Units |

|----------------------------------------------------------------------------------|-----------|-----------------|-----|-----|-----|-------|

| High-Level Input Voltage (all input pins except RST) (VL = 1.8 V)                | (% of VL) | V <sub>IH</sub> | 75% | -   | -   | ٧     |

| High-Level Input Voltage (all input pins except RST) (VL = 2.5 V, 3.3 V, or 5 V) | (% of VL) | V <sub>IH</sub> | 70% | -   | -   | ٧     |

| Low-Level Input Voltage (all input pins except RST)                              | (% of VL) | V <sub>IL</sub> | -   | -   | 30% | V     |

| High-Level Input Voltage (RST pin)                                               |           | $V_{IH}$        | 1.2 | -   | -   | V     |

| Low-Level Input Voltage (RST pin)                                                |           | $V_{IL}$        | -   | -   | 0.3 | V     |

| High-Level Output Voltage at I <sub>o</sub> = 2 mA                               | (% of VL) | V <sub>OH</sub> | 80% | -   | -   | V     |

| Low-Level Output Voltage at I <sub>o</sub> = 2 mA                                | (% of VL) | V <sub>OL</sub> | -   | -   | 20% | V     |

| Input Leakage Current                                                            |           | I <sub>in</sub> | -   | -   | ±10 | μΑ    |

| Input Capacitance                                                                |           |                 | -   | 8   | -   | pF    |

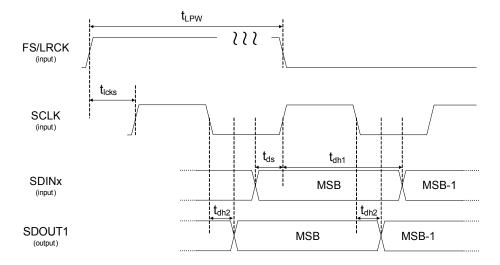

## **SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE**

VA\_SEL = 0 for VA = 3.3 VDC, 1 for VA = 5.0 VDC.

| Parameters                                                         | Symbol            | Min                 | Max                                  | Units          |

|--------------------------------------------------------------------|-------------------|---------------------|--------------------------------------|----------------|

| RST pin Low Pulse Width (Note 25)                                  |                   | 1                   | -                                    | ms             |

| MCLK Frequency (Note 26)                                           |                   | 7.68                | 25.6                                 | MHz            |

| MCLK Duty Cycle                                                    |                   | 45                  | 55                                   | %              |

| SCLK Duty Cycle                                                    |                   | 45                  | 55                                   | %              |

| Input Sample Rate (FS/LRCK pin) Single-Speed Mode                  | F <sub>S</sub>    | 30                  | 50                                   | kHz            |

| Double-Speed Mode                                                  | F <sub>S</sub>    | 60                  | 100                                  | kHz            |

| SCLK Falling Edge to SDOUTx Valid (VL = 1.8 V)                     | t <sub>dh2</sub>  | -                   | 31                                   | ns             |

| SCLK Falling Edge to SDOUTx Valid (VL = 2.5 V)                     | t <sub>dh2</sub>  | -                   | 22                                   | ns             |

| SCLK Falling Edge to SDOUTx Valid (VL = 3.3 V or 5 V)              | t <sub>dh2</sub>  | -                   | 17                                   | ns             |

| TDM Slave Mode                                                     |                   |                     |                                      |                |

| SCLK Frequency (Note 27)                                           |                   | 256x                | 512x                                 | F <sub>S</sub> |

| FS/LRCK High Time Pulse (Note 28)                                  | t <sub>lpw</sub>  | 1/f <sub>SCLK</sub> | (n-1)/f <sub>SCLK</sub><br>(Note 29) | ns             |

| FS/LRCK Rising Edge to SCLK Rising Edge                            | t <sub>lcks</sub> | 5                   | -                                    | ns             |

| SDINx Setup Time Before SCLK Rising Edge                           | t <sub>ds</sub>   | 3                   | -                                    | ns             |

| SDINx Hold Time After SCLK Rising Edge                             | t <sub>dh1</sub>  | 5                   | -                                    | ns             |

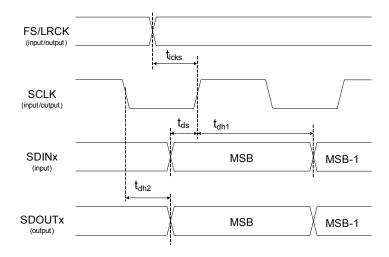

| PCM Slave Mode                                                     |                   |                     |                                      |                |

| SCLK Frequency                                                     |                   | 32x                 | 64x                                  | F <sub>S</sub> |

| FS/LRCK Duty Cycle                                                 |                   | 45                  | 55                                   | %              |

| FS/LRCK Edge to SCLK Rising Edge                                   | t <sub>lcks</sub> | 5                   | -                                    | ns             |

| SDINx Setup Time Before SCLK Rising Edge                           | t <sub>ds</sub>   | 3                   | -                                    | ns             |

| SDINx Hold Time After SCLK Rising Edge                             | t <sub>dh1</sub>  | 5                   | -                                    | ns             |

| PCM Master Mode                                                    |                   |                     |                                      |                |

| SCLK Frequency                                                     |                   | 64x                 | 64x                                  | F <sub>S</sub> |

| FS/LRCK Duty Cycle                                                 |                   | 45                  | 55                                   | %              |

| FS/LRCK Edge to SCLK Rising Edge                                   | t <sub>lcks</sub> | 5                   | -                                    | ns             |

| SDINx Setup Time Before SCLK Rising Edge                           | t <sub>ds</sub>   | 5                   | -                                    | ns             |

| SDINx Hold Time After SCLK Rising Edge (VL = 1.8 V)                | t <sub>dh1</sub>  | 11                  | -                                    | ns             |

| SDINx Hold Time After SCLK Rising Edge (VL = 2.5 V, 3.3 V, or 5 V) | t <sub>dh1</sub>  | 10                  | -                                    | ns             |

#### Notes:

- 25. After applying power to the CS4244, RST should be held low until after the power supplies and MCLK are stable.

- 26. MCLK must be synchronous to and scale with F<sub>S</sub>.

- 27. The SCLK frequency must remain less than or equal to the MCLK frequency. For this reason, SCLK may range from 256x to 512x only in single speed mode. In double speed mode, 256x is the only ratio supported.

- 28. The MSB of CH1 is always aligned with the second SCLK rising edge following FS/LRCK rising edge.

- 29. Where "n" is equal to the MCLK to LRCK ratio (set by the Master Clock Rate register bits), i.e. in 256x mode, n = 256, in 512x mode, n = 512, etc.

Figure 6. TDM Serial Audio Interface Timing

Figure 7. PCM Serial Audio Interface Timing

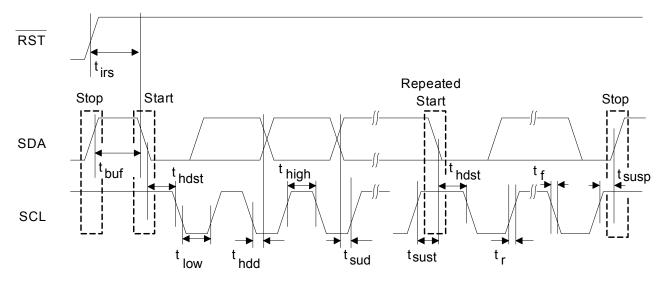

## **SWITCHING SPECIFICATIONS - CONTROL PORT**

Test conditions (unless otherwise specified): Inputs: Logic 0 = GND = 0 V, Logic 1 = VL; SDA load capacitance equal to maximum value of  $C_b$  specified below (Note 30).

| Parameters                                             | Symbol            | Min       | Max | Unit |

|--------------------------------------------------------|-------------------|-----------|-----|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>  | -         | 550 | kHz  |

| RESET Rising Edge to Start                             | t <sub>irs</sub>  | (Note 31) | -   | ns   |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>  | 1.3       | -   | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub> | 0.6       | -   | μs   |

| Clock Low time                                         | t <sub>low</sub>  | 1.3       | -   | μs   |

| Clock High Time                                        | t <sub>high</sub> | 0.6       | -   | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub> | 0.6       | -   | μs   |

| SDA Input Hold Time from SCL Falling (Note 32)         | t <sub>hddi</sub> | 0         | 0.9 | μs   |

| SDA Output Hold Time from SCL Falling                  | t <sub>hddo</sub> | 0.2       | 0.9 | μs   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>  | 100       | -   | ns   |

| Rise Time of SCL and SDA                               | t <sub>r</sub>    | -         | 300 | ns   |

| Fall Time SCL and SDA                                  | t <sub>f</sub>    | -         | 300 | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub> | 0.6       | -   | μs   |

| SDA Bus Load Capacitance                               | C <sub>b</sub>    | -         | 400 | pF   |

| SDA Pull-Up Resistance                                 | R <sub>p</sub>    | 500       | -   | Ω    |

#### Notes:

- 30. All specifications are valid for the signals at the pins of the CS4244 with the specified load capacitance.

- 31. 2 ms + (3000/MCLK). See Section 4.2.1.

- 32. Data must be held for sufficient time to bridge the transition time,  $t_{\rm f}$ , of SCL.

Figure 8. I<sup>2</sup>C Control Port Timing

### 4. APPLICATIONS

### 4.1 Power Supply Decoupling, Grounding, and PCB Layout

As with any high-resolution converter, the CS4244 requires careful attention to power supply and grounding arrangements if its potential performance is to be realized. Figure 2 shows the recommended power arrangements, with VA connected to clean supplies. VDREG, which powers the digital circuitry, is generated internally from an on-chip regulator from the VA supply. The VDREG pin provides a connection point for the decoupling capacitors, as shown in Figure 2.

Extensive use of power and ground planes, ground plane fill in unused areas and surface mount decoupling capacitors are recommended. Decoupling capacitors should be as near to the pins of the CS4244 as possible. The low value ceramic capacitor should be the nearest to the pin and should be mounted on the same side of the board as the CS4244 to minimize inductance effects. All signals, especially clocks, should be kept away from the FILT+, VBIAS, and VQ pins in order to avoid unwanted coupling into the modulators. The FILT+, VBIAS, and VQ decoupling capacitors, particularly the 0.1  $\mu$ F, must be positioned to minimize the electrical path from their respective pins and GND.VA\_SEL

For optimal heat dissipation from the package, it is recommended that the area directly under the device be filled with copper and tied to the ground plane. The use of vias connecting the topside ground to the backside ground is also recommended.

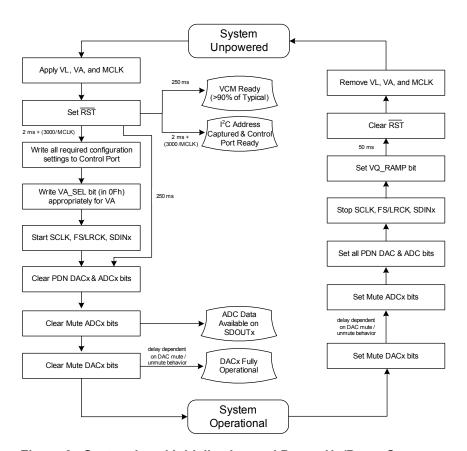

## 4.2 Recommended Power-up & Power-down Sequence

The initialization and Power-Up/Down sequence flow chart is shown in Figure 9. For the CS4244 Reset is defined as all lines held static, RST line is pulled low. Power Down is defined as all lines (excluding MCLK) held static, RST line is high, all PDNx bits are '1'. Running is defined as RST line high, all PDNx bits are '0'.

### 4.2.1 Power-up

The CS4244 enters a reset state upon the initial application of VA and VL. When these power supplies are initially applied to the device, the audio outputs, AOUTxx, are clamped to VQ which is initially low. Additionally, the interpolation and decimation filters, delta-sigma modulators and control port registers are all reset and the internal voltage reference, multi-bit digital-to-analog and analog-to-digital converters and low-pass filters are powered down. The device remains in the reset state until the RST pin is brought high.

Once  $\overline{\text{RST}}$  is brought high, the control port address is latched after 2 ms + (3000/MCLK). Until this latching transition is complete, the device will not respond to I²C reads or writes, but the I²C bus may still be used during this time. Once the latching transition is complete, the address is latched and the control port is accessible. At this point and the desired register settings can be loaded per the interface descriptions detailed in the Section 4.3 I²C Control Port. To ensure specified performance and timing, the VA\_SEL must be set to "0" for VA = 3.3 VDC and "1" for VA = 5.0 VDC before audio output begins.

After the RST pin is brought high and MCLK is applied, the outputs begin to ramp with VQ towards the nominal quiescent voltage. VQ will charge to VA/2 upon initial power up. The time that it takes to charge up to VA/2 is governed by the size of the capacitor attached to the VQ pin. With the capacitor value shown in the typical connection diagram, the charge time will be approximately 250 ms. The gradual voltage ramping allows time for the external DC-blocking capacitors to charge to VQ, effectively blocking the quiescent DC voltage. Once FS/LRCK is valid, MCLK occurrences are counted over one F<sub>S</sub> period to determine the MCLK/F<sub>S</sub> ratio. With MCLK valid and any of the PDNx bits cleared, the internal voltage references will transition to their nominal voltage. Power is applied to the D/A converters and filters, and the analog outputs are un-clamped from the quiescent voltage, VQ. Afterwards, normal operation begins.

#### 4.2.2 Power-down

To prevent audio transients at power-down, the DC-blocking capacitors must fully discharge before turning off the power. In order to do this in a controlled manner, it is recommended that all the converters be muted to start the sequence. Next, set PDNx for all converters to 1 to power them down internally. Then, FS/LRCK and SCLK can be removed if desired. Finally, the "VQ RAMP" bit in the "DAC Control 4" register must be set to '1' for a period of 50 ms before applying reset or removing power or MCLK. During this time, voltage on VQ and the audio outputs discharge gradually to GND. If power is removed before this 50 ms time period has passed, a transient will occur and a slight click or pop may be heard. There is no minimum time for a power cycle. Power may be re-applied at any time.

It is important to note that all clocks should be applied and removed in the order specified in Figure 9. If MCLK is removed or applied before RST has been pulled low, audible pops, clicks and/or distortion can result. If either SCLK or FS/LRCK is removed or applied before all PDNx bits are set to 1, audible pops, clicks and/or distortion can result.

**Note:** Timings are approximate and based upon the nominal value of the passive components specified in the "Typical Connection Diagram" on page 8. See Section 4.6.5.2 for volume ramp behavior.

Figure 9. System Level Initialization and Power-Up/Down Sequence

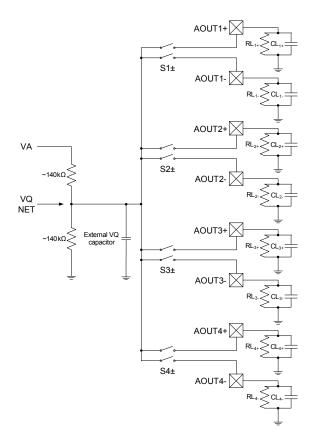

### 4.2.3 DAC DC Loading

Figure 10 shows the analog output configuration during power-up, with the AOUTx $\pm$  pins clamped to VQ to prevent pops and clicks. Thus any DC loads ( $RL_x$ ) on the output pins will be in parallel when the switches are closed. These DC loads will pull the VQ voltage down towards ground. If the parallel combination of all DC loads exceeds the specification shown in the Analog Output Characteristics tables on pages 16

and 17, the VQ voltage will never rise to its minimum operating voltage. If the VQ voltage never rises above this minimum operating voltage, the device will not finish the power-up sequence and normal operation will not begin.

Also note that any AOUT $x\pm$  pin(s) with a DC load must remain powered up (PDN DACx = 0) to keep the VQ net at its nominal voltage during normal operation, otherwise clipping may occur on the outputs.

Note that the load capacitors  $(CL_x)$  are also in parallel during power-up. The amount of total capacitance on the VQ net during power-up will affect the amount of time it takes for the VQ voltage to rise to its nominal operating voltage after VA power is applied. The time period can be calculated using the time constant given by the internal series resistor and the load capacitors.

Figure 10. DAC DC Loading

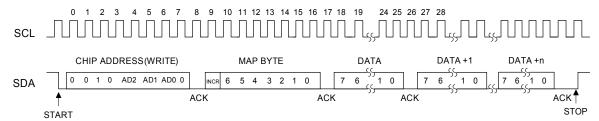

### 4.3 I<sup>2</sup>C Control Port

All device configuration is achieved via the I<sup>2</sup>C control port registers as described in the Switching Specifications - Control Port table. The operation via the control port may be completely asynchronous with respect to the audio sample rates. However, to avoid potential interference problems, the I<sup>2</sup>C pins should remain static if no operation is required. The CS4244 acts as an I<sup>2</sup>C slave device.

SDA is a bidirectional data line. Data is clocked into and out of the device by the clock, SCL. The AD0 and AD1 pins form the two least significant bits of the chip address and should be connected through a resistor to VL or GND as desired. The SDOUT2 pin is used to set the AD2 bit by connecting a resistor from the SDOUT2 pin to VL or to GND. The state of these pins are sensed after the CS4244 is released from reset.

The signal timings for a read and write cycle are shown in Figure 11 and Figure 12. A Start condition is defined as a falling transition of SDA while the clock is high. A Stop condition is a rising transition while the clock is high. All other transitions of SDA occur while the clock is low. The first byte sent to the CS4244 after a Start condition consists of a 7-bit chip address field and a R/W bit (high for a read, low for a write). The upper 4 bits of the 7-bit address field are fixed at 0010. To communicate with a CS4244, the chip address field, which is the first byte sent to the CS4244, should match 0010 followed by the settings of the ADx pins. The eighth bit of the address is the R/W bit. If the operation is a write, the next byte is the Memory Address Pointer (MAP) which selects the register to be read or written. If the operation is a read, the contents of the register pointed to by the MAP will be output. Setting the auto increment bit in MAP allows successive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit. The ACK bit is output from the CS4244 after each input byte is read, and is input to the CS4244 from the microcontroller after each transmitted byte.

Figure 11. Timing, I<sup>2</sup>C Write

Figure 12. Timing, I<sup>2</sup>C Read

Since the read operation can not set the MAP, an aborted write operation is used as a preamble. As shown in Figure 12, the write operation is aborted after the acknowledge for the MAP byte by sending a stop condition. The following pseudocode illustrates an aborted write operation followed by a read operation.

Send start condition.

Send 0010xxx0 (chip address & write operation).

Receive acknowledge bit.

Send MAP byte, auto increment off.

Receive acknowledge bit.

Send stop condition, aborting write.

Send start condition.

Send 0010xxx1 (chip address & read operation).

Receive acknowledge bit.

Receive byte, contents of selected register.

Send acknowledge bit.

Send stop condition.

Setting the auto increment bit in the MAP allows successive reads or writes of consecutive registers. Each byte is separated by an acknowledge bit.