# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## 130-dB, 32-Bit High-Performance DAC with Integrated Headphone Driver and Impedance Detection

| System Features                                                                               | Direct Stream Digital (DSD <sup>®</sup> ) path                                             |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| •                                                                                             |                                                                                            |

| • Enhanced $\Delta\Sigma$ oversampling DAC architecture                                       | <ul> <li>Patented DSD processor</li> </ul>                                                 |

| — 32-bit resolution                                                                           | <ul> <li>On-chip 50-kHz filter to meet Scarlet Book Super</li> </ul>                       |

| <ul> <li>Up to 384-kHz sampling rate</li> </ul>                                               | Audio Compact Disk (SACD) recommendations                                                  |

| <ul> <li>Low clock jitter sensitivity</li> </ul>                                              | <ul> <li>Matched PCM and DSD analog output levels</li> </ul>                               |

| — Auto mute detection                                                                         | <ul> <li>– Nondecimating volume control with 0.5-dB step size<br/>and soft ramp</li> </ul> |

| <ul> <li>Integrated high performance, ground-centered stereo<br/>headphone outputs</li> </ul> | <ul> <li>DSD and Pulse-code modulation (PCM) mixing for<br/>alerts</li> </ul>              |

| <ul> <li>— 130-dB dynamic range (A-weighted)</li> </ul>                                       | — Dedicated DSD and DoP pin interface                                                      |

| <ul> <li>— –108-dB total harmonic distortion + noise (THD+N)</li> </ul>                       | Serial audio input path                                                                    |

| — 110-dB interchannel isolation                                                               |                                                                                            |

| — Headphone power output                                                                      | <ul> <li>Five selectable digital filter responses</li> </ul>                               |

|                                                                                               | <ul> <li>Low-latency mode minimizes pre-echo</li> </ul>                                    |

| $-30$ mW per channel into 32 $\Omega$                                                         | <ul> <li>– 110 dB of stopband attenuation</li> </ul>                                       |

| $-5$ mW per channel into 600 $\Omega$                                                         | <ul> <li>— Supports sample rates from 32 to 384 kHz</li> </ul>                             |

| Headphone detection                                                                           | <ul> <li>— I<sup>2</sup>S, right-justified, left-justified, TDM, and</li> </ul>            |

| <ul> <li>Headphone DC and AC impedance measurement</li> </ul>                                 | DSD-over-PCM (DoP) interface                                                               |

| <ul> <li>Headphone plug-in detection</li> </ul>                                               | <ul> <li>Master or slave operation</li> </ul>                                              |

| <ul> <li>Popguard<sup>®</sup> technology eliminates pop noise</li> </ul>                      | <ul> <li>Volume control with 0.5-dB step size and soft ramp</li> </ul>                     |

| Integrated PLL                                                                                | — 44.1 kHz deemphasis and inverting feature                                                |

| — Support for 11.2896-/22.5792-, 12.288-/24.576-, 9.6-/                                       | Alternate headphone input                                                                  |

| 19.2-, 12-/24-, and 13-/26-MHz system MCLK rates                                              | 40-pin QFN or 42-ball CSP package option                                                   |

| <ul> <li>Reference clock sourced from XTI/MCLK pin</li> </ul>                                 | Applications                                                                               |

| <ul> <li>— System clock output</li> </ul>                                                     |                                                                                            |

| Mono mode support                                                                             | • Smart phones, tablets, portable media players, laptops,                                  |

|                                                                                               | digital headphones, powered speakers, AVR, home                                            |

I<sup>2</sup>C control—up to 1 MHz

theater systems, Blu-ray/DVD/SACD players and pro audio

## **General Description**

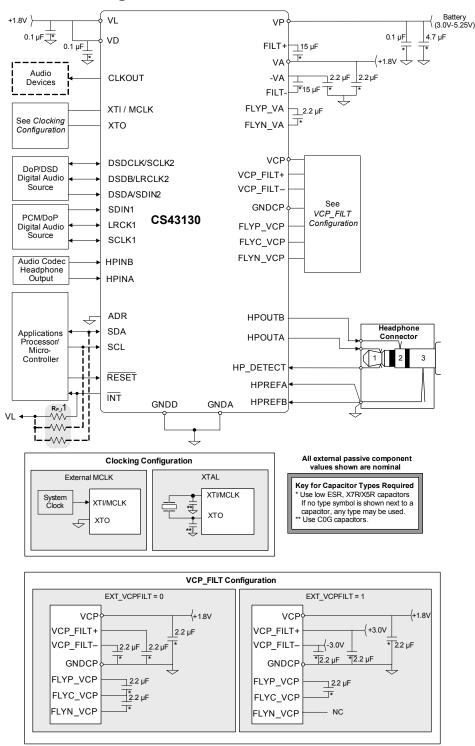

The CS43130 is a high-performance, 32-bit resolution, stereo audio DAC that supports up to 384-kHz sampling frequency with integrated low-noise ground-centered headphone amplifiers. The advanced 32-bit oversampled multibit modulator with mismatch shaping technology eliminates distortion due to on-chip component mismatch. Proprietary digital-interpolation filters support five selectable filter responses with pseudo-linear phase and ultralow latency to minimize pre-echos and ringing artifacts. Other features include volume control with 0.5-dB steps and digital deemphasis for 44.1-kHz sample rate.

The integrated ground-centered stereo headphone amplifiers are capable of delivering more than 30 mW into  $32-\Omega$  load or 5 mW into  $600-\Omega$  load per channel. Proprietary headphone impedance detection enables wide-band impedance detection for further digital post-processing. An internal stereo audio switch with true bypass supports an alternate analog input path for interfacing with external audio sources to minimize the overall bill-of-materials cost and PCB area.

The patented on-chip DSD processor preserves audio integrity by allowing signal processing such as volume control and 50-kHz Scarlet Book recommended filtering to be applied directly to the DSD stream without an intermediate decimation stage. Additional features like volume matching and channel mixing enable seamless transition between DSD and PCM playback paths.

The CS43130 accepts I<sup>2</sup>S, right-justified, left-justified, and TDM-format PCM data at sample rates from 32 to 384 kHz. The industry-standard high-speed I<sup>2</sup>C interface capable of up to 1-MHz operation provides easy configuration control. An integrated PLL allows for maximum clocking flexibility in any system. Popguard<sup>®</sup> technology eliminates output transients upon power-up or power-down events.

The CS43130 is available in a commercial-grade 42-ball WLCSP or 40-pin QFN package for operation from –10°C to +70°C.

## **Table of Contents**

| 1 | Pin Assignments and Descriptions                                                                                                                              |     |

|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| • | 1 1 40 Din OEN (Ton Down Through Dookage View)                                                                                                                | • 7 |

|   | 1.1 40-Pin QFN (Top-Down, Through-Package View)<br>1.2 42-Ball WLCSP (Top-down, Through-Package View)                                                         | . 4 |

|   | 1.2 42-Ball WLCSP (Top-down, Through-Package view)                                                                                                            | . ວ |

|   | 1.3 Pin Descriptions                                                                                                                                          | . 6 |

|   | 1.3 Pin Descriptions                                                                                                                                          | . 8 |

| 2 | Typical Connection Diagram                                                                                                                                    | 10  |

| 3 | Characteristics and Specifications                                                                                                                            | 11  |

|   | Table 3-1 Parameter Definitions                                                                                                                               | 11  |

|   | Table 3-1. Parameter Definitions         Table 3-2. Recommended Operating Conditions                                                                          | 11  |

|   | Table 3-3. Absolute Maximum Ratings         Table 3-4. Analog Output Characteristics (HV_EN = 1)         Table 3-5. Analog Output Characteristics (HV_EN = 0) | 12  |

|   | Table 3.4 Analog Output Characteristics (H)/ EN = 1)                                                                                                          | 12  |

|   | Table 3.5 Analog Output Characteristics $(HV = I)$                                                                                                            | 12  |

|   | Table 3-5. Analog Output Characteristics ( $\Pi V \_ E N = 0$ )                                                                                               | 13  |

|   | Table 3-6.    Headphone Load Measurement                                                                                                                      | 15  |

|   | Table 3-7. Alternate Headphone Path         Table 3-8. Combined DAC Digital, On-Chip Analog and                                                               | 16  |

|   | Table 3-8. Combined DAC Digital, On-Chip Analog and                                                                                                           |     |

|   | HPOUTx Filter Characteristics                                                                                                                                 | 16  |

|   | HPOUTx Filter Characteristics<br>Table 3-9. DAC High-Pass Filter (HPF) Characteristics<br>Table 3-10. DSD Combined Digital and On-Chip Analog                 | 18  |

|   | Table 3-10. DSD Combined Digital and On-Chip Analog                                                                                                           |     |

|   | Filter Response                                                                                                                                               | 18  |

|   | Table 3-11. Digital Interface Specifications and Characteristics                                                                                              | 19  |

|   | Table 3-12. CLKOUT Characteristics                                                                                                                            | 19  |

|   | Table 3-13. PLL Characteristics                                                                                                                               |     |

|   | Table 2-10. T LL Onaracteristics                                                                                                                              | 20  |

|   | Table 3-14. Crystal Characteristics         Table 3-15. Power-Supply Rejection Ratio (PSRR)                                                                   | 20  |

|   | Characteristics                                                                                                                                               | ~~  |

|   | Characteristics                                                                                                                                               | 20  |

|   | Table 3-16. DC Characteristics                                                                                                                                | 20  |

|   | Table 3-17. Power Consumption                                                                                                                                 |     |

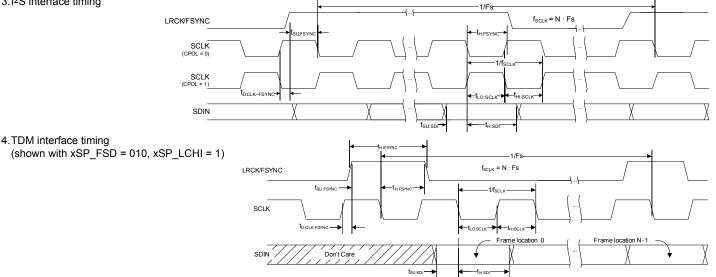

|   | Table 3-18.         Serial-Port Interface Characteristics                                                                                                     | 21  |

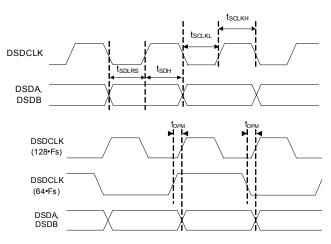

|   | Table 3-19. DSD Switching Characteristic                                                                                                                      | 22  |

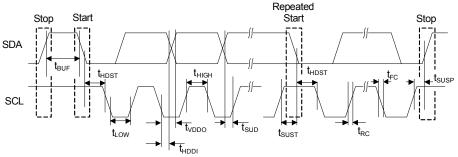

|   | Table 3-19. DSD Switching Characteristic         Table 3-20. I <sup>2</sup> C Slave Port Characteristics                                                      | 23  |

| 4 | Functional Description                                                                                                                                        | 24  |

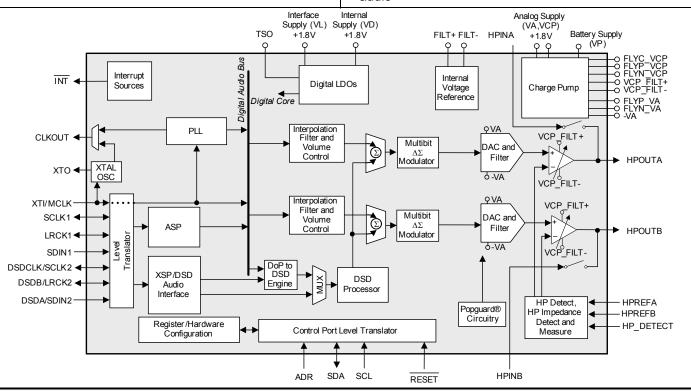

|   | 4.1 Overview                                                                                                                                                  |     |

|   | 4.2 Analog Outputs                                                                                                                                            |     |

|   | 4.3 Class H Amplifier Output                                                                                                                                  |     |

|   | 4 4 Alternate Headphone Inputs                                                                                                                                | 32  |

|   | <ul><li>4.4 Alternate Headphone Inputs</li><li>4.5 Headphone Presence Detect and Output Load Detection</li></ul>                                              | 22  |

|   | 4.6 Clocking Architecture                                                                                                                                     | 26  |

|   | 4.6 Clocking Architecture                                                                                                                                     | 20  |

|   | 4.7 Clock Oulput and Fractional-N PLL                                                                                                                         | 39  |

|   | 4.8 Filtering Options                                                                                                                                         | 41  |

|   | 4.9 Audio Šerial Port (ASP)                                                                                                                                   | 42  |

|   | 4.10 DSD Interface                                                                                                                                            | 50  |

|   | 4.11 DSD and PCM Mixing                                                                                                                                       | 52  |

|   | 4.12 Standard Interrupts                                                                                                                                      | 52  |

|   | 4.13 Control Port Operation                                                                                                                                   | 53  |

|   | · · · · · · · · · · · · · · · · · · ·                                                                                                                         |     |

| 5 Applications                                      | . 56 |

|-----------------------------------------------------|------|

| 5.1 PLL Clocking                                    | 56   |

| 5.2 Power Sequencing                                | 56   |

| 5.2 Crustel Tuning                                  | . 50 |

| 5.3 Crystal Tuning                                  | . 30 |

| 5.4 Alert Mixing Shutdown                           | . 5/ |

| 5.5 Enable/Disable Nonoversampling Filter           | . 57 |

| 5.6 Enable/Disable Alternate Headphone Path (HPINx) | . 58 |

| 5.7 Headphone Power Down Sequences                  | . 59 |

| 5.8 Headphone Power-Up Initialization               | . 61 |

| 5.9 Headphone Power-Un Sequence                     | 62   |

| 5.10 Example Sequences                              | . 64 |

| 5.10 Example Sequences                              | 82   |

| 6 Register Quick Reference                          | 91   |

| 7 Register Descriptions                             | 05   |

| 7.1 Global Registers                                |      |

|                                                     |      |

| 7.2 PLL Registers                                   | . 90 |

| 7.3 ASP and XSP Registers                           | 100  |

| 7.4 DSD Registers 7.5 Headphone and PCM Registers   | 106  |

| 7.5 Headphone and PCM Registers                     | 109  |

| 7.6 Interrupt Status and Mask Registers             | 115  |

| 8 PCB Layout Considerations                         | 121  |

| 8.1 Power Supply                                    | 121  |

| 8.2 Grounding                                       | 121  |

| 8.3 HPREFA and HPREFB Routing                       | 121  |

| 8.4 QFN Thermal Pad                                 | 121  |

| 9 Performance Plots                                 | 122  |

| 9.1 Digital Filter Response                         | 122  |

| 10 Package Dimensions                               |      |

| 10.1 40-Pin QFN Package Dimensions                  | 134  |

| 10.1 40-FILL QEN FACKAGE DIMENSIONS                 | 104  |

| 10.2 42-Ball WLCSP Package Dimensions               | 135  |

| 11 Thermal Characteristics                          |      |

| 12 Ordering Information                             | 136  |

| 13 References                                       | 136  |

| 14 Revision History                                 | 136  |

|                                                     |      |

## 1 Pin Assignments and Descriptions

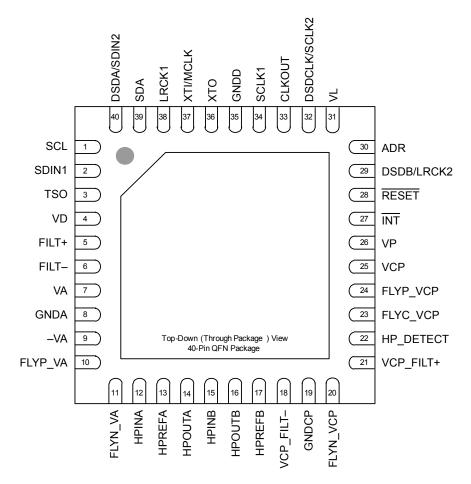

## 1.1 40-Pin QFN (Top-Down, Through-Package View)

Figure 1-1. Top-Down (Through-Package) View—QFN 40-Pin Diagram

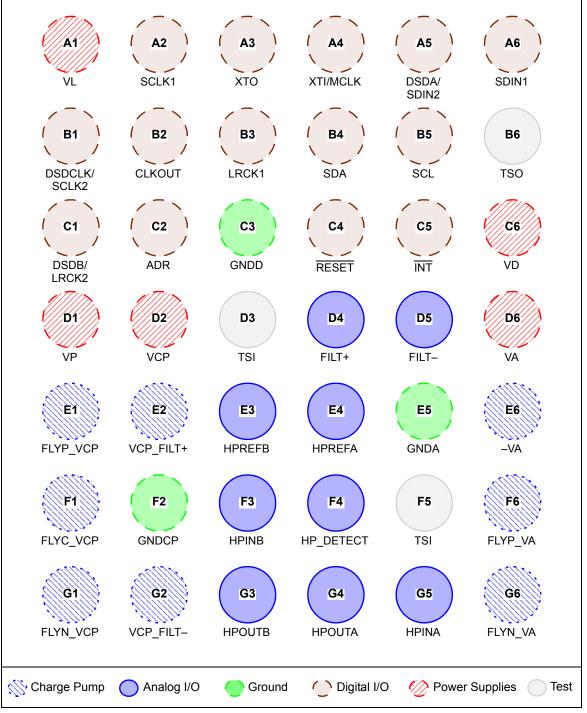

## 1.2 42-Ball WLCSP (Top-down, Through-Package View)

Figure 1-2. Top-Down (Through-Package) View—42-Ball WLCSP Package

## 1.3 Pin Descriptions

#### Table 1-1. Pin Descriptions

| Pin Name               | QFN<br>Pin # | WLCSP<br>Ball | Power<br>Supply |     | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Internal<br>Connection | Digital I/O<br>Driver        | Digital I/O<br>Receiver        |

|------------------------|--------------|---------------|-----------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------|--------------------------------|

|                        |              |               |                 |     | Digital I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |                              |                                |

| ADR                    | 30           | C2            | VL              | Ι   | Address Bit (I <sup>2</sup> C). In I <sup>2</sup> C Mode, ADR is a chip address pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                      | _                            | _                              |

| CLKOUT                 | 33           | B2            | VL              |     | <b>CLK Output.</b> Single-ended clock output sourced from PLL or buffered crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Weak<br>pull-down      | CMOS<br>output               | —                              |

| SCLK1                  | 34           | A2            | VL              | I/O | Serial Audio Input Bit Clock 1. Serial bit clock for audio data on the SDIN pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| LRCK1                  | 38           | В3            | VL              | I/O | Serial Audio Input Left/Right Clock. Word-rate clock for the audio data on the SDIN pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| SDIN1                  | 2            | A6            | VL              | Ι   | Serial Audio Input Data Port. Audio data serial input pin 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Weak<br>pull-down      | _                            | Hysteresis<br>on CMOS<br>input |

| DSDA/<br>SDIN2         | 40           | A5            | VL              | I   | <b>DSD Data Input A/Serial Data In 2.</b> DSD audio or PCM audio data serial input pin 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Weak<br>pull-down      | _                            | Hysteresis<br>on CMOS<br>input |

| DSDB/<br>LRCK2         | 29           | C1            | VL              |     | <b>DSD Data Input B/Serial Audio Input Left/Right Clock 2.</b> DSD audio data serial input pin or word rate clock for the audio data on the SDIN2 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| DSDCLK/<br>SCLK2       | 32           | B1            | VL              | I/O | <b>DSD Clock Input/Serial Audio Input Bit Clock 2.</b> DSD clock input. Serial bit clock for audio data on the SDIN2 pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Weak<br>pull-down      | CMOS<br>output               | Hysteresis<br>on CMOS<br>input |

| INT                    | 27           | C5            | VP              | 0   | <b>Interrupt.</b> When pulled up, works as system interrupt pin. Open drain, active low programmable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                      | CMOS<br>open-drain<br>output | _                              |

| RESET                  | 28           | C4            | VP              | Ι   | System Reset. The device enters system reset when enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | _                      | _                            | Hysteresis<br>on CMOS<br>input |

| SDA                    | 39           | B4            | VL              | I/O | Serial Control Data I/O (I <sup>2</sup> C). In I <sup>2</sup> C Mode, SDA is the control I/O data line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _                      | CMOS<br>open-drain<br>output | Hysteresis<br>on CMOS<br>input |

| SCL                    | 1            | B5            | VL              | I   | <b>Software Clock (I<sup>2</sup>C).</b> Serial control interface clock used to clock control data bits into and out of the CS43130.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                      | _                            | Hysteresis<br>on CMOS<br>input |

| XTI/MCLK               | 37           | A4            | VL              | I   | <b>Crystal/Oscillator Input/MCLK In.</b> Crystal or digital clock input for the master clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Weak<br>pull-down      | —                            | Hysteresis<br>on CMOS<br>input |

| XTO                    | 36           | A3            | VL              | 0   | Crystal/Oscillator Output. Crystal output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Weak<br>pull-down      | CMOS<br>output               | —                              |

|                        |              |               |                 |     | Analog I/O 🔵                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                        |                              |                                |

| FILT+                  | 5            | D4            | VA              | 0   | Positive/Negative Voltage Reference. Positive/negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                      | —                            | _                              |

| FILT-<br>HP_<br>DETECT | 6<br>22      | D5<br>F4      | VP              | I   | reference voltage for DAC.<br><b>Headphone Detect.</b> Can be configured to be debounced on<br>unplugged and plugged events before it is presented as a<br>parietor protocological details of the second debounced on the second debounced debounced debounced on the second debounced debo | _                      | Hi-Z                         | _                              |

| HPINB                  | 15           | F3            | VCP             |     | noninterrupt status bit (HPDETECT).<br>Headphone Audio Input. For interfacing low power audio source,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Weak                   |                              |                                |

| HPINA                  | 12           | G5            | FILT±           |     | an alternate analog input path for the headphone output. Refer to<br>analog specification table for full-scale input level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | pull-down              |                              |                                |

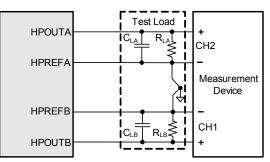

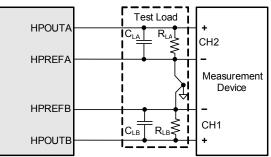

| HPOUTB<br>HPOUTA       | 16<br>14     | G3<br>G4      | VCP_<br>FILT±   | 0   | Headphone Audio Output. Refer to analog specification table for full-scale output level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                      | _                            |                                |

| HPREFB<br>HPREFA       | 17<br>13     | E3<br>E4      | VCP_<br>FILT±   | I   | Headphone Output Reference. Reference for headphone amplifier and detect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | _                      | _                            | _                              |

|                        |              |               |                 |     | Power Supplies 🥢                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                        |                              |                                |

| VL                     | 31           | A1            | N/A             | - 1 | Logic Power. Input/Output power supply, typically +1.8 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                        |                              |                                |

| Pin Name  | QFN<br>Pin # | WLCSP<br>Ball | Power<br>Supply         |     | Pin Description                                                                                                                                                                           | Internal<br>Connection | Digital I/O<br>Driver | Digital I/C<br>Receiver |

|-----------|--------------|---------------|-------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----------------------|-------------------------|

| VD        | 4            | C6            | N/A                     | I   | <b>Internal Digital Power.</b> Internal digital power supply, typically +1.8 V.                                                                                                           |                        |                       |                         |

| VA        | 7            | D6            | N/A                     | Ι   | Analog Power. Power supply for the internal analog section.                                                                                                                               | —                      | —                     | _                       |

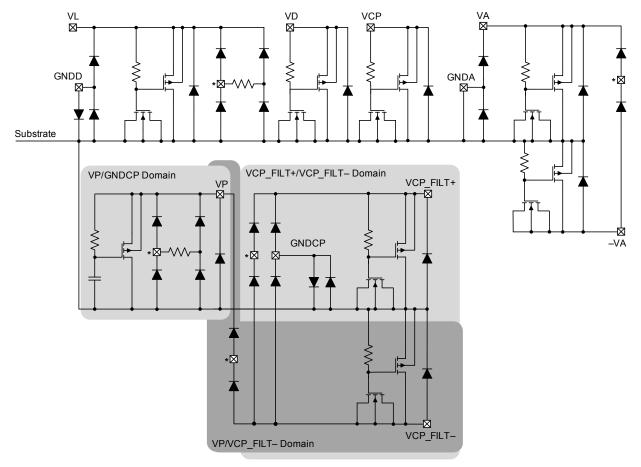

| VCP       | 25           | D2            | N/A                     | I   | <b>Charge Pump Supply.</b> Provides charge pump voltage to the headphone Class H analog output circuit.                                                                                   | _                      | _                     |                         |

| VP        | 26           | D1            | N/A                     | Ι   | <b>Battery supply</b> . Provides voltage to the headphone Class H circuit.                                                                                                                | _                      | _                     |                         |

|           |              |               |                         |     | Ground 🔴                                                                                                                                                                                  |                        |                       |                         |

| GNDD      | 35           | C3            | N/A                     | Ι   | <b>Digital and I/O Ground.</b> Ground for the I/O and core logic. GNDA, GNDCP, and GNDD must be connected to a common ground area under the chip.                                         | _                      | _                     | _                       |