Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

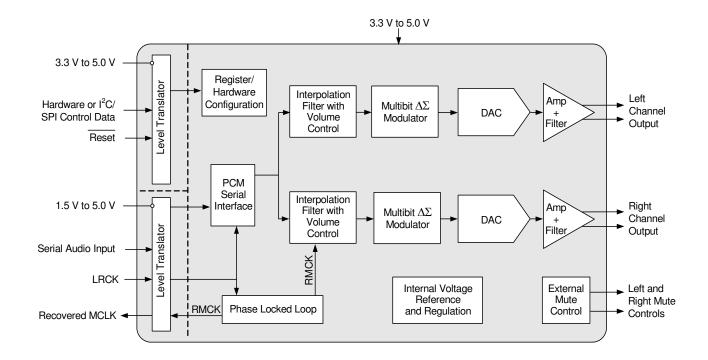

# 192-kHz Stereo DAC with Integrated PLL

#### **Features**

- Advanced multibit delta-sigma architecture

- ♦ 109-dB dynamic range

- ◆ -91-dB THD+N

- ♦ 24-bit conversion

- ♦ Supports audio sample rates up to 192 kHz

- Low-latency digital filtering

- Single-ended or differential analog output architecture

- Integrated PLL locks to incoming left-right clock

- Eliminates the need for external masterclock routing

- Reduces interference and jitter sensitivity

- No external loop filter components required

- Automatic sample-rate range detection

- Popguard<sup>®</sup> technology for control of clicks and pops

- Hardware popguard disable for fast startups

- ◆ Supports all standard serial audio formats including time-division multiplexed (TDM)

- ♦ +1.5- to 5.0-V logic supplies for serial port

- ♦ +3.3- to 5.0-V control port interface

#### **Control Port Mode Features**

- ♦ SPI™ and I²C Modes

- ♦ ATAPI mixing

- ♦ Mute control for individual channels

- Digital volume control with soft ramp

- 127.5-dB attenuation

- 0.5-dB step size

- Zero-crossing click-free transitions

## **Description**

The CS4350 is a complete stereo digital-to-analog system including PLL-based master clock derivation, digital interpolation, 5th-order multibit delta-sigma digital-to-analog conversion, digital de-emphasis, volume control, channel mixing, and analog filtering. The advantages of this architecture include ideal differential linearity, no distortion mechanisms due to resistor matching errors, no linearity drift over time and temperature, high tolerance to clock jitter, and a minimal set of external components.

The CS4350 supports all standard digital audio interface formats, including TDM.

The CS4350 is available in a 24-pin QFN package in Commercial grade (-40° to +85°C).

The CS4350 is available in a 24-pin TSSOP package in both Commercial (-40° to +85°C) and Automotive grades (-40° to +105°C).

The CDB4350 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please refer to "Ordering Information" on page 40 for complete ordering information.

These features are ideal for cost-sensitive, two-channel audio systems, including DVD players and recorders, settop boxes, digital TVs, mini-component systems, mixing consoles and automotive audio systems.

## **TABLE OF CONTENTS**

| 1 PIN DESCRIPTION                                                      | 6    |

|------------------------------------------------------------------------|------|

| 1.1 TSSOP Pinout                                                       | 6    |

| 1.2 QFN Pinout                                                         |      |

| 2 CHARACTERISTICS AND SPECIFICATIONS                                   | 8    |

| 2.1 Recommended Operating Conditions                                   | 8    |

| 2.2 Absolute Maximum Ratings                                           |      |

| 2.3 DAC Analog Characteristics - Commercial (-CZZ,-CNZ)                | 9    |

| 2.4 DAC Analog Characteristics - Automotive (-DZZ)                     |      |

| 2.5 Combined Interpolation and On-Chip Analog Filter Response          | . 12 |

| 2.6 Switching Specifications - Serial Audio Interface                  |      |

| 2.7 Switching Characteristics - Control Port - I <sup>2</sup> C Format | . 14 |

| 2.8 Switching Characteristics - Control Port - SPI Format              | . 15 |

| 2.9 Digital Characteristics                                            | . 16 |

| 2.10 Power and Thermal Characteristics                                 | . 16 |

| 3 TYPICAL CONNECTION DIAGRAM                                           | . 17 |

| 4 APPLICATIONS                                                         |      |

| 4.1 Sample Rate Range and Oversampling Mode Detect                     | . 18 |

| 4.1.1 Sample Rate Auto-Detect                                          | . 18 |

| 4.2 System Clocking                                                    | . 18 |

| 4.2.1 Recovered Master Clock (RMCK)                                    | . 18 |

| 4.3 Digital Interface Format                                           |      |

| 4.3.1 Time-Division Multiplex (TDM) Mode                               | . 20 |

| 4.4 De-Emphasis                                                        | . 21 |

| 4.5 Mute Control                                                       | . 21 |

| 4.6 Recommended Power-Up Sequence                                      | . 21 |

| 4.6.1 Stand-Alone Mode                                                 | . 21 |

| 4.6.2 Control Port Mode                                                | . 22 |

| 4.7 Popguard Transient Control                                         | . 22 |

| 4.7.1 Power-Up                                                         | . 22 |

| 4.7.2 Power-Down                                                       | . 22 |

| 4.7.3 Discharge Time                                                   | . 22 |

| 4.8 Analog Output and Filtering                                        | . 23 |

| 4.9 Grounding and Power Supply Arrangements                            | . 23 |

| 4.9.1 Capacitor Placement                                              |      |

| 5 STAND-ALONE OPERATION                                                | . 24 |

| 5.1 Serial Port Format Selection                                       | . 24 |

| 5.2 De-Emphasis Control                                                | . 24 |

| 5.3 Popguard Transient Control                                         | . 24 |

| 6 CONTROL PORT OPERATION                                               | . 24 |

| 6.1 MAP Auto Increment                                                 | . 24 |

| 6.2 I <sup>2</sup> C Mode                                              |      |

| 6.2.1 I <sup>2</sup> C Write                                           | . 25 |

| 6.2.2 I <sup>2</sup> C Read                                            | . 25 |

| 6.3 SPI Mode                                                           | . 26 |

| 6.3.1 SPI Write                                                        | . 26 |

| 6.3.2 SPI Read                                                         |      |

| 6.4 Memory Address Pointer (MAP)                                       |      |

| 6.4.1 INCR (Auto Map Increment Enable)                                 |      |

| 6.4.2 MAP (Memory Address Pointer)                                     |      |

| 7 REGISTER QUICK REFERENCE                                             |      |

| 8 REGISTER DESCRIPTION                                                 |      |

| 8.1 Device and Revision ID - Register 01h                              | . 29 |

| 8.2 Mode Control - Register 02h                                     | 29 |

|---------------------------------------------------------------------|----|

| 8.2.1 Digital Interface Format (DIF[2:0]) Bits 6-4                  | 29 |

| 8.2.2 De-Emphasis Control (DEM[1:0]) Bits 3-2                       |    |

| 8.2.3 Functional Mode (FM[1:0]) Bits 1-0                            | 30 |

| 8.3 Volume Mixing and Inversion Control - Register 03h              | 30 |

| 8.3.1 Channel A Volume = Channel B Volume (VOLB=A) Bit 7            | 30 |

| 8.3.2 Invert Signal Polarity (INVERT_A) Bit 6                       |    |

| 8.3.3 Invert Signal Polarity (INVERT_B) Bit 5                       | 31 |

| 8.3.4 ATAPI Channel Mixing and Muting (ATAPI[3:0]) Bits 3-0         |    |

| 8.4 Mute Control - Register 04h                                     | 32 |

| 8.4.1 Auto-Mute (AMUTE) Bit 7                                       | 32 |

| 8.4.2 AMUTEC = BMUTEC (MUTEC A=B) Bit 5                             | 32 |

| 8.4.3 Channel A Mute (MUTE_A) Bit 4 & Channel B Mute (MUTE_B) Bit 3 | 32 |

| 8.5 Channel A & B Volume Control - Register 05h & 06h               | 33 |

| 8.6 Ramp and Filter Control - Register 07h                          | 33 |

| 8.6.1 Soft Ramp and Zero Cross Control (SZC[1:0]) Bits 7-6          | 33 |

| 8.6.2 Soft Volume Ramp-Up after Error (RMP_UP) Bit 5                | 34 |

| 8.6.3 Soft Ramp-Down before Filter Mode Change (RMP_DN) Bit 4       |    |

| 8.6.4 Interpolation Filter Select (FILT_SEL) Bit 2                  |    |

| 8.7 Misc. Control - Register 08h                                    |    |

| 8.7.1 Power Down (PDN) Bit 7                                        |    |

| 8.7.2 Freeze Controls (FREEZE) Bit 5                                | 35 |

| 8.7.3 Popguard Enable (POPG_EN) Bit 4                               |    |

| 8.7.4 RMCK control (RMCK_CTRL[1:0]) Bits 3:2                        |    |

| 8.7.5 RMCK Ratio Select (R_SELECT[1:0]) Bits 2:1                    |    |

| 9 FILTER PLOTS                                                      |    |

| 10 PARAMETER DEFINITIONS                                            |    |

| 11 PACKAGE DIMENSIONS                                               |    |

| 11.1 24L TSSOP (4.4 mm body) Package Drawing                        |    |

| 11.2 24L QFN (4.00 mm BODY) PACKAGE DRAWING                         | 39 |

| 12 THERMAL CHARACTERISTICS                                          |    |

| 12.1 QFN Thermal Pad                                                |    |

| 13 ORDERING INFORMATION                                             | _  |

| 14 REVISION HISTORY                                                 | 41 |

## **LIST OF FIGURES**

| Figure 1. Equivalent Output Load                                            | 11 |

|-----------------------------------------------------------------------------|----|

| Figure 2. Maximum Loading                                                   |    |

| Figure 3. THD+N vs Output Amplitude for VA = 5.0 V                          |    |

| Figure 4. THD+N vs Output Amplitude for VA = 3.3 V                          |    |

| Figure 5. THD+N vs Output Amplitude for VA = 3.14 V                         |    |

| Figure 6. Serial Port Timing, Non-TDM Mode                                  |    |

| Figure 7. Serial Port Timing, TDM Mode                                      |    |

| Figure 8. Control Port Timing - I <sup>2</sup> C Format                     |    |

| Figure 9. Control Port Timing - SPI Mode                                    |    |

| Figure 10. Typical Connection Diagram                                       |    |

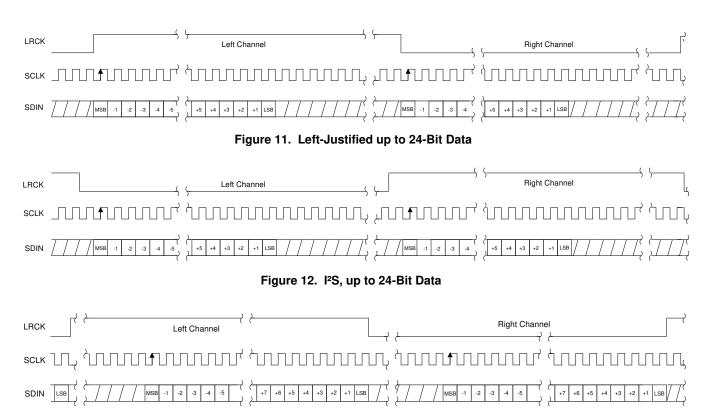

| Figure 11. Left-Justified up to 24-Bit Data                                 |    |

| Figure 12. I <sup>2</sup> S, up to 24-Bit Data                              |    |

| Figure 13. Right-Justified Data                                             |    |

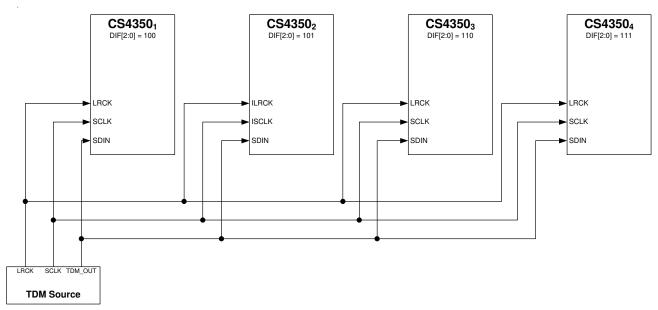

| Figure 14. TDM Mode Connection Diagram                                      |    |

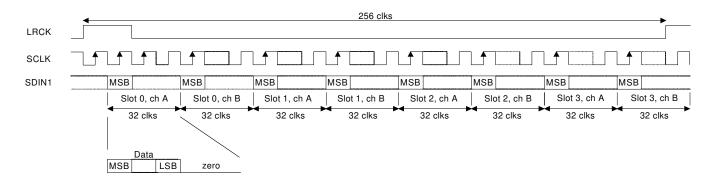

| Figure 15. TDM Mode Timing                                                  |    |

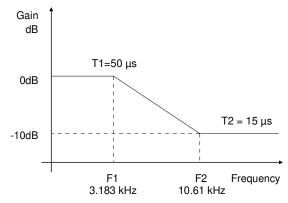

| Figure 16. De-Emphasis Curve                                                |    |

| Figure 17. Differential to Single-Ended Output Filter                       |    |

| Figure 18. Passive Single-Ended Output Filter                               |    |

| Figure 19. Control Port Timing, I <sup>2</sup> C Mode                       |    |

| Figure 20. Control Port Timing, SPI Mode                                    |    |

| Figure 21. De-Emphasis Curve                                                |    |

| Figure 22. ATAPI Block Diagram                                              |    |

| Figure 23. Stopband Rejection (fast), all Modes                             |    |

| Figure 24. Stopband Rejection (slow), all Modes                             |    |

| Figure 25. Single-Speed (fast) Passband Detail                              |    |

| Figure 26. Single-Speed (slow) Passband Detail                              | 36 |

| Figure 27. Double-Speed (fast) Passband Detail                              | 36 |

| Figure 28. Double-Speed (slow) Passband Detail                              | 36 |

| Figure 29. Quad-Speed (fast) Passband Detail                                | 37 |

| Figure 30. Quad-Speed (slow) Passband Detail                                | 37 |

| LIST OF TABLES                                                              |    |

| Table 1. Recommended Operating Conditions                                   | 8  |

| Table 2. Absolute Maximum Ratings                                           |    |

| Table 3. DAC Analog Characteristics - Commercial (-CZZ,-CNZ)                |    |

| Table 4. DAC Analog Characteristics - Automotive (-DZZ)                     |    |

| Table 5. Combined Interpolation and On-Chip Analog Filter Response          |    |

| Table 6. Switching Specifications - Serial Audio Interface                  |    |

| Table 7. Switching Characteristics - Control Port - I <sup>2</sup> C Format |    |

| Table 8. Switching Characteristics - Control Port - SPI Format              |    |

| Table 9. Digital Characteristics                                            |    |

| Table 10. Power and Thermal Characteristics                                 |    |

| Table 11. CS4350 Auto-Detect                                                |    |

| Table 12. Digital Interface Format - Stand-Alone Mode                       |    |

| Table 13. Digital Interface Formats                                         |    |

| Table 14. ATAPI Decode                                                      |    |

| Table 15. Example Digital Volume Settings                                   |    |

| Table 16. Thermal Characteristics                                           |    |

|                                                                             |    |

## 1 PIN DESCRIPTION

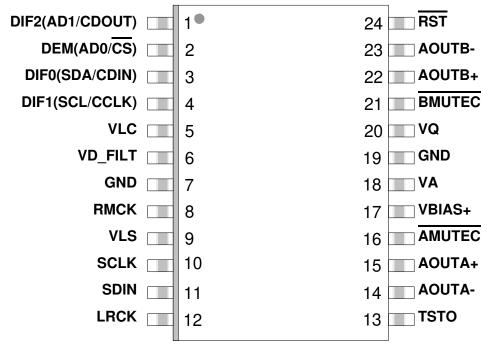

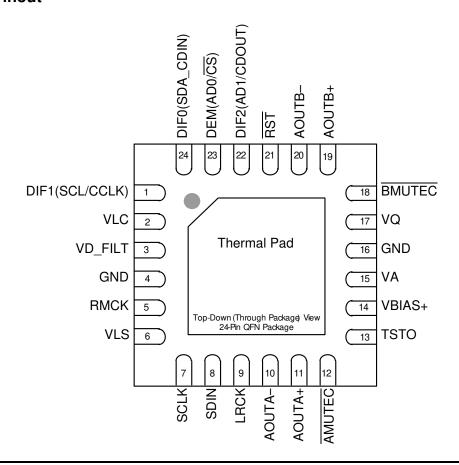

#### 1.1 TSSOP Pinout

#### 1.2 QFN Pinout

| Pin Name             | TSSOP<br>#        | QFN<br>#         | Pin Description                                                                                                                                                                  |

|----------------------|-------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VLC                  | 5                 | 2                | Control Interface Power (Input) - Positive power for the hardware/software control interface                                                                                     |

| VD_FILT              | 6                 | 3                | Regulator Voltage (Output) - Filter connection for internal voltage regulator                                                                                                    |

| GND                  | 7, 19             | 4,16             | Ground (Input) - Ground reference                                                                                                                                                |

| RMCK                 | 8                 | 5                | Recovered Master Clock (Output) - Outputs a master clock derived from LRCK                                                                                                       |

| VLS                  | 9                 | 6                | Serial Audio Interface Power (Input) - Positive power for the serial audio interface                                                                                             |

| SCLK                 | 10                | 7                | Serial Clock (Input) - Serial bit-clock for the serial audio interface                                                                                                           |

| SDIN                 | 11                | 8                | Serial Audio Data Input (Input) - Input for two's complement serial audio data                                                                                                   |

| LRCK                 | 12                | 9                | <b>Left/Right Clock</b> ( <i>Input</i> ) - Determines which channel, Left or Right, is currently active on the serial audio data line                                            |

| TSTO                 | 13                | 13               | Test Output - These pins need to be floating and not connected to any trace or plane.                                                                                            |

| AOUTA+,-<br>AOUTB+,- | 14, 15,<br>22, 23 | 11, 10<br>19, 20 | <b>Differential Analog Outputs</b> ( <i>Output</i> ) - The full-scale differential output level is specified in "DAC Analog Characteristics - Commercial (-CZZ,-CNZ)" on page 9. |

| AMUTEC<br>BMUTEC     | 16, 21            | 12<br>18         | Mute Control (Output) - Control signals for optional mute circuit.                                                                                                               |

| VBIAS+               | 17                | 14               | Positive Voltage Reference (Output) - Positive reference voltage for the internal DAC                                                                                            |

| VA                   | 18                | 15               | Analog Power (Input) - Positive power supply for the analog section                                                                                                              |

| VQ                   | 20                | 17               | Quiescent Voltage (Output) - Filter connection for internal quiescent voltage                                                                                                    |

| RST                  | 24                | 21               | <b>Reset</b> ( <i>Input</i> ) - When pulled low, device will power down and reset all internal registers to their default settings.                                              |

| <b>Control Port</b>  | Definition        | ns               |                                                                                                                                                                                  |

| AD1/CDOUT            | 1                 | 22               | Address Bit 1/Serial Control Data Out (I/O) - Chip address bit 1 in I <sup>2</sup> C Mode or data output in SPI Mode                                                             |

| AD0/CS               | 2                 | 23               | Address Bit 0/Chip Select (Input) - Chip address bit 0 in I2C Mode or Chip Select in SPI Mode                                                                                    |

| SDA/CDIN             | 3                 | 24               | Serial Control Data In (I/O) - Input/Output for I2C data. Input for SPI data                                                                                                     |

| SCL/CCLK             | 4                 | 1                | Serial Control Port Clock (Input) - Serial clock for the control port interface                                                                                                  |

| Stand-Alone          | Definition        | ns               |                                                                                                                                                                                  |

| DIF0                 | 1                 | 24               | Digital Interface Format (Input) - Defines the required relationship between the Left Right Clock, Serial                                                                        |

| DIF1                 | 3                 | 1                | Clock, and Serial Audio Data                                                                                                                                                     |

| DIF2<br>DEM          | 2                 | 22               | <b>De-emphasis</b> ( <i>Input</i> ) - Selects the standard 15 $\mu$ s/50 $\mu$ s digital de-emphasis filter response for 44.1 kHz sample rates                                   |

| Thermal Pad          | (QFN pa           | ckage c          | <u>·</u>                                                                                                                                                                         |

| Thermal Pad          | n/a               |                  | Thermal relief pad for optimized heat dissipation. See "QFN Thermal Pad" on page 40 for more information.                                                                        |

## **2 CHARACTERISTICS AND SPECIFICATIONS**

## 2.1 Recommended Operating Conditions

GND = 0 V; all voltages with respect to ground.

**Table 1. Recommended Operating Conditions**

|                                               | Parameters                           | Symbol | Min  | Тур | Max  | Units |

|-----------------------------------------------|--------------------------------------|--------|------|-----|------|-------|

| DC Power Supply                               | Analog power                         | VA     | 4.75 | 5.0 | 5.25 | V     |

|                                               |                                      |        | 3.14 | 3.3 | 3.46 | V     |

|                                               | Serial Audio Interface power(Note 1) | VLS    | 1.35 | 3.3 | 5.25 | V     |

|                                               | Control Interface power              | VLC    | 3.14 | 3.3 | 5.25 | V     |

| Ambient Operating Temperature (Power Applied) |                                      |        |      |     |      |       |

|                                               | Commercial (-CZZ,-CNZ)               | $T_A$  | -40  | -   | +85  | °C    |

|                                               | Automotive (-DZZ)                    | $T_A$  | -40  | -   | +105 | °C    |

Notes: 1. RMCK output frequency is dependent on VLS.

See Table 6 for supported RMCK frequencies with respect to VLS.

## 2.2 Absolute Maximum Ratings

GND = 0 V; all voltages with respect to ground (Note 2).

**Table 2. Absolute Maximum Ratings**

| P                          | arameters                    | Symbol             | Min  | Max      | Units |

|----------------------------|------------------------------|--------------------|------|----------|-------|

| DC Power Supply            | Analog power                 | VA                 | -0.3 | 6.0      | V     |

|                            | Serial Audio Interface power | VLS                | -0.3 | 6.0      | V     |

|                            | Control Interface power      | VLC                | -0.3 | 6.0      | V     |

| Input Current              | (Note 3)                     | I <sub>in</sub>    | -    | ±10      | mA    |

| Digital Input Voltage      | Serial Audio Interface       | V <sub>IN-LS</sub> | -0.3 | VLS+ 0.4 | V     |

| Control Interface          |                              | $V_{IN-LC}$        | -0.3 | VLC+ 0.4 | V     |

| Ambient Operating Temperat | ure (power applied)          | T <sub>A</sub>     | -55  | 125      | °C    |

| Storage Temperature        |                              | T <sub>stg</sub>   | -65  | 150      | °C    |

**Notes:** 2. Operation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

3. Any pin except supplies.

## 2.3 DAC Analog Characteristics - Commercial (-CZZ,-CNZ)

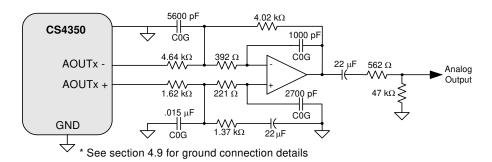

Test conditions (unless otherwise specified): VLS = VLC = 3.3 V;  $T_A = 25^{\circ} \text{ C}$ ; Input test signal is a 997 Hz sine wave; Valid with the recommended capacitor values on VD\_FILT, VQ, VBIAS (as shown in the typical connection diagram in Figure 10) and output circuits as shown in Figure 17 and Figure 18; Fs = 48 kHz, 96 kHz, and 192 kHz; measurement bandwidth 10 Hz to 20 kHz.

Table 3. DAC Analog Characteristics - Commercial (-CZZ,-CNZ)

| Parameter                                                |                                                               | Symbol              | Min                        | Тур                                                               | Max                                          | Unit                             |

|----------------------------------------------------------|---------------------------------------------------------------|---------------------|----------------------------|-------------------------------------------------------------------|----------------------------------------------|----------------------------------|

| VA= 5.0 V                                                |                                                               | ı                   |                            | Single-ended/Di                                                   | fferential                                   | ·I                               |

| 16-bit A-                                                | Weighted<br>weighted<br>Weighted<br>weighted                  |                     | 98/106<br>95/103<br>-<br>- | 101/109<br>98/106<br>95/96<br>92/93                               | -<br>-<br>-                                  | dB<br>dB<br>dB<br>dB             |

| Total Harmonic Distortion + Noise (Note 4) 24-bit 16-bit | 0 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB          | THD+N               | -<br>-<br>-<br>-<br>-<br>- | -91<br>-78/-86<br>-38/-46<br>-90<br>-72/-73<br>-32/-33            | -86/-87<br>-<br>-35/-43<br>-<br>-<br>-       | dB<br>dB<br>dB<br>dB<br>dB       |

| VA= 3.3 V                                                |                                                               |                     |                            | Single-ended/Di                                                   | fferential                                   |                                  |

| ur<br>16-bit A-                                          | Weighted<br>weighted<br>Weighted<br>weighted                  |                     | 98/106<br>95/103<br>-<br>- | 101/109<br>98/106<br>95/96<br>92/93                               | -<br>-<br>-<br>-                             | dB<br>dB<br>dB<br>dB             |

| Total Harmonic Distortion + Noise (Note 4) 24-bit 16-bit | 0 dB<br>-2 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB | THD+N               | -<br>-<br>-<br>-<br>-<br>- | -86<br>-91/-93<br>-78/-86<br>-38/-46<br>-83<br>-72/-73<br>-32/-33 | -77<br>-<br>-<br>-<br>-35/-43<br>-<br>-<br>- | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| VA= 3.3 to 5.0 V                                         |                                                               |                     |                            |                                                                   |                                              | _                                |

| Interchannel Isolation                                   | (1 kHz)                                                       |                     | -                          | 100                                                               | -                                            | dB                               |

| DC Accuracy Interchannel Gain Mismatch Gain Drift        |                                                               |                     | -                          | 0.1<br>-400                                                       | 0.25                                         | dB<br>ppm/°C                     |

| Analog Output                                            |                                                               |                     |                            |                                                                   |                                              |                                  |

| Full Scale Output Voltage - Single Ended                 | -CZZ<br>-CNZ                                                  |                     | 2.61<br>2.45               | 2.78<br>2.59                                                      | 2.96<br>2.91                                 | Vpp<br>Vpp                       |

| Full Scale Output Voltage - Differential                 | -CZZ<br>-CNZ                                                  |                     | 5.22<br>4.90               | 5.56<br>5.18                                                      | 5.92<br>5.82                                 | Vpp<br>Vpp                       |

| Quiescent Voltage                                        |                                                               | $V_{Q}$             | -                          | 0.5•VA                                                            | -                                            | VDC                              |

| Max DC Current draw from an AOUT pin                     |                                                               | I <sub>OUTmax</sub> | -                          | 10                                                                | -                                            | μА                               |

| Max Current draw from VQ                                 |                                                               | I <sub>Qmax</sub>   | -                          | 100                                                               | -                                            | μΑ                               |

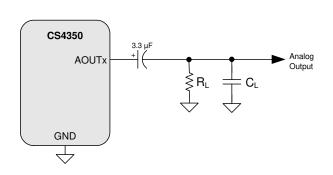

| Max AC-Load Resistance                                   | (Note 5)                                                      | $R_L$               | -                          | 3                                                                 | -                                            | kΩ                               |

| Max Load Capacitance                                     | (Note 5)                                                      | $C_{L}$             | -                          | 100                                                               | -                                            | pF                               |

| Output Impedance                                         |                                                               | Z <sub>OUT</sub>    | -                          | 100                                                               | -                                            | Ω                                |

Notes: 4. One LSB of triangular PDF dither is added to data

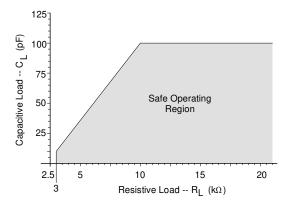

5. R<sub>L</sub> and C<sub>L</sub> represent the minimum resistance and maximum capacitance required for the CS4350's internal op-amp to remain stable. See Figure 1 and Figure 2 for more details.

## 2.4 DAC Analog Characteristics - Automotive (-DZZ)

Test conditions (unless otherwise specified): VLS = 1.35 V to 5.25 V, VLC = 3.14 V to 5.25 V,  $T_A = -40^{\circ}$  C to  $105^{\circ}$  C, input test signal is a 997 Hz sine wave; Valid with the recommended capacitor values on VFILT, VQ, VBIAS (as shown in the typical connection diagram in Figure 10) and output circuits as shown in Figure 17 and Figure 18; Fs = 48 kHz, 96 kHz, and 192 kHz; Measurement bandwidth 10 Hz to 20 kHz.

Table 4. DAC Analog Characteristics - Automotive (-DZZ)

| Parameter                     |                  | Symbol                                                         | Min                 | Тур                        | Max                                                               | Unit                                    |                                  |

|-------------------------------|------------------|----------------------------------------------------------------|---------------------|----------------------------|-------------------------------------------------------------------|-----------------------------------------|----------------------------------|

| VA= 4.7                       | '5 V to 5.2      | 25 V                                                           |                     |                            | Single-ended/Di                                                   | fferential                              | 1                                |

| Dynamic Range (Note 4)        | 24-bit<br>16-bit | A-Weighted<br>unweighted<br>A-Weighted<br>unweighted           |                     | 95/103<br>92/100<br>-<br>- | 101/109<br>98/106<br>95/96<br>92/93                               | -<br>-<br>-<br>-                        | dB<br>dB<br>dB<br>dB             |

| Total Harmonic Distortion + N | Noise (Note      | 4)                                                             |                     | -                          |                                                                   |                                         |                                  |

|                               | 24-bit<br>16-bit | 0 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB           | THD+N               | -<br>-<br>-<br>-           | -91<br>-78/-86<br>-38/-46<br>-90<br>-72/-73<br>-32/-33            | -85<br>-<br>-32/-40<br>-<br>-<br>-      | dB<br>dB<br>dB<br>dB<br>dB       |

| VA= 3.1                       | 4 V to 3.4       | 6 V                                                            | l                   |                            | Single-ended/Di                                                   | fferential                              | 1                                |

| Dynamic Range (Note 4)        | 24-bit<br>16-bit | A-Weighted<br>unweighted<br>A-Weighted<br>unweighted           |                     | 94/103<br>91/100<br>-<br>- | 101/109<br>98/106<br>95/96<br>92/93                               | -<br>-<br>-                             | dB<br>dB<br>dB<br>dB             |

| Total Harmonic Distortion + N | Noise (Note      | 6)                                                             |                     |                            |                                                                   |                                         |                                  |

|                               | 24-bit           | -1 dB<br>-2 dB<br>-20 dB<br>-60 dB<br>0 dB<br>-20 dB<br>-60 dB | THD+N               | -<br>-<br>-<br>-<br>-      | -89<br>-91/-93<br>-78/-86<br>-38/-46<br>-83<br>-72/-73<br>-32/-33 | -83<br>-<br>-<br>-31/-40<br>-<br>-<br>- | dB<br>dB<br>dB<br>dB<br>dB<br>dB |

| VA= 3.                        | 14 to 5.25       | 5 V                                                            |                     |                            |                                                                   | •                                       | •                                |

| Interchannel Isolation        |                  | (1 kHz)                                                        |                     | -                          | 100                                                               | -                                       | dB                               |

| DC Accuracy                   |                  |                                                                |                     |                            | 1                                                                 |                                         | 1                                |

| Interchannel Gain Mismatch    |                  |                                                                |                     | -                          | 0.1                                                               | 0.25                                    | dB                               |

| Gain Drift                    |                  |                                                                |                     | -                          | -400                                                              | -                                       | ppm/°C                           |

| Analog Output                 |                  |                                                                |                     |                            |                                                                   |                                         | •                                |

| Full Scale Output Voltage - S | Single Ende      | ed                                                             |                     | 2.55                       | 2.78                                                              | 3.03                                    | Vpp                              |

| Full Scale Output Voltage - D | Differential     |                                                                |                     | 5.10                       | 5.56                                                              | 6.06                                    | Vpp                              |

| Quiescent Voltage             |                  |                                                                | $V_{Q}$             | -                          | 0.5•VA                                                            | -                                       | VDC                              |

| Max DC Current draw from a    | ın AOUT pi       | n                                                              | I <sub>OUTmax</sub> | -                          | 10                                                                | -                                       | μА                               |

| Max Current draw from VQ      |                  |                                                                | I <sub>Qmax</sub>   | -                          | 100                                                               | -                                       | μА                               |

| Max AC-Load Resistance        | ·                | (Note 5)                                                       | $R_L$               | -                          | 3                                                                 | -                                       | kΩ                               |

| Max Load Capacitance          |                  | (Note 5)                                                       | C <sub>L</sub>      | -                          | 100                                                               | -                                       | pF                               |

| Output Impedance              |                  |                                                                | Z <sub>OUT</sub>    | -                          | 100                                                               | -                                       | Ω                                |

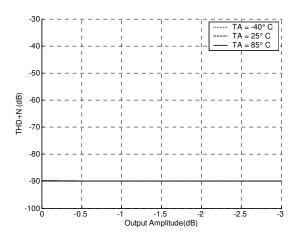

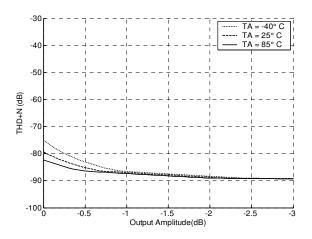

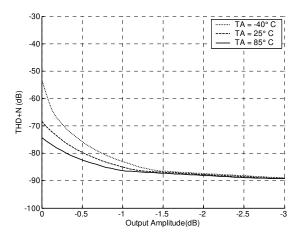

Note: 6. One-half LSB of triangular PDF dither is added to data. Also, see Figure 3, Figure 4, and Figure 5 for more details on the CS4350-DZZ THD+N performance with 0dB input signal.

Figure 1. Equivalent Output Load

Figure 2. Maximum Loading

Figures 3 through 5 show typical THD+N performance for CS4350 devices that exhibit the maximum full scale output voltages as specified in the DAC Analog Characteristics tables (see page 9 and 10). With decreasing VA, THD+N performance is increasingly affected by the full scale output voltage and temperature, with higher full scale output voltage and lower temperatures corresponding to lower THD+N performance.

Figure 3. THD+N vs Output Amplitude for VA = 5.0 V

Figure 4. THD+N vs Output Amplitude for VA = 3.3 V

Figure 5. THD+N vs Output Amplitude for VA = 3.14 V

## 2.5 Combined Interpolation and On-Chip Analog Filter Response

The filter characteristics have been normalized to the sample rate (Fs) and is referenced to the desired sample rate by multiplying the given characteristic by Fs. Amplitude vs. Frequency plots of this data are available in the "Filter Plots" on page 36.

Table 5. Combined Interpolation and On-Chip Analog Filter Response

| Parameter                                                        | Min   | Тур    | Max      | Unit |

|------------------------------------------------------------------|-------|--------|----------|------|

| Fast Roll-Off                                                    |       |        | •        | •    |

| Passband (Note 7) -0.01 dB corner (Single Speed)                 | 0     | -      | .454     | Fs   |

| -0.1 dB corner (Double Speed)                                    | 0     | -      | .42      | Fs   |

| -0.2 dB corner (Quad Speed)                                      | 0     | -      | .27      | Fs   |

| -3 dB corner (All Speed Modes)                                   | 0     | -      | .499     | Fs   |

| Frequency Response 10 Hz to 20 kHz Single Speed                  | -0.01 | -      | +0.01    | dB   |

| Double Speed, Quad Speed                                         | -0.02 | -      | +0.02    | dB   |

| StopBand                                                         | 0.547 | -      | -        | Fs   |

| Stop-Band Attenuation (Note 8)                                   | 102   | -      | -        | dB   |

| Total Group Delay (Fs - Output Sample Rate) TDM Slot 0 Channel B | -     | 8.4/Fs | -        | s    |

| All Other Interface Formats and TDM Slots/Channels               | -     | 9.4/Fs | -        | s    |

| Intrachannel Phase Deviation                                     | -     | -      | ±0.56/Fs | s    |

| Interchannel Phase Deviation                                     | -     | -      | 0        | s    |

| De-emphasis Error (Note 9) Fs = 32 kHz                           | -     | -      | ±0.23    | dB   |

| (Relative to 1 kHz) Fs = 44.1 kHz                                | -     | -      | ±0.14    | dB   |

| Fs = 48 kHz                                                      | -     | -      | ±0.09    | dB   |

| Slow Roll-Off (Note 1                                            | 0)    | •      | •        | •    |

| Passband (Note 7) -0.01 dB corner (Single Speed)                 | 0     | -      | 0.417    | Fs   |

| -0.1 dB corner (Double Speed)                                    | 0     | -      | .37      | Fs   |

| -0.2 dB corner (Quad Speed)                                      | 0     | -      | .27      | Fs   |

| -3 dB corner (All Speed Modes)                                   | 0     | -      | .499     | Fs   |

| Frequency Response 10 Hz to 20 kHz Single Speed                  | -0.01 | -      | +0.01    | dB   |

| Double Speed, Quad Speed                                         | -0.02 | -      | +0.02    | dB   |

| StopBand                                                         | .583  | -      | -        | Fs   |

| Stop-Band Attenuation (Note 8)                                   | 64    | -      | -        | dB   |

| Total Group Delay (Fs - Output Sample Rate) TDM Slot 0 Channel B | -     | 5.5/Fs | -        | s    |

| All Other Interface Formats and TDM Slots/Channels               | -     | 6.5/Fs | -        | s    |

| Intrachannel Phase Deviation                                     | -     | -      | ±0.14/Fs | S    |

| Interchannel Phase Deviation                                     | -     | -      | 0        | s    |

| De-emphasis Error (Note 9) Fs = 32 kHz                           | -     | -      | ±0.23    | dB   |

| (Relative to 1 kHz) Fs = 44.1 kHz                                | -     | -      | ±0.14    | dB   |

| Fs = 48 kHz                                                      | -     | -      | ±0.09    | dB   |

Notes: 7. Response is clock dependent.

- 8. The Measurement Bandwidth is from stopband to 3 Fs.

- 9. De-emphasis is available only in Single-Speed Mode; Only 44.1 kHz De-emphasis is available in Stand-Alone Mode.

- 10. Slow Roll-off interpolation filter is only available in Control Port Mode.

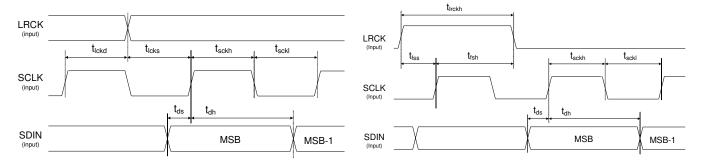

## 2.6 Switching Specifications - Serial Audio Interface

Inputs: Logic 0 = GND; Logic 1 = VLS;  $C_L$  = 20 pF.

Table 6. Switching Specifications - Serial Audio Interface

| Parameters                              | Symbol                | Min        | Max    | Units |

|-----------------------------------------|-----------------------|------------|--------|-------|

| RMCK Output Frequency (Note 11) VLS=1   | .5 V nominal          | Unsup      | ported | MHz   |

| VLS=1.6                                 | 2 V or above          | 7.680      | 16.896 | MHz   |

| VLS=2.9                                 | 7 V or above          | 7.680      | 55.3   | MHz   |

| 3.14 V ≤ VA ≤ 5.25 V an                 | d 1.35 V ≤ VLS ≤ 5.2  | 5 <i>V</i> | •      | -     |

| RMCK Output Duty Cycle                  |                       | 45         | 55     | %     |

| Input Sample Rate Single-               | Speed Mode            | 30         | 54     |       |

| Double-                                 | Speed Mode Fs         | 60         | 108    | kHz   |

| Quad-                                   | Speed Mode            | 120        | 216    |       |

| LRCK Duty Cycle (Non-TDM Mode)          |                       | 40         | 60     | %     |

| SDIN Setup Time Before SCLK Rising Edge | t <sub>ds</sub>       | 1          | -      | ns    |

| SDIN Hold Time After SCLK Rising Edge   | t <sub>dh</sub>       | 8          | -      | ns    |

| 4.75 V ≤ VA ≤ 5.25 V an                 | d 3.14 V ≤ VLS ≤ 5.2  | 5 V        | 1      | 1     |

| SCLK Frequency                          |                       | -          | 55.3   | MHz   |

| SCLK High Time                          | t <sub>sckh</sub>     | 6          | -      | ns    |

| SCLK Low Time                           | t <sub>sckl</sub>     | 6          | -      | ns    |

| Non-TDM Mode (refer to Figure 6)        | <u>.</u>              |            |        |       |

| LRCK Edge to SCLK Rising Edge           | t <sub>lcks</sub>     | 11         | -      | ns    |

| SCLK Rising Edge to LRCK Edge           | t <sub>lckd</sub>     | 1          | -      | ns    |

| TDM Mode (refer to Figure 7)            | <u>.</u>              |            |        |       |

| LRCK High Time                          | t <sub>Irckh</sub>    | 20         | -      | ns    |

| SCLK Rising to LRCK Falling Edge        | t <sub>fsh</sub>      | 3          | -      | ns    |

| LRCK Rising Edge to SCLK Rising Edge    | t <sub>fss</sub>      | 1          | -      | ns    |

| 3.14 V ≤ VA < 4.75 V o                  | r 1.35 V ≤ VLS < 3.14 | <i>V</i>   |        |       |

| SCLK Frequency                          |                       | -          | 27.7   | MHz   |

| SCLK High Time                          | t <sub>sckh</sub>     | 11         | -      | ns    |

| SCLK Low Time                           | t <sub>sckl</sub>     | 11         | -      | ns    |

| Non-TDM Mode (refer to Figure 6)        | _                     | •          | •      | -     |

| LRCK Edge to SCLK Rising Edge           | t <sub>lcks</sub>     | 16         | -      | ns    |

| SCLK Rising Edge to LRCK Edge           | t <sub>lckd</sub>     | 1          | -      | ns    |

| TDM Mode (refer to Figure 7)            | •                     |            |        |       |

| LRCK High Time                          | t <sub>Irckh</sub>    | 25         | -      | ns    |

| SCLK Rising to LRCK Falling Edge        | t <sub>fsh</sub>      | 8          | -      | ns    |

| LRCK Rising Edge to SCLK Rising Edge    | t <sub>fss</sub>      | 1          | -      | ns    |

**Note:** 11. RMCK output frequency depends on the input LRCK frequency. See Section 4.1 and Section 4.2 for more details.

Figure 6. Serial Port Timing, Non-TDM Mode

Figure 7. Serial Port Timing, TDM Mode

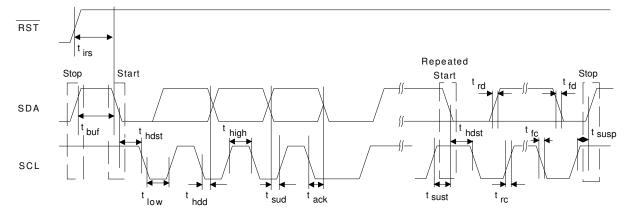

## 2.7 Switching Characteristics - Control Port - I<sup>2</sup>C Format

Inputs: Logic 0 = GND; Logic 1 = VLC;  $C_L = 20 pF$ .

Table 7. Switching Characteristics - Control Port - I<sup>2</sup>C Format

| Parameter                                              | Symbol                            | Min | Max  | Unit |

|--------------------------------------------------------|-----------------------------------|-----|------|------|

| SCL Clock Frequency                                    | f <sub>scl</sub>                  | -   | 100  | kHz  |

| RST Rising Edge to Start                               | t <sub>irs</sub>                  | 500 | -    | ns   |

| Bus Free Time Between Transmissions                    | t <sub>buf</sub>                  | 4.7 | -    | μs   |

| Start Condition Hold Time (prior to first clock pulse) | t <sub>hdst</sub>                 | 4.0 | -    | μs   |

| Clock Low time                                         | t <sub>low</sub>                  | 4.7 | -    | μs   |

| Clock High Time                                        | t <sub>high</sub>                 | 4.0 | -    | μs   |

| Setup Time for Repeated Start Condition                | t <sub>sust</sub>                 | 4.7 | -    | μs   |

| SDA Hold Time from SCL Falling (Note 12)               | t <sub>hdd</sub>                  | 0   | -    | μs   |

| SDA Setup time to SCL Rising                           | t <sub>sud</sub>                  | 250 | -    | ns   |

| Rise Time of SCL and SDA                               | t <sub>rc</sub> , t <sub>rc</sub> | -   | 1    | μs   |

| Fall Time SCL and SDA                                  | t <sub>fc</sub> , t <sub>fc</sub> | -   | 300  | ns   |

| Setup Time for Stop Condition                          | t <sub>susp</sub>                 | 4.7 | -    | μs   |

| Acknowledge Delay from SCL Falling                     | t <sub>ack</sub>                  | 300 | 1000 | ns   |

**Note:** 12. Data must be held for sufficient time to bridge the transition time,  $t_{fc}$ , of SCL.

Figure 8. Control Port Timing - I<sup>2</sup>C Format

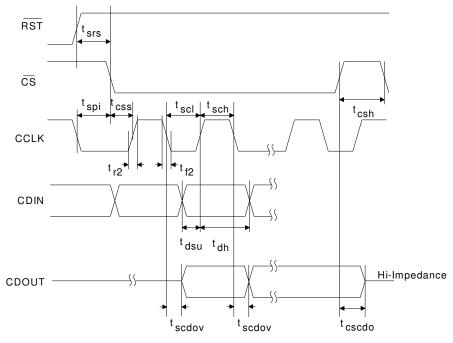

## 2.8 Switching Characteristics - Control Port - SPI Format

Inputs: Logic 0 = GND; Logic 1 = VLC;  $C_L = 20 \text{ pF}.$

Table 8. Switching Characteristics - Control Port - SPI Format

| Parameter                                          | Symbol             | Min | Max | Unit |

|----------------------------------------------------|--------------------|-----|-----|------|

| CCLK Clock Frequency                               | f <sub>sclk</sub>  | -   | 6   | MHz  |

| RST Rising Edge to CS Falling                      | t <sub>srs</sub>   | 500 | -   | ns   |

| CCLK Edge to CS Falling (Note 13)                  | t <sub>spi</sub>   | 500 | -   | ns   |

| CS High Time Between Transmissions                 | t <sub>csh</sub>   | 1.0 | -   | μs   |

| CS Falling to CCLK Edge                            | t <sub>css</sub>   | 20  | -   | ns   |

| CCLK Low Time                                      | t <sub>scl</sub>   | 66  | -   | ns   |

| CCLK High Time                                     | t <sub>sch</sub>   | 66  | -   | ns   |

| CDIN to CCLK Rising Setup Time                     | t <sub>dsu</sub>   | 40  | -   | ns   |

| CCLK Rising to DATA Hold Time (Note 14)            | t <sub>dh</sub>    | 15  | -   | ns   |

| Rise Time of CCLK and CDIN (Note 15)               | t <sub>r2</sub>    | -   | 100 | ns   |

| Fall Time of CCLK and CDIN (Note 15)               | t <sub>f2</sub>    | -   | 100 | ns   |

| Transition Time from CCLK to CDOUT Valid (Note 16) | t <sub>scdov</sub> | -   | 100 | ns   |

| Time from CS rising to CDOUT High-Z                | t <sub>cscdo</sub> | -   | 100 | ns   |

**Notes:** 13.  $t_{spi}$  only needed before first falling edge of  $\overline{CS}$  after  $\overline{RST}$  rising edge.  $t_{spi} = 0$  at all other times.

- 14. Data must be held for sufficient time to bridge the transition time of CCLK.

- 15. For  $F_{SCK}$  < 1 MHz.

- 16. CDOUT should *not* be sampled during this time.

Figure 9. Control Port Timing - SPI Mode

## 2.9 Digital Characteristics

**Table 9. Digital Characteristics**

| Parameters                                                          |                              |                 | Min                 | Тур   | Max                 | Units |

|---------------------------------------------------------------------|------------------------------|-----------------|---------------------|-------|---------------------|-------|

| High-Level Input Voltage                                            | VLC or VLS = 5.0 V           | V <sub>IH</sub> | 0.7•V <sub>L</sub>  | -     | -                   | V     |

|                                                                     | VLC or VLS = $3.3 \text{ V}$ | $V_{IH}$        | 2.0                 | -     | -                   | V     |

|                                                                     | VLS = 2.5 V                  | $V_{IH}$        | 1.7                 | -     | -                   | V     |

|                                                                     | VLS = 1.5 V                  | $V_{IH}$        | 0.75•V <sub>L</sub> | -     | -                   | V     |

| Low-Level Input Voltage                                             | VLC or VLS = 5.0 V           | V <sub>IL</sub> | -                   | -     | 0.35•V <sub>L</sub> | V     |

|                                                                     | VLC or VLS = $3.3 \text{ V}$ | $V_{IL}$        | -                   | -     | 0.8                 | V     |

|                                                                     | VLS = 2.5 V                  | $V_{IL}$        | -                   | -     | 0.7                 | V     |

|                                                                     | VLS = 1.5 V                  | $V_{IL}$        | -                   | -     | 0.25•V <sub>L</sub> | V     |

| Input Leakage Current                                               |                              | l <sub>in</sub> | -                   | 1     | ±10                 | μΑ    |

| Input Capacitance                                                   |                              |                 | -                   | 8     | -                   | pF    |

| High Level Output Voltage (RMCK) IO:                                | = 2 mA (VLS ≥ 3.0V)          | $V_{OH}$        | VLS-1.0             | S-1.0 |                     | V     |

| Low Level Output Voltage (RMCK) I <sub>O</sub> = -2 mA (VLS ≥ 3.0V) |                              |                 | -                   | -     | 0.4                 | V     |

| RMCK Output Load Drive                                              |                              |                 | -                   | -     | 10                  | pF    |

| Maximum MUTEC Drive Current                                         |                              | -               | 2                   | -     | mA                  |       |

| MUTEC High-Level Output Voltage                                     | V <sub>OH</sub>              | -               | VA                  | -     | V                   |       |

| MUTEC Low-Level Output Voltage                                      |                              |                 | -                   | 0     | -                   | V     |

#### 2.10 Power and Thermal Characteristics

**Table 10. Power and Thermal Characteristics**

| Parameters                                        |                          | Symbol         | Min | Тур  | Max | Units |

|---------------------------------------------------|--------------------------|----------------|-----|------|-----|-------|

| Power Supply Current - Normal Operation (Note 17  | ) VA= 5.0 V              | I <sub>A</sub> | -   | 28   | 34  | mA    |

|                                                   | VA= 3.3 V                | I <sub>A</sub> | -   | 24   | 29  | mA    |

| VLS = VLC                                         | C =5.0 V (Note 18)       | $I_{LS}$       | -   | 4    | 6   | mA    |

| VLS = VLC                                         | C =3.3 V (Note 18)       | $I_{LS}$       | -   | 2    | 5   | mA    |

| VLS = VLC                                         | = 5.0 V (Note 19)        | $I_{LC}$       | -   | 14   | 18  | mA    |

| VLS = VLC                                         | = 3.3 V (Note 19)        | $I_{LC}$       | -   | 14   | 18  | mA    |

| Power Supply Current - Power-Down State (Note 20) |                          |                |     |      |     |       |

|                                                   | VA, VLS <sub>,</sub> VLC | $I_{pd}$       | -   | 100  | -   | μΑ    |

| Power Dissipation - Normal Operation (Note 17)    |                          |                |     |      |     |       |

| VA = \                                            | /LC= VLS = 5.0 V         |                | -   | 230  | 290 | mW    |

| VA = \                                            | /LC= VLS = 3.3 V         |                | -   | 132  | 171 | mW    |

| Power Dissipation - Power-Down State (Note 20)    |                          |                |     |      |     |       |

| VA = \                                            | /LC= VLS = 5.0 V         |                | -   | 0.5  | -   | mW    |

| VA = \                                            | /LC= VLS = 3.3 V         |                | -   | 0.33 | -   | mW    |

| Power Supply Rejection Ratio (Note 21)            | (1 kHz)                  | PSRR           | -   | 60   | -   | dB    |

|                                                   | (60 Hz)                  | PSRR           | -   | 50   | -   | dB    |

**Notes:** 17. Current consumption increases with increasing Fs within the range of a speed mode. Variance between speed modes is small. Typ and Max values are based on Fs = 48 kHz.

- 18.  $I_{LS}$  measured with no external loading on pin 7 (RMCK).

- 19. I<sub>LC</sub> measured with no external loading on pin 2 (SDA).

- 20. Power-down mode is defined as  $\overline{RST}$  pin = Low with all clock and data lines held static.

- 21. Valid with the recommended capacitor values on VFILT, VQ, and VBIAS+ as shown in the typical connection diagram in Figure 10.

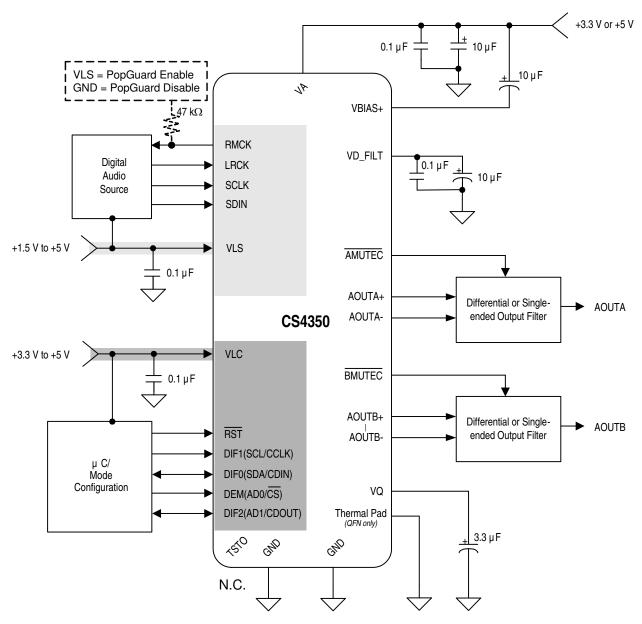

## 3 TYPICAL CONNECTION DIAGRAM

Figure 10. Typical Connection Diagram

#### 4 APPLICATIONS

## 4.1 Sample Rate Range and Oversampling Mode Detect

The device operates in one of three oversampling modes based on the input sample rate. In Control Port Mode, the allowed sample rate range in each mode will depend on how the FM[1:0] bits are configured. In Stand-Alone Mode, the sample rate range will be according to Table 11.

#### 4.1.1 Sample Rate Auto-Detect

The Auto-Detect feature is enabled by default. In this state, the CS4350 will auto-detect the correct mode when the input sample rate (Fs), defined by the LRCK frequency, falls within one of the ranges shown in Table 11. Sample rates outside the specified range for each mode are not supported when Auto-Detect is enabled.

Table 11. CS4350 Auto-Detect

| Input Sample Rate (Fs) | Mode              |

|------------------------|-------------------|

| 30 kHz - 54 kHz        | Single-Speed Mode |

| 60 kHz - 108 kHz       | Double-Speed Mode |

| 120 kHz - 216 kHz      | Quad-Speed Mode   |

In Control Port Mode, the Auto-Detect feature can be disabled by the Functional Mode (FM[1:0]) bits in the control port register 02h. In this state, the CS4350 will not auto-detect the correct mode based on the input sample rate (Fs). The operational mode must then be set manually according to one of the ranges referred to in Section 8.2.3. Sample rates outside the specified range for each mode are not supported. In Stand-Alone Mode it is not possible to disable auto-detect of sample rates.

#### 4.2 System Clocking

The device requires external generation of the left/right (LRCK) and serial (SCLK) clocks. The left/right clock frequency is equal to the input sample rate (Fs).

Refer to Section 4.3 for the required SCLK-to-LRCK timing associated with the selected digital interface format, and "Switching Specifications - Serial Audio Interface" on page 13 for the maximum allowed clock frequencies.

## 4.2.1 Recovered Master Clock (RMCK)

The CS4350 generates a high-frequency master clock (RMCK) which it derives from the LRCK input, available on the RMCK pin. In Stand-Alone Mode, the frequency of RMCK is equal to 256 x LRCK in Single-Speed and Double-Speed Mode; and 128 x LRCK in Quad-Speed Mode. In Control-Port Mode, the frequency of the RMCK signal can be selected through register 08h (see Section 8.7 on page 34 for more details).

#### 4.3 Digital Interface Format

The device will accept audio samples in 1 of 8 digital interface formats, as shown in Table 12 on page 24 for Stand-Alone Mode and Table 13 on page 29 for Control Port Mode.

The desired serial audio interface format is selected via the DIF[2:0] bits in Control Port Mode (see Section 8.2.1), or the DIF[2:0] pins in Stand-Alone Mode (see Section 5.1). For illustrations of the required relationship between LRCK, SCLK and SDIN, see Figures 11-13. For all formats, SDIN is valid on the rising edge of SCLK.

For more information about serial audio formats, refer to the Cirrus Logic Application Note AN282, *The 2-Channel Serial Audio Interface: A Tutorial*, available at www.cirrus.com.

Figure 13. Right-Justified Data

#### 4.3.1 Time-Division Multiplex (TDM) Mode

Four TDM interface modes are available that allow the CS4350 to input stereo PCM data in one of 4 time "slots". Figure 14 shows the serial port connections necessary to input 8-channel TDM data into four CS4350 devices, and the corresponding DIF[2:0] pin or register-bit settings required for each CS4350. Figure 15 shows the TDM data format for each of the four CS4350 devices shown in Figure 14.

**Note:** The group delay for TDM slot 0 channel B differs from the group delay of all other interface formats and TDM slots/channels by one sample. Refer to the group delay specification in the combined interpolation and on-chip analog filter response specifications table.

Figure 14. TDM Mode Connection Diagram

Figure 15. TDM Mode Timing

#### 4.4 De-Emphasis

The device includes on-chip digital de-emphasis. Figure 16 shows the de-emphasis curve for Fs equal to 44.1 kHz. The frequency response of the de-emphasis curve will scale proportionally with changes in sample rate, Fs.

Figure 16. De-Emphasis Curve

Note: De-emphasis is only available in Single-Speed Mode.

#### 4.5 Mute Control

The mute control pins (AMUTEC and BMUTEC) go active during power-up initialization, reset, muting (see Section 8.4.3), and loss of LRCK. These pins are intended to be used as control for external mute circuits to prevent the clicks and pops that can occur in any single-ended single-supply system.

Use of the mute control function is not mandatory but recommended for designs requiring the absolute minimum in extraneous clicks and pops. Also, use of the Mute Control function can enable the system designer to achieve idle-channel noise and signal-to-noise ratios which are only limited by the external mute circuit.

#### 4.6 Recommended Power-Up Sequence

#### 4.6.1 Stand-Alone Mode

- 1. Hold RST low until the power supplies and configuration pins are stable and the left/right clock is fixed to the appropriate frequencies, as discussed in Section 4.2. In this state, the control port registers are reset to their default settings, VQ will remain low, and VBIAS will be connected to VA.

- Bring RST high. The device will remain in a low power state with VQ low for approximately 192 LRCK cycles in Single-Speed Mode (384 LRCK cycles in Double-Speed Mode, and 768 LRCK cycles in Quad-Speed Mode).

- 3. The device will then initiate the power up sequence which lasts approximately 130 ms when the Popguard is disabled. If the Popguard is enabled, see Section 4.7 for a complete description of power-up timing.

#### 4.6.2 Control Port Mode

- 1. Hold RST low until the power supply is stable and the left/right clock is fixed to the appropriate frequency, as discussed in Section 4.2. In this state, the control port is reset to its default settings, VQ will remain low, and VBIAS will be connected to VA.

- 2. Bring RST high. The device will remain in a low-power state with VQ low.

- 3. Perform a control port write to a valid register prior to the completion of approximately 192 LRCK cycles in Single-Speed Mode (384 LRCK cycles in Double-Speed Mode, and 768 LRCK cycles in Quad-Speed Mode). The desired register settings can be loaded while keeping the PDN bit set to 1.

- 4. Set the PDN bit to 0. This will initiate the power-up sequence, which lasts approximately 130 ms when the Popguard is disabled. If the Popguard is enabled, see Section 4.7 for a complete description of power-up timing.

#### 4.7 Popguard Transient Control

The CS4350 uses a novel technique to minimize the effects of output transients during power-up and power-down. This technology, when used with external DC-blocking capacitors in series with the audio outputs, minimizes the audio transients commonly produced by single-ended single-supply converters. It is activated inside the DAC when the  $\overline{RST}$  pin is toggled and requires no other external control, aside from choosing the appropriate DC-blocking capacitors.

#### 4.7.1 **Power-Up**

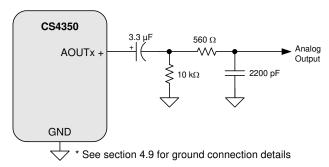

When the device is initially powered-up, the audio outputs, AOUTA and AOUTB, are clamped to GND. Following a delay of approximately 192 sample periods, each output begins to ramp toward the quiescent voltage. The amount of time it takes the outputs to ramp is related to the value of the DC-blocking capacitance and the output load. Using the example output circuit from Figure 18, the ramp up time will be approximately 0.25 seconds. When the ramp is complete, the outputs reach  $V_Q$  and audio output begins. This gradual voltage ramping allows time for the external DC-blocking capacitors to charge to the quiescent voltage, minimizing audible power-up transients.

Note the ramp up time will vary due to internal factors such as variance across device process, supply voltage, and die temperature corners as well as external output circuit component tolerances.

#### 4.7.2 Power-Down

To prevent audible transients at power-down, the device must first enter its power-down state. When this occurs, audio output ceases and the internal output buffers are disconnected from AOUTA and AOUTB. In their place, a soft-start current sink is substituted which allows the DC-blocking capacitors to slowly discharge. Once this charge is dissipated, the power to the device may be turned off, and the system is ready for the next power-on.

#### 4.7.3 Discharge Time

To prevent an audio transient at the next power-on, the DC-blocking capacitors must fully discharge before turning on the power or exiting the power-down state. If full discharge does not occur, a transient will occur when the audio outputs are initially clamped to GND. The time that the device must remain in the power-down state is related to the value of the DC-blocking capacitance and the output load. For example, with a  $3.3~\mu F$  capacitor, the minimum power-down time will be approximately 0.2~seconds.

#### 4.8 Analog Output and Filtering

The Cirrus Application Note titled *Design Notes for a 2-Pole Filter with Differential Input*, available as AN48 at www.cirrus.com, discusses the second-order Butterworth filter and differential-to-single-ended converter that was implemented on the CS4350 evaluation board, CDB4350. Figure 17 illustrates this implementation. If only single-ended outputs from the CS4350 are required, the passive output filter shown in Figure 18 can be used.

Figure 17. Differential to Single-Ended Output Filter

Figure 18. Passive Single-Ended Output Filter

### 4.9 Grounding and Power Supply Arrangements

As with any high-resolution converter, the CS4350 requires careful attention to power supply and grounding arrangements if its potential performance is to be realized. Figure 10 shows the recommended power arrangements, with VA, VLC, and VLS connected to clean supplies. The use of split analog and digital ground planes is not recommended. However, if planes are split between digital ground and analog ground the GND pins of the CS4350 should be connected to the analog ground plane.

All signals, especially clocks, should be kept away from the VBIAS, VFILT, and VQ pins in order to avoid unwanted coupling into the DAC.

## 4.9.1 Capacitor Placement

Decoupling capacitors should be placed as close to the DAC as possible, with the low value ceramic capacitor being the closest. To further minimize impedance, these capacitors should be located on the same layer as the DAC. If desired, all supply pins may be connected to the same supply, but a decoupling capacitor should still be placed on each supply pin.

**Note:** All decoupling capacitors should be referenced to GND.

The CDB4350 evaluation board demonstrates the optimum layout and power supply arrangements.

#### 5 STAND-ALONE OPERATION

#### 5.1 Serial Port Format Selection

The desired serial audio format is selected with the DIF2, DIF1 and DIF0 pins. For an explanation of the required relationship between the LRCK, SCLK and SDIN, see Figures 11-13. For all formats, SDIN is valid on the rising edge of SCLK. TDM Mode requires the selection of which stereo pair time "slot" is used to output data as shown in Table 12 and Figure 15.

**Note:** The group delay for TDM slot 0 channel B differs from the group delay of all other interface formats and TDM slots/channels by one sample. Refer to the group delay specification in the combined interpolation and on-chip analog filter response specifications table.

| DIF2 | DIF1 | DIF0 | DESCRIPTION                         | FORMAT | FIGURE |  |

|------|------|------|-------------------------------------|--------|--------|--|

| 0    | 0    | 0    | Left-Justified, up to 24-bit data   | 0      | 12     |  |

| 0    | 0    | 1    | I <sup>2</sup> S, up to 24-bit data | 1      | 11     |  |

| 0    | 1    | 0    | Right-Justified, 16-bit data        | 2      | 13     |  |

| 0    | 1    | 1    | Right-Justified, 24-bit data        | 3      | 13     |  |

| 1    | 0    | 0    | TDM slot 0                          | 4      | 15     |  |

| 1    | 0    | 1    | TDM slot 1                          | 5      | 15     |  |

| 1    | 1    | 0    | TDM slot 2                          | 6      | 15     |  |

| 1    | 1    | 1    | TDM slot 3                          | 7      | 15     |  |

Table 12. Digital Interface Format - Stand-Alone Mode

## 5.2 De-Emphasis Control

When pulled to VLC, the DEM pin activates the 44.1 kHz de-emphasis filter. When pulled to GND, the DEM pin turns off the de-emphasis filter.

## 5.3 Popguard Transient Control

In Stand-Alone Mode, Popguard is selected by placing a 47 k $\Omega$  resistor between RMCK and VLS. Popguard is defeated in Stand-Alone Mode by placing a 47 k $\Omega$  resistor between RMCK and ground.

#### 6 CONTROL PORT OPERATION

The control port is used to load all the internal register settings (see "Register Description" on page 29). The operation of the control port may be completely asynchronous with the audio sample rate. However, to avoid potential interference problems, the control port pins should remain static if no operation is required.

The control port can operate in I<sup>2</sup>C or SPI mode.

#### 6.1 MAP Auto Increment

The device has a MAP (memory address pointer) auto-increment capability enabled by the INCR bit (also the MSB) of the MAP. If INCR is set to 0, MAP will stay constant for consecutive writes or reads. If INCR is set to 1, MAP will auto increment after each byte is read or written, allowing block reads or writes of consecutive registers.

#### 6.2 I<sup>2</sup>C Mode

In the I<sup>2</sup>C Mode, data is clocked into and out of the bi-directional serial control data line, SDA, by the serial control port clock, SCL (see Figure 19 for the clock to data relationship). There is no CS pin. AD1 and AD0

enable the user to alter the chip address (10010[AD1][AD0][R/ $\overline{W}$ ]) and should be tied to VLC or GND as required before powering up the device. SPI Mode will be selected if the device ever detects a high to low transition on the AD0/ $\overline{CS}$  pin after power-up.

#### 6.2.1 I<sup>2</sup>C Write

To write to the device, follow the procedure below while adhering to the control port Switching Specifications in "Switching Characteristics - Control Port - I<sup>2</sup>C Format" on page 14.

- 1. Initiate a START condition to the I<sup>2</sup>C bus followed by the address byte. The upper 5 bits must be 10010. The sixth and seventh bit must match the settings of the AD1 and AD0 pins respectively, and the eighth must be 0 (the eighth bit of the address byte is the R/W bit).

- 2. Wait for an acknowledge (ACK) from the part, then write to the memory address pointer, MAP. This byte points to the register to be written.

- 3. Wait for an acknowledge (ACK) from the part, then write the desired data to the register pointed to by the MAP.

- 4. If the INCR bit (see Section 6.1) is set to 1, repeat the previous step until all the desired registers are written, then initiate a STOP condition to the bus.

- 5. If the INCR bit is set to 0 and further I<sup>2</sup>C writes to other registers are desired, it is necessary to initiate a repeated START condition and follow the procedure detailed from step 1. If no further writes to other registers are desired, initiate a STOP condition to the bus.

#### 6.2.2 I<sup>2</sup>C Read

To read from the device, follow the procedure below while adhering to the control port switching specifications in "Switching Characteristics - Control Port - I<sup>2</sup>C Format" on page 14.

- 1. Initiate a START condition to the I<sup>2</sup>C bus followed by the address byte. The upper 5 bits must be 10010. The sixth and seventh bits must match the setting of the AD1 and AD0 pins, respectively, and the eighth must be 1. The eighth bit of the address byte is the R/W bit.

- 2. After transmitting an acknowledge (ACK), the device will then transmit the contents of the register pointed to by the MAP. The MAP register will contain the address of the last register written to the MAP or the default address (see Section 6.4.2) if an I<sup>2</sup>C read is the first operation performed on the device.

- 3. Once the device has transmitted the contents of the register pointed to by the MAP, issue an ACK.

- 4. If the INCR bit is set to 1, the device will continue to transmit the contents of successive registers. Continue providing a clock and issue an ACK after each byte until all the desired registers are read; then initiate a STOP condition to the bus.

- 5. If the INCR bit is set to 0 and further I<sup>2</sup>C reads from other registers are desired, it is necessary to initiate a repeated START condition and follow the procedure detailed from steps 1 and 2 from the I<sup>2</sup>C Write instructions, followed by step 1 of the I<sup>2</sup>C Read section. If no further reads from other registers are desired, initiate a STOP condition to the bus.