Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

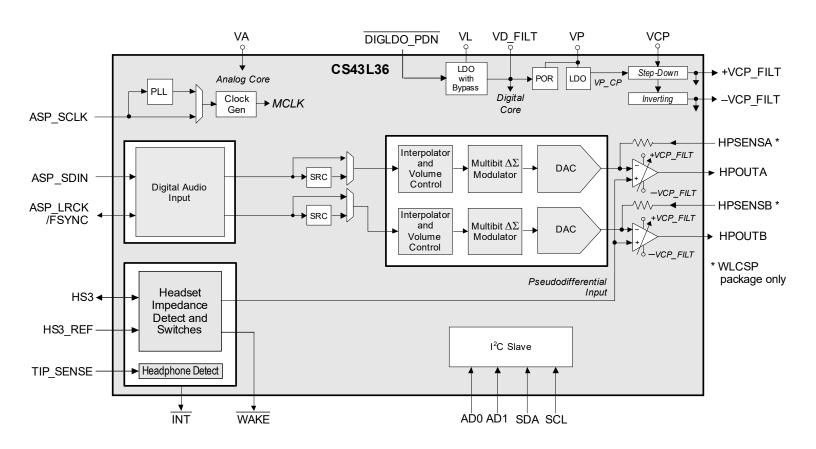

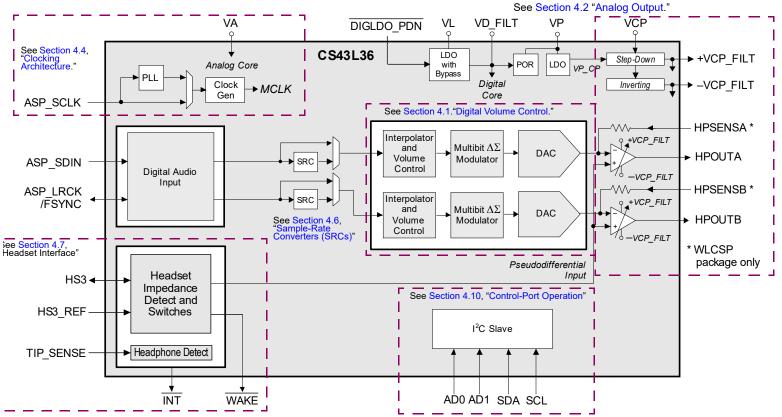

# Low-Power, High-Performance Audio DAC with Class H Headphone Drivers

# **System Features**

- Stereo headphone (HP) output with 114-dB dynamic range

- Class H HP amplifier with four-level automatic or manual supply adjust

- -98-dB THD+N into 30  $\Omega$  with 10-mW output power

- 2 x 35 mW output power into 30  $\Omega$  with 0.018% THD+N

- · Load detection

- Headphone load detection of 15 or 30  $\Omega$

- Line-level load (3 k $\Omega$ ) with capacitance detection

- Headphone insertion/removal detection with WAKE

- Audio serial port (ASP)

- I<sup>2</sup>S (two channels) or TDM (up to four channels)

- Slave or Hybrid-Master Mode (bit-clock slave and LRCK/FSYNC derived from bit clock)

- Supports up to 32-bit audio

- Sample rate support for 8 to 192 kHz

- I<sup>2</sup>C control with interrupt output

- Integrated fractional-N PLL

- Increases system-clock flexibility for audio processing

- Reference clock sourced from I<sup>2</sup>S/TDM bit clock

- Bypassable SRCs for maximum flexibility

- · Attenuation, mute, and volume controls for each output

- · Integrated power management

- Digital core operates from either an external 1.2-V supply or LDO from a 1.8-V supply.

- Step-down charge pump improves HP efficiency

- Independent peripheral power-down controls

- Standby operation from VP with all other supplies powered off

- VP monitor to detect and report brownout conditions

- Low-impedance switching suppresses ground-noise

# **Applications**

- · Ultrabooks, tablets, and smartphones

- · Digital headsets

# **General Description**

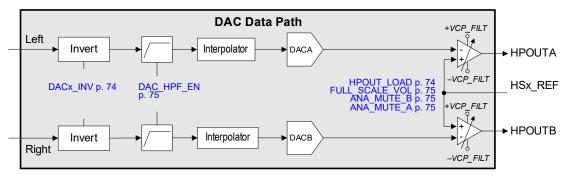

The CS43L36 is a low-power, high dynamic-range, stereo audio DAC with integrated I<sup>2</sup>S/I<sup>2</sup>C/TDM interfaces designed for portable applications. The CS43L36 features support for up to 32-bit audio inputs and includes bypassable SRCs.

The bypassable fractional-N PLL sourced from the ASP SCLK allows for maximum flexibility in any system.

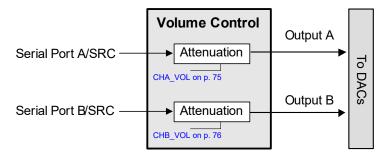

There is independent attenuation on each input along with volume adjustment and mute control.

The CS43L36 is available in 49-ball WLCSP package and a 40-pin QFN package, both supporting an extended commercial operational temperature range of –40°C to +85°C.

### **Table of Contents**

| 1 Pin Assignments and Descriptions                     | <b>. 3</b> 6   | 6.9 HP Control Registers                                                        | 56 |

|--------------------------------------------------------|----------------|---------------------------------------------------------------------------------|----|

| 1.1 WLCSP Pin Out (Through-Package View)               | . 3 6          | 5.10 Class H Registers                                                          |    |

| 1.2 QFN Pin Out (Through-Package View)                 |                | 6.11 Mixer Volume Registers                                                     | 56 |

| 1.3 Pin Descriptions                                   | . 4 6          | 6.12 AudioPort Interface Registers                                              | 56 |

| 1.4 Electrostatic Discharge (ESD) Protection Circuitry | . 6 6          | 5.13 SRC Registers                                                              | 57 |

| 2 Typical Connections                                  | . <b>9</b> 6   | 5.14 Serial Port Receive Registers                                              | 57 |

| 2.1 Electromagnetic Compatibility (EMC) Circuitry      | 10 6           | 6.15 ID Registers                                                               | 57 |

| 3 Characteristics and Specifications                   | 11 7 R         | egister Descriptions                                                            | 58 |

| 4 Functional Description                               | <b>19</b> 7    | ′.1 Global Registers                                                            | 58 |

| 4.1 Digital Volume Control                             | 20 7           | 7.1 Global Registers       5         7.2 Power Down and Headset Detects       6 | 31 |

| 4.2 Analog Output                                      |                | '.3 Clocking Registers                                                          |    |

| 4.3 Class H Amplifier                                  | 22 7           | '.4 Interrupt Registers                                                         | 66 |

| 4.4 Clocking Architecture                              | 27 7           | ′.5 Fractional-NັPLL Registers                                                  | 70 |

| 4.5 Audio Serial Port (ASP)                            | 33 7           | 7.6 HP Load-Detect Registers                                                    | 72 |

| 4.6 Sample-Rate Converters (SRCs)                      | 39 7           | 7.7 Headset Interface Registers                                                 |    |

| 4.7 Headset Interface                                  | 40 7           | 7.8 DAC Control Registers                                                       |    |

| 4.8 Plug Presence Detect                               |                | '.9 HP Control Register                                                         |    |

| 4.9 Power-Supply Considerations                        |                | ′.10 Class H Regišter                                                           |    |

| 4.10 Control-Port Operation                            | 43 7           | 7.11 Volume Control                                                             |    |

| 4.11 Reset                                             | 46 7           | '.12 AudioPort Interface Registers                                              | 76 |

| 4.12 Interrupts                                        | 46 7           | '.13 SRC Registers                                                              | 77 |

| 5 System Applications                                  | <b>47</b> 7    | '.14 Serial Port Receive Registers                                              | 77 |

| 5.1 Power-Up Sequence                                  | 47 7           | ′.15 ID Registers                                                               | 79 |

| 5.2 Power-Down Sequence                                | 49 8 PG        | CB Layout Considerations                                                        | 30 |

| 5.3 Page 0x30 Read Sequence                            | 50 8           | 8.1 Power Supply                                                                | 30 |

| 5.4 PLL Clocking                                       | 50 8           | 3.2 Groundina                                                                   | 30 |

| 5.5 VD FILT/VĽ ESD Diode                               | 50 8           | 3.2 Grounding                                                                   | 30 |

| 6 Register Quick Reference                             | 50 9 PI        | lots                                                                            | 31 |

| 6.1 Global Registers                                   | 51 9           | 9.1 Digital Filter Response                                                     | 81 |

| 6.2 Power-Down and Headset-Detect Registers            | 52 <b>10 F</b> | Package Dimensions                                                              | 35 |

| 6.3 Clocking Registers                                 | 52 1           | 0.1 WLCSP Package Dimensions                                                    | 35 |

| 6.4 Interrupt Registers                                |                | 0.2 QFN Package Dimensions                                                      |    |

| 6.5 Fractional-N PLL Registers                         |                |                                                                                 |    |

| 6.6 HP Load Detect Registers                           |                |                                                                                 |    |

| 6.7 Headset Interface Registers                        |                |                                                                                 |    |

|                                                        |                | Revision History                                                                |    |

# 1 Pin Assignments and Descriptions

This section shows pin assignments and describes pin functions.

# 1.1 WLCSP Pin Out (Through-Package View)

Figure 1-1. WLCSP Pin Diagram (Through-Package View)

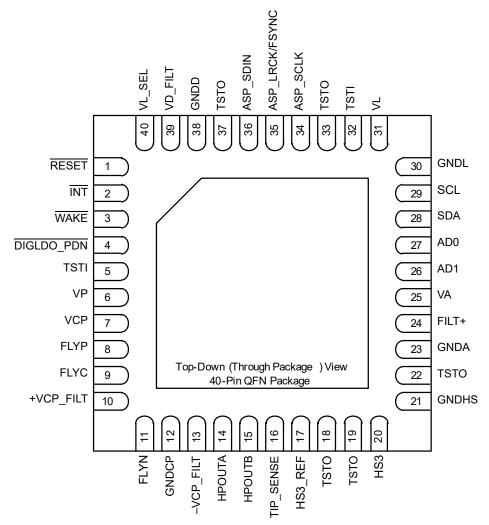

# 1.2 QFN Pin Out (Through-Package View)

Figure 1-2. QFN Pin Diagram

# 1.3 Pin Descriptions

Table 1-1. Pin Descriptions

| Pin Name           | CSP<br>Pin # | QFN<br>Pin # | Power Supply  | I/O | Pin Description                                                                                                               | Internal<br>Connection <sup>1</sup> | Driver | Receiver    | State at<br>Reset |

|--------------------|--------------|--------------|---------------|-----|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--------|-------------|-------------------|

|                    |              |              |               |     | Headphone 🃗                                                                                                                   |                                     |        |             |                   |

| HS3_REF            | G4           | 17           | VP            | I   | Headset Connection Reference. Input to pseudodifferential HP output reference                                                 | _                                   | _      | _           | Input             |

| HS3                | G2           | 20           | VP            | I   | Headset Connections. Input to headset and mic-button detection functions                                                      | _                                   | _      | <del></del> | Input             |

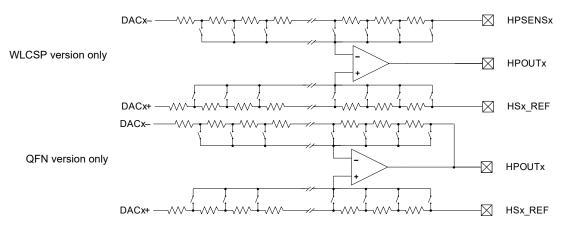

| HPOUTA<br>HPOUTB   | E5<br>G5     | 14<br>15     | ±VCP_<br>FILT | 0   | <b>Headphone Audio Output.</b> Ground-centered audio output.                                                                  | _                                   | _      | <del></del> |                   |

| HPSENSA<br>HPSENSB | D5<br>F5     | _            | ±VCP_<br>FILT | I   | <b>Headphone Audio Sense Input.</b> Audio sense input. WLCSP package only                                                     | _                                   | _      | <del></del> | Input             |

| TIP_SENSE          | E4           | 16           | VP            | I   | <b>Tip Sense.</b> Output can be set to wake the system. Independently configurable to be debounced on plug and unplug events. | —                                   | Hi-Z   | _           | _                 |

Table 1-1. Pin Descriptions (Cont.)

| Pin Name           | CSP<br>Pin # | QFN<br>Pin# | Power<br>Supply         | I/O  | Pin Description                                                                                                                                             | Internal<br>Connection <sup>1</sup> | Driver                                | Receiver                       | State at<br>Reset |

|--------------------|--------------|-------------|-------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|---------------------------------------|--------------------------------|-------------------|

|                    |              |             |                         |      | Digital I/O                                                                                                                                                 |                                     |                                       |                                |                   |

| AD0<br>AD1         | C3<br>B2     | 27<br>26    | VL                      | I    | <b>I<sup>2</sup>C Address Input.</b> Address pins for I <sup>2</sup> C Instance ID [1:0] input.                                                             | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| ASP_LRCK/<br>FSYNC | B5           | 35          | VL                      | I/O  | ASP Left/Right Clock or Frame Sync. Left or right word select, or frame start sync for the ASP interface.                                                   | _                                   | CMOS<br>output                        | Hysteresis<br>on CMOS<br>input | Input             |

| ASP_SCLK           | B4           | 34          | VL                      | I    | ASP/ Serial Data Clock. Serial data-shift clock for the ASP interface in I <sup>2</sup> S/TDM Mode. Source clock used for internal master clock generation. | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| ASP_SDIN           | A5           | 36          | VL                      | I/O  | ASP Serial Data Input. Serial data input and output in serial data input for the ASP interface in I <sup>2</sup> S/TDM mode.                                | _                                   | CMOS<br>output                        | Hysteresis<br>on CMOS<br>input | Input             |

| DIGLDO_PDN         | D4           | 4           | VP                      | I    | <b>Digital LDO Power Down.</b> Digital core logic LDO power down.                                                                                           | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| ĪNT                | В7           | 2           | VP                      | 0    | Interrupt output. Programmable, open-drain, active-low programmable interrupt output.                                                                       | _                                   | CMOS<br>open-drain<br>output          | _                              | Output            |

| RESET              | C5           | 1           | VP                      | I    | Reset. Hardware reset.                                                                                                                                      | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| SCL                | A2           | 29          | VL                      | I    | I <sup>2</sup> C Clock. Clock input for the I <sup>2</sup> C interface.                                                                                     | _                                   | _                                     | Hysteresis<br>on CMOS<br>input | Input             |

| SDA                | A1           | 28          | VL                      | I/O  | I2C Input/Output. I2C input and output.                                                                                                                     | _                                   | CMOS<br>open-drain<br>output          | Hysteresis<br>on CMOS<br>input | Input             |

| VL_SEL             | C4           | 40          | VP                      | I    | VL Supply Voltage Select. Select for VL power supply voltage level. Connect to VP for 1.8-V VL supply, connect to GNDD for 1.2-V VL supply                  | _                                   | Ė                                     | Hysteresis<br>on CMOS<br>input | Input             |

| WAKE               | C6           | 3           | VP                      | 0    | Wake up. Programmable, open-drain, active-low output. This outputs the state of the Mic S0 or HP wake detect.                                               | _                                   | Hi-Z,<br>CMOS<br>open-drain<br>output | <u> </u>                       | Output            |

|                    |              |             |                         |      | Charge Pump 🛑                                                                                                                                               |                                     |                                       |                                |                   |

| -VCP_FILT          | G6           | 13          | VCP/<br>VP <sup>2</sup> | 0    | <b>Inverting Charge Pump Filter Connection.</b> Power supply for the inverting charge pump that provides the negative rail for the HP amplifier.            | _                                   | _                                     | _                              | _                 |

| +VCP_FILT          | E6           | 10          | VCP/<br>VP <sup>2</sup> | 0    | Step Down Charge Pump Filter Connection. Power supply for the step down charge pump that provides the positive rail for the HP amplifier.                   | _                                   | _                                     | _                              | _                 |

| FLYC               | F7           | 9           | VCP/<br>VP <sup>2</sup> | 0    | Charge Pump Cap Common Node. Common positive node for the HP amplifiers' step-down and inverting charge pumps' flying capacitors.                           | _                                   | _                                     | _                              | _                 |

| FLYN               | G7           | 11          | VCP/<br>VP <sup>2</sup> | 0    | <b>Charge Pump Cap Negative Node.</b> Negative node for the inverting charge pump's flying capacitor.                                                       | _                                   | _                                     | _                              | _                 |

| FLYP               | E7           | 8           | VCP/<br>VP <sup>2</sup> | 0    | Charge Pump Cap Positive Node. Positive node for HP amps' step-down charge pump's flying capacitor.                                                         | _                                   | <del>-</del>                          | <del>_</del>                   | _                 |

|                    |              |             |                         |      | Power                                                                                                                                                       |                                     |                                       |                                |                   |

| FILT+              | C1           | 24          | VA                      | <br> | Positive Voltage Reference. Positive reference voltage for internal sampling circuits.                                                                      |                                     | _                                     | _                              | _                 |

| VA                 | B1           | 25          | N/A                     | I    | <b>Analog Power Supply.</b> Power supply for the internal analog section.                                                                                   |                                     |                                       |                                |                   |

| VCP                | D6           | 7           | N/A                     | I    | <b>Charge Pump Power.</b> Power supply for the internal HP amplifiers charge pump.                                                                          |                                     | _                                     |                                |                   |

| VD_FILT            | A7           | 39          | N/A                     | I    | <b>1.2-V Digital Core Power Supply.</b> Power supply for internal digital logic.                                                                            | _                                   | _                                     | _                              | _                 |

| VL                 | A3           | 31          | N/A                     | I    | I/O Power Supply. Power supply for external interface and internal digital logic.                                                                           | _                                   | _                                     | _                              | _                 |

| Pin Name | CSP<br>Pin #                 | QFN<br>Pin # | Power<br>Supply | I/O | Pin Description                                                                         | Internal<br>Connection <sup>1</sup> | Driver | Receiver | State at<br>Reset |

|----------|------------------------------|--------------|-----------------|-----|-----------------------------------------------------------------------------------------|-------------------------------------|--------|----------|-------------------|

| VP       | D7                           | 6            | N/A             | I   | <b>High Voltage Interface Supply.</b> Power supply for high voltage interface.          | _                                   | _      | _        | _                 |

|          |                              |              |                 |     | Ground 🔘                                                                                |                                     |        |          |                   |

| GNDA     | C2                           | 23           | N/A             | I   | <b>Analog Ground.</b> Ground reference for the internal analog section.                 | _                                   | _      | _        | _                 |

| GNDL     | В3                           | 30           | N/A             | I   | <b>Digital Ground.</b> Ground reference for interface section.                          | _                                   | _      | _        |                   |

| GNDHS    | G1                           | 21           | N/A             | I   | <b>Headset Ground.</b> Ground reference for the internal analog section.                | _                                   | _      | _        |                   |

| GNDCP    | F6                           | 12           | N/A             | I   | <b>Charge Pump Ground.</b> Ground reference for the internal HP amplifiers charge pump. | _                                   | _      | _        |                   |

| GNDD     | В6                           | 38           | N/A             | I   | <b>Digital Ground.</b> Ground reference for the internal digital circuits.              | _                                   | _      | _        |                   |

|          |                              |              |                 |     | Test                                                                                    |                                     |        |          |                   |

| TSTI     | C7                           | 5            | N/A             | I   | Test input. Connect to GNDD                                                             | _                                   | _      | _        | _                 |

| TSTI     | D3                           | 32           | VL              | ı   | Test input. Connect to GNDD.                                                            | _                                   | _      | _        | _                 |

| TSTI     | D1, E1,<br>E2, F1,<br>F2, G3 | _            | VP              | I   | Test input. Connect to GNDA.                                                            | _                                   | _      | _        | _                 |

| TSTI     | D2                           | _            | VA              | ı   | Test input. Connect to GNDA.                                                            | _                                   | _      | _        | _                 |

| TSTO     | A4, A6                       | 33,37        | VL              | 0   | Test output. No connection                                                              | _                                   | _      | _        | _                 |

| TSTO     | E3, F3,<br>F4                | 18,19,<br>22 | VP              | 0   | Test output. No connection                                                              | _                                   | _      | _        | _                 |

<sup>1.</sup> There are no internal connections for the CS43L36.

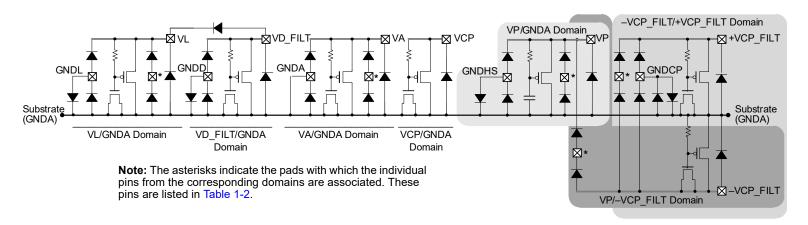

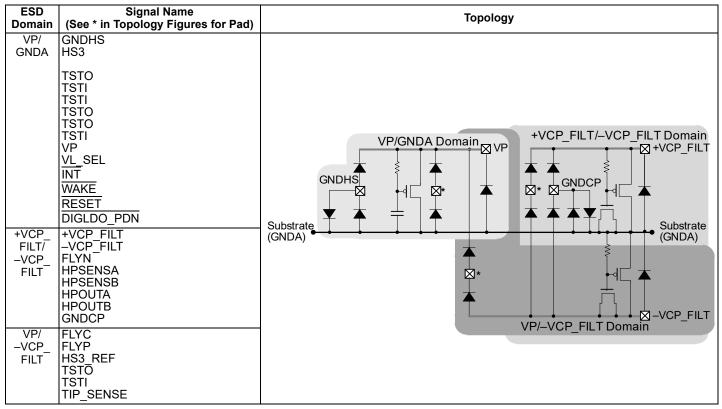

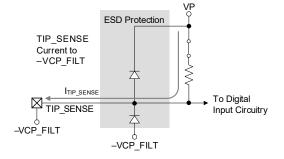

# 1.4 Electrostatic Discharge (ESD) Protection Circuitry

ESD-sensitive device. The CS43L36 is manufactured on a CMOS process. Therefore, it is generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken while handling and storing this device. This device is qualified to current JEDEC ESD standards.

Fig. 1-3 provides a composite view of the ESD domains showing the ESD protection paths between each pad and the substrate (GNDA) and the interrelations between some domains. Note that this figure represents the structure for the internal protection devices and that additional protections can be implemented as part of the integration into the board.

Figure 1-3. Composite ESD Topology

<sup>2.</sup> The power supply is determined by ADPTPWR setting (see Section 7.10.1). VP is used if ADPTPWR = 001 (VP\_CP Mode) or when necessary for ADPTPWR = 111 (Adapt-to-Signal Mode).

Table 1-2 shows the individual ESD domains and lists the pins associated with each domain.

Table 1-2. ESD Domains

| ESD<br>Domain    | Signal Name<br>(See * in Topology Figures for Pad)                              | Topology              |

|------------------|---------------------------------------------------------------------------------|-----------------------|

|                  | AD0 AD1 ASP_LRCK/FSYNC GNDL SCL SDA TSTO TSTO TSTI ASP_SCLK ASP_SDIN VD_FILT VL | Substrate (GNDA)      |

| VD_FILT/<br>GNDA | VD_FILT<br>GNDD<br>TSTI                                                         | Substrate (GNDA)      |

| GNDA             | FILT+<br>GNDA<br>TSTI<br>VA                                                     | GNDA Substrate (GNDA) |

| VCP/<br>GNDA     | VCP                                                                             | Substrate (GNDA)      |

#### Table 1-2. ESD Domains (Cont.)

<sup>1.</sup> See Section 5.5 for additional information regarding VD\_FILT and VL.

# 2 Typical Connections

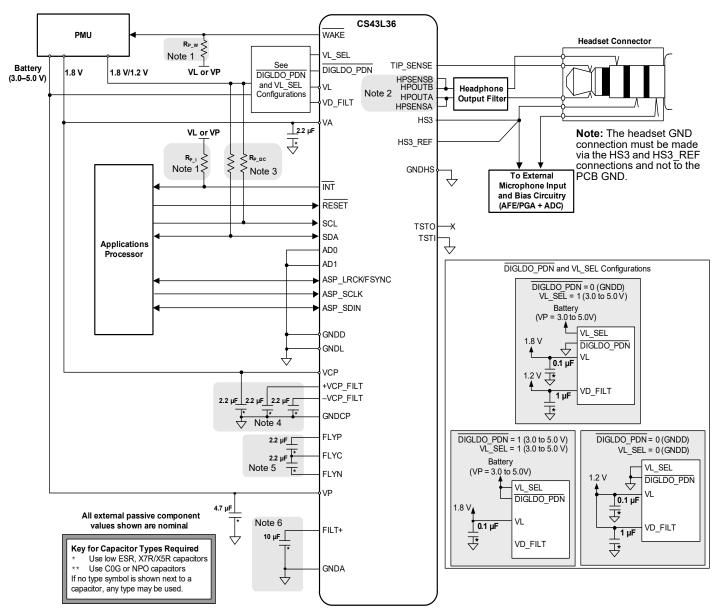

Figure 2-1. Typical Connection Diagram

#### Notes:

- 1. R<sub>P I</sub> and R<sub>P W</sub> values can be determined by the  $\overline{\text{INT}}$  and  $\overline{\text{WAKE}}$  pin specifications in Table 3-14.

- 2. HPSENSA and HPSENSB are supported only on the WLCSP package.

- 3. RP I2C values can be determined by the I2C pull-up resistance specification in Table 3-13.

- 4. The headphone amplifier's output power and distortion ratings use the nominal capacitances shown. Larger capacitance reduces ripple on the internal amplifiers' supplies and, in turn, reduces distortion at high-output power levels. Smaller capacitance may not reduce ripple enough to achieve output power and distortion ratings. Because actual values of typical X7R/X5R ceramic capacitors deviate from nominal values by a percentage specified in the manufacturer's data sheet, capacitors must be selected for minimum output power and maximum distortion required. Higher value capacitors than those shown may be used, however lower value capacitors must not (values can vary from the nominal by ±20%). See Section 2.1.2 for additional details.

- 5. Series resistance in the path of the power supplies must be avoided. Any voltage drop on VCP directly affects the negative charge-pump supply (–VCP\_FILT) and clips the audio output.

- 6. Lowering capacitance below the value shown affects PSRR, THD+N performance, and interchannel isolation and intermodulation.

# 2.1 Electromagnetic Compatibility (EMC) Circuitry

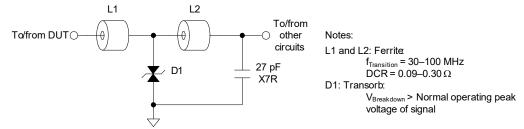

The circuit in Fig. 2-2 may be applied to signals not local to the CS43L36 (i.e., that traverse significant distances) for EMC.

Figure 2-2. Optional EMC Circuit

### 2.1.1 Low-Profile Charge-Pump Capacitors

In the typical connection for analog mics (Fig. 2-1), the recommended capacitor values for the charge-pump circuitry are 2.2 µF, rated as X7R/X5R or better. The following low-profile versions of these capacitors are suitable for the application:

- Description: 2.2 µF ±20%, 6.3 V, X5R, 0201

- Manufacturer, Part Number: Murata, GRM033R60J225ME47, nominal height = 0.3 mm

- Manufacturer, Part Number: AVX, 02016D225MAT2A, nominal height = 0.33 mm

**Note:** Although the 0201 capacitors described are suitable, larger capacitors such as 0402 or larger may provide acceptable performance.

## 2.1.2 Ceramic Capacitor Derating

Note 4 in Fig. 2-1 highlights that ceramic capacitor derating factors can significantly affect in-circuit capacitance values and, in turn, CS43L36 performance. Under typical conditions, numerous types and brands of large-value ceramic capacitors in small packages exhibit effective capacitances well below their ±20% tolerance, with some being derated by as much as –50%. These same capacitors, when tested by a multimeter, read much closer to their rated value. A similar derating effect has not been observed with tantalum capacitors.

The derating observed varied with manufacturer and physical size: Larger capacitors performed better, as did ones from Kemet Electronics Corp. and TDK Corp. of any size. This derating effect is described in data sheets and in applications notes from capacitor manufacturers. For instance, as DC and AC voltages are varied from the standard test points (applied DC and AC voltages for standard test points versus PSRR test are 0 and 1 V<sub>RMS</sub> @ 1 kHz versus 0.9 V and ~1 mV<sub>RMS</sub> @ 20 Hz–20 kHz), it is documented that the capacitances vary significantly.

# 3 Characteristics and Specifications

Table 3-1 defines parameters as they are characterized in this section.

Table 3-1. Parameter Definitions

| Parameter                                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                           | The ratio of the rms value of the signal to the rms sum of all other spectral components over the specified bandwidth. A signal-to-noise ratio measurement over the specified bandwidth made with a –60 dB signal; 60 dB is added to resulting measurement to refer the measurement to full scale. This technique ensures that distortion components are below the noise level and do not affect the measurement. This measurement technique has been accepted by the Audio Engineering Society, AES17–1991, and the Electronic Industries Association of Japan, EIAJ CP–307. Dynamic range is expressed in decibel units. |

| Idle channel noise                        | The rms value of the signal with no input applied (properly back-terminated analog input, digital zero, or zero modulation input). Measured over the specified bandwidth.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Interchannel isolation                    | A measure of cross talk between the left and right channel pairs. Interchannel isolation is measured for each channel at the converter's output with no signal to the input under test and a full-scale signal applied to the other channel. Interchannel isolation is expressed in decibel units.                                                                                                                                                                                                                                                                                                                         |

| Load resistance and capacitance           | The recommended minimum resistance and maximum capacitance required for the internal op-amp's stability and signal integrity. The load capacitance effectively moves the band-limiting pole of the amp in the output stage. Increasing load capacitance beyond the recommended value can cause the internal op-amp to become unstable.                                                                                                                                                                                                                                                                                     |

| Offset error                              | The deviation of the midscale transition (111111 to 000000) from the ideal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Output offset voltage                     | The DC offset voltage present at the amplifier's output when its input signal is in a mute state. The offset exists due to CMOS process limitations and is proportional to analog volume settings. When measuring the offset out the headphone amplifier, the headphone amplifier is ON.                                                                                                                                                                                                                                                                                                                                   |

| Total harmonic distortion + noise (THD+N) | The ratio of the rms sum of distortion and noise spectral components across the specified bandwidth (typically 20 Hz–20 kHz) relative to the rms value of the signal. THD+N is measured at –1 and –20 dBFS for the analog input and at 0 and –20 dB for the analog output, as suggested in AES17–1991 Annex A. THD+N is expressed in decibel units.                                                                                                                                                                                                                                                                        |

#### **Table 3-2. Recommended Operating Conditions**

Test conditions: GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground.

|                    | Parameters                                                           | Symbol            | Minimum <sup>1</sup> | Maximum <sup>1</sup> | Unit |

|--------------------|----------------------------------------------------------------------|-------------------|----------------------|----------------------|------|

| DC power           | Charge pump                                                          | VCP               | 1.66                 | 1.94                 | V    |

| supply             | LDO regulator for digital <sup>2</sup> DIGLDO_PDN = 0 and VL_SEL = 0 | VD_FILT           | 1.10                 | 1.30                 | V    |

|                    | Serial interface control port DIGLDO_PDN = 0 and VL_SEL = 0          | VL                | 1.10                 | 1.30                 | V    |

|                    | VL_SEL = 1                                                           | VL                | 1.66                 | 1.94                 | V    |

|                    | Analog                                                               | VA                | 1.66                 | 1.94                 | V    |

|                    | Battery supply                                                       | VP                | 2.50 <sup>3</sup>    | 5.25                 | V    |

| External voltage   | TIP_SENSE pin                                                        | V <sub>INHI</sub> | -VCP_FILT - 0.3      |                      | V    |

| applied to pin 4,5 | ±VCP_FILT domain pins 6                                              | $V_{VCPF}$        | -VCP_FILT - 0.3      | +VCP_FILT + 0.3      | V    |

|                    | VL domain pins                                                       | $V_{VL}$          | -0.3                 | VL + 0.3             | V    |

|                    | VA domain pins                                                       | $V_{VA}$          | -0.3                 | VA + 0.3             | V    |

|                    | VP domain pins                                                       | $V_{VP}$          | -0.3                 | VP + 0.3             | >    |

| Ambient tempera    | ature                                                                | T <sub>A</sub>    | -40                  | +85                  | °C   |

<sup>1.</sup>Device functional operation is guaranteed within these limits; operation outside them is not guaranteed or implied and may reduce device reliability.

### Table 3-3. Absolute Maximum Ratings

Test conditions: GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground.

|                            | Parameters                                                 | Symbol           | Minimum | Maximum | Unit |

|----------------------------|------------------------------------------------------------|------------------|---------|---------|------|

| DC power supply            | Charge pump, LDO, serial/control, analog (see Section 4.9) | VL, VA, VCP      | -0.3    | 2.33    | V    |

|                            | Digital core                                               | VD_FILT          | -0.3    | 1.55    | V    |

|                            | Battery                                                    | VP               | -0.3    | 6.3     | V    |

| Input current <sup>1</sup> |                                                            | l <sub>in</sub>  | _       | ±10     | mA   |

| Ambient operating temperat | ture (power applied)                                       | T <sub>A</sub>   | -50     | +115    | °C   |

| Storage temperature        |                                                            | T <sub>stg</sub> | -65     | +150    | ç    |

Caution: Stresses beyond "Absolute Maximum Ratings" levels may cause permanent damage to the device. These levels are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in Table 3-2, "Recommended Operating Conditions" is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2.</sup>If DIGLDO PDN is deasserted, no external voltage must be applied to VD FILT.

<sup>3.</sup>Although device operation is guaranteed down to 2.5 V, device performance is guaranteed only down to 3.0 V. The following are affected when VP < 3.0 V: charge pump LDO, TIP\_SENSE threshold.

<sup>4.</sup> The maximum over/undervoltage is limited by the input current.

<sup>5.</sup> Table 1-1 lists the power supply domain in which each CS43L36 pin resides.

<sup>6.±</sup>VCP FILT is specified in Table 3-8.

<sup>1.</sup> Any pin except supply pins. Transient currents of up to ±100 mA on analog input pins do not cause SCR latch-up.

### Table 3-4. Combined DAC Digital, On-Chip Analog, and HPOUTx Filter Characteristics

Test conditions (unless specified otherwise): T<sub>A</sub> = +25°C; MCLK = 12 MHz, MCLK\_SRC\_SEL = 0, Fs<sub>INT</sub> = 48 kHz; path is internal routing engine to HPOUTx, analog and digital gains are all set to 0 dB; HPF disabled.

| Parameter <sup>1</sup>                                                                                                                          | Minimum | Typical                | Maximum | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------------|---------|-------------------|

| Passband –0.05-dB corner                                                                                                                        | _       | 0.48                   | _       | Fs <sub>INT</sub> |

| -3.0-dB corner                                                                                                                                  | _       | 0.50                   | _       | Fs <sub>INT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>INT</sub> to 0.417 Fs <sub>INT</sub> ; normalized to 0.417x10 <sup>-3</sup> Fs <sub>INT</sub> ) | -0.04   | _                      | 0.063   | dB                |

| Stopband attenuation (0.545 Fs <sub>INT</sub> to Fs <sub>INT</sub> )                                                                            | 60      | _                      | _       | dB                |

| Total group delay <sup>2</sup>                                                                                                                  | _       | 5.35/Fs <sub>INT</sub> | _       | S                 |

<sup>1.</sup> Response scales with Fs<sub>INT</sub> (based on internal MCLK). Specifications are normalized to Fs<sub>INT</sub> and denormalized by multiplying by Fs<sub>INT</sub>.

#### Table 3-5. DAC High-Pass Filter (HPF) Characteristics

Test conditions (unless specified otherwise) Analog and digital gains are all set to 0 dB; T<sub>A</sub> = +25°C.

| Parameter <sup>1</sup>                                                                                                         | Minimum | Typical                                 | Maximum | Unit              |

|--------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------|---------|-------------------|

| Passband -0.05-dB corner                                                                                                       | _       | 0.180x10 <sup>-3</sup>                  | _       | Fs <sub>INT</sub> |

| -3.0-dB corner                                                                                                                 | _       | 19.5x10 <sup>-6</sup>                   | _       | Fs <sub>INT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>INT</sub> to 0.417 Fs <sub>INT</sub> ; normalized to 0.417 Fs <sub>INT</sub> ) | _       | _                                       | 0.01    | dB                |

| Phase deviation @ 0.453x10 <sup>-3</sup> Fs <sub>INT</sub>                                                                     | _       | 2.45                                    | _       | ٥                 |

| Filter settling time <sup>2</sup>                                                                                              | _       | 24.5x10 <sup>3</sup> /Fs <sub>INT</sub> | _       | S                 |

<sup>1.</sup> Response scales with Fs<sub>INT</sub> (internal sample rate, based on MCLK). Specifications are normalized to Fs<sub>INT</sub> and are denormalized by multiplying by Fs<sub>INT</sub>.

#### Table 3-6. SDIN to HPOUTx with SRC-Enabled Datapath Characteristics

Test conditions (unless specified otherwise): LRCK =  $Fs_{INT}$  =  $Fs_{EXT}$  = 48 kHz; MCLK = 12 MHz; HPF disabled; passband/stopband levels normalized to 0.417x10<sup>-3</sup>  $Fs_{EXT}$ ; entire path characteristics including serial port + SRC + DAC + HPOUT.

| Parameters <sup>1</sup>                                                                                                                         | Minimum | Typical                                                 | Maximum              | Unit              |

|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------|----------------------|-------------------|

| Passband –0.2-dB corner                                                                                                                         | _       | 0.463                                                   | _                    | Fs <sub>EXT</sub> |

| -3.0-dB corner                                                                                                                                  |         | 0.466                                                   |                      | Fs <sub>EXT</sub> |

| Passband ripple (0.417x10 <sup>-3</sup> Fs <sub>EXT</sub> to 0.417 Fs <sub>EXT</sub> ; normalized to 0.417x10 <sup>-3</sup> Fs <sub>EXT</sub> ) | -0.16   | _                                                       | 0.02                 | dB                |

| Response at 0.5 Fs <sub>EXT</sub>                                                                                                               | _       | _                                                       | -54.9                | dB                |

| Stopband rejection from 0.480 Fs <sub>EXT</sub> to 0.524 Fs <sub>EXT</sub>                                                                      | 55      | _                                                       | _                    | dB                |

| Stopband rejection from 0.524 Fs <sub>EXT</sub> to 0.545 Fs <sub>EXT</sub>                                                                      | 39      | _                                                       | _                    | dB                |

| Stopband rejection from 0.545 Fs <sub>EXT</sub> to 3 Fs <sub>EXT</sub>                                                                          | 60      | _                                                       | _                    | dB                |

| Square wave overshoot                                                                                                                           | _       | _                                                       | 3.1                  | dB                |

| Group delay, bark-weighted average                                                                                                              | _       | _                                                       | 34/Fs <sub>EXT</sub> | S                 |

| Group delay $Fs_{EXT} \le 48 \text{ kHz}$                                                                                                       | _       | (15.8 ± 1.5)/Fs <sub>EXT</sub> + 10.3/Fs <sub>INT</sub> | _                    | S                 |

| $Fs_{EXT} \ge 88.2 \text{ kHz}$                                                                                                                 |         | $(20.1 \pm 1)/Fs_{EXT} + (11.6 \pm 0.5)/Fs_{INT}$       | _                    | s                 |

| SRC disabled group delay <sup>2</sup>                                                                                                           | _       | (15±1)/Fs                                               | _                    | S                 |

$<sup>1.</sup>Fs_{EXT}$  is the external sample rate (LRCK/FSYNC frequency). Response scales with  $Fs_{EXT}$ .

<sup>2.</sup>Informational only; group delay cannot be measured for this block by itself. An additional 5.5/Fs<sub>int</sub> group delay may be present through the serial ports and internal audio bus.

<sup>2.</sup> Required time for the magnitude of the DC component present at the output of the HPF to reach 5% of the applied DC signal.

<sup>2.</sup> This value varies by up to 1 Fs. If SRC is disabled, Fs =  $Fs_{OUT}$  =  $Fs_{IN}$ .

### Table 3-7. Serial Data In-to-HPOUTx Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; input test signal is a 24-bit full-scale 997-Hz sine wave with 1 LSB of triangular PDF dither applied; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; parameters can vary with VA; typical performance data taken with VL = VA = 1.8 V, VP = 3.6 V; min/max performance data taken with VA = 1.66–1.94 V; VL = 1.8 V, VP = 3.6 V; VCP Mode;  $T_A = +25^{\circ}C$ ; measurement bandwidth is 20 Hz–20 kHz; ASP\_LRCK =  $F_{SINT} = 48$ -kHz mode; MCLK = 12 MHz, MCLK\_SRC\_SEL = 0; volume = 0 dB; FULL\_SCALE\_VOL = 0 (0dB); HP load:  $R_L = 30 \Omega$ ,  $R_L = 10 \Omega$ ,  $R_L = 10$

|                         | Parameter <sup>1</sup>                               |                  |                                  | Minimum     | Typical    | Maximum    | Unit            |

|-------------------------|------------------------------------------------------|------------------|----------------------------------|-------------|------------|------------|-----------------|

| $R_L = 3 k\Omega$       | Dynamic range                                        | 18–24 bit        | A-weighted                       | 108         | 114        | _          | dB              |

| VP_CP Mode              | (defined in Table 3-1)                               |                  | unweighted                       | 105         | 111        | _          | dB              |

|                         | THD+N <sup>2</sup> (defined in Table 3-1)            | 18–24 bit        | 0 dB                             | _           | -90        | -84        | dB              |

|                         |                                                      |                  | –20 dB                           |             | -83        | _          | dB              |

|                         |                                                      |                  | -60 dB                           |             | -51        | -48        | dB              |

|                         | 1                                                    | 16 bit           | 0 dB                             |             | -88        | -82        | dB              |

|                         |                                                      |                  | −20 dB<br>−60 dB                 |             | -73<br>-33 | <br>_27    | dB<br>dB        |

|                         | Idle channel noise (A-weighted)                      |                  | _00 ub                           | _           | 2.0        | -21<br>-   | μV              |

|                         | ` ,                                                  |                  |                                  | 4.50.1/4    |            |            |                 |

| <b>D</b> 00 0           | Full-scale output voltage 3                          | 10.0413          | A                                | 1.50•VA     | 1.58•VA    | 1.66•VA    | V <sub>PP</sub> |

| $R_L = 30 \Omega$       | Dynamic range (defined in Table 3-1)                 | 18–24 bit        | A-weighted                       | 108         | 114        | _          | dB              |

| VP_CP Mode              | TUD:NO.41                                            |                  | unweighted                       | 105         | 111        | _          | dB              |

|                         | THD+N <sup>2</sup> (defined in Table 3-1)            |                  | Pout = 10 mW<br>Pout = 35 mW     |             | -98<br>-75 | <u> </u>   | dB<br>dB        |

|                         | Trill cools sutput valtage 3                         |                  | Pout - 35 IIIVV                  | <br>1.50•VA | 1.58•VA    | 1.66•VA    |                 |

|                         | Full-scale output voltage <sup>3</sup>               |                  |                                  | 1.5U•VA     |            |            | V <sub>PP</sub> |

|                         | Output power <sup>2</sup>                            |                  |                                  |             | 35.0       | _          | mW              |

| $R_L = 15 \Omega$       | Dynamic range (defined in Table 3-1)                 | 18–24 bit        | A-weighted                       | 102         | 108        | _          | dB              |

| VCP Mode<br>(FULL SCALE | TUD NO (1 C 1 : T 1 1 0 4)                           |                  | unweighted                       | 99          | 105        | _          | dB              |

| VOL = 1 [-6 dB])        | THD+N <sup>2</sup> (defined in Table 3-1)            |                  | Pout = 17.3 mW                   | —           | -75        | <b>-69</b> | dB              |

| VOL I[ OUD])            | Full-scale output voltage 3                          |                  |                                  | 0.71•VA     | 0.79•VA    | 0.86•VA    | $V_{PP}$        |

|                         | Output power <sup>2</sup>                            |                  |                                  | _           | 17.3       | _          | mW              |

| $R_L = 15 \Omega$       | Dynamic range                                        | 18–24 bit        | A-weighted                       | 102         | 108        | _          | dB              |

| VP_CP Mode              |                                                      |                  | unweighted                       | 99          | 105        | _          | dB              |

| Other characteristics   | Interchannel isolation $^3$ (3 k $\Omega$ )          |                  | 217 Hz                           | _           | 90         | _          | dB              |

| (Table 3-1 gives        |                                                      |                  | 1 kHz                            | _           | 90         | _          | dB              |

| parameter definitions.) |                                                      |                  | 20 kHz                           |             | 80         |            | dB              |

|                         | Interchannel isolation $^3$ (30 $\Omega$ )           |                  | 217 Hz                           | _           | 90         | _          | dB              |

|                         |                                                      |                  | 1 kHz<br>20 kHz                  |             | 90<br>70   |            | dB<br>dB        |

|                         | Output offset voltage: mute <sup>3,4</sup> (ANA MUTE | = x = 1 coo n 75 |                                  |             | ±0.5       | ±1.0       | mV              |

|                         | Output offset voltage. Thate 3.4                     | X = 1, See p. 75 | HPOUTX                           |             | ±0.5       | ±2.5       | mV              |

|                         |                                                      |                  |                                  |             |            |            |                 |

|                         | Load resistance (R <sub>L</sub> )                    |                  | Normal operation <sup>3</sup>    | 15          |            | _          | Ω               |

|                         | Load capacitance (C <sub>L</sub> ) <sup>3,5</sup>    |                  | HPOUT_LOAD = 0<br>HPOUT_LOAD = 1 | _<br>_      | _          | 1<br>10    | nF<br>nF        |

|                         | Turn on time 6                                       | CL CVA           |                                  |             |            |            |                 |

|                         | Turn-on time <sup>6</sup>                            | SLOW             | /_START_EN = 000                 |             | _          | 25         | ms              |

<sup>1.</sup> One LSB of triangular PDF dither is added to data.

<sup>3.</sup>HP output test configuration. Symbolized component values are specified in the test conditions above.

<sup>4.</sup>Assumes no external impedance on HSx/HSx\_REF. External impedance on HSx/HSx\_REF affects the offset and step deviation. See Section 4.2.1. 5.Amplifier is guaranteed to be stable with either headphone load setting.

<sup>2.</sup>Because VCP settings lower than VA reduce the HP amplifier headroom, the specified THD+N performance at full-scale output voltage and power may not be achieved.

<sup>6.</sup> Turn-on time is measured from when the HP\_PDN = 0 ACK signal is received to when the signal appears on the HP output. In most cases, enabling the SRC increases the turn-on time and may exceed the maximum specified value.

#### Table 3-8. DC Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; VL = VCP = VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C.

|                           | Parameters                                                   |             | Minimum | Typical | Maximum | Unit |

|---------------------------|--------------------------------------------------------------|-------------|---------|---------|---------|------|

| VCP_FILT (No load         | VP_CP Mode (ADPTPWR = 001)                                   | +VCP_FILT   | _       | 2.6     | _       | V    |

| connected to HPOUTx.)     |                                                              | -VCP_FILT   | _       | -2.6    | _       | V    |

|                           | VCP Mode (ADPTPWR = 010)                                     | +VCP_FILT   | _       | VCP     | _       | V    |

|                           |                                                              | -VCP_FILT   | _       | -VCP    | _       | V    |

|                           | VCP/2 Mode (ADPTPWR = 011)                                   | +VCP_FILT   | _       | VCP/2   | _       | V    |

|                           |                                                              | -VCP_FILT   | _       | -VCP/2  | _       | V    |

|                           | VCP/3 Mode (ADPTPWR = 100)                                   | +VCP_FILT   | _       | VCP/3   | _       | V    |

|                           |                                                              | -VCP_FILT   | _       | -VCP/3  | _       | V    |

| HS3 ground switch resista | ance (Typical values have ±25% tolerance.)                   |             | _       | 0.5     | _       | Ω    |

| Other DC filter           | FILT+ voltage                                                |             | _       | VA      | _       | V    |

|                           | HP output current limiter on threshold. See Section 4.3.4. 1 |             | 80      | 115     | 160     | mA   |

|                           | VD_FILT and VL power-on reset threshold (VPOR)               | Up          | _       | 0.777   | _       | V    |

|                           |                                                              | Down        | _       | 0.628   | _       | V    |

| HPOUT pull-down           | HPOUT_PULLDOWN = 000                                         |             |         | 0.9     | _       | kΩ   |

| resistance 2,3            | HPOUT_PULLI                                                  |             |         | 9.3     |         | kΩ   |

|                           | HPOUT_PULLI                                                  | DOWN = 1010 | _       | 5.8     | _       | kΩ   |

<sup>1.</sup> The HP output current limiter threshold spec is valid only while the Class H rails are in VCP Mode.

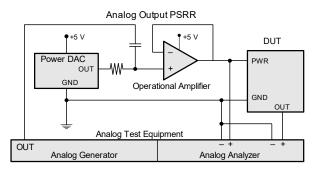

### Table 3-9. Power-Supply Rejection Ratio (PSRR) Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; input test signal held low (all zero data); GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; VL = VA = 1.8 V, VP = 3.6 V; T<sub>A</sub> = +25°C.

| Parameters <sup>1</sup>                                         |        | Minimum | Typical | Maximum | Unit |

|-----------------------------------------------------------------|--------|---------|---------|---------|------|

| HPOUTx (-6-dB analog gain)                                      | 217 Hz | _       | 75      | _       | dB   |

| PSRR with 100-mVpp signal AC coupled to VA supply <sup>2</sup>  | 1 kHz  | _       | 75      | _       | dB   |

|                                                                 | 20 kHz | _       | 70      | _       | dB   |

| HPOUTx (-6-dB analog gain)                                      | 217 Hz | _       | 85      | _       | dB   |

| PSRR with 100-mVpp signal AC-coupled to VCP supply <sup>2</sup> | 1 kHz  | _       | 85      | _       | dB   |

|                                                                 | 20 kHz | _       | 65      | _       | dB   |

| HPOUTx (0-dB analog gain)                                       | 217 Hz | _       | 80      | _       | dB   |

| PSRR with 100-mVpp signal AC coupled to VP supply               | 1 kHz  | _       | 80      | _       | dB   |

|                                                                 | 20 kHz | _       | 60      | _       | dB   |

<sup>1.</sup>PSRR test configuration: Typical PSRR can vary by approximately 6 dB below the indicated values.

2. No load connected to any analog outputs.

<sup>2.</sup> Typical values have ±20% tolerance.

<sup>3.</sup> Clamp is disabled (HPOUT CLAMP = 1) and channel is powered down (HPOUT PDN = 1).

#### **Table 3-10. Power Consumption**

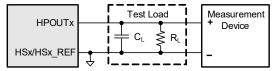

Test conditions (unless specified otherwise): Fig. 2-1 shows CS43L36 connections; GNDA = GNDL = GNDCP = 0 V; voltages are with respect to ground; performance data taken with VA = VCP = VL = 1.8 V;  $\overline{DIGLDO\_PDN}$  is deasserted; VP = 3.6 V;  $T_A$  = +25°C; ASP\_LRCK = 48-kHz Mode;  $F_{SINT}$  = 48 kHz; SCLK = 12 MHz, MCLK\_SRC\_SEL = 0; volume= 0 dB;  $F_{SINT}$  = 40 kHz; no signal on any input; control port inactive; input clock/data are held low when not required; test load is  $R_L$  = 30  $\Omega$  and  $R_L$  = 1 nF for HPOUTx; measured values include currents consumed by the DAC and do not include current delivered to external loads unless specified otherwise (e.g., HPOUTx); see Fig. 3-1.

|   | Use Cases |                        |                                          | ClassH | Typical Current (μA) |                  |                 |     | Total Power |  |

|---|-----------|------------------------|------------------------------------------|--------|----------------------|------------------|-----------------|-----|-------------|--|

|   |           |                        |                                          | Mode   | i <sub>VA</sub>      | i <sub>VCP</sub> | i <sub>VL</sub> | İγΡ | (µW)        |  |

| 1 | Α         | Off <sup>1</sup>       |                                          | _      | 0                    | 0                | 0               | 3.1 | 11.16       |  |

| 2 | Α         | Standby <sup>2,3</sup> |                                          | _      | 0                    | 0                | 0               | 20  | 72.0        |  |

| 3 | Α         | Standby (RCO Mode) 4,5 |                                          | _      | 0                    | 0                | 343             | 31  | 729         |  |

| 4 | Α         | Playback               | Stereo HPOUT (no signal, HPOUT_LOAD = 0) | VCP/3  | 1413                 | 1204             | 858             | 58  | 6464        |  |

|   | В         |                        | Stereo HPOUT (0.1 mW, HPOUT_LOAD = 0)    | VCP/3  | 1441                 | 2336             | 965             | 58  | 8744        |  |

- 1. Off configuration: Clock/data lines held low; RESET = LOW; VA = VL = VCP = 0 V; VP = 3.6 V.

- 2.Standby configuration: Clock/data lines held low; VA = VL = VCP = 0 V; VP = 3.6 V; M HP WAKE = 0 (unmasked).

- 3.SCLK PRESENT = 1.

- 4.SCLK PRESENT = 0 (RCO clocking).

- 5. Standby configuration (RCO clocking): Clock/data lines held low; VA = 0 V; VL = 1.8 V, VCP = 0 V, VP = 3.6 V; M\_HP\_WAKE = 0 (unmasked).

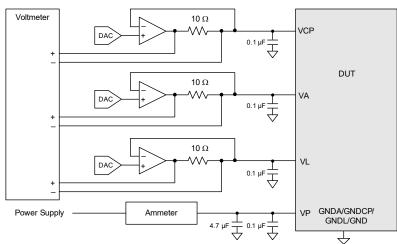

**Note:** The current draw on the VA, VCP, and VL power supply pins is derived from the measured voltage drop across a 10- $\Omega$  series resistor between the associated supply source and each voltage supply pin. Given the larger currents that are possible on the VP supply, an ammeter is used for the measurement.

Figure 3-1. Power Consumption Test Configuration

**Table 3-11. Register Field Settings**

|   |              |   |             | Register Fields and S | ettings               |

|---|--------------|---|-------------|-----------------------|-----------------------|

|   | Use<br>Cases |   | ASP_DAI_PDN | HP_PDN                | Class H Mode<br>p. 22 |

| 1 | Α            |   |             | _                     | _                     |

| 2 | Α            | 1 | _           | _                     | _                     |

| 3 | Α            | 1 | _           | _                     | _                     |

| 4 | Α            | 0 | 0           | 0                     | VCP/3                 |

|   | В            | 0 | 0           | 0                     | VCP/3                 |

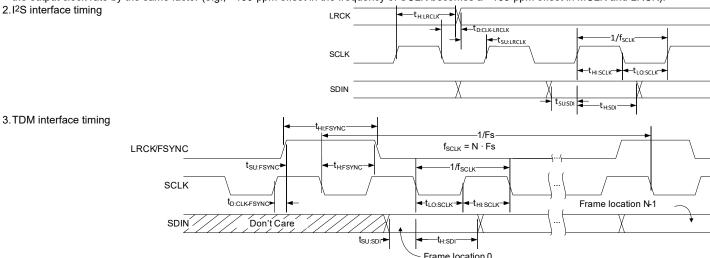

### Table 3-12. Digital Audio Interface Timing Characteristics

Test conditions (unless specified otherwise): GNDA = GNDL = GNDCP = 0 V; all voltages with respect to ground; values are for both VL = 1.2 and 1.8 V; inputs: Logic 0 = GNDL = 0 V, Logic 1 = VL;  $T_A$  = +25°C;  $C_{LOAD}$  = 30 pF (for VL = 1.2 V) and 60 pF (for VL = 1.8 V); input timings are measured at  $V_{IL}$  and  $V_{IH}$  thresholds; output timings are measured at  $V_{OL}$  and  $V_{OH}$  thresholds (see Table 3-14); ASP\_TX\_HIZ\_DLY = 00.

|        | Parameters 1,2,3                                                        | Symbol                | Minimum             | Typical | Maximum                 | Unit |

|--------|-------------------------------------------------------------------------|-----------------------|---------------------|---------|-------------------------|------|

| _      | CLK frequency <sup>4</sup>                                              | f <sub>SCLK</sub>     | 0.973 [5]           | _       | 25.81                   | MHz  |

|        | igh period <sup>4</sup>                                                 | t <sub>HI:SCLK</sub>  | 18.5                |         | _                       | ns   |

|        | ow period <sup>4</sup>                                                  | t <sub>LO:SCLK</sub>  | 18.5                | _       | _                       | ns   |

|        | uty cycle <sup>4</sup>                                                  | _                     | 45                  | _       | 55                      | %    |

| 1      | FSYNC/LRCK frame rate                                                   | _                     | 0.99                |         | 1.01                    | Fs   |

| Master | LRCK duty cycle                                                         | _                     | 45                  | _       | 55                      | %    |

| Mode   | FSYNC high period <sup>6</sup>                                          | t <sub>HI:FSYNC</sub> | 1/f <sub>SCLK</sub> | _       | (n-1)/f <sub>SCLK</sub> | S    |

|        | FSYNC/LRCK delay time after SCLK launching edge <sup>7</sup> VL = 1.8 V | D.OLIN-LINON          | 0                   | _       | 15                      | ns   |

|        | VL = 1.2 V                                                              |                       | 0                   |         | 17                      | ns   |

|        | SDIN setup time before SCLK latching edge <sup>7</sup>                  | t <sub>SU:SDI</sub>   | 10                  | _       | _                       | ns   |

|        | SDIN hold time after SCLK latching edge <sup>7</sup>                    | t <sub>H:SDI</sub>    | 5                   | _       | _                       | ns   |

| Slave  | FSYNC/LRCK frame rate                                                   | _                     | 0.99                | _       | 1.01                    | Fs   |

| Mode   | FSYNC/LRCK duty cycle                                                   | _                     | 45                  |         | 55                      | %    |

|        | FSYNC/LRCK setup time before SCLK latching edge <sup>7</sup>            | t <sub>SU:LRCK</sub>  | 10                  | _       | _                       | ns   |

|        | FSYNC/LRCK hold time after SCLK latching edge <sup>7</sup>              | t <sub>H:LRCK</sub>   | 5                   |         | _                       | ns   |

|        | SDIN hold time after SCLK latching edge <sup>7</sup>                    | t <sub>H:SDI</sub>    | 5                   |         | _                       | ns   |

|        | FSYNC/LRCK duty cycle                                                   | _                     | 45                  |         | 55                      | %    |

1. Output clock frequencies follow SCLK frequency proportionally. Deviation of the bit-clock source from nominal supported rates is directly imparted to the output clock rate by the same factor (e.g., +100-ppm offset in the frequency of SCLK becomes a +100-ppm offset in MCLK and LRCK).

- 4.SCLK is mastered from an external device. The external device is expected to maintain SCLK timing specifications.

- 5. SCLK operation below 2.8224 MHz may result in degraded performance.

- 6.Maximum LRCK duty cycle is equal to frame length, in SCLK periods, minus 1. Maximum duty cycle occurs when LRCK\_HI is set to 511 SCLK periods and LRCK period is set to 512 SCLK periods.

- 7. Data is latched on the rising or falling edge of SCLK, as determined by ASP\_SCPOL\_IN\_x and ASP\_FSD (See Section 7.3.6 and Section 7.3.7).

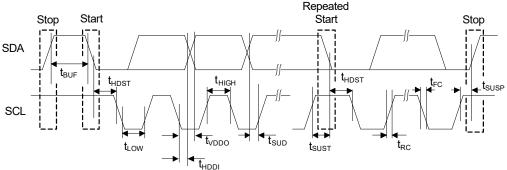

#### Table 3-13. I<sup>2</sup>C Slave Port Characteristics

Test conditions (unless specified otherwise): Fig. 2-1 shows typical connections; Inputs: GNDA = GNDL = GNDCP = 0 V; all voltages with respect to ground; min/max performance data taken with VL = 1.66–1.94 V (VL\_SEL = VP) or VL = 1.1–1.3 V (VL\_SEL = GNDD); inputs: Logic 0 = GNDA = 0 V, Logic 1 = VL;  $T_A = +25^{\circ}C$ ; SDA load capacitance equal to maximum value of  $C_B = 400$  pF; minimum SDA pull-up resistance,  $R_{P(min)}$ . Table 3-1 describes some parameters in detail. All specifications are valid for the signals at the pins of the CS43L36 with the specified load capacitance.

| Parameter <sup>2</sup>                               |                | Symbol <sup>3</sup> | Minimum | Maximum | Unit |

|------------------------------------------------------|----------------|---------------------|---------|---------|------|

| SCL clock frequency                                  |                | f <sub>SCL</sub>    | _       | 1000    | kHz  |

| Clock low time                                       |                | $t_{LOW}$           | 500     | _       | ns   |

| Clock high time                                      |                | t <sub>HIGH</sub>   | 260     | _       | ns   |

| Start condition hold time (before first clock pulse) |                | t <sub>HDST</sub>   | 260     | _       | ns   |

| Setup time for repeated start                        |                | t <sub>SUST</sub>   | 260     | _       | ns   |

| Rise time of SCL and SDA                             | Standard Mode  | t <sub>RC</sub>     | _       | 1000    | ns   |

|                                                      | Fast Mode      |                     | _       | 300     | ns   |

|                                                      | Fast Mode Plus |                     | _       | 120     | ns   |

### Table 3-13. I<sup>2</sup>C Slave Port Characteristics (Cont.)

Test conditions (unless specified otherwise): Fig. 2-1 shows typical connections; Inputs: GNDA = GNDL = GNDCP = 0 V; all voltages with respect to ground; min/max performance data taken with VL = 1.66-1.94 V (VL\_SEL = VP) or VL = 1.1-1.3 V (VL\_SEL = GNDD); inputs: Logic 0 = GNDA = 0 V, Logic 1 = VL;  $T_A$  =  $+25^{\circ}$ C; SDA load capacitance equal to maximum value of  $C_B$  = 400 pF; minimum SDA pull-up resistance,  $R_{P(min)}$ . Table 3-1 describes some parameters in detail. All specifications are valid for the signals at the pins of the CS43L36 with the specified load capacitance.

| Parameter <sup>2</sup>                                  |                          | Symbol <sup>3</sup> | Minimum | Maximum | Unit |

|---------------------------------------------------------|--------------------------|---------------------|---------|---------|------|

| Fall time of SCL and SDA                                | Standard Mode            | t <sub>FC</sub>     | _       | 300     | ns   |

|                                                         | Fast Mode                |                     | _       | 300     | ns   |

|                                                         | Fast Mode Plus           |                     | _       | 120     | ns   |

| Setup time for stop condition                           |                          | t <sub>SUSP</sub>   | 260     | _       | ns   |

| SDA setup time to SCL rising                            |                          | t <sub>SUD</sub>    | 50      | _       | ns   |

| SDA input hold time from SCL falling <sup>4</sup>       |                          | t <sub>HDDI</sub>   | 0       | _       | ns   |

| Output data valid (Data/Ack) <sup>5</sup>               | Standard Mode            | $t_{VDDO}$          | _       | 3450    | ns   |

|                                                         | Fast Mode                |                     | _       | 900     | ns   |

|                                                         | Fast Mode Plus           |                     | _       | 450     | ns   |

| Bus free time between transmissions                     |                          | t <sub>BUF</sub>    | 500     | _       | ns   |

| SDA bus capacitance                                     | Fast Mode Plus           | C <sub>B</sub>      | _       | 550     | pF   |

|                                                         | Standard Mode, Fast Mode |                     | _       | 400     | pF   |

| SCL/SDA pull-up resistance 1                            | VL = 1.2 V               | $R_P$               | 200     | _       | Ω    |

|                                                         | VL = 1.8 V               |                     | 250     | _       | Ω    |

| Switching time between RCO and PLL or SCLK <sup>6</sup> |                          | _                   | 150     | _       | μs   |