Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

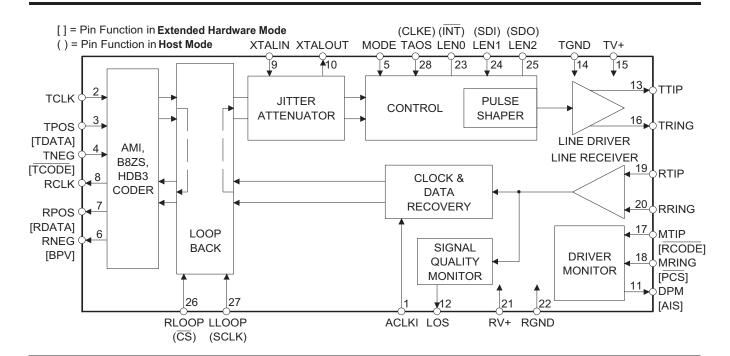

# T1/E1 Line Interface

#### **Features**

- Provides Analog PCM Line Interface for T1 and E1 Applications

- Provides Line Driver, and Data and Clock Recovery Functions

- Transmit Side Jitter Attenuation

Starting at 6 Hz, with > 300 UI of Jitter

Tolerance

- Low Power Consumption (typically 175 mW)

- B8ZS/HDB3/AMI Encoders/Decoders

- 14 dB of Transmitter Return Loss

- Compatible with SONET, M13, CCITT G.742, and Other Asynchronous Muxes

## General Description

The CS61535A combines the complete analog transmit and receive line interface for T1 or E1 applications in a low power, 28-pin device operating from a +5V supply.

The device features a transmitter jitter attenuator making it ideal for use in asynchronous multiplexor systems with gapped transmit clocks. The CS61535A provides a matched, constant impedance output stage to insure signal quality on mismatched, poorly terminated lines.

The IC uses a digital Delay-Locked-Loop clock and data recovery circuit which is continuously calibrated from a crystal reference to provide excellent stability and jitter tolerance.

## **Applications**

- Interfacing network transmission equipment such as SONET multiplexor and M13 to a DSX-1 cross connect.

- Interfacing customer premises equipment to a CSU.

- Interfacing to E1 links.

#### **Ordering Information**

CS61535A-IL1Z 28 Pin PLCC (Lead-free)

#### **ABSOLUTE MAXIMUM RATINGS**

|                | Parameter                    |          | Symbol           | Min      | Max         | Units |

|----------------|------------------------------|----------|------------------|----------|-------------|-------|

| DC Supply      | (referenced to RGND,TGND=0V) |          | RV+              | -        | 6.0         | V     |

|                |                              |          | TV+              | -        | (RV+) + 0.3 | V     |

| Input Voltage, | Any Pin                      | (Note 1) | V <sub>in</sub>  | RGND-0.3 | (RV+) + 0.3 | V     |

| Input Current, | Any Pin                      | (Note 2) | l <sub>in</sub>  | -10      | 10          | mA    |

| Ambient Opera  | ating Temperature            |          | T <sub>A</sub>   | -40      | 85          | °C    |

| Storage Temp   | erature                      |          | T <sub>stg</sub> | -65      | 150         | °C    |

WARNING: Operations at or beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes.

Notes: 1. Excluding RTIP, RRING, which must stay within -6V to (RV+) + 0.3V.

2. Transient currents of up to 100 mA will not cause SCR latch-up. Also TTIP, TRING, TV+ and TGND can withstand a continuous current of 100 mA.

#### RECOMMENDED OPERATING CONDITIONS

| Parameter                      | Symbol   | Min  | Тур | Max  | Units |

|--------------------------------|----------|------|-----|------|-------|

| DC Supply (Note 3)             | RV+, TV+ | 4.75 | 5.0 | 5.25 | V     |

| Ambient Operating Temperature  | TA       | -40  | 25  | 85   | °C    |

| Power Consumption (Notes 4, 5) | Pc       | -    | 290 | 350  | mW    |

| Power Consumption (Notes 4, 6) | Pc       | _    | 175 | -    | mW    |

Notes: 3. TV+ must not exceed RV+ by more than 0.3V.

- 4. Power consumption while driving line load over operating temperature range. Includes IC and load. Digital input levels are within 10% of the supply rails and digital outputs are driving a 50 pF load.

- 5. Assumes 100% ones density and maximum line length at 5.25V.

- 6. Assumes 50% ones density and 300ft. line length at 5.0V.

## **DIGITAL CHARACTERISTICS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ; GND = 0V)

| Parameter                                                                                      | Symbol          | Min         | Тур | Max | Units |

|------------------------------------------------------------------------------------------------|-----------------|-------------|-----|-----|-------|

| High-Level Input Voltage Pins 1-4, 17, 18, 23-28 (Notes 7, 8, 9)                               | Vih             | 2.0         | -   | _   | V     |

| Low-Level Input Voltage Pins 1-4, 17, 18, 23-28 (Notes 7, 8, 9)                                | VIL             | -           | -   | 0.8 | V     |

| High-Level Output Voltage (I <sub>OUT</sub> = -40 μA)<br>Pins 6-8, 11, 12, 25 (Notes 7, 8, 10) | Voh             | 4.0         | -   | _   | V     |

| Low-Level Output Voltage (IOUT = 1.6 mA)<br>Pins 6-8, 11, 12, 23, 25 (Notes 7, 8, 10)          | V <sub>OL</sub> | -           | -   | 0.4 | V     |

| Input Leakage Current (Except Pin 5)                                                           |                 | -           | -   | ±10 | μΑ    |

| Low-Level Input Voltage, Pin 5                                                                 | VIL             | _           | -   | 0.2 | V     |

| High-Level Input Voltage, Pin 5                                                                | V <sub>IH</sub> | (RV+) - 0.2 | -   | -   | V     |

| Mid-Level Input Voltage, Pin 5 (Note 11)                                                       | VIM             | 2.3         | -   | 2.7 | V     |

- Notes: 7. This specification guarantees TTL compatibility ( $V_{OH}$  = 2.4V @  $I_{OUT}$  = -40 $\mu$ A).

- 8. In Host Mode, pin 23 is an open drain output and pin 25 is a tristate output.

- 9. Pins 17 and 18 of the CS61535A are digital inputs in the Extended Hardware Mode.

- 10. Output drivers will drive CMOS logic levels into a CMOS load.

- 11. As an alternative to supplying a 2.3-to-2.7V input, this pin may be left floating.

### **ANALOG SPECIFICATIONS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ; GND = 0V)

| Parameter                                                          | Min                     | Тур | Max | Units |    |

|--------------------------------------------------------------------|-------------------------|-----|-----|-------|----|

| Jitter Attenuator                                                  | '                       |     |     |       |    |

| Jitter Attenuation Curve Corner Frequency                          | (Note 12)               | -   | 6   | -     | Hz |

| T1 Jitter Attenuation in Remote Loopback Jitter Freq. [Hz] Amplitu | (Note 13)<br>ude [Ulpp] |     |     |       |    |

| 10 10                                                              |                         | 3.0 | 6.0 | -     | dB |

| 100 10                                                             |                         | 20  | 30  | -     | dB |

| 500 10                                                             |                         | 35  | 35  | -     | dB |

| 1k 5                                                               |                         | 40  | 50  | -     | dB |

| 10k, 40k 0.3                                                       |                         | 40  | 50  | -     | dB |

| E1 Jitter Attenuation in Remote Loopback Jitter Freg. [Hz] Amplitu | (Note 14)<br>ude [UIpp] |     |     |       |    |

| 10 1.5                                                             |                         | 3.0 | 6.0 | -     | dB |

| 100 1.5                                                            |                         | 20  | 32  | -     | dB |

| 400 1.5                                                            |                         | 30  | 43  | -     | dB |

| 1k 1.5                                                             |                         | 35  | 50  | -     | dB |

| 10k, 100k 0.2                                                      |                         | 35  | 50  | -     | dB |

| Attenuator Input Jitter Tolerance                                  | (Note 15)               | 12  | 23  | -     | UI |

Notes: 12. Not production tested. Parameters guaranteed by design and characterization.

- 13. Attenuation measured at the demodulator output of an HP3785B with input jitter equal to 3/4 of measured jitter tolerance using a measurement bandwidth of 1 Hz (10<f<100Hz), 4Hz (100<f<1000 Hz) and 10 Hz (f> 1kHz) centered around the jitter frequency. With a 2<sup>15</sup>-1 PRBS data pattern. Crystal must meet specifications in Appendix A.

- 14. Jitter measured at the demodulator output of an HP3785A using a measurement bandwidth not to exceed 20 Hz centered around the jitter frequency. With a 2<sup>15</sup>-1 PRBS data pattern. Crystal must meet specifications in Appendix A.

- 15. Output jitter increases significantly when attenuator input jitter tolerance is exceeded.

#### **ANALOG SPECIFICATIONS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ; GND = 0V)

| Parameter                                                                                                                               | Min                                                           | Тур                       | Max                                    | Units                                   |                     |

|-----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|----------------------------------------|-----------------------------------------|---------------------|

| Transmitter                                                                                                                             |                                                               |                           |                                        |                                         |                     |

| AMI Output Pulse Amplitudes E1, 75 $\Omega$ E1, 120 $\Omega$ T1, FCC Part 68 T1, DSX-1                                                  | (Note 16)<br>(Note 17)<br>(Note 18)<br>(Note 19)<br>(Note 20) | 2.14<br>2.7<br>2.7<br>2.4 | 2.37<br>3.0<br>3.0<br>3.0              | 2.6<br>3.3<br>3.3<br>3.6                | V<br>V<br>V         |

| E1 Zero (space) level (LEN2/1/0 = 0/0/0) $75\Omega$ application $120\Omega$ application                                                 | ` '                                                           | -0.237<br>-0.3            | -<br>-                                 | 0.237<br>0.3                            | V                   |

| Recommended Output Load at TTIP and<br>Jitter Added During Remote Loopback<br>10Hz - 8kHz<br>8kHz - 40kHz<br>10Hz - 40kHz<br>Broad Band | TRING (Note 21)                                               | -<br>-<br>-<br>-          | 75<br>0.005<br>0.008<br>0.010<br>0.015 | 0.02<br>0.025<br>0.025<br>0.025<br>0.05 | Ω<br>UI<br>UI<br>UI |

| Power in 2kHz band about 772kHz<br>Power in 2kHz band about 1.544MHz<br>(referenced to power in 2kHz band at 77                         | (Notes 12, 16)<br>(Notes 12, 16)<br>2kHz)                     | 12.6<br>-29               | 15<br>-38                              | 17.9<br>-                               | dBm<br>dB           |

| Positive to Negative Pulse Imbalance<br>T1, DSX-1<br>E1 amplitude at center o<br>E1 pulse width at 50% o                                | (Notes 12, 16) f pulse                                        | -<br>-5<br>-5             | 0.2<br>-<br>-                          | 0.5<br>5<br>5                           | dB<br>%<br>%        |

| Transmitter Return Loss 51 kHz to 102 kHz 102 kHz to 2.048 MHz 2.048 MHz to 3.072 MHz                                                   | (Notes 12, 16, 22)                                            | 8<br>14<br>10             | -<br>-<br>-                            | -<br>-<br>-                             | dB<br>dB<br>dB      |

| Transmitter Short Circuit Current                                                                                                       | (Notes 12, 23)                                                | -                         | _                                      | 50                                      | mA RMS              |

Notes: 16. Using a 0.47 μF capacitor in series with the primary of a transformer recommended in the Applications Section.

- 17. Amplitude measured at the transformer (CS61535A-1:1 or 1:1.26) output across a 75  $\Omega$  load for line length setting LEN2/1/0 = 0/0/0.

- 18. Amplitude measured at the transformer (CS61535A-1:1.26) output across a 120  $\Omega$  load for line length setting LEN2/1/0 = 0/0/0.

- 19. Amplitude measured at the transformer (CS61535A-1:1.15) output across a 100  $\Omega$  load for line length setting LEN2/1/0 = 0/1/0.

- 20. Amplitude measured across a 100  $\Omega$  load at the DSX-1 cross-connect for line length settings LEN2/1/0 = 0/1/1, 1/0/0, 1/0/1, 1/1/0 and 1/1/1 after the length of #22 AWG ABAM equivalent cable specified in Table 3. The CS61535A requires a 1:1.15 transformer.

- 21. Input signal to RTIP/RRING is jitter free. Values will reduce slightly if jitter free clock is input to TCLK.

- 22. Return loss =  $20 \log_{10} ABS((z_1 + z_0)/(z_1 z_0))$  where  $z_1$  = impedance of the transmitter, and  $z_0$  = impedance of line load. Measured with a repeating 1010 data pattern with LEN2/1/0 = 0/0/0 and a 1:1 transformer terminated with a  $75\Omega$  load, or a 1:1.26 transformer terminated with a  $120\Omega$  load.

- 23. Measured broadband through a 0.5  $\Omega$  resistor across the secondary of a 1:1.26 transformer during the transmission of an all ones data pattern for LEN2/1/0 = 0/0/0.

#### **ANALOG SPECIFICATIONS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ; GND = 0V)

| Parameter                                                                   |                                     |                   | Тур            | Max            | Units                               |

|-----------------------------------------------------------------------------|-------------------------------------|-------------------|----------------|----------------|-------------------------------------|

| Driver Performance Monitor                                                  | ·                                   |                   | •              |                |                                     |

| MTIP/MRING Sensitivity: Differential Voltage Required for Detection         |                                     | -                 | 0.60           | -              | V                                   |

| Receiver                                                                    |                                     |                   |                |                |                                     |

| RTIP/RRING Input Impedance                                                  |                                     | -                 | 50k            | -              | Ω                                   |

| Sensitivity Below DSX (0dB = 2.4V)                                          |                                     | -13.6             | -              | -              | dB                                  |

| Data Decision Threshold T1, DSX-1 T1, DSX-1 T1, FCC Part 68 and E1          | (Note 24)<br>(Note 25)<br>(Note 26) | 60<br>53<br>45    | 65<br>65<br>50 | 70<br>77<br>55 | % of peak<br>% of peak<br>% of peak |

| Data Decision Threshold                                                     | T1<br>E1                            | -                 | 65<br>50       | -<br>-         | % of peak % of peak                 |

| Allowable Consecutive Zeros before LOS                                      |                                     | 160               | 175            | 190            | bits                                |

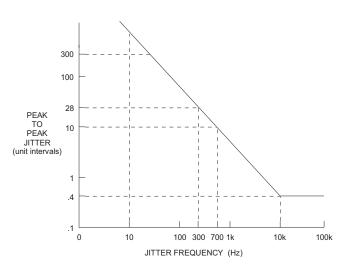

| Receiver Input Jitter Tolerance<br>10kHz - 100kHz<br>2kHz<br>10Hz and below | (Note 27)                           | 0.4<br>6.0<br>300 | -<br>-<br>-    | -<br>-<br>-    | UI<br>UI<br>UI                      |

| Loss of Signal Threshold                                                    | (Note 28)                           | 0.25              | 0.30           | 0.50           | V                                   |

Notes: 24. For input amplitude of 1.2  $V_{pk}$  to 4.14  $V_{pk}$ .

- 25. For input amplitude of 0.5  $V_{pk}$  to 1.2  $V_{pk}$  and from 4.14  $V_{pk}$  to RV+.

- 26. For input amplitude of 1.05  $V_{pk}$  to 3.3  $V_{pk}$ .

- 27. Jitter tolerance increases at lower frequencies. See Figure 11.

- 28. LOS goes high after 160 to 190 consecutive zeros are received. A zero is output on RPOS and RNEG (or RDATA) for each bit period where the input signal amplitude remains below the data decision threshold. The analog input squelch circuit operates when the input signal amplitude above ground on the RTIP and RRING pins falls within the squelch range long enough for the internal slicing threshold to decay within this range. Operation of the squelch causes zeros to be output on RPOS and RNEG as long as the input amplitude remains below 0.25V. During receive LOS, pulses greater than 0.25V in amplitude may be output on RPOS and RNEG. LOS returns low after the ones density reaches 12.5% (based upon 175 bit periods starting with a one and containing less than 100 consecutive zeros) as prescribed in ANSI T1.231-1993.

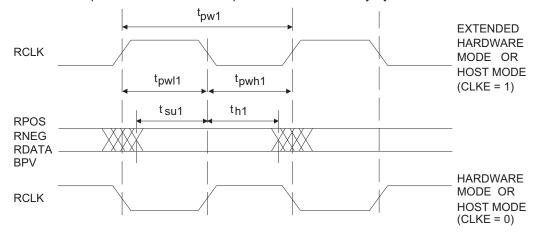

## **T1 SWITCHING CHARACTERISTICS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ;

GND = 0V; Inputs: Logic 0 = 0V, Logic 1 = RV+; See Figures 1, 2, & 3)

| Parameter                                | Symbol                                  | Min                                                        | Тур               | Max               | Units             |                |

|------------------------------------------|-----------------------------------------|------------------------------------------------------------|-------------------|-------------------|-------------------|----------------|

| Crystal Frequency                        | (Note 29)                               | f <sub>C</sub>                                             | -                 | 6.176000          | -                 | MHz            |

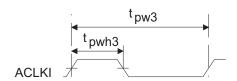

| ACLKI Duty Cycle                         |                                         | t <sub>pwh3</sub> /t <sub>pw3</sub>                        | 40                | -                 | 60                | %              |

| ACLKI Frequency                          | (Note 30)                               | f <sub>aclki</sub>                                         | -                 | 1.544             | -                 | MHz            |

| RCLK Duty Cycle                          | (Notes 31, 32)                          | t <sub>pwh1</sub> /t <sub>pw1</sub>                        | -                 | 78<br>29          | -                 | %<br>%         |

| RCLK Cycle Width (Note 32)               |                                         | t <sub>pw1</sub><br>t <sub>pwh1</sub><br>t <sub>pwl1</sub> | 320<br>130<br>100 | 648<br>190<br>458 | 980<br>240<br>850 | ns<br>ns<br>ns |

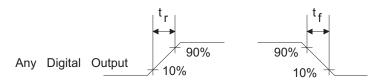

| Rise Time, All Digital Outputs           | (Note 33)                               | t <sub>r</sub>                                             | -                 | -                 | 85                | ns             |

| Fall Time, All Digital Outputs (Note 33) |                                         | t <sub>f</sub>                                             | -                 | -                 | 85                | ns             |

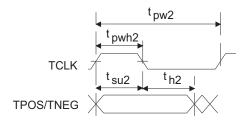

| TPOS/TNEG (TDATA) to TCLK Falling Setu   | ıp Time                                 | t <sub>su2</sub>                                           | 25                | -                 | -                 | ns             |

| TCLK Falling to TPOS/TNEG (TDATA) Hold   | d Time                                  | t <sub>h2</sub>                                            | 25                | -                 | -                 | ns             |

| RPOS/RNEG Valid Before RCLK Falling      | (Note 34)                               | t <sub>su1</sub>                                           | 150               | 274               | -                 | ns             |

| RDATA Valid Before RCLK Falling          | (Note 35)                               | t <sub>su1</sub>                                           | 150               | 274               | -                 | ns             |

| RPOS/RNEG Valid Before RCLK Rising       | (Note 31)                               | t <sub>su1</sub>                                           | 150               | 274               | -                 | ns             |

| RPOS/RNEG Valid After RCLK Falling       | (Note 34)                               | t <sub>h1</sub>                                            | 150               | 274               | -                 | ns             |

| RDATA Valid After RCLK Falling           | (Note 35)                               | t <sub>h1</sub>                                            | 150               | 274               | -                 | ns             |

| RPOS/RNEG Valid After RCLK Rising        | (Note 31)                               | t <sub>h1</sub>                                            | 150               | 274               | -                 | ns             |

| TCLK Frequency                           |                                         | f <sub>tclk</sub>                                          | -                 | 1.544             | -                 | MHz            |

|                                          | 2, 31, 34, 36, 37)<br>Notes 35, 36, 37) | t <sub>pwh2</sub>                                          | 80<br>150         | -                 | 500<br>500        | ns<br>ns       |

Notes: 29. Crystal must meet specifications described in Appendix A.

- 30. ACLKI provided by an external source or TCLK, but not RCLK.

- 31. Hardware Mode, or Host Mode (CLKE = 0).

- 32. RCLK cycle width will vary with extent by which pulses displaced by jitter. Specified under worst case jitter conditions: 0.4 UI AMI data displacement for T1 and 0.2 UI AMI data displacement for E1.

- 33. At max load of 1.6 mA and 50 pF.

- 34. Host Mode (CLKE = 1).

- 35. Extended Hardware Mode.

- 36. The maximum TCLK burst rate is 5 MHz and  $t_{pw2}$ (min) = 200 ns. The maximum gap size that can be tolerated on TCLK is 12 VI.

- 37. The transmitted pulse width does not depend on the TCLK duty cycle.

Figure 1. Recovered Clock and Data Switching Characteristics

## **E1 SWITCHING CHARACTERISTICS** (TA = -40°C to 85°C; TV+, RV+ = $5.0V \pm 5\%$ ;

GND = 0V; Inputs: Logic 0 = 0V, Logic 1 = RV+; See Figures 1, 2, & 3)

| Parameter                              |                                         | Symbol                                                     | Min              | Тур               | Max               | Units          |

|----------------------------------------|-----------------------------------------|------------------------------------------------------------|------------------|-------------------|-------------------|----------------|

| Crystal Frequency                      | (Note 29)                               | f <sub>C</sub>                                             | -                | 8.192000          | -                 | MHz            |

| ACLKI Duty Cycle                       |                                         | t <sub>pwh3</sub> /t <sub>pw3</sub>                        | 40               | -                 | 60                | %              |

| ACLKI Frequency                        | (Note 30)                               | f <sub>aclki</sub>                                         | -                | 2.048             | -                 | MHz            |

| RCLK Duty Cycle                        | (Notes 31, 32)                          | t <sub>pwh1</sub> /t <sub>pw1</sub>                        | -                | 29                | -                 | %              |

| RCLK Cycle Width                       | (Note 32)                               | t <sub>pw1</sub><br>t <sub>pwh1</sub><br>t <sub>pwl1</sub> | 310<br>90<br>120 | 488<br>140<br>348 | 670<br>190<br>500 | ns<br>ns<br>ns |

| RCLK Cycle Width                       | (Note 32)                               | t <sub>pw1</sub><br>t <sub>pwh1</sub><br>t <sub>pwl1</sub> | 320<br>-<br>100  | 488<br>348<br>140 | 670<br>-<br>-     | ns<br>ns<br>ns |

| Rise Time, All Digital Outputs         | (Note 33)                               | t <sub>r</sub>                                             | -                | -                 | 85                | ns             |

| Fall Time, All Digital Outputs         | (Note 33)                               | t <sub>f</sub>                                             | -                | -                 | 85                | ns             |

| TPOS/TNEG (TDATA) to TCLK Falling Set  | up Time                                 | t <sub>su2</sub>                                           | 25               | -                 | -                 | ns             |

| TCLK Falling to TPOS/TNEG (TDATA) Hold | d Time                                  | t <sub>h2</sub>                                            | 25               | -                 | -                 | ns             |

| RPOS/RNEG Valid Before RCLK Falling    | (Note 34)                               | t <sub>su1</sub>                                           | 100              | 194               | -                 | ns             |

| RDATA Valid Before RCLK Falling        | (Note 35)                               | t <sub>su1</sub>                                           | 100              | 194               | -                 | ns             |

| RPOS/RNEG Valid Before RCLK Rising     | (Note 31)                               | t <sub>su1</sub>                                           | 100              | 194               | -                 | ns             |

| RPOS/RNEG Valid After RCLK Falling     | (Note 34)                               | t <sub>h1</sub>                                            | 100              | 194               | -                 | ns             |

| RDATA Valid After RCLK Falling         | (Note 35)                               | t <sub>h1</sub>                                            | 100              | 194               | -                 | ns             |

| RPOS/RNEG Valid After RCLK Rising      | (Note 31)                               | t <sub>h1</sub>                                            | 100              | 194               | -                 | ns             |

| TCLK Frequency                         |                                         | f <sub>tclk</sub>                                          | -                | 2.048             | -                 | MHz            |

|                                        | es 31, 34, 36, 37)<br>Notes 35, 36, 37) | t <sub>pwh2</sub>                                          | 80<br>150        |                   | 340<br>340        | ns<br>ns       |

Figure 2. Signal Rise and Fall Characteristics

Figure 3a. Transmit Clock and Data Switching Characteristics

Figure 3b. Alternate External Clock Characteristics

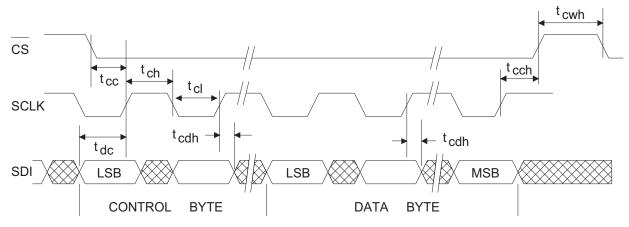

## **SWITCHING CHARACTERISTICS** (TA = -40° to 85°C; TV+, RV+ = $\pm$ 5%;

Inputs: Logic 0 = 0V, Logic 1 = RV+)

| Parameter                             | Symbol                          | Min | Тур | Max | Units |

|---------------------------------------|---------------------------------|-----|-----|-----|-------|

| SDI to SCLK Setup Time                | t <sub>dc</sub>                 | 50  | -   | -   | ns    |

| SCLK to SDI Hold Time                 | t <sub>cdh</sub>                | 50  | -   | -   | ns    |

| SCLK Low Time                         | t <sub>cl</sub>                 | 240 | -   | -   | ns    |

| SCLK High Time                        | t <sub>ch</sub>                 | 240 | -   | -   | ns    |

| SCLK Rise and Fall Time               | t <sub>r</sub> , t <sub>f</sub> | -   | -   | 50  | ns    |

| CS to SCLK Setup Time                 | tcc                             | 50  | -   | -   | ns    |

| SCLK to CS Hold Time (Note 3          | 8) t <sub>cch</sub>             | 50  | -   | -   | ns    |

| CS Inactive Time                      | t <sub>cwh</sub>                | 250 | -   | -   | ns    |

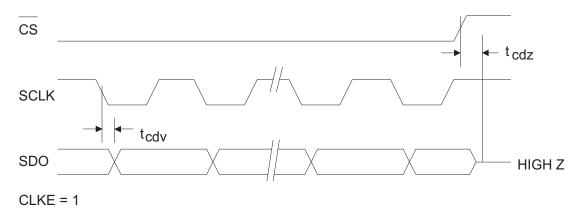

| SCLK to SDO Valid (Note 3             | 9) t <sub>cdv</sub>             | _   | -   | 200 | ns    |

| CS to SDO High Z                      | t <sub>cdz</sub>                | _   | 100 | -   | ns    |

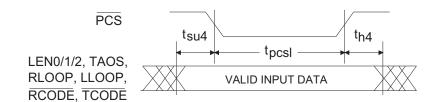

| Input Valid To PCS Falling Setup Time | t <sub>su4</sub>                | 50  | -   | -   | ns    |

| PCS Rising to Input Invalid Hold Time | t <sub>h4</sub>                 | 50  | -   | -   | ns    |

| PCS Active Low Time                   | t <sub>pcsl</sub>               | 250 | _   | _   | ns    |

Notes: 38. For CLKE = 0, CS must remain low at least 50 ns after the 16<sup>th</sup> falling edge of SCLK.

39. Output load capacitance = 50pF.

Figure 4. Serial Port Write Timing Diagram

Figure 5. Serial Port Read Timing Diagram

Figure 6. Extended Hardware Mode Parallel Chip Select Timing Diagram

#### THEORY OF OPERATION

#### Enhancements in CS61535A

The CS61535A provides higher performance and more features than the CS61535 including:

- 50% lower power consumption,

- Internally matched transmitter output impedance for improved signal quality,

- Optional AMI, B8ZS, HDB3 encoder/decoder or external line coding support,

- Receiver AIS (unframed all ones) detection,

- ANSI T1.23 1-1993 compliant receiver Loss of Signal (LOS) handling,

- Transmitter T TIP and T RING outputs are forced low when TCLK is static,

- The Dri ver Performance Monitor oper ates over a wider range of input signal levels.

- Elimination of the requirement that a reference clock be input on the ACLKI pin.

Existing designs using the CS61535 can be converted to the higher performance, pin-compatible CS61535A if the transmit transformer is replaced by a pin -compatible transformer with a new turns ratio and the 4.4  $\Omega$  resistor used in E1 75  $\Omega$  applications is shorted.

#### Introduction to Operating Modes

The CS 61535A s upports three o perating modes which are selected by the level of the MODE pin

|                                    |                                | MODE                                                           |                               |

|------------------------------------|--------------------------------|----------------------------------------------------------------|-------------------------------|

|                                    | HARDWARE                       | EXTENDED HARDWARE                                              | HOST                          |

| MODE-PIN<br>INPUT LEVEL            | <0.2V                          | FLOAT, or<br>2.5V                                              | >(RV+) - 0.2V                 |

| CONTROL<br>METHOD                  | INDIVIDUAL<br>CONTROL<br>LINES | INDIVIDUAL<br>CONTROL<br>LINES &<br>PARALLEL<br>CHIP<br>SELECT | SERIAL<br>μ-PROCESSOR<br>PORT |

| LINE CODE<br>ENCODER &<br>DECODER  | NONE                           | AMI,<br>B8ZS,<br>HDB3                                          | NONE                          |

| AIS DETECTION                      | NO                             | YES                                                            | NO                            |

| DRIVER<br>PERFORM-<br>ANCE MONITOR | YES                            | NO                                                             | YES                           |

**Table 1. Differences in Operating Modes**

as shown in Tables 1 and 2, Figure 7, and Figures A1-A3 of the Applications section.

The CS 61535A m odes are Hardware M ode, Extended Hardware Mode, and Ho st Mode. In Hardware and Extended Hardware Modes, discrete pins are used to configure and monitor the device. The Extended Hardware Mode provides a parallel chip s elect input which latches the control inputs allowing individual I Cs to be configured using a common set of control lines. In the Host Mode, an external processor monitors and configures the device through a serial interface. There are thirteen multi-function pins whose function ality is determined by the operating mode (see Table 2).

#### Transmitter

The transmitter takes data from a T1 (or E1) terminal, attenuates jitter, and produces pulses of appropriate shape. The transmit clock, TCLK, and transmit data, TPOS & TNEG or TDATA, are supplied synchronously. Data is sampled on the falling edge of the input clock, TCLK.

Either T 1 (DSX-1 o r Ne twork Int erface) or E 1 G.703 pulse shapes may be se lected. Pulse shaping and signal level are determined by "line length's elect" in puts as shown in Table 3. The

|              |     |          | MODE                 |       |

|--------------|-----|----------|----------------------|-------|

| FUNCTION     | PIN | HARDWARE | EXTENDED<br>HARDWARE | HOST  |

| TRANSMITTER  | 3   | TPOS     | TDATA                | TPOS  |

| TRANSMITTER  | 4   | TNEG     | TCODE                | TNEG  |

|              | 6   | RNEG     | BPV                  | RNEG  |

|              | 7   | RPOS     | RDATA                | RPOS  |

| RECEIVER/DPM | 11  | DPM      | AIS                  | DPM   |

|              | 17  | MTIP     | RCODE                | MTIP  |

|              | 18  | MRING    | -                    | MRING |

|              | 18  | -        | PCS                  | -     |

|              | 23  | LEN0     | LEN0                 | INT   |

| CONTROL      | 24  | LEN1     | LEN1                 | SDI   |

| CONTROL      | 25  | LEN2     | LEN2                 | SDO   |

|              | 26  | RLOOP    | RLOOP                | CS    |

|              | 27  | LLOOP    | LLOOP                | SCLK  |

|              | 28  | TAOS     | TAOS                 | CLKE  |

**Table 2. Pin Definitions**

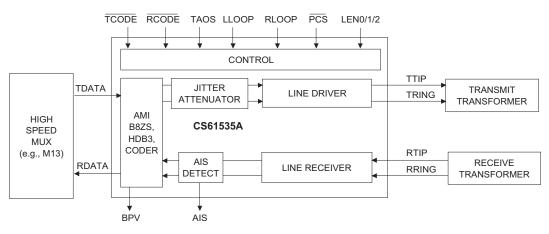

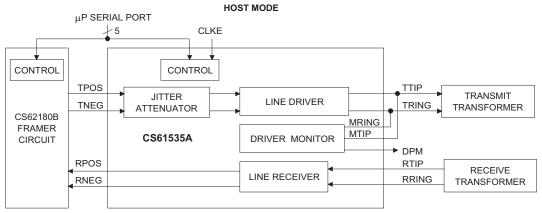

#### HARDWARE MODE TAOS LLOOP RLOOP LEN0/1/2 CONTROL **TPOS** TTIP TRANSMIT JITTER LINE DRIVER TNEG TRING TRANSFORMER **ATTENUATOR** MRING CS62180B MTIP CS61535A DRIVER MONITOR FRAMER **▶** DPM CIRCUIT RPOS RTIP RECEIVE LINE RECEIVER RNEG RRING TRANSFORMER

#### **EXTENDED HARDWARE MODE**

Figure 7. Overview of Operating Modes

| LEN2 | LEN1 | LEN0 | OPTION SELECTED               | APPLICATION  |

|------|------|------|-------------------------------|--------------|

| 0    | 1    | 1    | 0-133 FEET                    | DSX-1        |

| 1    | 0    | 0    | 133-266 FEET                  | ABAM         |

| 1    | 0    | 1    | 266-399 FEET                  | (AT&T 600B   |

| 1    | 1    | 0    | 399-533 FEET                  | or 600C)     |

| 1    | 1    | 1    | 533-655 FEET                  |              |

| 0    | 0    | 1    | AT&T CB113<br>(CS61535A only) | REPEATER     |

| 0    | 0    | 0    | CCITT G.703                   | 2.048 MHz E1 |

| 0    | 1    | 0    | FCC Part 68, Option A         | CSU NETWORK  |

| 0    | 1    | 1    | ANSI T1.403                   | INTERFACE    |

**Table 3. Line Length Selection**

CS61535A line driver is designed to drive a 75  $\Omega$  equivalent load.

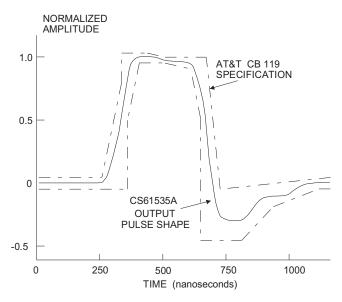

For T1 DSX-1 applications, line lengths from 0 to 655 feet (as measured from the transmitter to the DSX-1 c ross c onnect) are selectable. The f ive partition a rrangement meets ANSI T 1.102-1993 requirements when using ABAM cable. A typical output pulse is shown in Fi gure 8. These pulse settings can also be used to meet CC ITT pulse shape requirements for 1.544 MHz operation.

For T1 Network Interface applications, additional options are provided. Note that the optimal pulse width for Pa rt 68 (324 ns) is na rrower than the optimal pulse width for D SX-1 (350 ns). The CS61535A automatically adjusts the pulse width based upon the "line length" selection made.

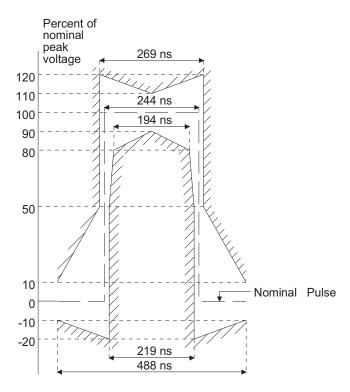

The E1 G.703 pulse shape is supported with line length s election L EN2/1/0=0/0/0. The pulse

width will meet the G.703 pulse shape template shown in Figure 9, and specified in Table 4.

For E 1 a pplications, the C S61535A driver provides 14 dB of return loss during the transmission of both marks and spaces. This improves signal quality by minimizing reflections off the transmitter. Similar levels of return loss are provided for T1 applications.

The CS61 535A transmitter will detect a failed TCLK, and will force the TTIP and TRING outputs low.

Figure 8. Typical Pulse Shape at DSX-1 Cross Connect

For coaxial cable, For shielded twisted

|                                                                                             | $75\Omega$ load and transformer specified in Application Section. | pair, $120\Omega$ load and transformer specified in Application Section. |

|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------------------------------------------------------|

| Nominal peak voltage of a mark (pulse)                                                      | 2.37 V                                                            | 3 V                                                                      |

| Peak voltage of a space (no pulse)                                                          | 0 ±0.237 V                                                        | 0 ±0.30 V                                                                |

| Nominal pulse width                                                                         | 244                                                               | ns                                                                       |

| Ratio of the amplitudes of positive and negative pulses at the center of the pulse interval | 0.95 to                                                           | 1.05*                                                                    |

| Ratio of the widths of positive and negative pulses at the nominal half amplitude           | 0.95 to 1.05*                                                     |                                                                          |

<sup>\*</sup> When configured with a 0.47 μF nonpolarized capacitor in series with the TX transformer primary as shown in Figures A1, A2 and A3.

**Table 4. CCITT G.703 Specifications**

Figure 9. Mask of the Pulse at the 2048 kbps Interface

When any transmit control pin (TAOS, LEN0-2 or LLOOP) is toggled, the transmitter stabilizes within 22 bit periods. The transmitter will take longer to stabilize when RLOOP is selected because the timing circuitry must adjust to the new frequency.

#### Jitter Attenuator

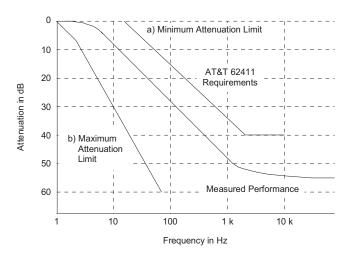

The jitter attenuator is designed to reduce wander and jitter in the transmit clock signal. It consists of a 32 bit FIFO, a crystal oscillator, a set of load capacitors for the crystal, and control logic. The jitter attenuator ex ceeds the jitter attenuation requirements of Publications 43802 and RE C. G.742. A typical jitter attenuation curve is shown in Figure 10.

The jitter attenuator works in the following manner. Data on TPOS and TNEG (or TDATA) are written into the jitter attenuator's FIFO by TCLK. The rate at which data is read out of the FIFO and transmitted is determined by the oscillator. Logic circuits adjust the capacitive loading on the crys-

Figure 10. Typical Jitter Attenuation Curve

tal to set its oscillation frequency to the average of the TCLK frequency. Signal jitter is absorbed in the FIFO.

#### Jitter Tolerance of Jitter Attenuator

The FIFO in the jitter attenuator is designed to neither overflow nor underflow. If the jitter amplitude becomes very large, the read and write pointers may get very close together. Should the pointers a ttempt to cross, the oscillator's divide by four circuit adjusts by performing a divide by 3 1/2 or divide by 4 1/2 to prevent the overflow or underflow. When a divide by 3 1/2 or 4 1/2 occurs, the data bit will be driven on to the line either an eighth bit period early or an eighth bit period late.

When the TCLK frequency is close to the center frequency of the crystal oscillator, the high frequency jitter tolerance is 23 UI before the divide by 3 1/2 or 4 1/2 circuitry is a ctivated. As the center frequency of the oscillator and the TCLK frequency deviate from one another, the jitter tolerance is reduced. As this frequency deviation becomes large, the maximum jitter to lerance at high frequencies is reduced to 12 UI before the underflow/overflow circuitry is activated. In application, it is unlikely that the oscillator center frequency will be precisely a ligned with the

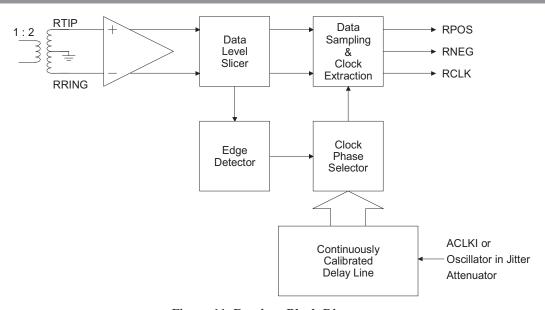

Figure 11. Receiver Block Diagram not available on the C S61535A when ACL KI is

TCLK frequency due to a llowable TCLK tolerance, part to part variations, crystal to crystal variations, and crystal temperature drift. The oscillator tends to track low frequency jitter so jitter tolerance increases as jitter frequency decreases.

The crystal frequency must be 4 times the nominal signal frequency: 6.176 MHz for 1. 544 MHz operation; 8.192 MH z for 2.048 MH z applications. Internal capacitors load the crystal, controlling the os cillation frequency. The crystal must be designed so that over operating temperature, the o scillator frequency range exceeds the system frequency tolerance. To obtain optimum performance, the crystal used must meet the specifications in Appendix A.

#### Transmit All Ones Select

The transmitter provides for all one sinsertion at the frequency of ACLKI. Transmit all ones is selected when TAOS goes high, and causes continuous on es to be t ransmitted on t he line (TTIP and TRING). In this mode, the TPOS and TNEG (or TDATA) inputs are ignored. A TAOS request will be i gnored if remote loopback is in effect. ACLKI jitter will be attenuated. TAOS is

grounded.

#### Receiver

The receiver extracts data and clock from an AMI (Alternate Mark Inversion) coded signal and outputs clock and synchronized data. The receiver is sensitive to signals over the entire range of cable lengths and r equires no equalization or AL BO (Automatic Line Build Out) circuits. The signal is received on both ends of a cen ter-tapped, centergrounded transformer. The transformer is center-tapped on the IC side. The clock and data recovery circuit exceeds the jitter tolerance specifications of Publications 438 02, 43 801, 6 2411 amended, TR-TSY-000170, and CCIT TREC. G.823.

A block diagram of the receiver is shown in Figure 11. The two leads of the transformer (RTIP and RRING) have opposite polarity allowing the receiver to treat RTIP and RRING as unipolar signals. Comparators are used to d etect p ulses on RTIP and RRING. The comparator thresholds are dynamically established at a percent of the peak level (50% of p eak for E 1, 65% of pe ak for T 1; with the slicing level selected by LEN2/1/0).

The receiver uses an edge detector and a continuously calibrated delay line to generate the recovered clock. The delay line divides its reference clock, ACLKI or the jitter at tenuator's oscillator, into 13 equal divisions or phases. Continuous calibration assures timing accuracy, even if temperature or power supply voltage fluctuate.

The leading edge of a n incoming data pulse triggers the clock phase selector. The phase selector chooses one of the 13 available phases which the delay line produces for each bit period. The output from the phase selector feeds the clock and data recovery circuits which generate the recovered clock and sample the incoming signal at appropriate intervals to recover the data. The jitter tolerance of the receiver exceeds that shown in Figure 12.

Figure 12. Input Jitter Tolerance of Receiver

The CS61535A outputs a clock immediately upon power-up. The clock recovery circuit is calibrated, and the device will lock onto the AMI data input immediately. If loss of signal occurs, the RCLK frequency will equal the ACLKI frequency.

In the Hardware Mode, data at RPOS and RNEG is stable and may be sampled on the rising edge of the recovered clock. In the Extended Hardware Mode, data at RDATA is stable and may be sampled on the falling edge of the recovered clock. In

the Host Mode, CLKE determines the clock polarity for which output data is stable and valid as shown in Table 5.

|      | MODE<br>(pin 5)     | CLKE<br>(pin 28) | DATA                | CLOCK                | Clock Edge for<br>Valid Data |

|------|---------------------|------------------|---------------------|----------------------|------------------------------|

|      | LOW<br>(<0.2V)      | Х                | RPOS<br>RNEG        | RCLK<br>RCLK         | Rising<br>Rising             |

| (>(' | HIGH<br>V+) - 0.2V) | LOW              | RPOS<br>RNEG<br>SDO | RCLK<br>RCLK<br>SCLK | Rising<br>Rising<br>Falling  |

| (>(' | HIGH<br>V+) - 0.2V) | HIGH             | RPOS<br>RNEG<br>SDO | RCLK<br>RCLK<br>SCLK | Falling<br>Falling<br>Rising |

| ı    | MIDDLE<br>(2.5V)    | Х                | RDATA               | RCLK                 | Falling                      |

X = Don't care

Table 5. Data Output/Clock Relationship

#### Jitter and Recovered Clock

The CS61 535A are designed for error free clock and data reco very from an AMI encoded data stream in the presence of more than 0.4 unit intervals of jitter at high frequency. The clock recovery circuit is also tolerant of long strings of zeros. The edge of an incoming data bit causes the circuitry to choose a phase from the delay line which most closely corresponds with the arrival time of the data edge, and that clock phase triggers a pulse which is typically 140 ns in duration. This phase of the delay line will continue to be selected until a data bit arrives which is closer to another of the 13 phases, causing a new phase to be selected. The largest jump allowed along the delay line is six phases.

When an input signal is jitter free, the phase selection will o ccasionally jump between two adjacent phases resulting in RCLK jitter with an amplitude of 1/13 UIpp. These single phase jumps are due to differences in frequency of the incoming data and the calibration clock input to ACLKI. For T 1 operation of the CS61535A, the instantaneous period can be 14/13 \* 648 ns = 698 ns (1,662,769 Hz) or 12/13 \* 648 ns = 598 ns (1,425,231 Hz) when adjacent clock phases are chosen. As long as the same phase is chosen, the

period wil 1 b e 64 8 ns. Si milar c alculations hol d for the E1 rate.

The clock recovery circuit is designed to accept at least 0.4 UI of jitter at the receiver. Since the data stream contains in formation only when ones are transmitted, a clock/data recovery circuit must assume a zero when no signal is measured during a bit period. Likewise, when zeros are received, no information is present to u pdate the clock recovery circuit regarding the trend of a signal which is jittered. The result is that two one s that are separated by a string of zero s can exhibit maximum deviation in pulse arrival time. For example, one half of a period of jitter at 100 kHz oc curs in 5 us, which is 7.7 T1 bit periods. If the jitter amplitude is 0.4 UI, then a one preceded by seven zeros can have maximum displacement in arrival time, i.e. either 0.4 UI too early or 0.4 UI too late. For the CS61535A, the data recovery circuit correctly assigns a received bit to its proper clock period if it is displaced by less than 6/13 of a bit period from its optimal location. Theoretically, this would give a jit ter tolerance of 0.46 UI. The actual jitter toler ance of the CS61535A is only slightly less than the ideal.

In the event of a maximum j itter h it, the RCLK clock p eriod i mmediately adj usts to a lign it self with the incoming data and prepare to ac curately place the next one, whether it arrives one period later, or aft er another string of ze ros and is displaced by ji tter. For a m aximum early jitter hit, RCLK will have a period of 7/13 \* 648 ns = 349 ns (2,865,961 Hz). For a maximum late jitter hit, RCLK will have a period of 19/13 \* 648 ns = 947 ns (1,055,880 Hz).

#### Loss of Signal

Receiver loss of signal is in dicated up on receiving 175 consecutive zeros. A digital counter counts received zeros based on RCLK cycles. A zero input is determined either when zeros are re-

ceived, or when the received signal amplitude drops below a 0.3 V peak threshold.

The rece iver reports loss of s ignal by s etting the Loss of Signal pin, LOS, high. If the serial interface is u sed, the LOS b it will be set and an interrupt is sued on INT. LOS will go low (and flag the INT pin again if serial I/O is used) when a valid s ignal is detected. Note that in the Host Mode, LOS is simultaneously available from both the register and pin 12.

In a loss of signal state, the RCLK frequency will be equal to the ACLKI frequency since ACLKI is being used to calibrate the clock recovery circuit. Received data is output on RPOS and RNEG (or RDATA) regardless of LOS status. The LOS returns to logic zero when the ones density reaches 12.5% (based upon 175 bit periods staring with a one and containing less than 100 consecutive zeros) as prescribed in ANSI T 1.231-1993. A power-up or manual reset will also set LOS high.

#### Local Loopback

The loc al loopback mode takes clock and data presented on T CLK, T POS, and T NEG (or TDATA) and out puts it at RCL K, RPOS and RNEG (or RDATA). Lo cal loopback is selected by taking pin 27 high, or LLOOP may be selected using the serial interface. The data on the transmitter inputs is transmitted on the line unless TAOS is selected to cause the transmission of an all ones signal instead. Receiver inputs are ignored when local loopback is in effect. The jitter attenuator is not included in the local loopback data path. Se lection of local loopback overrides the chip's loss of signal response.

#### Remote Loopback

In remote loopback, the recovered clock and data input on RTIP and RRING are sent through the jitter attenuator and back out on the line via TTIP and TRING. The recovered incoming signals are also sent to RCLK, RPOS and RNEG (or

RDATA). Remote loopback is selected by taking pin 26 high, or RLOOP may be selected using the serial in terface. Si multaneous s election of lo cal and remote loopback modes is not valid (see Reset).

In the CS61535A Extended Hardware Mode, remote loo pback occurs before the line code encoder/decoder, insuring that the transmitted signal matches the received signal, even in the presence of received bipolar violations. The recovered data will also be decoded and output on RDATA if RCODE is low.

#### Driver Performance Monitor

To aid in early detection and easy is olation of nonfunctioning links, the Har dware and H ost Modes of the CS6 1535A are able to monitor transmit drive performance and report when the driver is nolonger operational. This feature can be used to monitor either the device's performance or the performance of a neighboring driver. The driver performance monitor indicator is normally at a low (zero) logic level, and goes to high level upon detecting driver failure. In the Host Mode, DPM is available from both the register and pin 11.

The driver performance monitor consists of an activity detector that monitors the transmitted signal when MTIP is connected to TTIP and MRING is connected to TRING. DPM wil 1 go hi gh if the absolute difference be tween MT IP and MRING does not transition a bove or be low at hreshold level within a time-out period.

Whenever more than one line interface IC resides on the same circuit board, the effectiveness of the driver performance monitor can be maximized by having each IC monitor performance of a neighboring device, rather than having it monitor its own performance.

#### Line Code Encoder/Decoder

In Extended Hardware Mode, three line codes are available: AMI, B 8ZS and HDB3. The input to the encoder is TDATA. The outputs from the decoder are RD ATA and BPV (Bipolar Violation Strobe). The encoder and decoder are selected using p ins L EN2, L EN1, L EN0, TCODE and RCODE as shown in Table 6.

|                       |      | LEN 2/1/0      |         |

|-----------------------|------|----------------|---------|

|                       |      | 000            | 010-111 |

| TCODE                 | LOW  | HDB3           | B8ZS    |

| (Transmit             |      | Encoder        | Encoder |

| Encoder               | HIGH | AMI            |         |

| Selection)            |      | Encoder        |         |

| RCODE                 | LOW  | HDB3           | B8ZS    |

| (Receiver             |      | Decoder        | Decoder |

| Decoder<br>Selection) | HIGH | AMI<br>Decoder |         |

Table 6. Selection of Encoder/Decoder

#### Alarm Indication Signal

In Extended Hardware Mode, the receiver sets the output p in AIS hi gh when less than 9 zeros are detected out of 8192 bit periods. AIS returns low when 9 or more ze ros are detected out of 8192 bits.

#### Parallel Chip Select

In Extended Hardware Mode,  $\overline{PCS}$  can be used to gate the digital control inputs:  $\overline{TCODE}$ ,  $\overline{RCODE}$ , LEN0, LEN1, LEN2, RLOOP, LLOOP and TAOS. Inputs are accepted on these pins only when  $\overline{PCS}$  is low. Changes in inputs will immediately change the operating setate of the device. Therefore, when cycling  $\overline{PCS}$  to update the operating setate, the digital control inputs should be stable for the entire  $\overline{PCS}$  low period. The control inputs are ignored when  $\overline{PCS}$  is high.

#### Power On Reset / Reset

Upon power-up, the CS61535A is held in a static state u ntil the s upply c rosses a thre shold of ap-

Figure 13. Input/Output Timing

proximately thre e Volts. When this th reshold is crossed, the device will delay for about 10 ms to allow the power supply to reach operating voltage. After this delay, calibration of the delay lines used in the transmit and receive sections commences. The delay lines can be calibrated only if a reference clock is present. The reference clock for the receiver is provided by A CLKI (or by the crystal oscillator if ACLKI is not present). The reference clock for the transmitter is provided by TCLK. The initial calibration should take less than 20 ms.

In operation, the delay lines are continuously calibrated, making the performance of the device independent of power supply or temperature variations. The continuous calibration function foregoes any requirement to reset the line interface when in operation. However, a reset function is available which will clear all registers.

In the Hardware and Extended Hardware modes, a reset request is made by simultaneously setting both RLOOP and LLOOP high for at least 200 ns. Reset will initiate on the f alling edge of the res et request (falling edge of RLOOP and LLOOP). In the Hos t Mode, a res et is initiated by simultaneously writing RLOOP and LLOOP to the register. In either mode, a reset will set all registers to 0 and set LOS high.

#### Serial Interface

In the Host Mode, pins 23 through 28 serve as a microprocessor/microcontroller inter face. One eight-bit register can be written to via the SDI pin or read from the SDO p in at the clock rate determined by SCL K. Through this register, a hos t controller can be used to control operational char-

acteristics and monitor device status. The serial port read/write timing is independent of the system transmit and receive timing.

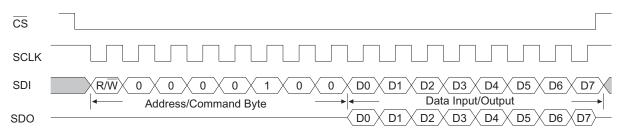

Data transfers are initiated by taking the chip select input,  $\overline{CS}$ , low ( $\overline{CS}$  must in itially be h igh). SCLK may be either high or low when  $\overline{CS}$  initially goeslow. Address and input data bits are clocked in on the rising edge of SCLK. Data on SDO is valid and stable on the falling edge of SCLK when CLKE is low, and on the rising edge of SCLK when CLKE is high. Data transfers are terminated by setting  $\overline{CS}$  high.  $\overline{CS}$  may go high no sooner than 50 ns after the rising edge of the SCLK cycle corresponding to the last write bit. For a serial data read,  $\overline{CS}$  may go high any time to terminate the output.

Figure 13 s hows the timing relationships for data transfers when CLKE = 1. When CLKE = 0, data output from the serial port, SDO, is valid on the falling edge of SCLK. For CLKE = 1, data bit D7 is held to the falling edge of the 16th clock cycle; for CLKE = 0, data bit D7 is held to the rising edge of the 17th clock cycle. SDO goes to a high

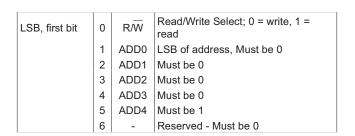

Table 7. Address/Command Byte

impedance state either after bit D7 is output or at the end of the hold period of data bit D7.

An a ddress/command byt e, s hown in Table 7, precedes a data register. The first bit of the address/command byte determines whether a read or a write is requested. The next six bits contain the address. The CS61 535A responds to address 16 (0010000). The last bit is ignored.

The data register, shown in Table 8, can be written to the serial p ort. Data is input on the eight clock cycles immediately following the address/command byte. Bits 0 and 1 are eused to clear an interrupt issued from the INT pin, which occurs in response to a loss of signal or a problem with the output driver. If bits 0 or 1 are true, the corresponding interrupt is suppressed. So if a loss of signal interrupt is cleared by writing a 1 to bit 0, the interrupt will be reenabled by writing a 0 to bit 0. This holds for DPM as well.

| LSB: first bit in | 0 | clr LOS | Clear Loss of Signal             |

|-------------------|---|---------|----------------------------------|

|                   | 1 | clr DPM | Clear Driver Performance Monitor |

|                   | 2 | LEN0    | Bit 0 - Line Length Select       |

|                   | 3 | LEN1    | Bit 1 - Line Length Select       |

|                   | 4 | LEN2    | Bit 2 - Line Lenght Select       |

|                   | 5 | RLOOP   | Remote Loopback                  |

|                   | 6 | LLOOP   | Local Loopback                   |

| MSB: last bit in  | 7 | TAOS    | Transmit All Ones Select         |

Table 8. Input Data Register

Writing a "1" to either "Clear L OS" or "Clear DPM" over the serial interface has three effects:

- 1) the current interrupt on the serial interface will be cleared. (Note that simply reading the register bits will not clear the interrupt),

- 2) output data bits 5, 6 and 7 will be reset as appropriate,

- 3) future interrupts for the corresponding LOS or DPM will be prevented from occuring).

| LSB: first bit in | 0 | LOS  | Loss of Signal             |

|-------------------|---|------|----------------------------|

|                   | 1 | DPM  | Driver Performance Monitor |

|                   | 2 | LEN0 | Bit 0 - Line Length Select |

|                   | 3 | LEN1 | Bit 1 - Line Length Select |

|                   | 4 | LEN2 | Bit 2 - Line Lenght Select |

Table 9. Output Data Bits 0 - 4

| _          |   |        |                                                                        |

|------------|---|--------|------------------------------------------------------------------------|

| Bits 5 6 7 |   | s<br>7 | Status                                                                 |

| 0          | 0 | 0      | Reset has occurred or no program input.                                |

| 0          | 0 | 1      | TAOS in effect.                                                        |

| 0          | 1 | 0      | LLOOP in effect.                                                       |

| 0          | 1 | 1      | TAOS/LLOOP in effect.                                                  |

| 1          | 0 | 0      | RLOOP in effect                                                        |

| 1          | 0 | 1      | DPM changed state since last "clear DPM" occured.                      |

| 1          | 1 | 0      | LOS changed state since last "clear LOS" occured.                      |

| 1          | 1 | 1      | LOS and DPM have changed state since last "clear LOS" and "clear DPM". |

Table 10. Coding for Serial Output Bits 5, 6, 7

Writing a "0" to either "Clear LOS" or "Clear DPM" e nables the corresponding interrupt for LOS or DPM.

Output data from the serial interface is presented as shown in Tables 9 and 10. Bits 2, 3 and 4 can be read to verify line length selection. Bits 5, 6 and 7 mus t be de coded. Codes 101, 110 and 111 (bits 5, 6 and 7) in dicate L OS and D PM s tate changes. Writing a "1" to the "Clear LOS" and/or "Clear DPM" bits in the register also resets status bits 5, 6, and 7.

SDO goes to a high impedance state when not in use. SDO and SDI may be tied together in applications where the host processor has a bidirectional I/O port.

#### **Power Supply**

The device operates from a single +5 Volt supply. Separate pi ns f or tr ansmit and r eceive supplies provide in ternal i solation. T hese pi ns should be connected externally near the device and decoupled to their respective grounds. T V+ must not exceed RV+ by more than 0.3V.

Decoupling and filtering of the power supplies is crucial for the proper operation of the analog circuits in both the transmit and receive paths. A 1.0  $\mu F$  capacitor should be connected between TV+ and TGND, and a 0.1  $\mu F$  capacitor should be connected between RV+ and RGND. Use m ylar or ceramic capacitors and place them as closely as possible to their respective power supply pins. A 68  $\mu F$  tantalum capacitor should be added close to the RV+/RGND supply. Wire wrap breadboarding of the line interface is not recommended because lead resistance and inductance serve to defeat the function of the decoupling capacitors.

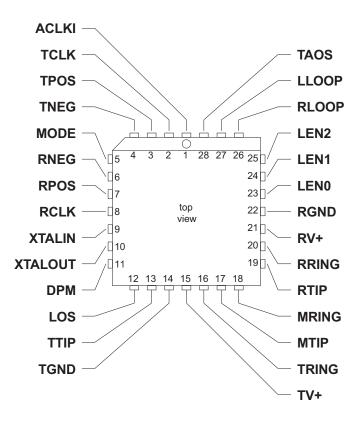

#### Hardware Mode Pinout

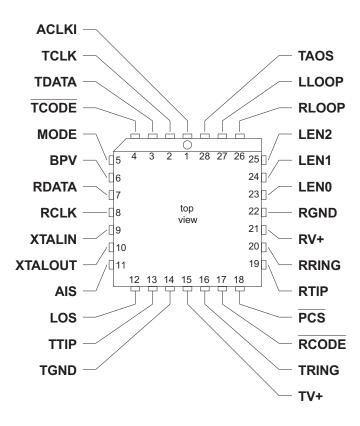

#### Extended Hardware Mode Pinout

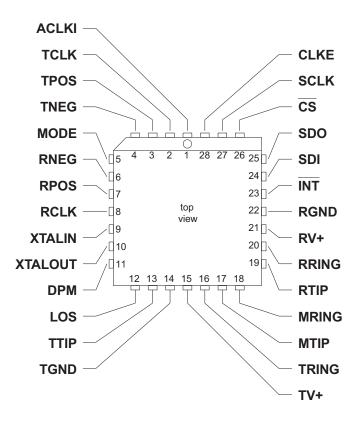

#### **Host Mode Pinout**

#### **Power Supplies**

#### RGND - Ground, Pin 22.

Power supply ground for all subcircuits except the transmit driver; typically 0 Volts.

#### RV+ - Power Supply, Pin 21.

Power supply for all subcircuits except the transmit driver; typically +5 Volts.

#### TGND - Ground, Transmit Driver, Pin 14.

Power supply ground for the transmit driver; typically 0 Volts.

#### TV+ - Power Supply, Transmit Driver, Pin 15.

Power supply for the transmit driver; typically +5 Volts. TV+ must not exceed RV+ by more than 0.3 V.

#### **Oscillator**

#### XTALIN, XTALOUT - Crystal Connections, Pins 9 and 10.

A 6.176 MHz (or 8.192 MHz) crystal should be connected across these pins. If a 1.544 MHz (or 2.048 MHz) clock is provided on ACLKI (pin 1), the jitter attenuator may be disabled by tying XTALIN, Pin 9 to RV+ through a 1 k $\Omega$  resistor, and floating XTALOUT, Pin 10.

Overdriving the oscillator with an external clock is not supported. See Appendix A for crystal specifications.

#### Control

#### ACLKI - Alternate External Clock Input, Pin 1.

The CS61535A does not require a clock signal to be input on ACLKI when a crystal is connected between p ins 9 and 10. If a clock is not provided on AC LKI, this input must be grounded. If ACLKI is grounded, the oscillator in the jitter attenuator is used to calibrate the clock recovery circuit and TAOS is not available.

#### CLKE - Clock Edge, Pin 28. (Host Mode)

Setting CLKE to logic 1 causes RPOS and RNEG to be valid on the falling edge of RCLK, and SDO to be valid on the rising edge of SCLK. Conversely, setting CLKE to logic 0 causes RPOS and RNEG to be valid on the rising edge of RCLK, and SDO to be valid on the falling edge of SCLK.

#### CS - Chip Select, Pin 26. (Host Mode)

This pin must transition from high to low to read or write the serial port.

#### INT - Receive Alarm Interrupt, Pin 23. (Host Mode)

Goes low when LOS or DPM change state to <u>flag</u> the host processor. INT is cleared by writing "Clear LOS" or "Clear DPM" to the register. INT is an open drain output and should be tied to the power supply through a resistor.

# LEN0, LEN1, LEN2 - Line Length Selection, Pins 23, 24 and 25. (Hardware and Extended Hardware Modes)

Determines the shape and amplitude of the transmitted pulse to accommodate several cable types and lengths. See T able 3 for information on line lengths election. Also controls the receiver slicing level and the line code in Extended Hardware Mode.

#### LLOOP - Local Loopback, Pin 27. (Hardware and Extended Hardware Modes)

Setting LLOOP to a logic 1 routes the transmit clock and data through to the receive clock and data pins. TPOS/TNEG (or TDATA) are still transmitted unless overridden by a TAOS request. Inputs on RTIP and RRING are ignored.

#### MODE - Mode Select, Pin 5.

Driving the MODE p in high p uts the CS61535A line interface in the Host Mo de. In the host mode, a serial control port is used to control the CS61535A line interface and determine its status. Grounding the MODE pin puts the CS 61535A line interface in the Hardware Mode, where configuration and status are controlled by discrete pins. Floating the MODE pin or driving it to +2.5 V puts the CS61535A in Extended Hardware Mode, where configuration and status are controlled by discrete pins. When floating MODE, there should be no external load on the pin. MODE defines the status of 13 pins (see Table 2).

## PCS - Parallel Chip Select, Pin 18. (Extended Hardware Mode)

Setting PCS high causes the CS61535Aline interface to ignore the TCODE, RCODE, LEN0, LEN1, LEN2, RLOOP, LLOOP and TAOS inputs.

#### **RCODE** - Receiver Decoder Select, Pin 17. (Extended Hardware Mode)

Setting RCODE low enables B8ZS or HDB 3 zero substitution in the receiver decoder. Setting RCODE high enables the AMI receiver decoder (see Table 8).

#### RLOOP - Remote Loopback, Pin 26. (Hardware and Extended Hardware Modes)

Setting RL OOP to a lo gic 1 causes the recovered clock and data to be s ent through the jitter attenuator (if active) and through the driver back to the line. The recovered signal is also sent to RCLK and RPOS/RNEG (or RDATA). Any TAOS request is ignored.

Simultaneously taking RLOOP and LLOOP high for at least 200 ns initiates a device reset.

#### SCLK - Serial Clock, Pin 27. (Host Mode)

Clock used to read or write the <u>serial</u> port registers. SCLK can be either high or low when the line interface is selected using the CS pin.

#### SDI - Serial Data Input, Pin 24. (Host Mode)

Data for the on-chip register. Sampled on the rising edge of SCLK.

#### SDO - Serial Data Output, Pin 25. (Host Mode)

Status and control information from the on-chip register. If CLKE is high SDO is valid on the rising edge of SCLK. If CLKE is low SDO is valid on the falling edge of SCLK. This pin goes to a high-impedance state when the serial port is being written to or after bit D7 is output.