Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

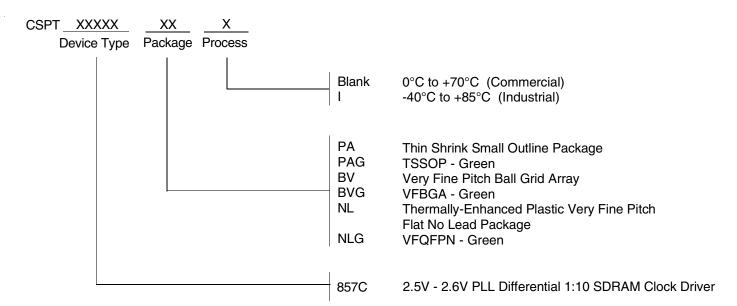

# 2.5V - 2.6V PHASE LOCKED LOOP DIFFERENTIAL 1:10 SDRAM CLOCK DRIVER

#### IDTCSPT857C

#### **FEATURES:**

- 1 to 10 differential clock distribution

- Optimized for clock distribution in DDR (Double Data Rate) SDRAM applications

- Operating frequency: 60MHz to 220MHz

- · Very low skew:

- <100ps for PC1600 PC2700

- <75ps for PC3200

- · Very low jitter:

- <75ps for PC1600 PC2700</p>

- <50ps for PC3200</p>

- 2.5V AVDD and 2.5V VDDQ for PC1600-PC2700

- 2.6V AVDD and 2.6V VDDQ for PC3200

- CMOS control signal input

- Test mode enables buffers while disabling PLL

- · Low current power-down mode

- Tolerant of Spread Spectrum input clock

- Available in 48-pin TSSOP, 40-pin VFQFPN, and 56-pin VFBGA packages

#### **APPLICATIONS:**

- Meets or exceeds JEDEC standard JESD 82-1A for registered DDR clock driver

- Meets proposed DDR1-400 specification

- For all DDR1 speeds: PC1600 (DDR200), PC2100 (DDR266), PC2700 (DDR333), PC3200 (DDR400)

- Along with SSTV16857, SSTVF16857, SSTV16859, SSTVM16859, SSTVF16859, DDR1 register, provides complete solution for DDR1 DIMMs

#### **DESCRIPTION:**

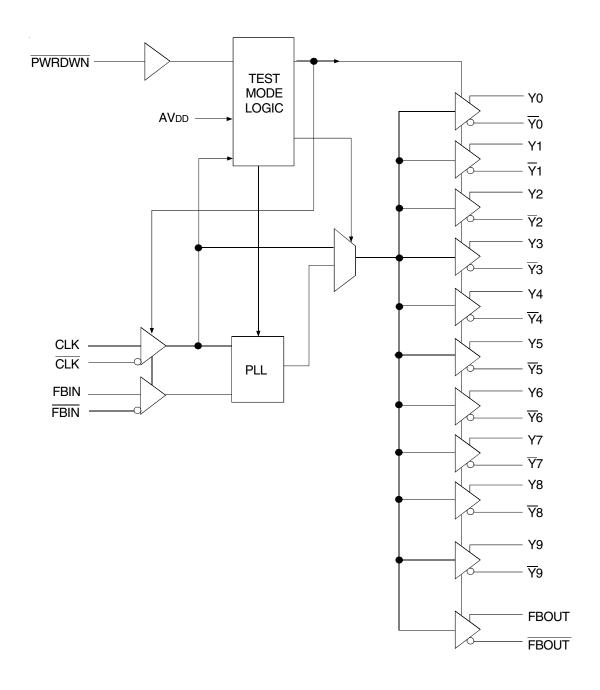

The CSPT857C is a PLL based clock driver that acts as a zero delay buffer to distribute one differential clock input pair (CLK,  $\overline{\text{CLK}}$ ) to 10 differential output pairs (Y [0:9],  $\overline{\text{Y}}$  [0:9]) and one differential pair of feedback clock output (FBOUT, FBOUT). External feedback pins (FBIN,  $\overline{\text{FBIN}}$ ) for synchronization of the outputs to the input reference is provided. A CMOS Enable/Disable pin is available for low power disable. When the input frequency falls below approximately 20MHz, the device will enter power down mode. In this mode, the receivers are disabled, the PLL is turned off, and the output clock drivers are tristated, resulting in a current consumption of less than 200 $\mu$ A.

The CSPT857C requires no external components and has been optimised for very low I/O phase error, skew, and jitter, while maintaining frequency and duty cycle over the operating voltage and temperature range. The CSPT857C, designed for use in both module assemblies and system motherboard based solutions, provides an optimum high-performance clock source.

The CSPT857C is available in Commercial Temperature Range (0°C to +70°C) and Industrial Temperature Range (-40°C to +85°C). See Ordering Information for details.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

# **FUNCTIONAL BLOCK DIAGRAM**

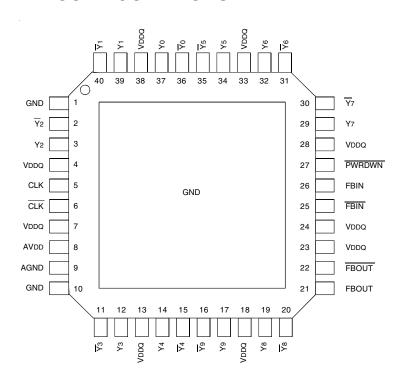

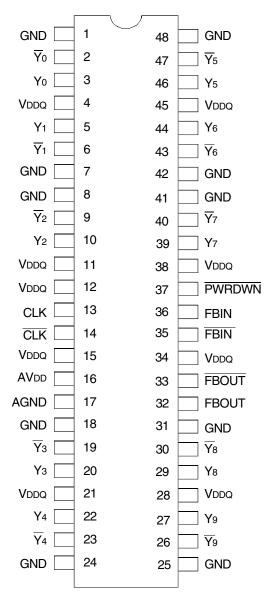

# **PIN CONFIGURATIONS**

|   |            |            |     |                | 1          |      | 1     |       |            |            |

|---|------------|------------|-----|----------------|------------|------|-------|-------|------------|------------|

| 6 | <b>Y</b> 5 | <u>Y6</u>  | GND | <b>Y</b> 7     | PWR<br>DWN | FBIN | VDDQ  | FBOUT | <u>Y</u> 8 | <b>Y</b> 9 |

| 5 | <u>Y</u> 5 | <b>Y</b> 6 | GND | <del>Y</del> 7 | VDDQ       | FBIN | FBOUT | GND   | <b>Y</b> 8 | <u>Y9</u>  |

| 4 | GND        | VDDQ       | NC  | NC             |            |      | NC    | NC    | VDDQ       | GND        |

| 3 | GND        | VDDQ       | NC  | NC             |            |      | NC    | NC    | VDDQ       | GND        |

| 2 | <u>Y</u> 0 | Y1         | GND | <u>Y2</u>      | VDDQ       | CLK  | AVDD  | GND   | <b>Y</b> 3 | <u>Y</u> 4 |

| 1 | Y0         | <u>Y</u> 1 | GND | <b>Y</b> 2     | VDDQ       | CLK  | VDDQ  | AGND  | <u>Y</u> 3 | Y4         |

|   | Α          | В          | С   | D              | E          | F    | G     | Н     | J          | K          |

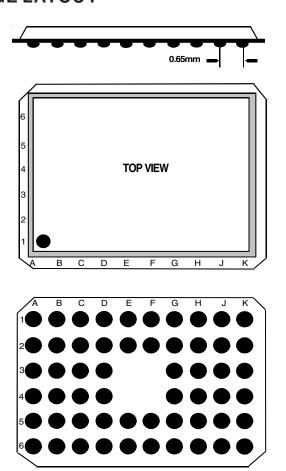

VFBGA TOP VIEW

## **56 BALL VFBGA PACKAGE LAYOUT**

#### **PIN CONFIGURATIONS**

VFQFPN TOP VIEW

# **ABSOLUTE MAXIMUM RATINGS**(1)

| Symbol                         | Rating                          | Max                | Unit |

|--------------------------------|---------------------------------|--------------------|------|

| Vddq, AVdd                     | Supply Voltage Range            | -0.5 to +3.6       | V    |

| V <sub>I</sub> <sup>(2)</sup>  | Input Voltage Range             | -0.5 to VDDQ + 0.5 | V    |

| Vo <sup>(2)</sup>              | Voltage range applied to any    | -0.5 to VDDQ + 0.5 | V    |

|                                | output in the high or low state |                    |      |

| lık                            | Input Clamp Current             | -50                | mA   |

| (VI <0)                        |                                 |                    |      |

| Іок                            | Output Clamp Current            | ±50                | mA   |

| (Vo <0 or                      |                                 |                    |      |

| VO > VDDQ)                     |                                 |                    |      |

| lo                             | Continuous Output Current       | ±50                | mA   |

| $(Vo = 0 \text{ to } V_{DDQ})$ |                                 |                    |      |

| VDDQ or GND                    | Continuous Current              | ±100               | mA   |

| TSTG                           | Storage Temperature Range       | -65 to +150        | °C   |

#### NOTES:

- Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause

permanent damage to the device. This is a stress rating only and functional operation

of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating

conditions for extended periods may affect reliability.

- The input and output negative-voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

- The maximum package power dissipation is calculated using a junction temperature of 150°C and a board trace length of 750 mils.

TSSOP TOP VIEW

#### CAPACITANCE(1)

|                       | i                       |       |      |      |      |

|-----------------------|-------------------------|-------|------|------|------|

| Parameter Description |                         | Min.  | Тур. | Max. | Unit |

| CIN                   | Input Capacitance       | 2.5   | _    | 3.5  | pF   |

|                       | VI = VDDQ or GND        |       |      |      |      |

| CI(∆)                 | Delta Input Capacitance | -0.25 | _    | 0.25 | pF   |

|                       | VI = VDDQ or GND        |       |      |      |      |

| CL                    | Load Capacitance        | _     | 14   | _    | pF   |

#### NOTE:

1. Unused inputs must be held high or low to prevent them from floating.

# **RECOMMENDED OPERATING CONDITIONS**

| Symbol | Parameter                      |               | Min.      | Тур. | Max. | Unit |

|--------|--------------------------------|---------------|-----------|------|------|------|

| AVDD   | Supply Voltage                 |               | VDDQ-0.12 | VDDQ | 2.7  | V    |

| VDDQ   | I/O Supply Voltage             | PC1600-PC2700 | 2.3       | 2.5  | 2.7  | V    |

|        |                                | PC3200        | 2.5       | 2.6  | 2.7  |      |

| TA     | Operating Free-Air Temperature |               | -40       | _    | +85  | °C   |

# PIN DESCRIPTION (TSSOP/TVSOP)

| Pin Name     | Pin Number                           | Description                            |

|--------------|--------------------------------------|----------------------------------------|

| AGND         | 17                                   | Ground for analog supply               |

| AVDD         | 16                                   | Analog supply                          |

| CLK, CLK     | 13, 14                               | Differential clock input               |

| FBIN, FBIN   | 35, 36                               | Feedbackdifferential clock input       |

| FBOUT, FBOUT | 32, 33                               | Feedback differential clock output     |

| GND          | 1, 7, 8, 18, 24, 25, 31, 41, 42, 48  | Ground                                 |

| PWRDWN       | 37                                   | Output enable for Y and $\overline{Y}$ |

| VDDQ         | 4, 11, 12, 15, 21, 28, 34, 38, 45    | I/O supply                             |

| Y[0:9]       | 3, 5, 10, 20, 22, 27, 29, 39, 44, 46 | Buffered output of input clock, CLK    |

| Y[0:9]       | 2, 6, 9, 19, 23, 26, 30, 40, 43, 47  | Buffered output of input clock, CLK    |

# **PIN DESCRIPTION (VFBGA)**

| Pin Name     | Pin Number                             | Description                            |

|--------------|----------------------------------------|----------------------------------------|

| AGND         | H1                                     | Ground for analog supply               |

| AVDD         | G2                                     | Analog supply                          |

| CLK, CLK     | F1, F2                                 | Differential clock input               |

| FBIN, FBIN   | F5, F6                                 | Feedback differential clock input      |

| FBOUT, FBOUT | H6, G5                                 | Feedback differential clock output     |

| GND          | A3, A4, C1, C2, C5, C6, H2, H5, K3, K4 | Ground                                 |

| PWRDWN       | E6                                     | Output enable for Y and $\overline{Y}$ |

| VDDQ         | B3, B4, E1, E2, E5, G1, G6, J3, J4     | I/O supply                             |

| Y[0:9]       | A1, A6, B2, B5, D1, D6, J2, J5, K1, K6 | Buffered output of input clock, CLK    |

| Y[0:9]       | A2, A5, B1, B6, D2, D5, J1, J6, K2, K5 | Buffered output of input clock, CLK    |

# PIN DESCRIPTION (MLF)

| Pin Name     | Pin Number                            | Description                            |

|--------------|---------------------------------------|----------------------------------------|

| AGND         | 9                                     | Groundforanalogsupply                  |

| AVDD         | 8                                     | Analog supply                          |

| CLK, CLK     | 5, 6                                  | Differential clock input               |

| FBIN, FBIN   | 25,26                                 | Feedback differential clock input      |

| FBOUT, FBOUT | 21,22                                 | Feedback differential clock output     |

| GND          | 1, 10                                 | Ground                                 |

| PWRDWN       | 27                                    | Output enable for Y and $\overline{Y}$ |

| VDDQ         | 4, 7, 13, 18, 23, 24, 28, 33, 38      | I/O supply                             |

| Y[0:9]       | 3, 12, 14, 17, 19, 29, 32, 34, 37, 39 | Buffered output of input clock, CLK    |

| Y[0:9]       | 2, 11, 15, 16, 20, 30, 31, 35, 36, 40 | Buffered output of input clock, CLK    |

#### **FUNCTION TABLE**(1)

| INPUTS                   |        |        |        | OUTPUTS |    |       |       |              |

|--------------------------|--------|--------|--------|---------|----|-------|-------|--------------|

| AVDD                     | PWRDWN | CLK    | CLK    | Υ       | Ϋ́ | FBOUT | FBOUT | PLL          |

| GND                      | Н      | L      | Н      | L       | Н  | L     | Н     | Bypassed/OFF |

| GND                      | Н      | Н      | L      | Н       | L  | Н     | L     | Bypassed/OFF |

| Х                        | L      | L      | Н      | Z       | Z  | Z     | Z     | OFF          |

| Х                        | L      | Н      | L      | Z       | Z  | Z     | Z     | OFF          |

| Nominal <sup>(2)</sup>   | Н      | L      | Н      | L       | Н  | L     | Н     | ON           |

| Nominal <sup>(2)</sup>   | Н      | Н      | L      | Н       | L  | Н     | L     | ON           |

| Nominal <sup>(2,3)</sup> | Х      | <20MHz | <20MHz | Z       | Z  | Z     | Z     | OFF          |

#### NOTES:

- 1. H = HIGH Voltage Level

- L = LOW Voltage Level

- Z = High-Impedance OFF-State

- X = Don't Care

- 2. AVDD nominal is 2.5V for PC1600, PC2100, and PC2700. AVDD nominal is 2.6V for PC3200.

- 3. Additional feature that senses when the clock input is less than approximately 20MHz and places the part in sleep mode. Reciever inputs and PLL are turned off and outputs = tristate.

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR PC1600 - PC2700

Following Conditions Apply Unless Otherwise Specified:

Commercial:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ; Industrial:  $TA = -40^{\circ}C$  to  $+85^{\circ}C$

| Symbol                 | Parameter                            | Conditions                                                | Min.       | Тур. | Max.       | Unit |

|------------------------|--------------------------------------|-----------------------------------------------------------|------------|------|------------|------|

| Vik                    | Input Clamp Voltage (All Inputs)     | VDDQ = 2.3V, II = -18mA                                   | _          | _    | -1.2       | V    |

| VIL(dc)                | Static Input LOW Voltage             | PWRDWN                                                    | -0.3       | _    | 0.7        | V    |

| VIH (dc)               | Static Input HIGH Voltage            | PWRDWN                                                    | 1.7        | _    | VDDQ + 0.3 |      |

| VIL (ac)               | Dynamic Input LOW Voltage            | CLK, CLK, FBIN, FBIN                                      | _          | _    | 0.7        | ٧    |

| VIH (ac)               | Dynamic Input HIGH Voltage           | CLK, CLK, FBIN, FBIN                                      | 1.7        |      | VDDQ       |      |

| Vol                    | Output LOW Voltage                   | AVDD/VDDQ = Min., IoL = $100\mu$ A                        | _          |      | 0.1        | V    |

|                        |                                      | AVDD/VDDQ = Min., IOL = 12mA                              | _          |      | 0.6        | ĺ    |

| Vон                    | Output HIGH Voltage                  | AVDD/VDDQ = Min., IOH = $-100\mu$ A                       | VDDQ-0.1   |      |            | V    |

|                        |                                      | AVDD/VDDQ = Min., IOH = -12mA                             | 1.7        |      |            | ĺ    |

| Vıx                    | Input Differential Cross Voltage     |                                                           | VDDQ/2-0.2 |      | VDDQ/2+0.2 | V    |

| VID(DC) <sup>(1)</sup> | DC Input Differential Voltage        |                                                           | 0.36       |      | VDDQ + 0.6 | V    |

| VID(AC) <sup>(1)</sup> | AC Input Differential Voltage        |                                                           | 0.7        |      | VDDQ + 0.6 | V    |

| lin                    | Input Current                        | VDDQ = 2.7V, VI = 0V to 2.7V                              |            |      | ±10        | μΑ   |

| IDDPD                  | Power-Down Current on VDDQ and AVDD  | AVDD/VDDQ = Max., CLK = $0MHz$ or $\overline{PWRDWN} = L$ | _          | 100  | 200        | μΑ   |

| IDDQ                   | Dynamic Power Supply Current on VDDQ | AVDD/VDDQ = Max., CLK = 200MHz, $120\Omega/14pF$          | _          | 320  | 360        | mA   |

|                        |                                      | AVDD/VDDQ = Max., CLK = 170MHz, $120\Omega/14pF$          | _          | 250  | 300        |      |

| ladd                   | Dynamic Power Supply Current on AVDD | AVDD/VDDQ = Max., CLK = 170MHz                            | _          |      | 12         | mA   |

#### NOTE:

1. VID is the magnitude of the difference between the input level on CLK and the input level on  $\overline{\text{CLK}}$ .

# DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE FOR PC3200

Following Conditions Apply Unless Otherwise Specified:

Commercial:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$ ; Industrial:  $TA = -40^{\circ}C$  to  $+85^{\circ}C$

| Symbol                 | Parameter                            | Conditions                                                | Min.       | Тур. | Max.       | Unit |

|------------------------|--------------------------------------|-----------------------------------------------------------|------------|------|------------|------|

| Vik                    | Input Clamp Voltage (All Inputs)     | VDDQ = 2.5V, II = -18mA                                   | _          | _    | -1.2       | V    |

| VIL(dc)                | Static Input LOW Voltage             | PWRDWN                                                    | -0.3       | _    | 0.7        | V    |

| VIH (dc)               | Static Input HIGH Voltage            | PWRDWN                                                    | 1.7        | _    | VDDQ + 0.3 |      |

| VIL(ac)                | Dynamic Input LOW Voltage            | CLK, CLK, FBIN, FBIN                                      | _          | _    | 0.7        | V    |

| VIH (ac)               | Dynamic Input HIGH Voltage           | CLK, CLK, FBIN, FBIN                                      | 1.7        |      | VDDQ       |      |

| Vol                    | Output LOW Voltage                   | AVDD/VDDQ = Min., IoL = 100μA                             | _          |      | 0.1        | V    |

|                        |                                      | AVDD/VDDQ = Min., IOL = 12mA                              | _          |      | 0.6        |      |

| Vон                    | Output HIGH Voltage                  | AVDD/VDDQ = Min., IOH = -100μA                            | VDDQ-0.1   |      |            | V    |

|                        |                                      | AVDD/VDDQ = Min., IOH = -12mA                             | 1.7        |      |            |      |

| Vıx                    | Input Differential Cross Voltage     |                                                           | VDDQ/2-0.2 |      | VDDQ/2+0.2 | V    |

| VID(DC) <sup>(1)</sup> | DC Input Differential Voltage        |                                                           | 0.36       |      | VDDQ + 0.6 | V    |

| VID(AC) <sup>(1)</sup> | AC Input Differential Voltage        |                                                           | 0.7        |      | VDDQ + 0.6 | V    |

| lin                    | Input Current                        | VDDQ = 2.7V, VI = 0V to 2.7V                              |            |      | ±10        | μΑ   |

| IDDPD                  | Power-Down Current on VDDQ and AVDD  | AVDD/VDDQ = Max., CLK = $0MHz$ or $\overline{PWRDWN} = L$ | _          | 100  | 200        | μΑ   |

| IDDQ                   | Dynamic Power Supply Current on VDDQ | AVDD/VDDQ = Max., CLK = 200MHz, $120\Omega/14pF$          | _          | 320  | 360        | mA   |

|                        |                                      | AVDD/VDDQ = Max., CLK = 200MHz, 120Ω/14pF                 | _          | 250  | 300        |      |

| ladd                   | Dynamic Power Supply Current on AVDD | AVDD/VDDQ = Max., CLK = 200MHz                            | _          |      | 12         | mA   |

#### NOTE:

#### **TIMING REQUIREMENTS FOR PC1600 - PC2700**

| Symbol | Parameter                                    | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| fclk   | Operating Clock Frequency <sup>(1,2)</sup>   | 60   | 200  | MHz  |

|        | Application Clock Frequency <sup>(1,3)</sup> | 60   | 200  | MHz  |

| toc    | Input Clock Duty Cycle                       | 40   | 60   | %    |

| t_     | Stabilization Time <sup>(4)</sup>            |      | 100  | μs   |

#### NOTES:

- 1. The PLL will track a spread spectrum clock input.

- 2. Operating clock frequency is the range over which the PLL will lock, but may not meet all timing specifications.

- 3. Application clock frequency is the range over which timing specifications apply.

- 4. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up.

#### TIMING REQUIREMENTS FOR PC3200

| Symbol | Parameter                                    | Min. | Max. | Unit |

|--------|----------------------------------------------|------|------|------|

| fclk   | Operating Clock Frequency <sup>(1,2)</sup>   | 60   | 220  | MHz  |

|        | Application Clock Frequency <sup>(1,3)</sup> | 60   | 220  | MHz  |

| toc    | Input Clock Duty Cycle                       | 40   | 60   | %    |

| t_     | StabilizationTime <sup>(4)</sup>             |      | 100  | μs   |

#### NOTES:

- 1. The PLL will track a spread spectrum clock input.

- 2. Operating clock frequency is the range over which the PLL will lock, but may not meet all timing specifications.

- 3. Application clock frequency is the range over which timing specifications apply.

- 4. Stabilization time is the time required for the integrated PLL circuit to obtain phase lock of its feedback signal to its reference signal after power up.

<sup>1.</sup> VID is the magnitude of the difference between the input level on CLK and the input level on CLK.

# **SWITCHING CHARACTERISTICS FOR PC1600 - PC2700**

| Symbol              | Description                                        | Test Conditions                               | Min.                | Typ. <sup>(1)</sup> | Max.   | Unit |

|---------------------|----------------------------------------------------|-----------------------------------------------|---------------------|---------------------|--------|------|

| tPLH <sup>(1)</sup> | LOW to HIGH Level Propagation Delay Time           | Test mode, CLK to any output                  |                     | 4.5                 |        | ns   |

| tPHL <sup>(1)</sup> | HIGH to LOW Level Propagation Delay Time           | Test mode, CLK to any output                  |                     | 4.5                 |        | ns   |

| tJIT(PER)           | Jitter (period), see figure 6                      | 66MHz                                         | -90                 |                     | 90     | ps   |

|                     |                                                    | 100/ 133/ 167/ 200 MHz                        | -75                 |                     | 75     | ]    |

| tJIT(CC)            | Jitter (cycle-to-cycle), see figure 3              | 66MHz                                         | -180                |                     | 180    | ps   |

|                     |                                                    | 100/ 133/ 167/ 200 MHz                        | -75                 |                     | 75     | 1    |

| tJIT(HPER)          | Half-Period Jitter, see figure 7                   | 66MHz                                         | -160                |                     | 160    | ps   |

|                     |                                                    | 100/ 133/ 167/ 200 MHz                        | -100                |                     | 100    | 1    |

| tslr(0)             | Output Clock Slew Rate (Single-Ended)              | 100/ 133/ 167/ 200 MHz (20% to 80%)           | 1                   |                     | 2.5    | V/ns |

| tslr(i)             | Input Clock Slew Rate                              |                                               | 1                   |                     | 4      | V/ns |

| t(∅)                | Static Phase Offset, see figure 4 <sup>(2,3)</sup> | 66/ 100/ 133/ 167/ 200 MHz                    | -50                 |                     | 50     | ps   |

| tsk(o)              | Output Skew, see figure 5                          |                                               |                     |                     | 75     | ps   |

| tR,tF               | Output Rise and Fall Times (20% to 80%)            | Load: 120Ω / 14pF                             | 650                 |                     | 900    | ps   |

| Vox <sup>(5)</sup>  | Output Differential Voltage                        | Differential outputs are terminated           | VDDQ/2              |                     | VDDQ/2 | V    |

|                     |                                                    | with 120 $\Omega$                             | -0.15               |                     | + 0.15 |      |

| The PLL on          | the CSPT857 will meet all the above test paramete  | rs while supporting SSC synthesizers (4) with | n the following par | ameters:            |        | •    |

| SSC                 | Modulation Frequency                               | _                                             | 30                  | _                   | 50     | KHz  |

| SSC                 | Clock Input Frequency Deviation                    | _                                             | 0                   |                     | -0.5   | %    |

| f3dB                | PLL Loop Bandwidth                                 | _                                             | _                   | 5                   | _      | MHz  |

#### NOTES:

- 1. Refers to transition of non-inverting output.

- 2. Static phase offset does not include jitter.

- 3.  $t(\phi)$  is measured with input clock slew rate tslr(i) = 2V/ns and an input differential voltage ViD of 1.75V.

- 4. The SSC requirements meet the Intel PC100 SDRAM Registered DIMM specification.

- 5. Vox is specified at the SDRAM clock input or test load.

#### SWITCHING CHARACTERISTICS FOR PC3200

| Symbol              | Description                                        | Test Conditions                                          | Min.                | Typ. <sup>(1)</sup> | Max.   | Unit |

|---------------------|----------------------------------------------------|----------------------------------------------------------|---------------------|---------------------|--------|------|

| tPLH <sup>(1)</sup> | LOW to HIGH Level Propagation Delay Time           | Test mode, CLK to any output                             |                     | 4.5                 |        | ns   |

| tPHL <sup>(1)</sup> | HIGH to LOW Level Propagation Delay Time           | Test mode, CLK to any output                             |                     | 4.5                 |        | ns   |

| tJIT(PER)           | Jitter (period), see figure 6                      | 66MHz                                                    | -90                 |                     | 90     | ps   |

|                     |                                                    | 200 MHz                                                  | -50                 |                     | 50     |      |

| tJIT(CC)            | Jitter (cycle-to-cycle), see figure 3              | 66MHz                                                    | -180                |                     | 180    | ps   |

|                     |                                                    | 200 MHz                                                  | -75                 |                     | 75     | 1    |

| tjit(HPER)          | Half-Period Jitter, see figure 7                   | 66MHz                                                    | -160                |                     | 160    | ps   |

|                     |                                                    | 200 MHz                                                  | -75                 |                     | 75     | 1    |

| tslr(0)             | Output Clock Slew Rate (Single-Ended)              | 200 MHz (20% to 80%)                                     | 1                   |                     | 2.5    | V/ns |

| tslr(i)             | Input Clock Slew Rate                              |                                                          | 1                   |                     | 4      | V/ns |

| t(∅)                | Static Phase Offset, see figure 4 <sup>(2,3)</sup> | 200 MHz                                                  | -50                 |                     | 50     | ps   |

| tsk(o)              | Output Skew, see figure 5                          |                                                          |                     |                     | 75     | ps   |

| tR,tF               | Output Rise and Fall Times (20% to 80%)            | Load: 120Ω / 14pF                                        | 650                 |                     | 900    | ps   |

| Vox <sup>(5)</sup>  | Output Differential Voltage                        | Differential outputs are terminated                      | VDDQ/2              |                     | VDDQ/2 | V    |

|                     |                                                    | with 120 $\Omega$                                        | -0.15               |                     | + 0.15 |      |

| The PLL on          | the CSPT857 will meet all the above test paramete  | ers while supporting SSC synthesizers <sup>(4)</sup> wit | h the following par | ameters:            |        |      |

| SSC                 | Modulation Frequency                               | _                                                        | 30                  | _                   | 50     | KHz  |

| SSC                 | Clock Input Frequency Deviation                    | _                                                        | 0                   | _                   | -0.5   | %    |

| f3dB                | PLL Loop Bandwidth                                 | _                                                        | _                   | 5                   | _      | MHz  |

#### NOTES:

- 1. Refers to transition of non-inverting output.

- 2. Static phase offset does not include jitter.

- 3.  $t(\phi)$  is measured with input clock slew rate tslr(i) = 2V/ns and an input differential voltage ViD of 1.75V.

- 4. The SSC requirements meet the Intel PC100 SDRAM Registered DIMM specification.

- 5. Vox is specified at the SDRAM clock input or test load.

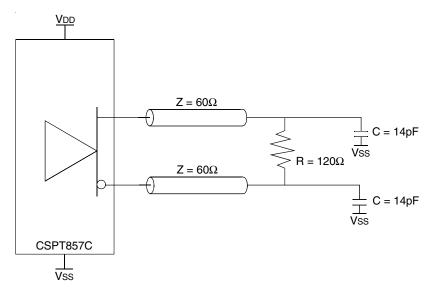

Figure 1. Output Load

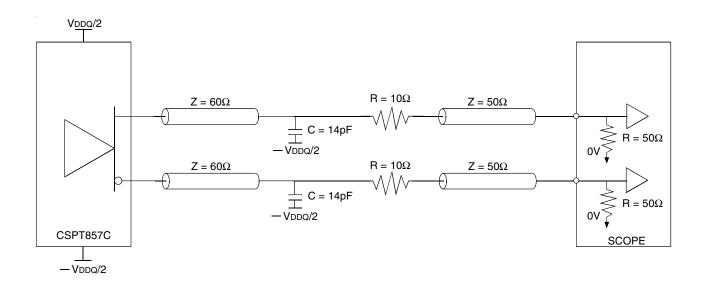

Figure 2. Output Load Test Circuit

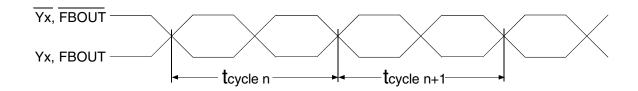

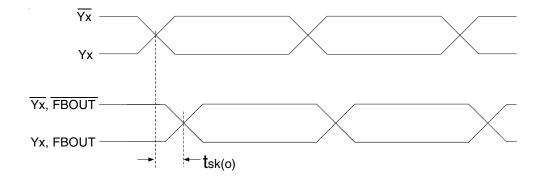

$$t_{jit(cc)} = t_{cycle n} - t_{cycle n+1}$$

Figure 3. Cycle-to-Cycle jitter

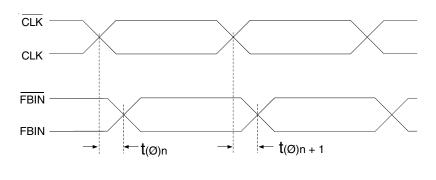

$$t(\emptyset) = \frac{\sum_{1}^{n = N} t(\emptyset)n}{N}$$

(N is a large number of samples)

Figure 4. Static Phase Offset

Figure 5. Output Skew

$$t_{jit(per)} = t_{cycle n} - \frac{1}{f_o}$$

Figure 6. Period jitter

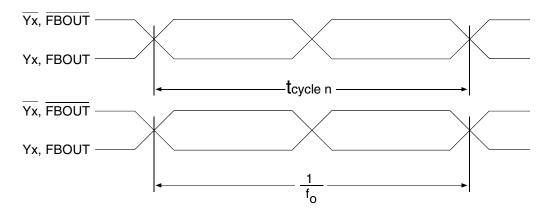

Figure 7. Half-Period jitter

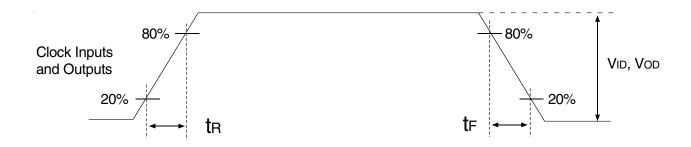

Figure 8. Input and Output Slew Rates

## **APPLICATION INFORMATION**

|                 |                            | Clock Loading on the PLL outputs (pF) |      |

|-----------------|----------------------------|---------------------------------------|------|

| Clock Structure | # of SDRAM Loads per Clock | Min.                                  | Max. |

| #1              | 2                          | 4                                     | 7    |

| #2              | 4                          | 8                                     | 14   |

# **APPLICATION INFORMATION**

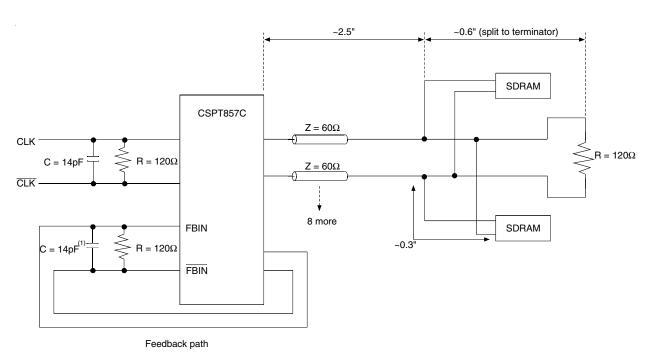

Figure 9. Clock Structure 1

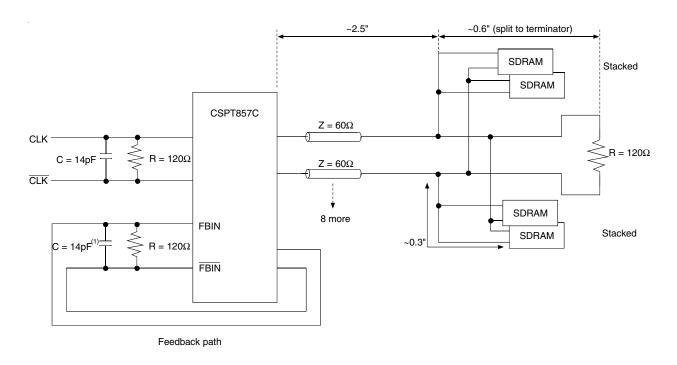

Figure 10. Clock Structure 2

#### NOTE:

1. Memory module vendors may need to adjust the feedback capacitive load in order to meet DDR SDRAM registered DIMM timing requirements.

#### **ORDERING INFORMATION**