Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#### **FEATURES**

- 2.5V-3.3V Operation

- Ultra-Low Phase Noise Floor

- o LVPECL -167dBc/Hz

- o LVDS -165dBc/Hz

- Configurable

- LVPECL or LVDS Output

- o +1 or +2

- Enable Active High or Low

- > 1GHz+ Bandwidth

- RoHS Compliant Pb Free Packages

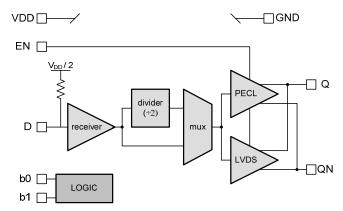

#### **BLOCK DIAGRAM**

# **DESCRIPTION**

- The CTSLV310 is a configurable LVPECL, LVDS buffer & translator IC that is optimized for ultra-low phase noise and 2.5V-3.3V nominal supply voltage. It is particularly useful in converting crystal or SAW based oscillators into LVPECL and LVDS outputs for up to 1GHz of bandwidth. For a design that includes gain in the signal path, refer to the <a href="CTSLV315">CTSLV315</a>.

- A configurable IC design capable of providing LVPECL or LVDS outputs, ÷1 or ÷2 function, and active high or active low enable selection. See Table 1 for details of the configurations options that provide designers with a single IC buffer/translator solution that is extremely compact, flexible and high performance.

- 8 configurations which are determined by the static voltage levels of b-0 and b-1. Table 1 details the configurations.

**Table 1 - Possible IC Configuration**

| Configuration Bits |      | Functional Configuration    |             |          |  |

|--------------------|------|-----------------------------|-------------|----------|--|

| b-0                | b-1  | Output Type Enable Polarity |             | Division |  |

| Open               | Open | LVPECL                      | Active High | ÷1       |  |

| Open               | Low  | LVPECL                      | Active High | ÷2       |  |

| Open               | High | LVPECL                      | Active Low  | ÷1       |  |

| Low                | Open | LVPECL                      | Active Low  | ÷2       |  |

| Low                | Low  | LVDS                        | Active High | ÷1       |  |

| Low                | High | LVDS                        | Active High | ÷2       |  |

| High               | Open | LVDS                        | Active Low  | ÷1       |  |

| High               | Low  | LVDS                        | Active Low  | ÷2       |  |

| High               | High | Not Used                    | Not Used    | Not Used |  |

CTSLV310

# **Ultra-Low Phase Noise LVPECL, LVDS Buffer and Translator**

SON8, MSOP8

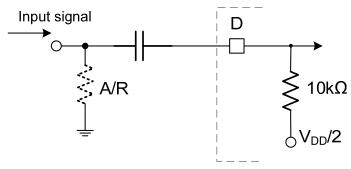

#### **Input Termination**

The D input bias is  $V_{DD}/2$  fed through an internal  $10k\Omega$  resistor. For clock applications, an input signal of at least 750m  $V_{PP}$  ensures the CTSLV10 meets AC specifications. The input should also be AC coupled to maintain a 50% duty cycle on the outputs. The input can be driven to any voltage between 0V and  $V_{DD}$  without damage or waveform degradation.

#### **LVPECL Output Termination Techniques**

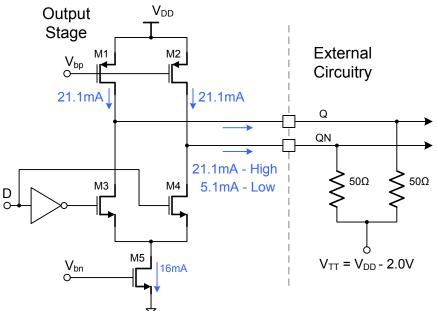

#### **DC** Coupling

The LVPECL compatible output stage of the CTSLV310 uses a current drive topology to maximize switching speed as illustrated below. Two current source PMOS transistors (M1-M2) feed the output pins. M5 is an NMOS current source which is switched by M3 and M4. When M4 is on, M5 takes current from M2. This produces an output current of 5.1mA (low output state). M3 is off, and the entire 21.1mA flows through the output pin. The associated output voltage swings match LVPECL levels when external  $50\Omega$  resistors terminate the outputs.

Both Q and QN should always be terminated identically to avoid waveform distortion and circulating current caused by unsymmetrical loads. This rule should be followed even if only one output is in use.

**Typical Output Termination**

CTSLV310

# Ultra-Low Phase Noise LVPECL, LVDS Buffer and Translator

SON8, MSOP8

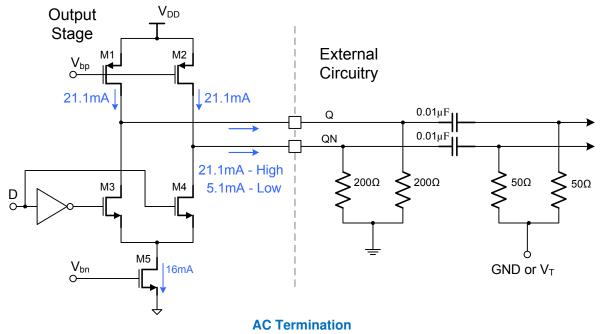

#### **AC Coupling**

Clock applications or phase noise/frequency domain testing scenarios typically require AC coupling. The illustration below shows the AC coupling technique. The  $200\Omega$  resistors form the required DC loads, and the  $50\Omega$  resistors provide the AC termination. The parallel combination of the  $200\Omega$  and  $50\Omega$  resistors results in a net  $40\Omega$  AC load termination. In many cases this will work well. If necessary, the  $50\Omega$  resistors can be increased to about  $56\Omega$ . Alternately, bias tees combined with current setting resistors will eliminate the lowered AC load impedance. The  $50\Omega$  resistors are typically connected to ground but can be connected to the bias level needed by the succeeding stage.

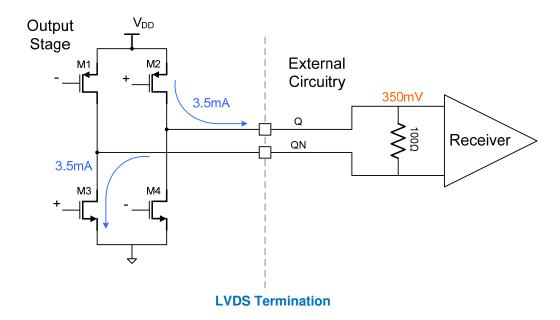

#### **LVDS Output Termination Technique**

The following LVDS termination is compliant to the LVDS specification TIA/EIA-644A.

CTS.

#### **ELECTRICAL SPECIFICATIONS**

# **Absolute Maximum Rating**

| Symbol                      | Characteristic                           | Conditions                 | Min                  | Тур | Max                  | Unit |  |

|-----------------------------|------------------------------------------|----------------------------|----------------------|-----|----------------------|------|--|

| V                           | Cupply Voltage                           |                            | 2.375                | 2.5 |                      | V    |  |

| $V_{DD}$                    | Supply Voltage                           |                            |                      | 3.3 | 3.6                  | V    |  |

| V                           | Absolute Max Power Supply                | Continuous                 |                      |     | 3.6                  | V    |  |

| V <sub>ABSOLUTE</sub>       | Absolute Max Fower Supply                | t ≤ 1s                     |                      |     | 5.5                  | V    |  |

| T <sub>OP</sub>             | Operating Temperature Range              |                            | -40                  |     | 85                   | °C   |  |

| T <sub>STORAGE</sub>        | Storage Temperature Range                |                            | -65                  |     | 150                  | °C   |  |

|                             |                                          | D                          | -0.5                 |     | V <sub>DD</sub> +0.5 |      |  |

| V                           | Maximum Input Voltages                   | EN                         | -0.5                 |     | $V_{DD} + 0.5$       | V    |  |

| $V_{I\_MAX}$                | waxiinum input voitages                  | b0                         | -0.5                 |     | $V_{DD} + 0.5$       |      |  |

|                             |                                          | b1                         | -0.5                 |     | $V_{DD} + 0.5$       |      |  |

| 1                           | b-0, b-1 Input High Current              | b-0, b-1 = V <sub>DD</sub> |                      |     | 11                   | uA   |  |

| I <sub>b0,b1</sub>          | b-0, b-1 Input Low Current               |                            | -11                  |     |                      | uA   |  |

| Vt <sub>b0,b1</sub>         | b-0, b-1 Input High Voltage<br>Threshold |                            | V <sub>DD</sub> -0.5 |     | $V_{DD}$             | V    |  |

| <b>ν</b> ι <sub>b0,b1</sub> | b-0, b-1 Input Low Voltage<br>Threshold  |                            | 0                    |     | 0.5                  | V    |  |

| I <sub>EN</sub>             | EN Input Current                         |                            | -4                   |     | 3                    | uA   |  |

| Vt <sub>EN</sub>            | EN Input High Voltage<br>Threshold       |                            | V <sub>DD</sub> -0.5 |     | $V_{DD}$             | V    |  |

| VIEN                        | EN Input Low Voltage<br>Threshold        |                            | 0                    |     | 0.5                  | V    |  |

|                             |                                          | Human Body Model           | 2000                 |     |                      |      |  |

| ESD                         | ESD Ratings                              | Machine Model              | 200                  |     |                      | V    |  |

| LOD                         | 202                                      | Charged Device<br>Model    | 2000                 |     |                      |      |  |

RevA0215

# **LVPECL Performance Specifications**

| Symbol               | Characteristic                              | Conditions                        | Min                   | Тур  | Max                   | Unit                   |

|----------------------|---------------------------------------------|-----------------------------------|-----------------------|------|-----------------------|------------------------|

| f                    | May Input Fraguency                         | ÷1 mode                           | 1000                  |      |                       | MHz                    |

| f <sub>MAX</sub>     | Max Input Frequency                         | ÷2 mode                           | 1600                  |      |                       | IVITZ                  |

| $R_L$                | Output Loading                              |                                   |                       | 50   |                       | Ω                      |

| R <sub>BIAS</sub>    | Input Bias Resistor                         | D input to V <sub>DD</sub> /2 ref |                       | 10k  |                       | Ω                      |

| W                    | Input Voltage Cwing                         | minimum <sup>1</sup>              | 0.2                   |      |                       | V                      |

| $V_{IN\_SWING}$      | Input Voltage Swing                         | recommended <sup>1</sup>          | 0.6                   |      |                       | $V_{PP}$               |

|                      |                                             | $V_{DD}$ = 2.5V, HIGH             | V <sub>DD</sub> -1.25 |      | V <sub>DD</sub> -0.88 | V                      |

| V                    | Voltago Output Lavola                       | $V_{DD}$ = 2.5V, LOW              | V <sub>DD</sub> -1.86 |      | V <sub>DD</sub> -1.66 | V                      |

| V <sub>OUT</sub>     | Voltage Output Levels                       | $V_{DD}$ = 3.3V, HIGH             | V <sub>DD</sub> -1.15 |      | V <sub>DD</sub> -0.88 | V                      |

|                      |                                             | $V_{DD}$ = 3.3V, LOW              | V <sub>DD</sub> -1.86 |      | V <sub>DD</sub> -1.75 | V                      |

|                      |                                             | V <sub>DD</sub> = 2.5V            | 0.54                  |      | 0.93                  | V <sub>PP</sub> , Q/QN |

| V                    | V <sub>OD</sub> Differential Output Voltage |                                   | 0.75                  |      | 5.47                  | dBm,<br>Q/QN           |

| V <sub>OD</sub>      |                                             |                                   | 0.74                  |      | 0.93                  | V <sub>PP</sub> , Q/QN |

|                      |                                             | V <sub>DD</sub> = 3.3V            | 3.49                  |      | 5.47                  | dBm,<br>Q/QN           |

| $t_R / t_F$          | Output Rise/Fall Time                       | 80%-20%                           | 100                   |      | 205                   | ps                     |

| PN                   | Phase Noise Floor                           | 1MHz Offset                       | -167                  |      |                       | dBc/Hz                 |

| J <sub>INTEG</sub>   | Integrated Jitter:<br>12kHz-20MHz           | 155MHz Carrier                    | 26                    |      |                       | fs                     |

| T <sub>ENABLE</sub>  | Enable Time <sup>2</sup>                    | EN = active                       |                       |      | 15                    | us                     |

| T <sub>DISABLE</sub> | Disable Time <sup>2</sup>                   | EN = disabled                     |                       |      | 0.5                   | us                     |

| T <sub>PROP</sub>    | Propagation Delay <sup>3</sup>              |                                   | 0.9                   |      | 2.2                   | ns                     |

| I                    | Power Supply Current                        | EN = active <sup>4</sup>          |                       | 28.5 |                       | mA                     |

| I <sub>DD</sub>      | r ower Suppry Current                       | EN = disabled <sup>5</sup>        |                       |      | 5                     | IIIA                   |

<sup>1</sup> Phase noise floor performance is dependent upon input voltage swing. Voltage swing values below recommended values may result in degraded phase noise values.

Into and out of tri-state condition.

Time from D crossing  $V_{DD}/2$  to Q=QN.

$V_{DD}$  =3.3V,  $F_{IN}$  @ 200MHz.

D = 0V.

# **LVDS Performance Specifications**

| Symbol                          | Characteristic                                      | Conditions                        | Min   | Тур  | Max   | Unit     |  |

|---------------------------------|-----------------------------------------------------|-----------------------------------|-------|------|-------|----------|--|

| f <sub>MAX</sub>                | Max Input Fraguency                                 | ÷1 mode                           | 1000  |      |       | MHz      |  |

| MAX                             | Max Input Frequency                                 | ÷2 mode                           | 1600  |      |       | IVITIZ   |  |

| $R_L$                           | Output Loading                                      |                                   |       | 100  |       | Ω        |  |

| R <sub>BIAS</sub>               | Input Bias Resistor                                 | D input to V <sub>DD</sub> /2 ref |       | 10k  |       | Ω        |  |

| \/                              | Input Valtage Swing                                 | minimum <sup>1</sup>              | 0.2   |      |       | V        |  |

| V <sub>IN_SWING</sub>           | Input Voltage Swing                                 | recommended <sup>1</sup>          | 0.6   |      |       | $V_{PP}$ |  |

| \/                              | Voltage Output Levels                               | V <sub>DD</sub> = 2.5V            | 290   |      | 454   | mV       |  |

| $V_{OUT}$                       | Voltage Output Levels                               | V <sub>DD</sub> = 3.3V            | 290   |      | 454   | IIIV     |  |

| V <sub>OD</sub>                 | Differential Output Voltage                         |                                   | -50   |      | 50    | mV       |  |

| V <sub>oc</sub>                 | Common Mode Output<br>Voltage                       |                                   | 1.125 |      | 1.375 | V        |  |

| ΔV <sub>OC</sub>                | Delta in Common Mode<br>Output Voltage <sup>2</sup> |                                   | -50   |      | 50    | mV       |  |

| $V_{OC,PP}$                     | Peak-to-Peak Common<br>Mode Output Voltage          |                                   |       |      | 100   | mV       |  |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time                               | 80%-20%                           | 120   |      | 220   | ps       |  |

| PN                              | Phase Noise Floor                                   | 1MHz Offset                       | -165  |      |       | dBc/Hz   |  |

| J <sub>INTEG</sub>              | Integrated Jitter:<br>12kHz - 20MHz                 | 155MHz Carrier                    | 36    |      |       | fs       |  |

| T <sub>ENABLE</sub>             | Enable Time <sup>3</sup>                            | EN = active                       |       |      | 4     | us       |  |

| T <sub>DISABLE</sub>            | Disable Time <sup>3</sup>                           | EN = disabled                     |       |      | 0.5   | us       |  |

| T <sub>PROP</sub>               | Propagation Delay <sup>4</sup>                      |                                   | 8.0   |      | 1.7   | ns       |  |

| 1                               | Dower Supply Current                                | EN = active <sup>5</sup>          |       | 12.9 |       | mΛ       |  |

| I <sub>DD</sub>                 | Power Supply Current                                | EN = disabled <sup>6</sup>        | 5     |      | 5     | mA       |  |

Phase noise floor performance is dependent upon input voltage swing. Voltage swing values below recommended values may result in degraded phase noise values.

Between logics states.

Into and out of tri-state condition.

Time from D crossing  $V_{DD}/2$  to Q=QN.

$V_{DD}$  =3.3V,  $F_{in}$  @ 200MHz.

D = 0V.

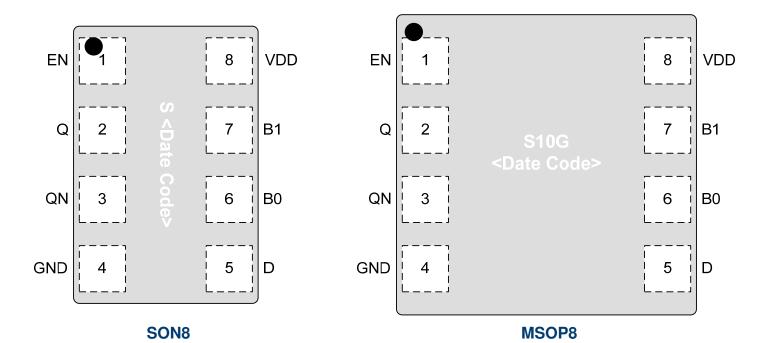

# **Pin Description and Configuration**

#### **Pin Assignments**

| Pin | Name     | I/O/P | Function          | Properties                  |

|-----|----------|-------|-------------------|-----------------------------|

| 1   | EN       | I     | Enable            | Configurable functionality  |

| 2   | Q        | 0     | Output Signal     | Configurable (LVPECL, LVDS) |

| 3   | QN       | 0     | Output Signal     | Configurable (LVPECL, LVDS) |

| 4   | GND      | Р     | Negative Supply   | 0V                          |

| 5   | D        | I     | Input Signal      |                             |

| 6   | В0       | 1     | Configuration Bit | Tertiary Levels             |

| 7   | B1       |       | Configuration Bit | Tertiary Levels             |

| 8   | $V_{DD}$ | Р     | Positive Supply   | 2.375V - 3.6V               |

# **PART ORDERING INFORMATION**

| Part Number | Package | Marking     |

|-------------|---------|-------------|

| CTSLV310QG  | SON8    | SYW         |

| CTSLV310TG  | MSOP8   | BE0G / YYWW |

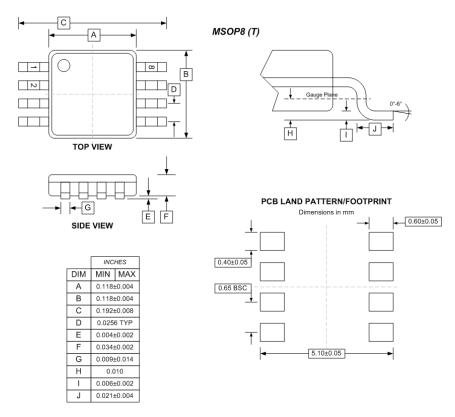

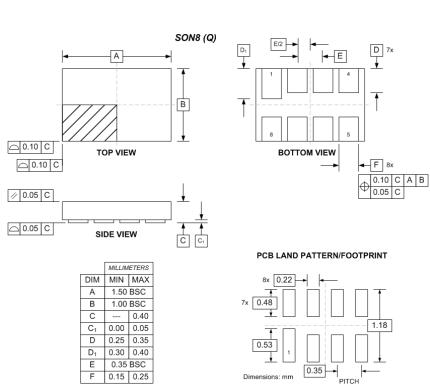

#### **PACKAGE DIMENSIONS**