Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs MLP8

#### **FEATURES**

- Selectable Divide Ratio

- Selectable Enable Priority and Threshold (CMOS or PECL)

- Tristate Compatible Outputs

- Input Buffer Powers Down when Disabled

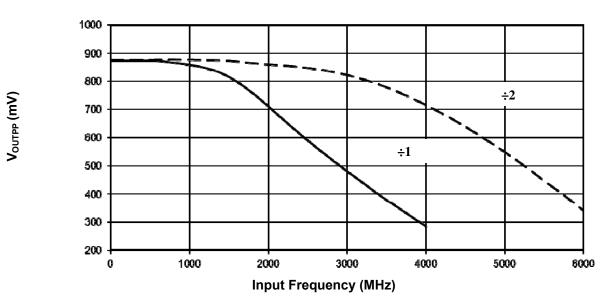

- High BW [1.5GHz (÷1), 3.0GHz (÷2)]

- 3V to 5.5V Power Supply

- -145dBc/Hz (÷1) Typ Noise Floor

- -151dBc/Hz (÷2) Typ Noise Floor

- RoHS Compliant Pb Free Packages

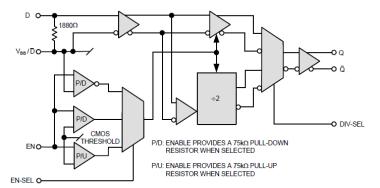

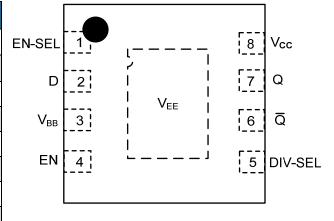

#### **BLOCK DIAGRAM**

#### **DESCRIPTION**

The CTSLV394 is a ÷1 or ÷2 clock generation part specifically designed to accommodate Colpitts or Pierce based oscillators. The tri-state compatible outputs allow for on-the-fly switching of multiple oscillators on a common bus. Other features are incorporated to reduce board components. A voltage reference and input biasing allows for easy oscillator interface.

The CTSLV394 provides a ÷ 2 mode of operation for more frequency options and is selectable with a single connection. A selectable enable is also provided which doubles as a reset when the CTSLV394 is in ÷2 mode. With a single connection, the enable can be selected to operate as active high or active low.

#### **ENGINEERING NOTES**

The CTSLV394 is a specialized  $\div 1$  or  $\div 2$  clock generation part including an enable/reset function. The divide ratio is selected with the DIV-SEL pin/pad. When DIV-SEL is open (NC), the CTSLV394 functions as a standard receiver. If DIV-SEL is connected to  $V_{EE}$ , it functions as a  $\div 2$  divider.

Enable (EN) functionality is selected with the EN-SEL pin/pad which has three valid states: open (NC),  $V_{\text{EE}}$ , or connected to  $V_{\text{EE}}$  via a  $20 \text{k}\Omega \pm 20\%$  resistor. Leaving EN-SEL open or connecting it to  $V_{\text{EE}}$  allows the EN pin/pad to function as an active high CMOS/TTL enable. When EN-SEL is open, an internal  $75 \text{k}\Omega$  pull-up resistor is selected which enables the outputs whenever EN is left open. When EN-SEL is connected to  $V_{\text{EE}}$ , an internal  $75 \text{k}\Omega$  pull-down resistor is selected which disables the outputs whenever EN is left open.

Connecting the EN-SEL to  $V_{EE}$  with a  $20k\Omega$  resistor will allow the EN pin/pad to function as an active low PECL/ECL enable with an internal  $75k\Omega$  pull-down resistor. In this mode, outputs are enabled when EN is left open (NC). The default logic condition can be overridden by connecting the EN to  $V_{CC}$  with an external resistor of  $\leq 20k\Omega$ . If the enable signal is CMOS (rail-to-rail) and the logic sense is active low (EN-SEL connected to  $V_{EE}$  with a  $20k\Omega$  resistor), the EN pin/pad voltage swing must be reduced using two external resistors. Contact the factory for details.

When the CTSLV394 is disabled, the Q and  $\overline{Q}$  outputs are forced LOW and the input buffer is powered down to minimize feed through. This feature allows tri-state compatible parallel output connections. Multiple CTSLV394 chip outputs can be wired together. Since both outputs are forced LOW in the disable mode, an enabled CTSLV394 can drive the output lines without interference from the unselected units. In addition, the CTSLV394 can be used in parallel connection with PECL/ECL parts whose outputs are high impedance when disabled.

The EN pin/pad also functions as a reset when the  $\div 2$  mode is selected. In the  $\div 2$  mode, the counter resets when the outputs are disabled.

The CTSLV394 provides a  $V_{BB}$  with an 1880 $\Omega$  internal bias resistor from D to  $V_{BB}$ . This feature allows AC coupling with minimal external components. The  $V_{BB}$  pin supports 1.5mA sink/source current and should be bypassed to ground or  $V_{CC}$  with a 0.01  $\mu$ F capacitor.

1

# LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs MLP8

#### **ELECTRICAL SPECIFICATIONS**

## Absolute Maximum Ratings are those values beyond which device life may be impaired.

| Symbol             | Characteristic                                | Condition            | Rating      | Unit |

|--------------------|-----------------------------------------------|----------------------|-------------|------|

| $V_{CC}$           | PECL Power Supply                             | V <sub>EE</sub> = 0V | 0 to + 6.0  | V    |

| $V_{I\_PECL}$      | PECL Input Voltage                            | V <sub>EE</sub> = 0V | 0 to + 6.0  | V    |

| $V_{EE}$           | ECL Power Supply                              | V <sub>CC</sub> = 0V | -6.0 to 0   | V    |

| $V_{I\_ECL}$       | ECL Input Supply                              | V <sub>CC</sub> = 0V | -6.0 to 0   | V    |

|                    | Output Current                                | Continuous           | 50          | m A  |

| I <sub>HGOUT</sub> | Output Current                                | Surge                | 100         | mA   |

| T <sub>A</sub>     | Operating Temperature Range                   | -                    | -40 to +85  | °C   |

| $T_{STG}$          | Storage Temperature Range                     | -                    | -65 to +150 | °C   |

| ESD <sub>HBM</sub> | Human Body Model Electro Static Discharge     | -                    | 2500        | V    |

| ESD <sub>MM</sub>  | Machine Model Electro Static Discharge        | -                    | 200         | V    |

| ESD <sub>CDM</sub> | Charged Device Model Electro Static Discharge | -                    | 2000        | V    |

## 100K ECL DC Characteristics ( $V_{EE}$ = -3.0V to -5.5V, $V_{CC}$ = GND)

| Cymhol          | Characteristic                                | -40                      | °C                      | 0°                       | С                       | 25                       | °C                      | 85                       | Unit                    |      |

|-----------------|-----------------------------------------------|--------------------------|-------------------------|--------------------------|-------------------------|--------------------------|-------------------------|--------------------------|-------------------------|------|

| Symbol          | Characteristic                                | Min                      | Max                     | Min                      | Max                     | Min                      | Max                     | Min                      | Max                     | Unit |

| $V_{OH}$        | Output HIGH Voltage <sup>1</sup>              | -1085                    | -880                    | -1025                    | -880                    | -1025                    | -880                    | -1025                    | -880                    | mV   |

| V <sub>OL</sub> | Output LOW Voltage <sup>1</sup>               | -1900                    | -1555                   | -1900                    | -1620                   | -1900                    | -1620                   | -1900                    | -1620                   | mV   |

|                 | Input HIGH Voltage<br>D,EN (ECL) <sup>2</sup> | -1165                    | -740                    | -1165                    | -740                    | -1165                    | -740                    | -1165                    | -740                    | mV   |

| V <sub>IH</sub> | Input HIGH Voltage EN (CMOS) <sup>3</sup>     | V <sub>EE</sub><br>+2000 | $V_{CC}$                | V <sub>EE</sub><br>+2000 | V <sub>CC</sub>         | V <sub>EE</sub><br>+2000 | $V_{CC}$                | V <sub>EE</sub><br>+2000 | V <sub>CC</sub>         | mV   |

|                 | Input LOW Voltage<br>D,EN (ECL) <sup>2</sup>  | -1900                    | -1475                   | -1900                    | -1475                   | -1900                    | -1475                   | -1900                    | -1475                   | mV   |

| V <sub>IL</sub> | Input LOW Voltage EN (CMOS) <sup>3</sup>      | V <sub>EE</sub>          | V <sub>EE</sub><br>+800 | mV   |

| $V_{BB}$        | Reference Voltage                             | -1390                    | -1250                   | -1390                    | -1250                   | -1390                    | -1250                   | -1390                    | -1250                   | mV   |

| I <sub>IH</sub> | Input HIGH Current EN                         |                          | 150                     |                          | 150                     |                          | 150                     |                          | 150                     | μΑ   |

|                 | Input LOW Current EN (ECL) <sup>2</sup>       | 0.5                      |                         | 0.5                      |                         | 0.5                      |                         | 0.5                      |                         | μA   |

| I <sub>IL</sub> | Input LOW Current EN (CMOS) <sup>3</sup>      | -150                     |                         | -150                     |                         | -150                     |                         | -150                     |                         |      |

| I <sub>EE</sub> | Power Supply Current <sup>1</sup>             |                          | 34                      |                          | 34                      |                          | 34                      |                          | 37                      | mA   |

- $^{1}$  Specified with each output terminated through  $50\Omega$  resistors to  $V_{CC}$  -2V.

- $^2$   $\,$  EN-SEL connected to  $V_{\text{EE}}$  through a 20k $\!\Omega$  resistor.

- <sup>3</sup> EN-SEL connected to V<sub>EE</sub> or left open (NC).

# LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs MLP8

## 100K LVPECL DC Characteristics ( $V_{EE}$ = GND, $V_{CC}$ = +3.3V)

| Cumbal          | Characteristic                             |      | -40°C    |      | 0°C      |      | °C       | 85°C |          | Unit |

|-----------------|--------------------------------------------|------|----------|------|----------|------|----------|------|----------|------|

| Symbol          | Characteristic                             | Min  | Max      | Min  | Max      | Min  | Max      | Min  | Max      | Unit |

| $V_{OH}$        | Output HIGH Voltage <sup>1,2</sup>         | 2215 | 2420     | 2275 | 2420     | 2275 | 2420     | 2275 | 2420     | mV   |

| V <sub>OL</sub> | Output LOW Voltage <sup>1,2</sup>          | 1400 | 1745     | 1400 | 1680     | 1400 | 1680     | 1400 | 1680     | mV   |

| V               | Input HIGH Voltage D,EN (ECL) <sup>3</sup> | 2135 | 2560     | 2135 | 2560     | 2135 | 2560     | 2135 | 2560     | mV   |

| $V_{IH}$        | Input HIGH Voltage EN (CMOS) <sup>4</sup>  | 2000 | $V_{CC}$ | 2000 | $V_{CC}$ | 2000 | $V_{CC}$ | 2000 | $V_{CC}$ | mV   |

| \/              | Input LOW Voltage D,EN (ECL) <sup>3</sup>  | 1400 | 1825     | 1400 | 1825     | 1400 | 1825     | 1400 | 1825     | mV   |

| V <sub>IL</sub> | Input LOW Voltage EN (CMOS) <sup>4</sup>   | GND  | 800      | GND  | 800      | GND  | 800      | GND  | 800      | mV   |

| $V_{BB}$        | Reference Voltage <sup>1</sup>             | 1910 | 2050     | 1910 | 2050     | 1910 | 2050     | 1910 | 2050     | mV   |

| I <sub>IH</sub> | Input HIGH Current EN                      |      | 150      |      | 150      |      | 150      |      | 150      | μA   |

|                 | Input LOW Current EN (ECL) <sup>3</sup>    | 0.5  |          | 0.5  |          | 0.5  |          | 0.5  |          | μA   |

| I <sub>IL</sub> | Input LOW Current EN (CMOS)4               | -150 |          | -150 |          | -150 |          | -150 |          |      |

| I <sub>EE</sub> | Power Supply Current <sup>2</sup>          |      | 34       |      | 34       |      | 34       |      | 37       | mA   |

- <sup>1</sup> For supply voltages other than 3.3V, use the ECL table values and ADD supply voltage value.

- Specified with each output terminated through  $50\Omega$  resistors to  $V_{CC}$  -2V.

- <sup>3</sup> EN-SEL connected to  $V_{EE}$  through a 20k $\Omega$  resistor.

- <sup>4</sup> EN-SEL connected to VEE or left open (NC).

## 100K PECL DC Characteristics ( $V_{EE}$ = GND, $V_{CC}$ = +5.0V)

| Symbol          | Symbol Characteristic                      |                        | -40°C    |      | 0°C      |      | ၁        | 85°C |          | Unit  |

|-----------------|--------------------------------------------|------------------------|----------|------|----------|------|----------|------|----------|-------|

| Syllibol        | Cildiacteristic                            | Characteristic Min Max |          | Min  | Max      | Min  | Max      | Min  | Max      | Ullit |

| $V_{OH}$        | Output HIGH Voltage <sup>1,2</sup>         | 3915                   | 4120     | 3975 | 4120     | 3975 | 4120     | 3975 | 4120     | mV    |

| V <sub>OL</sub> | Output LOW Voltage <sup>1,2</sup>          | 3100                   | 3445     | 3100 | 3380     | 3100 | 3380     | 3100 | 3380     | mV    |

| V               | Input HIGH Voltage D,EN (ECL) <sup>3</sup> | 3835                   | 4260     | 3835 | 4260     | 3835 | 4260     | 3835 | 4260     | mV    |

| $V_{IH}$        | Input HIGH Voltage EN (CMOS) <sup>4</sup>  | 2000                   | $V_{CC}$ | 2000 | $V_{CC}$ | 2000 | $V_{CC}$ | 2000 | $V_{CC}$ | mV    |

| \/              | Input LOW Voltage D,EN (ECL) <sup>3</sup>  | 3100                   | 3525     | 3100 | 3525     | 3100 | 3525     | 3100 | 3525     | mV    |

| V <sub>IL</sub> | Input LOW Voltage EN (CMOS) <sup>4</sup>   | GND                    | 800      | GND  | 800      | GND  | 800      | GND  | 800      | mV    |

| $V_{BB}$        | Reference Voltage <sup>1</sup>             | 3610                   | 3750     | 3610 | 3750     | 3610 | 3750     | 3610 | 3750     | mV    |

| I <sub>IH</sub> | Input HIGH Current EN                      |                        | 150      |      | 150      |      | 150      |      | 150      | μΑ    |

|                 | Input LOW Current EN (ECL) <sup>3</sup>    | 0.5                    |          | 0.5  |          | 0.5  |          | 0.5  |          | μΑ    |

| I <sub>IL</sub> | Input LOW Current EN (CMOS) <sup>4</sup>   | -150                   |          | -150 |          | -150 |          | -150 |          |       |

| I <sub>EE</sub> | Power Supply Current <sup>2</sup>          |                        | 34       |      | 34       |      | 34       |      | 37       | mA    |

- <sup>1</sup> For supply voltages other than 3.3V, use the ECL table values and ADD supply voltage value.

- $^2$   $\,$  Specified with each output terminated through  $50\Omega$  resistors to  $V_{\text{CC}}$  -2V.

- $^3$  EN-SEL connected to  $V_{\text{EE}}$  through a  $20k\Omega$  resistor.

- <sup>4</sup> EN-SEL connected to V<sub>EE</sub> or left open (NC).

240

ps

CTSLV394

$t_R/t_F$

## LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs MLP8

| _                                  |                                                           |       | ,   |      |     |      |      |     | ,    |      |     | •       |      |      |

|------------------------------------|-----------------------------------------------------------|-------|-----|------|-----|------|------|-----|------|------|-----|---------|------|------|

| O make all and the second after    |                                                           | -40°C |     | 0°C  |     | 25°C |      |     | 85°C |      |     | I I mid |      |      |

| Symbol                             | Characteristic                                            | Min   | Тур | Max  | Min | Тур  | Max  | Min | Тур  | Max  | Min | Тур     | Max  | Unit |

|                                    | D to Q/Q                                                  |       |     | 450  |     |      | 450  |     |      | 450  |     |         | 450  | ps   |

| t <sub>PLH</sub> /t <sub>PHL</sub> | EN to<br>Q <sub>HG</sub> /Qb <sub>HG</sub> <sup>1,2</sup> |       |     | 3000 |     |      | 3000 |     |      | 3000 |     |         | 3000 | ps   |

| t <sub>SKEW</sub>                  | Duty Cycle<br>Skew <sup>3</sup>                           |       | 5   | 20   |     | 5    | 20   |     | 5    | 20   |     | 5       | 20   | ps   |

| V <sub>PP</sub> (AC)               | Input Swing⁴                                              | 150   |     | 1000 | 150 |      | 1000 | 150 |      | 1000 | 150 |         | 1000 | mV   |

| 4 /4                               | Output Rise/Fall <sup>1</sup>                             | 100   |     | 240  | 100 |      | 240  | 100 |      | 240  | 100 |         | 240  | 20   |

240

100

240

100

AC Characteristics ( $V_{EE} = -3.0V$  to -5.5V;  $V_{CC}$ =GND or  $V_{EE}$ =GND;  $V_{CC} = +3.0V$  to +5.5V)

- <sup>1</sup> Specified with each output terminated through  $50\Omega$  resistors to  $V_{CC}$  -2V.

- Specified from 50% EN input edge to  $V_{OH}$  min to  $V_{OL}$  max of the Q/ $\bar{Q}$  outputs.

240

<sup>3</sup> Duty cycle skew is the difference between a t<sub>PLH</sub> and t<sub>PHL</sub> propagation delay through a device.

100

V<sub>PP</sub> is the peak-to-peak differential input swing for which AC parameters are guaranteed.

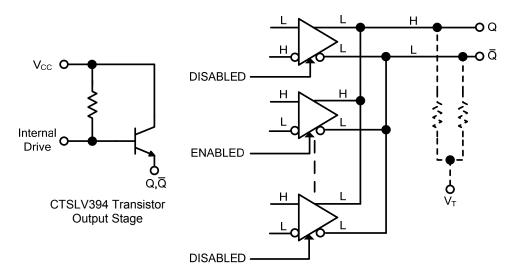

## **Tri-state Compatible Operation**

(20% - 80%)

100

The outputs of the CTSLV394 are emitter followers as shown in the left side of Figure 1. When a part is disabled, both outputs are set in the LOW state. This allows a HIGH output from an enabled part to override a disabled output and pull the combined line HIGH as seen in the right hand side of Figure 1. When the enabled part output is LOW, the combined line remains LOW. If all connected CTS94 parts are disabled, both output lines will be in the LOW state. As another feature, while disabled, the input buffer is powered down to minimize feed through.

**Figure 1: Typical Tri-state Operation**

# LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs MLP8

#### **Divide Truth Table**

| DIV-SEL                      | ÷Ratio |

|------------------------------|--------|

| NC                           | ÷1     |

| V <sub>EE</sub> <sup>1</sup> | ÷2     |

<sup>&</sup>lt;sup>1</sup> DIV-SEL connection must be ≤1W.

#### **Enable Truth Table**

| EN-SEL                 | EN                               | Q    | Q    |

|------------------------|----------------------------------|------|------|

| NC                     | CMOS Low or V <sub>EE</sub>      | Low  | Low  |

| NC                     | CMOS High, V <sub>CC</sub> or NC | Data | Data |

| V                      | CMOS Low, V <sub>EE</sub> or NC  | Low  | Low  |

| $V_{EE}$               | CMOS High or V <sub>CC</sub>     | Data | Data |

| $20$ k $Ω$ to $V_{EE}$ | PECL Low, $V_{EE}$ or NC         | Low  | Low  |

| ZOKZZ IO VEE           | PECL High or V <sub>CC</sub>     | Data | Data |

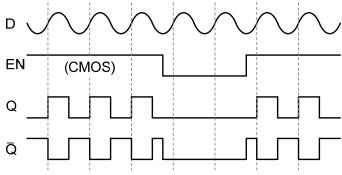

Figure 2 illustrates the timing sequences for the CTSLV394 in the ÷1 mode which is determined by leaving the DIV-SEL open (NC). It also illustrates the enable in the active High mode being controlled by a CMOS signal. This mode is determined by leaving the EN-SEL open (NC).

Figure 2

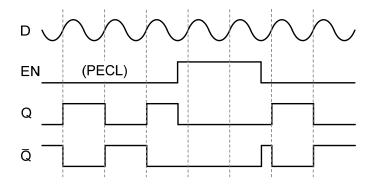

Figure 3 illustrates the timing sequences for the CTSLV394 in the  $\div 2$  mode which is determined by connecting the DIV-SEL to  $V_{EE}$ . It also illustrates the enable in the active Low mode being controlled by a PECL signal. This mode is determined by connecting the EN-SEL to  $V_{EE}$  via  $20k\Omega$  resistor.

Figure 3

CTSLV394

LVPECL Divide by 1, Divide by 2 Clock Generator w/ Tri-State Compatible Outputs

MLP8

Typical Large Signal Output Swing Measured with 750mV D input, Q/ $\bar{Q}$  each terminated to  $V_{CC}$ -2V via 50 $\Omega$  resistors.

## **Pin Description and Configuration**

### **Pin Assignments**

| Pin | Name            | Туре   | Function               |  |  |

|-----|-----------------|--------|------------------------|--|--|

| 1   | EN-SEL          | Input  | Enable Polarity Select |  |  |

| 2   | D               | Input  | Data Input             |  |  |

| 3   | $V_{BB}$        | Input  | Reference Voltage      |  |  |

| 4   | EN              | Input  | Output Enable          |  |  |

| 5   | DIV-SEL         | Input  | Divide Select          |  |  |

| 6   | Q               | Output | Inverted PECL Output   |  |  |

| 7   | Q               | Output | PECL Output            |  |  |

| 8   | V <sub>CC</sub> | Power  | Positive Supply        |  |  |

| 9   | V <sub>EE</sub> | Power  | Negative Supply        |  |  |

### PART ORDERING INFORMATION

| Part Number | Package | Marking   |

|-------------|---------|-----------|

| CTSLV394NG  | MLP8    | J4G / YWW |