# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

#

#### PROGRAMMABLE FLEXPC CLOCK FOR P4 PROCESSOR

#### FEATURES:

- · Power management control suitable for notebook applications

- One high precision PLL for CPU, SSC and N programming

- One high precision PLL for SRC/PCI, supports 100MHz output frequency, SSC and N programming

- One high precision PLL for LVDS. Supports 100/96MHz output frequency, SSC programming

- One high precision PLL for 96MHz/48MHz

- · Band-gap circuit for differential outputs

- Support spread spectrum modulation, –0.5 down spread and others

- · Support SMBus block read/write, index read/write

- · Selectable output strength for REF

- Allows for CPU frequency to change to a slower frequency to conserve power when an application is less executionintensive

- Smooth transition for N programming

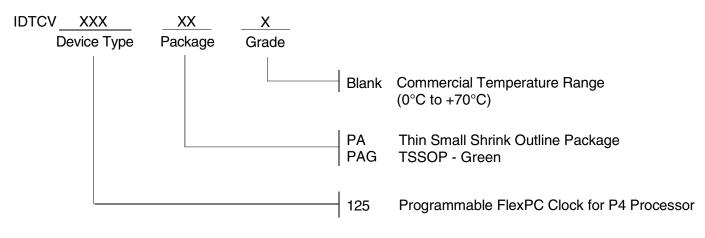

- Available in TSSOP package

#### **KEY SPECIFICATION:**

- CPU/SRC CLK cycle to cycle jitter < 85ps

- PCI CLK cycle to cycle jitter < 250ps

- Static PLL frequency divide error ≤ 114 ppm

- Static PLL frequency divide error for 48MHz ≤ 5 ppm

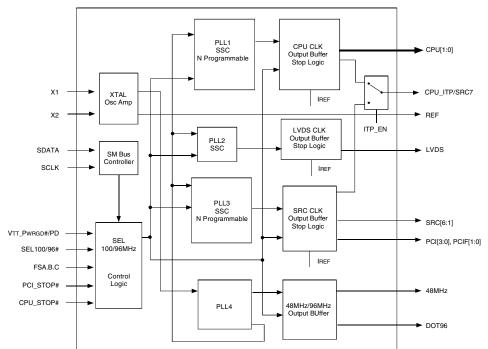

### FUNCTIONAL BLOCK DIAGRAM

### **DESCRIPTION:**

IDTCV125 is a 56 pin clock device, incorporating both Intel CK410M and CKSSCD requirements, for Intel advance P4 processors. The CPU output buffer is designed to support up to 400MHz processor. This chip has four PLLs inside for CPU, SRC/PCI, LVDS, and 48MHz/DOT96 IO clocks. This device also implements Band-gap referenced IREF to reduce the impact of VDD variation on differential outputs, which can provide more robust system performance.

Static PLL frequency divide error can be as low as 36 ppm, worse case 114 ppm, providing high accuracy output clock. Each CPU/SRC/LVDS has its own Spread Spectrum selection.

#### **OUTPUTS**:

- 2\*0.7V current -mode differential CPU CLK pair

- 6\*0.7V current -mode differential SRC CLK pair

- One CPU\_ITP/SRC selectable CLK pair

- 6\*PCI, 2 free running, 33.3MHz

- 1\*96MHz, 1\*48MHz

- 1\*REF

- One 100/96 MHz differential LVDS

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### **DECEMBER 2004**

#### **PIN CONFIGURATION**

| VDD_PCI                         | 1  | 56 | PCI0            |

|---------------------------------|----|----|-----------------|

|                                 | 2  | 55 | PCI_STOP#       |

| PCI1                            | 3  | 54 | CPU_STOP#       |

| PCI2                            | 4  | 53 | FSC/TEST_SEL    |

| PCI3                            | 5  | 52 | REF             |

| Vss_PCI                         | 6  | 51 | Vss_REF         |

|                                 | 7  | 50 | ] XTAL_IN       |

| PCIF0/ITP_EN                    | 8  | 49 | _ XTAL_OUT      |

| <sup>(1)</sup> PCIF1/SEL100/96# | 9  | 48 | VDD_REF         |

| VTT_PWRGD#/PD                   | 10 | 47 | ] SDA           |

| VDD48                           | 11 | 46 | ] SCL           |

| USB48/FSA                       | 12 | 45 | Vss_CPU         |

| Vss48                           | 13 | 44 | CPU0            |

| DOT96                           | 14 | 43 | CPU0#           |

| DOT96# [                        | 15 | 42 | VDD_CPU         |

| FSB/TEST_MODE                   | 16 | 41 | CPU1            |

| <sup>(2)</sup> LVDS             | 17 | 40 | CPU1#           |

| <sup>(2)</sup> LVDS#            | 18 | 39 | IREF            |

| SRC1                            | 19 | 38 | VSSA            |

| SRC1#                           | 20 | 37 | VDDA            |

|                                 | 21 | 36 | CPU2_ITP/SRC7   |

| SRC2                            | 22 | 35 | CPU2_ITP#/SRC7# |

| SRC2#                           | 23 | 34 | VDD_SRC         |

| SRC3                            | 24 | 33 | SRC6            |

| SRC3#                           | 25 | 32 | SRC6#           |

| SRC4                            | 26 | 31 | SRC5            |

| SRC4#                           | 27 | 30 | SRC5#           |

|                                 | 28 | 29 | Vss_SRC         |

|                                 |    |    | I               |

#### NOTES:

Can be configured as 100MHz or 96MHz output clock, depending on pin9 power on pull-up (100MHz) or pull-down (96MHz) latch. If using internal pull-up resistor, power on would be 100MHz.

#### TSSOP TOP VIEW

#### FREQUENCY SELECTION TABLE

| FSC, B, A | CPU     | SRC[7:0] | PCI  | USB | DOT | REF    |

|-----------|---------|----------|------|-----|-----|--------|

| 101       | 100     | 100      | 33.3 | 48  | 96  | 14.318 |

| 001       | 133     | 100      | 33.3 | 48  | 96  | 14.318 |

| 011       | 166     | 100      | 33.3 | 48  | 96  | 14.318 |

| 010       | 200     | 100      | 33.3 | 48  | 96  | 14.318 |

| 000       | 266     | 100      | 33.3 | 48  | 96  | 14.318 |

| 100       | 333     | 100      | 33.3 | 48  | 96  | 14.318 |

| 110       | 400     | 100      | 33.3 | 48  | 96  | 14.318 |

| 111       | Reserve | 100      | 33.3 | 48  | 96  | 14.318 |

#### COMMERCIALTEMPERATURERANGE

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol   | Description                     | Min       | Max  | Unit |

|----------|---------------------------------|-----------|------|------|

| Vdda     | 3.3V Core Supply Voltage        |           | 4.6  | V    |

| VDDIN    | 3.3V Logic Input Supply Voltage | GND - 0.5 | 4.6  | V    |

| Tstg     | Storage Temperature             | -65       | +150 | °C   |

| TAMBIENT | Ambient Operating Temperature   | 0         | +70  | °C   |

| TCASE    | Case Temperature                |           | +115 | °C   |

| ESD Prot | Input ESD Protection            | 2000      |      | V    |

|          | Human Body Model                |           |      |      |

#### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>1. 130</sup>K internal pull-up resistor.

#### **PIN DESCRIPTION**

| Pin Number | Name             | Туре | Description                                                                                                                                                                                                                |

|------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | Vdd_PCI          | PWR  | 3.3V                                                                                                                                                                                                                       |

| 2          | Vss_PCI          | GND  | GND                                                                                                                                                                                                                        |

| 3          | PCI1             | OUT  | PCI clock                                                                                                                                                                                                                  |

| 4          | PCI2             | OUT  | PCI clock                                                                                                                                                                                                                  |

| 5          | PCI3             | OUT  | PCI clock                                                                                                                                                                                                                  |

| 6          | Vss_PCI          | GND  | GND                                                                                                                                                                                                                        |

| 7          | VDD_PCI          | PWR  | 3.3V                                                                                                                                                                                                                       |

| 8          | PCIF0/ITP_EN     | I/O  | PCI clock, free running. CPU2 select (sampled on VTT_Pwred# assertion) HIGH = CPU2.                                                                                                                                        |

| 9          | PCIF1/SEL100/96# | I/O  | PCI clock, free running. SEL100/96MHz (sampled on $VTT_PwRGD#$ assertion) HIGH, LVDS = 100MHz.                                                                                                                             |

| 10         | Vtt_Pwrgd#/PD    | IN   | Level-sensitive strobe used to latch the FSA, FSB, FSC/TEST_SEL, and PCIF0/ITP_EN inputs. After $V\pi$ _PwRGD# assertion, becomes a real-time input for asserting power down. (Active HIGH). Latch PCIF1/SEL100/96# input. |

| 11         | Vdd48            | PWR  | 3.3V                                                                                                                                                                                                                       |

| 12         | USB48/FSA        | I/O  | 48MHz clock/FSA for CPU frequency selection                                                                                                                                                                                |

| 13         | Vss48            | GND  | GND                                                                                                                                                                                                                        |

| 14         | DOT96            | OUT  | 96MHz 0.7 current mode differential clock output                                                                                                                                                                           |

| 15         | DOT96#           | OUT  | 96MHz 0.7 current mode differential clock output                                                                                                                                                                           |

| 16         | FSB/TEST_MODE    | IN   | CPU frequency selection. Selects REF/N or Hi-Z when in test mode, Hi-Z = 1, REF/N = 0.                                                                                                                                     |

| 17         | LVDS             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 18         | LVDS#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 19         | SRC1             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 20         | SRC1#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 21         | VDD_SRC          | PWR  | 3.3V                                                                                                                                                                                                                       |

| 22         | SRC2             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 23         | SRC2#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 24         | SRC3             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 25         | SRC3#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 26         | SRC4             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 27         | SRC4#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 28         | VDD_SRC          | PWR  | 3.3V                                                                                                                                                                                                                       |

| 29         | Vss_SRC          | GND  | GND                                                                                                                                                                                                                        |

| 30         | SRC5#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 31         | SRC5             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 32         | SRC6#            | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 33         | SRC6             | OUT  | Differential serial reference clock                                                                                                                                                                                        |

| 34         | VDD_SRC          | PWR  | 3.3V                                                                                                                                                                                                                       |

| 35         | CPU2_ITP#/SRC7#  | OUT  | Selectable CPU or SRC differential clock output. ITP_EN = 0 at VTT_PwRGD# assertion = SRC7#.                                                                                                                               |

| 36         | CPU2_ITP/SRC7    | OUT  | Selectable CPU or SRC differential clock output. ITP_EN = 0 at $VTT_Pwrgd \#$ assertion = SRC7.                                                                                                                            |

| 37         | Vdda             | PWR  | 3.3V                                                                                                                                                                                                                       |

| 38         | Vssa             | GND  | GND                                                                                                                                                                                                                        |

| 39         | IREF             | OUT  | Reference current for differential output buffer                                                                                                                                                                           |

| 40         | CPU1#            | OUT  | Host 0.7 current mode differential clock output                                                                                                                                                                            |

| 41         | CPU1             | OUT  | Host 0.7 current mode differential clock output                                                                                                                                                                            |

| 42         | VDD_CPU          | PWR  | 3.3V                                                                                                                                                                                                                       |

#### **PIN DESCRIPTION (CONT.)**

| Pin Number | Name         | Туре | Description                                                                                    |

|------------|--------------|------|------------------------------------------------------------------------------------------------|

| 43         | CPU0#        | OUT  | Host 0.7 current mode differential clock output                                                |

| 44         | CPU0         | OUT  | Host 0.7 current mode differential clock output                                                |

| 45         | Vss_CPU      | GND  | GND                                                                                            |

| 46         | SCL          | IN   | SM bus clock                                                                                   |

| 47         | SDA          | I/O  | SM bus data                                                                                    |

| 48         | VDD_REF      | PWR  | 3.3V                                                                                           |

| 49         | XTAL_OUT     | OUT  | XTALoutput                                                                                     |

| 50         | XTAL_IN      | IN   | XTALinput                                                                                      |

| 51         | Vss_REF      | GND  | GND                                                                                            |

| 52         | REF          | OUT  | 14.318 MHz reference clock output                                                              |

| 53         | FSC/TEST_SEL | IN   | CPU frequency selection. Selects test mode if pulled above 2V when VTT_PwRGD# is asserted LOW. |

| 54         | CPU_STOP#    | IN   | Stop all stoppable CPU CLK                                                                     |

| 55         | PCI_STOP#    | IN   | Stop all stoppable PCI, SRC CLK                                                                |

| 56         | PCI0         | OUT  | PCI clock                                                                                      |

### INDEX BLOCK WRITE PROTOCOL

| Bit   | # of bits | From   | Description                          |

|-------|-----------|--------|--------------------------------------|

| 1     | 1         | Master | Start                                |

| 2-9   | 8         | Master | D2h                                  |

| 10    | 1         | Slave  | Ack (Acknowledge)                    |

| 11-18 | 8         | Master | Register offset byte (starting byte) |

| 19    | 1         | Slave  | Ack (Acknowledge)                    |

| 20-27 | 8         | Master | Byte count, N (0 is not valid)       |

| 28    | 1         | Slave  | Ack (Acknowledge)                    |

| 29-36 | 8         | Master | first data byte (Offset data byte)   |

| 37    | 1         | Slave  | Ack (Acknowledge)                    |

| 38-45 | 8         | Master | 2nd data byte                        |

| 46    | 1         | Slave  | Ack (Acknowledge)                    |

|       |           |        | :                                    |

|       |           | Master | Nth data byte                        |

|       |           | Slave  | Acknowledge                          |

|       |           | Master | Stop                                 |

### INDEX BLOCK READ PROTOCOL

Master can stop reading any time by issuing the stop bit without waiting until Nth byte (byte count bit30-37).

| Bit   | # of bits | From   | Description                                               |

|-------|-----------|--------|-----------------------------------------------------------|

| 1     | 1         | Master | Start                                                     |

| 2-9   | 8         | Master | D2h                                                       |

| 10    | 1         | Slave  | Ack (Acknowledge)                                         |

| 11-18 | 8         | Master | Register offset byte (starting byte)                      |

| 19    | 1         | Slave  | Ack (Acknowledge)                                         |

| 20    | 1         | Master | Repeated Start                                            |

| 21-28 | 8         | Master | D3h                                                       |

| 29    | 1         | Slave  | Ack (Acknowledge)                                         |

| 30-37 | 8         | Slave  | Byte count, N (block read back of N bytes), power on is 8 |

| 38    | 1         | Master | Ack (Acknowledge)                                         |

| 39-46 | 8         | Slave  | first data byte (Offset data byte)                        |

| 47    | 1         | Master | Ack (Acknowledge)                                         |

| 48-55 | 8         | Slave  | 2nd data byte                                             |

|       |           |        | Ack (Acknowledge)                                         |

|       |           |        | :                                                         |

|       |           | Master | Ack (Acknowledge)                                         |

|       |           | Slave  | Nth data byte                                             |

|       |           |        | Notacknowledge                                            |

|       |           | Master | Stop                                                      |

#### INDEX BYTE WRITE

Setting bit[11:18] = starting address, bit[20:27] = 01h.

#### **INDEX BYTE READ**

Setting bit[11:18] = starting address. After reading back the first data byte, master issues Stop bit.

#### COMMERCIALTEMPERATURERANGE

# SSC MAGNITUDE CONTROL FOR CPU, SRC, AND SMC

| SMC[2:0] |        |

|----------|--------|

| 000      | -0.25  |

| 001      | -0.5   |

| 010      | -0.75  |

| 011      | -1     |

| 100      | ±0.125 |

| 101      | ±0.25  |

| 110      | ±0.375 |

| 111      | ±0.5   |

#### RESOLUTION

| CPU (MHz) | Resolution | N = |

|-----------|------------|-----|

| 100       | 0.666667   | 150 |

| 133       | 0.666667   | 200 |

| 166       | 1.333333   | 125 |

| 200       | 1.333333   | 150 |

| 266       | 1.333333   | 200 |

| 333       | 2.666667   | 125 |

| 400       | 2.666667   | 150 |

### SEL 100/96# CONFIGURATION

| SEL 100/96# | LVDS Frequency | Unit |

|-------------|----------------|------|

| 0           | 96             | MHz  |

| 1           | 100            | MHz  |

# S.E. CLOCK STRENGTH SELECTION (PCI, REF, USB48)

| Str[1:0] | Level |

|----------|-------|

| 00       | 1     |

| 01       | 0.8   |

| 10       | 0.6   |

| 11       | 1.2   |

# SPREAD SPECTRUM CONTROL SELECTION (SSC) FOR LVDS

| S[3:0] | Spread |

|--------|--------|

| 0000   | -0.8%  |

| 0001   | -1%    |

| 0010   | -1.25% |

| 0011   | -1.5%  |

| 0100   | -1.75% |

| 0101   | -2%    |

| 0110   | -0.3%  |

| 0111   | -0.5%  |

| 1000   | ±0.3%  |

| 1001   | ±0.4%  |

| 1010   | ±0.5%  |

| 1011   | ±0.6%  |

| 1100   | ±0.8%  |

| 1101   | ±1%    |

| 1110   | ±1.25% |

| 1111   | ±1.5%  |

#### **CONTROL REGISTERS**

#### N PROGRAMMING PROCEDURE

- Use Index byte write.

- For N programming, the user only needs to access Byte 11, Byte 12, and Byte 9.

- 1. Write Byte 11 for CPU PLL N, CPU  $f = N^*$  Resolution (see resolution table).

- 2. Write Byte 12 for SRC PLL N, SRC f = N\*0.6666667, PCI = SRC f/3.

- 3. Enable N Programming bit, Byte 9 bit 1. Once this bit is enabled, any N value will be changed on the fly.

#### **BYTE0**

| Bit | Output(s) Affected | Description/Function | 0        | 1      | Туре | Power On |

|-----|--------------------|----------------------|----------|--------|------|----------|

| 0   | Reserved           |                      |          |        |      |          |

| 1   | SRC1, SRC1#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 2   | SRC2, SRC2#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 3   | SRC3, SRC3#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 4   | SRC4, SRC4#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 5   | SRC5, SRC5#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 6   | SRC6, SRC6#        | Output Enable        | Tristate | Enable | RW   | 1        |

| 7   | CPU2, CPU2#/       | Output Enable        | Tristate | Enable | RW   | 1        |

|     | SRC7, SRC7#        |                      |          |        |      |          |

#### **BYTE1**

| Bit | Output(s) Affected  | Description/Function        | 0          | 1        | Туре | Power On |

|-----|---------------------|-----------------------------|------------|----------|------|----------|

| 0   | CPU[2:0], SRC[7:1], | Spread Spectrum mode enable | Spread off | Spreadon | RW   | 0        |

|     | PCI[5:0], PCIF[1:0] |                             |            |          |      |          |

| 1   | CPU0, CPU0#         | Output Enable               | Tristate   | Enable   | RW   | 1        |

| 2   | CPU1, CPU1#         | Output Enable               | Tristate   | Enable   | RW   | 1        |

| 3   | Reserved            |                             |            |          | RW   | 0        |

| 4   | REF                 | Output Enable               | Tristate   | Enable   | RW   | 1        |

| 5   | USB48               | Output Enable               | Tristate   | Enable   | RW   | 1        |

| 6   | DOT96               | Output Enable               | Tristate   | Enable   | RW   | 1        |

| 7   | PCIF0               | Output Enable               | Tristate   | Enable   | RW   | 1        |

#### **BYTE2**

| Bit | Output(s) Affected | Description/Function | 0        | 1      | Туре | Power On |

|-----|--------------------|----------------------|----------|--------|------|----------|

| 0   | PCIF1              | Output Enable        | Tristate | Enable | RW   | 1        |

| 1   | Reserved           |                      |          |        | RW   | 1        |

| 2   | PCI0               | Output Enable        | Tristate | Enable | RW   | 1        |

| 3   | PCI1               | Output Enable        | Tristate | Enable | RW   | 1        |

| 4   | PCI2               | Output Enable        | Tristate | Enable | RW   | 1        |

| 5   | PCI3               | Output Enable        | Tristate | Enable | RW   | 1        |

| 6   | Reserved           |                      |          |        | RW   | 1        |

| 7   | Reserved           |                      |          |        | RW   | 1        |

| Bit | Output(s) Affected | <b>Description / Function</b> | 0                     | 1            | Туре | Power On |

|-----|--------------------|-------------------------------|-----------------------|--------------|------|----------|

| 0   | Reserved           |                               |                       |              | RW   | 0        |

| 1   | SRC1               |                               |                       |              | RW   | 0        |

| 2   | SRC2               |                               |                       |              | RW   | 0        |

| 3   | SRC3               | Allow controlled by           | Free running, not     | Stopped with | RW   | 0        |

| 4   | SRC4               | PCI_STOP# assertion           | affected by PCI_STOP# | PCI_STOP#    | RW   | 0        |

| 5   | SRC5               |                               |                       |              | RW   | 0        |

| 6   | SRC6               |                               |                       |              | RW   | 0        |

| 7   | SRC7               |                               |                       |              | RW   | 0        |

#### **BYTE4**

| Bit | Output(s) Affected | Description / Function                               | 0                          | 1                         | Туре | Power On |

|-----|--------------------|------------------------------------------------------|----------------------------|---------------------------|------|----------|

| 0   | CPU0, CPU0#        | Allow control of CPU0<br>with assertion of CPU_STOP# | Notstopped<br>by CPU_STOP# | Stopped with<br>CPU_STOP# | RW   | 1        |

| 1   | CPU1, CPU1#        | Allow control of CPU1<br>with assertion of CPU_STOP# | Notstopped<br>by CPU_STOP# | Stopped with<br>CPU_STOP# | RW   | 1        |

| 2   | CPU2, CPU2#        | Allow control of CPU2<br>with assertion of CPU_STOP# | Notstopped<br>by CPU_STOP# | Stopped with<br>CPU_STOP# | RW   | 1        |

| 3   | PCIF0              | Allow controlled by                                  | Not stopped                | Stopped with              | RW   | 0        |

| 4   | PCIF1              | PCI_STOP# assertion                                  | by PCI_STOP#               | PCI_STOP#                 | RW   | 0        |

| 5   | Reserved           |                                                      |                            |                           | RW   | 0        |

| 6   | DOT96              | DOT96 power down drive mode                          | Driven in power down       | Tristate                  | RW   | 0        |

| 7   | Reserved           |                                                      |                            |                           | RW   | 0        |

#### **BYTE5**

| Bit | Output(s) Affected  | Description / Function   | 0                    | 1                      | Туре | Power On |

|-----|---------------------|--------------------------|----------------------|------------------------|------|----------|

| 0   | CPU0, CPU0#         | CPU0 PD drive mode       | Driven in power down | Tristate in power down | RW   | 0        |

| 1   | CPU1, CPU1#         | CPU1 PD drive mode       | Driven in power down | Tristate in power down | RW   | 0        |

| 2   | CPU2, CPU2#         | CPU2 PD drive mode       | Driven in power down | Tristate in power down | RW   | 0        |

| 3   | SRC[7:1], SRC[7:1]# | SRC PD drive mode        | Driven in power down | Tristate in power down | RW   | 0        |

| 4   | CPU0, CPU0#         | CPU0 CPU_STOP drive mode | Driven in CPU_STOP#  | Tristate when stopped  | RW   | 0        |

| 5   | CPU1, CPU1#         | CPU1 CPU_STOP drive mode | Driven in CPU_STOP#  | Tristate when stopped  | RW   | 0        |

| 6   | CPU2, CPU2#         | CPU2 CPU_STOP drive mode | Driven in CPU_STOP#  | Tristate when stopped  | RW   | 0        |

| 7   | SRC[7:1], SRC[7:1]# | SRC PCI_STOP drive mode  | Driven in PCI_STOP   | Tristate when stopped  | RW   | 0        |

| Bit | Output(s)Affected                           | Description / Function                           | 0                                                                   | 1                                        | Туре | Power On |

|-----|---------------------------------------------|--------------------------------------------------|---------------------------------------------------------------------|------------------------------------------|------|----------|

| 0   | CPU[2:0]                                    | FSA latched value on power up                    |                                                                     |                                          | R    |          |

| 1   | CPU[2:0]                                    | FSB latched value on power up                    |                                                                     |                                          | R    |          |

| 2   | CPU[2:0]                                    | FSC latched value on power up                    |                                                                     |                                          | R    |          |

| 3   | PCI, SRC                                    | Software PCI_STOP control for<br>PCI and SRC CLK | Stop all PCI, PCIF, and<br>SRC which can be stopped<br>by PCI_STOP# | Software STOP<br>Disabled                | RW   | 1        |

| 4   | REF                                         | <b>REF</b> drive strength                        | 1x drive                                                            | 2x drive                                 | RW   | 1        |

| 5   | Reserved                                    |                                                  |                                                                     |                                          | RW   | 0        |

| 6   |                                             | Test clock mode entry control                    | Normal operation                                                    | Testmode, controlled<br>by Byte 6, Bit 7 | RW   | 0        |

| 7   | CPU, SRC, PCI<br>PCIF, REF,<br>USB48, DOT96 | Only valid when Byte 6, Bit 6<br>is HIGH         | Hi-Z                                                                | REF/N                                    | RW   | 0        |

#### **BYTE7**

| Bit | Output(s) Affected | <b>Description / Function</b> | 0 | 1 | Туре | Power On |

|-----|--------------------|-------------------------------|---|---|------|----------|

| 0   |                    | Vendor ID                     |   |   | R    | 1        |

| 1   |                    | Vendor ID                     |   |   | R    | 0        |

| 2   |                    | Vendor ID                     |   |   | R    | 1        |

| 3   |                    | Vendor ID                     |   |   | R    | 0        |

| 4   |                    | Revision ID                   |   |   | R    | 0        |

| 5   |                    | Revision ID                   |   |   | R    | 0        |

| 6   |                    | Revision ID                   |   |   | R    | 0        |

| 7   |                    | Revision ID                   |   |   | R    | 0        |

### **BYTE 8, LVDS CONTROL BYTE**

| Bit | Output(s) Affected | Description/Function   | 0                 | 1      | Туре | Power On    |

|-----|--------------------|------------------------|-------------------|--------|------|-------------|

| 0   | LVDS               | HW/ SMBus control      | HW <sup>(1)</sup> | SW     | RW   | 0           |

| 1   | LVDS SSC EN        | Spread spectrum enable | Off               | On     | RW   | 1           |

| 2   | LVDS Enable        | Output Enable          | Disable           | Enable | RW   | 1           |

| 3   | SEL 100/96#        | Select LVDS frequency  | 96MHz             | 100MHZ | RW   | SEL 100/96# |

| 4   | S3                 | see SSC table          |                   |        | RW   | 0           |

| 5   | S2                 | see SSC table          |                   |        | RW   | 0           |

| 6   | S1                 | see SSC table          |                   |        | RW   | 0           |

| 7   | S0                 | see SSC table          |                   |        | RW   | 0           |

NOTE:

1. If bit 0 is set to 0, LVDS output frequency is selected by HW SEL 100/96#. If bit 0 is set to 1, LVDS output frequency is selected by bit 3.

| Bit | Output(s) Affected    | Description / Function          | 0       | 1          | Туре | Power On |

|-----|-----------------------|---------------------------------|---------|------------|------|----------|

| 0   | One cycle read        |                                 | disable | enable     | RW   | 0        |

| 1   |                       | N Programming enable            | Disable | enable     | RW   | 0        |

| 2   |                       | LVDS PLL power down             | normal  | Power down | RW   | 0        |

| 3   |                       |                                 |         |            | RW   | 0        |

| 4   |                       | USB PLL power down              | normal  | Power down | RW   | 0        |

| 5   |                       | SRC PLL power down              | normal  | Power down | RW   | 0        |

| 6   |                       | CPU PLL power down              | normal  | Power down | RW   | 0        |

| 7   | SRC, PLL2, SSC enable | Only valid when Byte1 bit0 is 1 | disable | enable     | RW   | 1        |

#### BYTE10

| Bit | Output(s) Affected | Description / Function | 0 | 1 | Туре | Power On |

|-----|--------------------|------------------------|---|---|------|----------|

| 0   | SRC SMC0           | SRC/PCI SSC control    |   |   | RW   | 1        |

| 1   | SRC SMC1           | see SMC table          |   |   | RW   | 0        |

| 2   | SRC SMC2           |                        |   |   | RW   | 0        |

| 3   | Reserved           |                        |   |   | RW   | 0        |

| 4   | CPU SMC0           | CPU PLL SSC control    |   |   | RW   | 1        |

| 5   | CPU SMC1           | see SMC table          |   |   | RW   | 0        |

| 6   | CPU SMC2           |                        |   |   | RW   | 0        |

| 7   | Reserved           |                        |   |   | RW   | 0        |

### BYTE11

| Bit | Output(s)Affected | Description / Function  | 0 | 1 | Туре | Power On |

|-----|-------------------|-------------------------|---|---|------|----------|

| 0   | CPU_N0, LSB       | CPU CLK = N* Resolution |   |   | RW   | 0        |

| 1   | CPU_N1            | see Resolution table    |   |   | RW   | 1        |

| 2   | CPU_N2            |                         |   |   | RW   | 1        |

| 3   | CPU_N3            |                         |   |   | RW   | 0        |

| 4   | CPU_N4            |                         |   |   | RW   | 1        |

| 5   | CPU_N5            |                         |   |   | RW   | 0        |

| 6   | CPU_N6            |                         |   |   | RW   | 0        |

| 7   | CPU_N7, MSB       |                         |   |   | RW   | 1        |

### BYTE12

| Bit | Output(s) Affected | Description / Function   | 0 | 1 | Туре | Power On |

|-----|--------------------|--------------------------|---|---|------|----------|

| 0   | SRC_N0, LSB        |                          |   |   | RW   | 0        |

| 1   | SRC_N1             |                          |   |   | RW   | 1        |

| 2   | SRC_N2             | SRC f = N*SRC Resolution |   |   | RW   | 1        |

| 3   | SRC_N3             | Resolution = 0.666667    |   |   | RW   | 0        |

| 4   | SRC_N4             | 100MHz N= 150            |   |   | RW   | 1        |

| 5   | SRC_N5             |                          |   |   | RW   | 0        |

| 6   | SRC_N6             |                          |   |   | RW   | 0        |

| 7   | SRC_N7, MSB        |                          |   |   | RW   | 1        |

| Bit | Output(s) Affected | Description / Function       | 0 | 1 | Туре | Power On |

|-----|--------------------|------------------------------|---|---|------|----------|

| 0   | 48MHzStr0          |                              |   |   | RW   | 0        |

| 1   | 48MHStr1           | USB48MHz0 strength selection |   |   | RW   | 0        |

| 2   | REFStr0            |                              |   |   | RW   | 0        |

| 3   | REFStr1            | REF strength selection       |   |   | RW   | 0        |

| 4   | PCIStrC0           |                              |   |   | RW   | 0        |

| 5   | PCIStrC1           | PCI strength selection       |   |   | RW   | 0        |

| 6   | PCIFStr0           |                              |   |   | RW   | 0        |

| 7   | PCIFStr1           | PCIF strength selection      |   |   | RW   | 0        |

# ELECTRICAL CHARACTERISTICS - INPUT / SUPPLY / COMMON OUTPUT PARAMETERS

Following Conditions Apply Unless Otherwise Specified: Operating Condition: TA =  $0^{\circ}$ C to +70°C, Supply Voltage: VDD =  $3.3V \pm 5\%$

| Symbol   | Parameter                                             | Test Conditions                                        | Min.      | Тур.     | Max.      | Unit |

|----------|-------------------------------------------------------|--------------------------------------------------------|-----------|----------|-----------|------|

| VIH      | Input HIGH Voltage                                    | 3.3V ± 5%                                              | 2         | —        | Vdd + 0.3 | ۷    |

| VIL      | Input LOW Voltage                                     | 3.3V ± 5%                                              | Vss - 0.3 | —        | 0.8       | ۷    |

| VIH_FS   | LOW Voltage, HIGH Threshold                           | For FSA.B.C test_mode                                  | 0.7       | _        | VDD + 0.3 | V    |

| VIL_FS   | LOW Voltage, LOW Threshold                            | For FSA.B.C test_mode                                  | Vss - 0.3 | _        | 0.35      | V    |

| Ін       | Input HIGH Current                                    | VIN = VDD                                              | -5        | _        | 5         | μA   |

| liL1     | Input LOW Current                                     | VIN = 0V, inputs with no pull-up resistors             | -5        | _        | _         | μA   |

| IIL2     | Input LOW Current                                     | VIN = 0V, inputs with pull-up resistors                | -200      | _        | —         | μA   |

| IDD3.30P | Operating Supply Current                              | Full active, CL = full load                            | _         | _        | 400       | mA   |

| IDD3.3PD | Powerdown Current                                     | All differential pairs driven                          | _         | _        | 70        | mA   |

|          |                                                       | All differential pairs tri-stated                      | —         | —        | 12        | 1    |

| Fi       | Input Frequency <sup>(1)</sup>                        | VDD = 3.3V                                             | —         | 14.31818 | —         | MHz  |

| LPIN     | Pin Inductance <sup>(2)</sup>                         |                                                        | _         | —        | 7         | nH   |

| CIN      |                                                       | Logic inputs                                           | _         | _        | 5         |      |

| Соит     | Input Capacitance <sup>(2)</sup>                      | Output pin capacitance                                 | —         | —        | 6         | pF   |

| CINX     |                                                       | XTAL_IN                                                | —         | —        | 5         |      |

| Соитх    |                                                       | XTAL_OUT                                               | —         | —        | 12        | 1    |

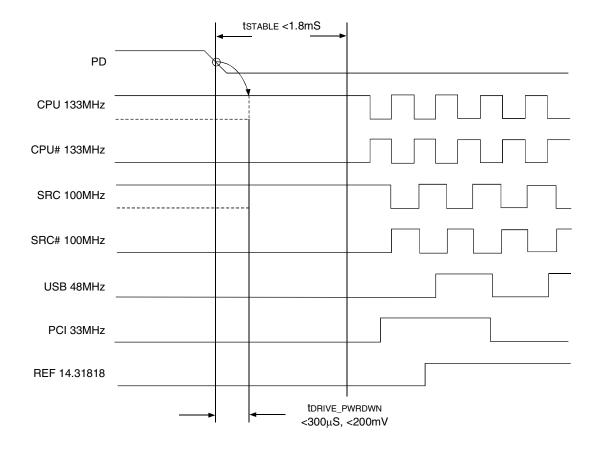

| TSTAB    | Clock Stabilization <sup>(2,3)</sup>                  | From VDD power-up or de-assertion of PD to first clock | -         | —        | 1.8       | ms   |

|          | Modulation Frequency <sup>(2)</sup>                   | Triangular modulation                                  | 30        | —        | 33        | KHz  |

|          | TDRIVE_SRC <sup>(2)</sup>                             | SRC output enable after PCI_STOP# de-assertion         | _         | _        | 15        | ns   |

|          | TDRIVE_PD <sup>(2)</sup>                              | CPU output enable after PD de-assertion                | _         | _        | 300       | US   |

|          | TFALL_PD <sup>(2)</sup>                               | Fall time of PD                                        | _         | _        | 5         | ns   |

|          | Trise_PD <sup>(3)</sup>                               | Rise time of PD                                        | _         | _        | 5         | ns   |

|          | TDRIVE_CPU_STOP# <sup>(2)</sup>                       | CPU output enable after CPU_STOP# de-assertion         | _         | —        | 10        | us   |

|          | TFALL_CPU_STOP# <sup>(2)</sup> Fall time of CPU_STOP# |                                                        | _         | —        | 5         | ns   |

|          | TRISE_CPU_STOP# <sup>(3)</sup>                        | Rise time of CPU_STOP#                                 | _         | _        | 5         | ns   |

#### NOTES:

1. Input frequency should be measured at the REF output pin and tuned to ideal 14.31818MHz to meet ppm frequency accuracy on PLL outputs.

2. This parameter is guaranteed by design, but not 100% production tested.

3. See TIMING DIAGRAMS for timing requirements.

# ELECTRICAL CHARACTERISTICS - CPU, SRC, AND DOT96 0.7 CURRENT MODE DIFFERENTIAL PAIR<sup>(1)</sup>

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, Supply Voltage: VDD = 3.3V ± 5%; CL = 2pF

| Symbol     | Parameter                                      | Test Conditions                                         | Min.    | Тур. | Max.    | Unit |

|------------|------------------------------------------------|---------------------------------------------------------|---------|------|---------|------|

| Zo         | Current Source Output Impedance <sup>(2)</sup> | Vo = Vx                                                 | 3000    | _    | _       | Ω    |

| Vонз       | Output HIGH Voltage                            | Iон = -1mA                                              | 2.4     | _    | _       | V    |

| Vol3       | Output LOW Voltage                             | IoL = 1mA                                               | _       | _    | 0.4     | V    |

| Vhigh      | Voltage HIGH <sup>(2)</sup>                    | Statistical measurement on single-ended signal using    | 660     | _    | 1150    | mV   |

| VLOW       | Voltage LOW <sup>(2)</sup>                     | oscilloscope math function                              | -300    | _    | 150     |      |

| Vovs       | Max Voltage <sup>(2)</sup>                     | Measurement on single-ended signal using absolute value | _       | _    | 1150    | mV   |

| VUDS       | Min Voltage <sup>(2)</sup>                     |                                                         | -300    | _    | _       |      |

| CROSS(ABS) | Crossing Voltage (abs) <sup>(2)</sup>          |                                                         | 250     | _    | 550     | mV   |

| d - Vcross | Crossing Voltage (var) <sup>(2)</sup>          | Variation of crossing over all edges                    | _       | _    | 140     | mV   |

| ppm        | Long Accuracy <sup>(2,3)</sup>                 | See TPERIOD Min Max. values                             | -300    | _    | 300     | ppm  |

|            | <u> </u>                                       | 400MHz nominal / -0.5% spread                           | 2.4993  | _    | 2.5133  |      |

|            |                                                | 333.33MHz nominal / -0.5% spread                        | 2.9991  | _    | 3.016   |      |

|            |                                                | 266.66MHz nominal / -0.5% spread                        | 3.7489  | —    | 3.77    |      |

| TPERIOD    | Average Period <sup>(3)</sup>                  | 200MHz nominal / -0.5% spread                           | 4.9985  | _    | 5.0266  | ns   |

|            |                                                | 166.66MHz nominal / -0.5% spread                        | 5.9982  | _    | 6.032   |      |

|            |                                                | 133.33MHz nominal / -0.5% spread                        | 7.4978  | _    | 7.54    | ,    |

|            |                                                | 100MHz nominal / -0.5% spread                           | 9.997   | _    | 10.0533 |      |

|            |                                                | 96MHz nominal                                           | 10.4135 | _    | 10.4198 |      |

|            |                                                | 400MHz nominal / -0.5% spread                           | 2.4143  | _    | _       |      |

|            |                                                | 333.33MHz nominal / -0.5% spread                        | 2.9141  | —    | —       |      |

|            |                                                | 266.66MHz nominal / -0.5% spread                        | 3.6639  | —    | —       | ,    |

|            |                                                | 200MHz nominal / -0.5% spread                           | 4.9135  | —    | —       |      |

| TABSMIN    | Absolute Min Period <sup>(2,3)</sup>           | 166.66MHz nominal / -0.5% spread                        | 5.9132  | _    | —       | ns   |

|            |                                                | 133.33MHz nominal / -0.5% spread                        | 7.4128  | —    | —       |      |

|            |                                                | 100MHz nominal / -0.5% spread                           | 9.912   | —    | —       |      |

|            |                                                | 96MHz nominal                                           | 10.1635 | —    | —       |      |

| <b>t</b> R | Rise Time <sup>(2)</sup>                       | Vol = 0.175V, Voн = 0.525V                              | 175     | —    | 700     | ps   |

| tr         | Fall Time <sup>(2)</sup>                       | Vol = 0.175V, Voн = 0.525V                              | 175     | _    | 700     | ps   |

| d-tr       | Rise Time Variation <sup>(2)</sup>             |                                                         | _       | _    | 125     | ps   |

| d-t⊧       | Fall Time Variation <sup>(2)</sup>             |                                                         | _       | _    | 125     | ps   |

| dтз        | Duty Cycle <sup>(2)</sup>                      | Measurement from differential waveform                  | 45      | _    | 55      | %    |

#### NOTES:

1. SRC clock outputs run only at 100MHz.

2. This parameter is guaranteed by design, but not 100% production tested.

3. All long term accuracy and clock period specifications are guaranteed with the assumption that the REF output is at 14.31818MHz.

# ELECTRICAL CHARACTERISTICS - CPU, SRC, AND DOT96 0.7 CURRENT MODE DIFFERENTIAL PAIR, CONTINUED<sup>(1)</sup>

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA =  $0^{\circ}$ C to + $70^{\circ}$ C, Supply Voltage: VDD = 3.3V ± 5%; CL = 2pF

| Symbol    | Parameter                                       | Test Conditions                        | Min. | Тур. | Max. | Unit |

|-----------|-------------------------------------------------|----------------------------------------|------|------|------|------|

|           | Skew, CPU[1:0] <sup>(2)</sup>                   |                                        | _    | _    | 100  |      |

| tsk3      | Skew, CPU2 <sup>(2)</sup>                       | VT = 50%                               | -    | —    | 250  | ps   |

|           | Skew, SRC <sup>(2)</sup>                        |                                        |      |      | 250  |      |

|           | Jitter, Cycle to Cycle, CPU[1:0] <sup>(2)</sup> |                                        |      | -    | 85   |      |

| tucyc-cyc | Jitter, Cycle to Cycle, CPU2 <sup>(2)</sup>     | Measurement from differential waveform |      |      | 100  | ps   |

|           | Jitter, Cycle to Cycle, SRC <sup>(2)</sup>      |                                        | _    |      | 125  |      |

|           | Jitter, Cycle to Cycle, DOT96 <sup>(2)</sup>    |                                        | _    | _    | 250  |      |

NOTES:

1. SRC clock outputs run only at 100MHz.

2. This parameter is guaranteed by design, but not 100% production tested.

# ELECTRICAL CHARACTERISTICS - PCICLK / PCICLK\_F

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA =  $0^{\circ}$ C to + $70^{\circ}$ C, Supply Voltage: VDD = 3.3V ± 5%; CL = 10 - 30pF

| Symbol    | Parameter                             | Test Conditions             | Min.   | Тур. | Max.    | Unit |

|-----------|---------------------------------------|-----------------------------|--------|------|---------|------|

| ppm       | Static Error <sup>(1,2)</sup>         | See Tperiod Min Max. values | _      | _    | 0       | ppm  |

| TPERIOD   | Clock Period <sup>(2)</sup>           | 33.33MHz output nominal     | 29.991 | _    | 30.009  | ns   |

|           |                                       | 33.33MHz output spread      | 29.991 | _    | 30.1598 |      |

| Vон       | Output HIGH Voltage                   | Юн = -1mA                   | 2.4    | _    | _       | V    |

| Vol       | Output LOW Voltage                    | IOL = 1mA                   | _      | —    | 0.55    | V    |

| Юн        | Output HIGH Current                   | VOH at Min. = 1V            | -33    | _    | _       | mA   |

|           |                                       | Voн at Max. = 3.135V        | _      | _    | -33     | ]    |

| IOL       | Output LOW Current                    | Vo∟ at Min. = 1.95V         | 30     | _    | _       | mA   |

|           |                                       | VOL at Max. = 0.4V          | _      | _    | 38      |      |

|           | Edge Rate <sup>(1)</sup>              | Rising edge rate            | 1      | _    | 4       | V/ns |

|           | Edge Rate <sup>(1)</sup>              | Falling edge rate           | 1      | _    | 4       | V/ns |

| tR1       | Rise Time <sup>(1)</sup>              | VOL = 0.8V, VOH = 2V        | 0.3    | _    | 1.2     | ns   |

| tF1       | FallTime <sup>(1)</sup>               | VOL = 0.8V, VOH = 2V        | 0.3    | _    | 1.2     | ns   |

| dT1       | Duty Cycle <sup>(1)</sup>             | VT = 1.5V                   | 45     | _    | 55      | %    |

| tSK1      | Skew <sup>(1)</sup>                   | VT = 1.5V                   | —      | _    | 500     | ps   |

| tucyc-cyc | Jitter, Cycle to Cycle <sup>(1)</sup> | VT = 1.5V                   | _      | _    | 500     | ps   |

NOTES:

1. This parameter is guaranteed by design, but not 100% production tested.

2. All long term accuracy and clock period specifications are guaranteed with the assumption that the REF output is at 14.31818MHz.

#### **ELECTRICAL CHARACTERISTICS, 48MHZ, USB**

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, Supply Voltage: VDD = 3.3V ± 5%; CL = 10 - 20pF

| Symbol    | Parameter                     | Test Conditions             | Min.    | Тур. | Max.   | Unit |

|-----------|-------------------------------|-----------------------------|---------|------|--------|------|

| ppm       | Static Error <sup>(1,2)</sup> | See Tperiod Min Max. values | —       | —    | 0      | ppm  |

| TPERIOD   | Clock Period <sup>(2)</sup>   | 48MHz output nominal        | 20.8257 | _    | 20.834 | ns   |

| Vон       | Output HIGH Voltage           | IOH = -1mA                  | 2.4     | _    | _      | V    |

| Vol       | Output LOW Voltage            | IOL = 1mA                   | _       | —    | 0.55   | V    |

| Іон       | Output HIGH Current           | Voн at Min. = 1V            | -29     | _    | _      | mA   |

|           |                               | Vон at Max. = 3.135V        | _       | —    | -23    |      |

| IOL       | Output LOW Current            | VoL at Min. = 1.95V         | 29      | _    | _      | mA   |

|           |                               | VoL at Max. = 0.4V          | _       | _    | 27     |      |

|           | Edge Rate <sup>(1)</sup>      | Rising edge rate            | 1       | _    | 2      | V/ns |

|           | Edge Rate <sup>(1)</sup>      | Fallingedgerate             | 1       | _    | 2      | V/ns |

| tR1       | Rise Time <sup>(1)</sup>      | Vol = 0.8V, Voh = 2V        | 0.5     | _    | 1.2    | ns   |

| tF1       | Fall Time <sup>(1)</sup>      | Vol = 0.8V, Voh = 2V        | 0.5     | _    | 1.2    | ns   |

| dT1       | Duty Cycle <sup>(1)</sup>     | VT = 1.5V                   | 45      | _    | 55     | %    |

| tлсус-сус | Jitter, Cycle to Cycle        |                             | _       | _    | 350    | ps   |

NOTES:

1. This parameter is guaranteed by design, but not 100% production tested.

2. All long term accuracy and clock period specifications are guaranteed with the assumption that the REF output is at 14.31818MHz.

### **ELECTRICAL CHARACTERISTICS-REF-14.318MHZ**

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA =  $0^{\circ}$ C to +70°C, Supply Voltage: VDD =  $3.3V \pm 5\%$ ; CL = 10 - 20pF

| Symbol          | Parameter                             | Test Conditions             | Min.   | Тур. | Max.   | Unit |

|-----------------|---------------------------------------|-----------------------------|--------|------|--------|------|

| ppm             | Long Accuracy <sup>(1)</sup>          | See Tperiod Min Max. values | —      | —    | 0      | ppm  |

| TPERIOD         | Clock Period                          | 14.318MHz output nominal    | 69.827 | —    | 69.855 | ns   |

| Vон             | Output HIGH Voltage <sup>(1)</sup>    | Юн = -1mA                   | 2.4    | —    | _      | V    |

| Vol             | Output LOW Voltage <sup>(1)</sup>     | IOL = 1mA                   | _      | —    | 0.4    | V    |

| Іон             | Output HIGH Current                   | VOH at Min. = 1V            | -33    | —    | _      | mA   |

|                 |                                       | Voн at Max. = 3.135V        | _      | _    | -33    |      |

| IOL             | Output LOW Current                    | VoL at Min. = 1.95V         | 30     | —    | _      | mA   |

|                 |                                       | VoL at Max. = 0.4V          | —      | —    | 38     |      |

|                 | Edge Rate <sup>(1)</sup>              | Rising edge rate            | 1      | —    | 4      | V/ns |

|                 | Edge Rate <sup>(1)</sup>              | Falling edge rate           | 1      | —    | 4      | V/ns |

| t <sub>R1</sub> | Rise Time <sup>(1)</sup>              | Vol = 0.8V, Voh = 2V        | 0.3    | _    | 1.2    | ns   |

| tF1             | Fall Time <sup>(1)</sup>              | Vol = 0.8V, Voн = 2V        | 0.3    | _    | 1.2    | ns   |

| dT1             | Duty Cycle <sup>(1)</sup>             | VT = 1.5V                   | 45     | —    | 55     | %    |

| tucyc-сус       | Jitter, Cycle to Cycle <sup>(1)</sup> | VT = 1.5V                   | —      | _    | 1000   | ps   |

NOTE:

1. This parameter is guaranteed by design, but not 100% production tested.

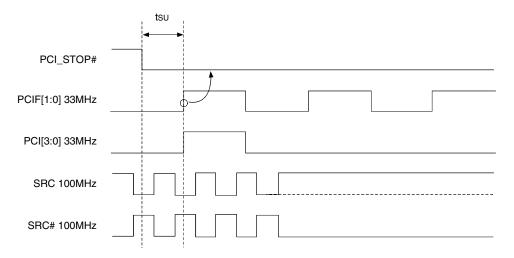

#### **PCI STOP FUNCTIONALITY**

The PCI\_STOP# signal is on an active low input controlling PCI and SRC outputs. If PCIF[1:0] and SRC clocks can be set to be free-running through SMBus programming, they will ignore both the PCI\_STOP# pin and the PCI\_STOP register bit.

| PCI_STOP# | CPU    | CPU#   | SRC               | SRC#   | PCIF/PCI | USB   | DOT96  | DOT96# | REF       |

|-----------|--------|--------|-------------------|--------|----------|-------|--------|--------|-----------|

| 1         | Normal | Normal | Normal            | Normal | 33MHz    | 48MHz | Normal | Normal | 14.318MHz |

| 0         | Normal | Normal | IREF * 6 or float | Low    | Low      | 48MHz | Normal | Normal | 14.318MHz |

#### PCI\_STOP# ASSERTION (TRANSITION FROM '1' TO '0')

The clock samples the PCI\_STOP# signal on a rising edge of PCIF clock. After detecting the PCI\_STOP# assertion low, all PCI[6:0] and stoppable PCIF[1:0] clocks will latch low on their next high to low transition. After the PCI clocks are latched low, the SRC clock, (if set to stoppable) will latch high at IREF \* 6 (or tristate if Byte 2 Bit 6 = 1) upon its next low to high transition and the SRC# will latch low as shown below.

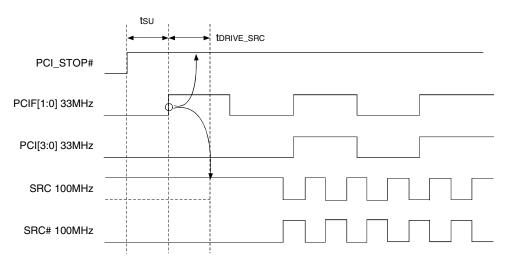

#### PCI\_STOP#-DE-ASSERTION

The de-assertion of the PCI\_STOP# signal is to be sampled on the rising edge of the PCIF free running clock domain. After detecting PCI\_STOP# de-assertion, all PCI[6:0], stoppable PCIF[1:0] and stoppable SRC clocks will resume in a glitch free manner.

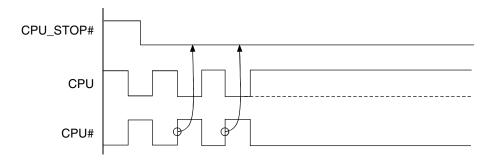

#### **CPU STOP FUNCTIONALITY**

The CPU\_STOP# signal is an active low input controlling the CPU outputs. This signal can be asserted asynchronously.

| CPU_STOP# | CPU               | CPU#   | SRC    | SRC#   | PCIF/PCI | USB   | DOT96  | DOT96# | REF       |

|-----------|-------------------|--------|--------|--------|----------|-------|--------|--------|-----------|

| 1         | Normal            | Normal | Normal | Normal | 33MHz    | 48MHz | Normal | Normal | 14.318MHz |

| 0         | IREF * 6 or float | Low    | Normal | Normal | 33MHz    | 48MHz | Normal | Normal | 14.318MHz |

#### CPU\_STOP# ASSERTION (TRANSITION FROM '1' TO '0')

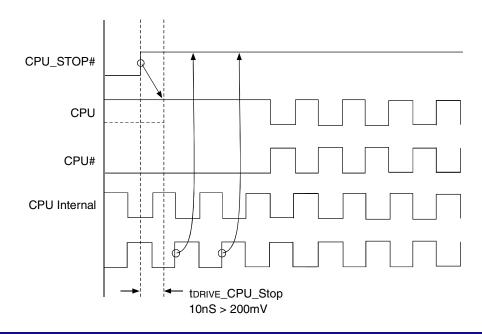

Asserting CPU\_STOP# pin stops all CPU outputs that are set to be stoppable after their next transition. When the SMBus CPU\_STOP tri-state bit corresponding to the CPU output of interest is programmed to a '0', CPU output will stop CPU\_True = High and CPU\_Complement = Low. When the SMBus CPU\_STOP# tri-state bit corresponding to the CPU output of interest is programmed to a '1', CPU outputs will be tri-stated.

#### CPU\_STOP# - DE-ASSERTION (TRANSITION FROM '0' TO '1')

With the de-assertion of CPU\_STOP# all stopped CPU outputs will resume without a glitch. The maximum latency from the de-assertion to active outputs is two to six CPU clock periods. If the control register tristate bit corresponding to the output of interest is programmed to '1', then the stopped CPU outputs will be driven High within 10nS of CPU\_STOP# de-assertion to a voltage greater than 200mV.

#### **PD, POWER DOWN**

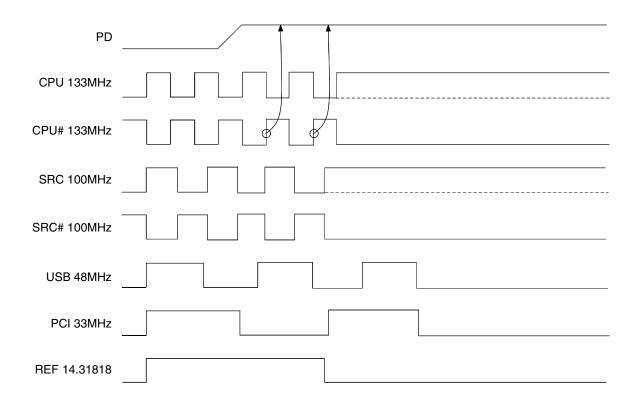

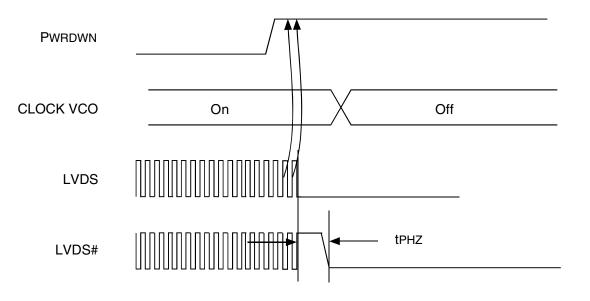

PD is an asynchronous active high input used to shut off all clocks cleanly prior to clock power. When PD is asserted high all clocks will be driven low before turning off the VCO. In PD de-assertion all clocks will start without glitches.

| PD | CPU               | CPU#   | SRC               | SRC#   | PCIF/PCI | USB   | DOT96             | DOT96# | REF       |

|----|-------------------|--------|-------------------|--------|----------|-------|-------------------|--------|-----------|

| 0  | Normal            | Normal | Normal            | Normal | 33MHz    | 48MHz | Normal            | Normal | 14.318MHz |

| 1  | IREF * 2 or float | Float  | IREF * 2 or float | Float  | Low      | Low   | IREF * 2 or float | Float  | Low       |

## **PDASSERTION**

#### **PD DE-ASSERTION**

#### DIFFERENTIAL CLOCK TRISTATE

To minimize power consumption, CPU[2:0] clock outputs are individually configurable through SMBus to be driven or tristated during PD and CPU\_STOP# mode and the SRC clock is configurable to be driven or tristated during PCI\_STOP# and PD mode. Each differential clock (SRC, CPU[2:0]) output can be disabled by setting the corresponding output's register OE bit to "0" (disable). Disabled outputs are to be tristated regardless of "CPU\_STOP", "SRC\_STOP" and "PD" register bit settings.

| Signal | Pin PD | Pin CPU_STOP# | CPU_STOPTristate Bit | PD Tristate Bit | Non-Stoppable Outputs | Stoppable Outputs  |

|--------|--------|---------------|----------------------|-----------------|-----------------------|--------------------|

| CPU    | 0      | 1             | Х                    | Х               | Running               | Running            |

| CPU    | 0      | 0             | 0                    | Х               | Running               | Driven at IREF x 6 |

| CPU    | 0      | 0             | 1                    | Х               | Running               | Tristate           |

| CPU    | 1      | Х             | Х                    | 0               | Driven at IREF x 2    | Driven at IREF x 2 |

| CPU    | 1      | Х             | Х                    | 1               | Tristate              | Tristate           |

NOTES:

1. Each output has four corresponding control register bits; OE, PD, CPU\_STOP, and "Free Running".

2. IREF x 6 and IREF x 2 is the output current in the corresponding mode.

3. See CONTROL REGISTERS section for bit address.

| Signal | Pin PD | Pin PCI_STOP# | PCI_STOPTristate Bit | PD Tristate Bit | Non-Stoppable Outputs | Stoppable Outputs  |

|--------|--------|---------------|----------------------|-----------------|-----------------------|--------------------|

| SRC    | 0      | 1             | Х                    | Х               | Running               | Running            |

| SRC    | 0      | 0             | 0                    | Х               | Running               | Driven at IREF x 6 |

| SRC    | 0      | 0             | 1                    | Х               | Running               | Tristate           |

| SRC    | 1      | Х             | Х                    | 0               | Driven at IREF x 2    | Driven at IREF x 2 |

| SRC    | 1      | X             | Х                    | 1               | Tristate              | Tristate           |

#### NOTES:

1. SRC output has four corresponding control register bits; OE, PD, SRC\_STOP, and "Free Running".

2. IREF x 6 and IREF x 2 is the output current in the corresponding mode.

3. See CONTROL REGISTERS section for bit address.

#### **TRISTATE DOT96 CLOCK CONTROL**

| Signal | Pin PD | PD Tristate Bit | Output             |

|--------|--------|-----------------|--------------------|

| DOT96  | 1      | Х               | Running            |

| DOT96  | 0      | 0               | Driven at IREF x 2 |

| DOT96  | 0      | 1               | Tristate           |

#### NOTES:

1. DOT output has two corresponding control register bits; OE and PD.

2. IREF x 6 and IREF x 2 is the output current in the corresponding mode.

3. See CONTROL REGISTERS section for bit address.

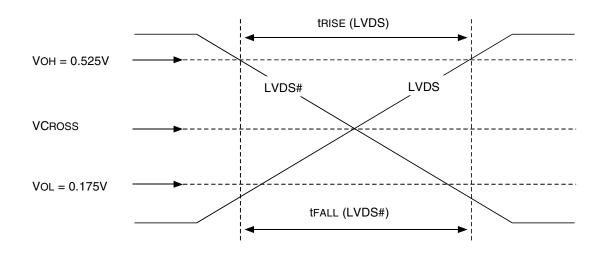

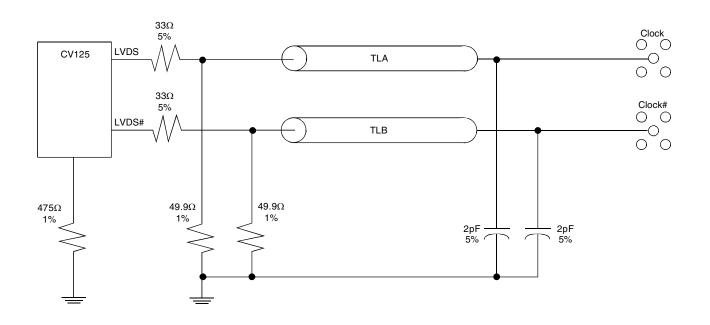

## LVDS AC TIMING REQUIREMENTS

Following Conditions Apply Unless Otherwise Specified: Operating Condition:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| Symbol                | Parameter                                                          | Min.  | Тур. | Max.         | Unit |

|-----------------------|--------------------------------------------------------------------|-------|------|--------------|------|

| tr:1                  | Clock Rise Time <sup>(1,2,3)</sup>                                 | 175   | _    | 700          | ps   |

| tF1                   | Clock Fall Time <sup>(1,2,3)</sup>                                 | 175   |      | 700          | ps   |

| $\Delta{ m tr}$       | Clock Rise Time Variation <sup>(2,3,4)</sup>                       | _     | -    | 125          | ps   |

| ΔtF                   | Clock Fall Time Variation <sup>(2,3,4)</sup>                       | _     | _    | 125          | ps   |

|                       | Rise/Fall Matching <sup>(2,3,5)</sup>                              | -     | _    | 20           | %    |

| Vhigh                 | Voltage HIGH <sup>(2,3,6)</sup>                                    | 660   | 700  | 850          | mV   |

| VLOW                  | Voltage LOW <sup>(2,3,7)</sup>                                     | -150  | 0    | _            | mV   |

| VCROSS(ABS)           | Crossing Voltage (abs) <sup>(2,3,8,9,10)</sup>                     | 250   | _    | 550          | mV   |

| VCROSS(REL)           | Crossing Voltage (rel) <sup>(2,3,10,11)</sup>                      | Calc. | _    | Calc.        |      |

| Total $\Delta$ VCROSS | Total Variation of VCROSS Over All Edges <sup>(2,3,12)</sup>       | _     | _    | 140          | mV   |

| tucyc-cyc             | Cycle-to-Cycle Jitter <sup>(2,13)</sup>                            | _     | _    | 350          | ps   |

| dтз                   | Duty Cycle <sup>(2,13)</sup>                                       | 45    | _    | 55           | %    |

| Vovs                  | Maximum Voltage Allowed at Output (overshoot) <sup>(2,3,14)</sup>  | _     | _    | Vнідн + 0.3V | V    |

| Vuds                  | Minimum Voltage Allowed at Output (undershoot) <sup>(2,3,15)</sup> | -0.3  | _    | —            | V    |

| Vrb                   | Ringback Margin <sup>(2,3)</sup>                                   | n/a   | —    | 0.2          | V    |

#### NOTES:

1. Measured from VoL = 1.75V to VoH =0.525V. Only valid for Rising LVDS and Falling LVDS#. Signal must be monotonic through the VoL to VoH region for tRISE and tFALL.

2. Test configuration is Rs =  $32.2\Omega$ , Rp =  $49.9\Omega$ , 2pF.

3. Measurement taken from single-ended waveform.

- 4. Measured with oscilloscope, averaging off, using Min. Max. statistics. Variation is the delta between Min. and Max.

- 5. Measured with oscilloscope, averaging off, the difference between the tRISE (average) of LVDS versus the tFALL (average) of LVDS#.

- 6. VHIGH is defined as the statistical average HIGH value as obtained by using the oscilloscope VHIGH math function.

- 7. VLow is defined as the statistical average LOW value as obtained by using the oscilloscope VLow math function.

- 8. Measured at crossing point where the instantaneous voltage value of the rising edge of LVDS equals the falling edge of LVDS#.

- 9. This measurement refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing.

10. The crossing point must meet the absolute and relative crossing point specifications simultaniously.

11. VCROSS (rel) Min. and Max. are derived using the following: VCROSS (rel) Min. = 0.25V + 0.5 (VHAVG - 0.7V), VCROSS (rel) Max. = 0.55V + 0.5 (0.7V - VHAVG).

A VCROSS is defined as the total variation of all crossing voltages of Rising LVDS and Falling LVDS#. This is the maximum allowed variance in VCROSS for any particular system.

Measurement is taken from differential waveform.

14. Overshoot is defined as the absolute value of the maximum voltage.

15. Undershoot is defined as the absolute value of the minimum voltage.

#### LVDS AVERAGE PERIOD, TPERIOD<sup>(1,2,3,4)</sup>

Following Conditions Apply Unless Otherwise Specified:

| Operating Condition: $IA = 0^{\circ}C$ to | +70°C |

|-------------------------------------------|-------|

|-------------------------------------------|-------|

|                    | 96MHz  |        | 100MHz |        |      |  |

|--------------------|--------|--------|--------|--------|------|--|

| Spread             | Min.   | Max.   | Min.   | Max.   | Unit |  |

| 0% (no spread)     | 10.406 | 10.427 | 9.99   | 10.01  | ns   |  |

| 0.8% down-spread   | 10.406 | 10.511 | 9.99   | 10.09  | ns   |  |

| 1% down-spread     | 10.406 | 10.531 | 9.99   | 10.11  | ns   |  |

| 1.25% down-spread  | 10.406 | 10.557 | 9.99   | 10.135 | ns   |  |

| 1.5% down-spread   | 10.406 | 10.583 | 9.99   | 10.16  | ns   |  |

| 1.75% down-spread  | 10.406 | 10.61  | 9.99   | 10.185 | ns   |  |

| 2% down-spread     | 10.406 | 10.636 | 9.99   | 10.21  | ns   |  |

| 2.5% down-spread   | 10.406 | 10.688 | 9.99   | 10.26  | ns   |  |

| 3% down-spread     | 10.406 | 10.74  | 9.99   | 10.31  | ns   |  |

| ±0.3% down-spread  | 10.375 | 10.458 | 9.96   | 10.04  | ns   |  |

| ±0.4% down-spread  | 10.365 | 10.469 | 9.95   | 10.05  | ns   |  |

| ±0.5% down-spread  | 10.354 | 10.479 | 9.94   | 10.06  | ns   |  |

| ±0.6% down-spread  | 10.344 | 10.49  | 9.93   | 10.07  | ns   |  |

| ±0.8% down-spread  | 10.323 | 10.511 | 9.91   | 10.09  | ns   |  |

| ±1% down-spread    | 10.302 | 10.531 | 9.89   | 10.11  | ns   |  |

| ±1.25% down-spread | 10.276 | 10.557 | 9.865  | 10.135 | ns   |  |

| ±1.5% down-spread  | 10.25  | 10.583 | 9.84   | 10.16  | ns   |  |

#### NOTES:

1. Test configuration is Rs =  $32.2\Omega$ , Rp =  $49.9\Omega$ , 2pF.

2. The average period over any 1µS period of time must be greater than the minimum and less than the maximum specified period.

3. Measurement is taken from differential waveform.

4. Calculated using a ±0.1% accuracy in spread modulation. Assumes 300ppm long term accuracy on CLKIN.

Single-Ended Measurement Point for tRISE and TFALL

#### **MISCELLANEOUS ACTIMING REQUIREMENTS**

$\label{eq:conditions} Following \, Conditions \, Apply \, Unless \, Otherwise \, Specified:$

Operating Condition:  $TA = 0^{\circ}C$  to  $+70^{\circ}C$

| Symbol          | Parameter                                                   | Min. | Тур. | Max. | Unit |

|-----------------|-------------------------------------------------------------|------|------|------|------|

| tPZL            | Output Enable Delay (All Outputs) <sup>(1)</sup>            | 0    | _    | 10   | μs   |

| tPZH            |                                                             |      |      |      |      |

| tPLZ            | Output Disable Delay (All Outputs) <sup>(1)</sup>           | 0    | _    | 10   | μs   |

| tPHZ            |                                                             |      |      |      |      |

| <b>t</b> STABLE | All Clock Stabilization from Power-Up <sup>(2)</sup>        | _    | _    | 3    | ms   |

| <b>İ</b> SPREAD | Setting Period for Spread Selection Change <sup>(2,3)</sup> | _    |      | 3    | ms   |

#### NOTES: