Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 256-Kbit (32 K × 8) nvSRAM with Real Time Clock

#### **Features**

- 256-Kbit nonvolatile static random access memory (nvSRAM)

- □ 25 ns and 45 ns access times

- □ Internally organized as 32 K × 8 (CY14B256KA)

- ☐ Hands off automatic STORE on power-down with only a small capacitor

- □ STORE to QuantumTrap nonvolatile elements is initiated by software, hardware, or AutoStore on power-down

- □ RECALL to SRAM initiated on power-up or by software

- High reliability

- □ Infinite Read, Write, and RECALL cycles

- □ 1 million STORE cycles to QuantumTrap

- □ 20 year data retention

- Real time clock (RTC)

- □ Full-featured real time clock

- □ Watchdog timer

- □ Clock alarm with programmable interrupts

- □ Capacitor or battery backup for RTC

- □ Backup current of 0.35 µA (Typ)

- Industry standard configurations

- ☐ Single 3 V +20%, –10% operation

- □ Industrial temperature

- □ 48-pin shrink small-outline package (SSOP)

- □ Pb-free and Restriction of hazardous substances (RoHS) compliant

# **Functional Description**

The Cypress CY14B256KA combines a 256-Kbit nonvolatile static RAM with a full featured real time clock in a monolithic integrated circuit. The embedded nonvolatile elements incorporate QuantumTrap technology producing the world's most reliable nonvolatile memory. The SRAM is read and written an infinite number of times, while independent nonvolatile data resides in the nonvolatile elements.

The real time clock function provides an accurate clock with leap year tracking and a programmable, high accuracy oscillator. The alarm function is programmable for periodic minutes, hours, days, or months alarms. There is also a programmable watchdog timer for process control.

For a complete list of related documentation, click here.

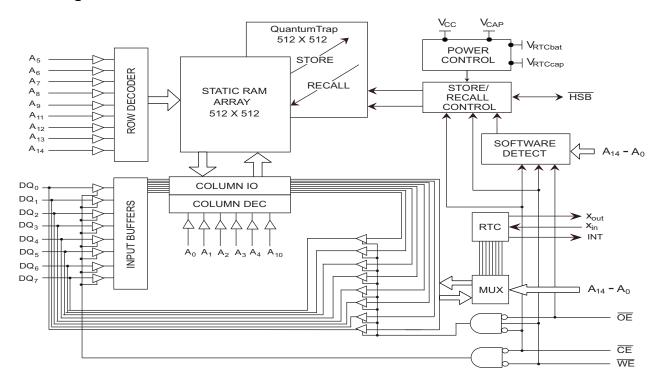

# Logic Block Diagram

# Contents

| Pinouts                              | 3  |

|--------------------------------------|----|

| Pin Definitions                      | 3  |

| Device Operation                     | 4  |

| SRAM Read                            | 4  |

| SRAM Write                           | 4  |

| AutoStore Operation                  | 4  |

| Hardware STORE (HSB) Operation       | 4  |

| Hardware RECALL (Power-Up)           |    |

| Software STORE                       |    |

| Software RECALL                      | 5  |

| Preventing AutoStore                 | 6  |

| Data Protection                      | 6  |

| Real Time Clock Operation            | 7  |

| nvTIME Operation                     | 7  |

| Clock Operations                     | 7  |

| Reading the Clock                    | 7  |

| Setting the Clock                    | 7  |

| Backup Power                         |    |

| Stopping and Starting the Oscillator |    |

| Calibrating the Clock                | 8  |

| Alarm                                | 8  |

| Watchdog Timer                       | 8  |

| Power Monitor                        | 9  |

| Interrupts                           | 9  |

| Interrupt Register                   | 9  |

| Flags Register                       |    |

| RTC External Components              | 10 |

| PCB Design Considerations for RTC    | 11 |

| Layout requirements                  | 11 |

| Maximum Ratings                      |    |

| Operating Range                      | 16 |

| DC Electrical Characteristics           | 16 |

|-----------------------------------------|----|

| Data Retention and Endurance            | 17 |

| Capacitance                             |    |

| Thermal Resistance                      | 17 |

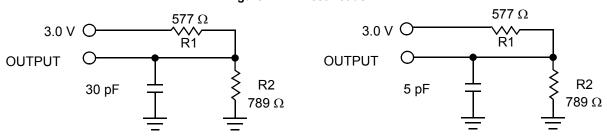

| AC Test Loads                           | 18 |

| AC Test Conditions                      | 18 |

| RTC Characteristics                     | 18 |

| AC Switching Characteristics            | 19 |

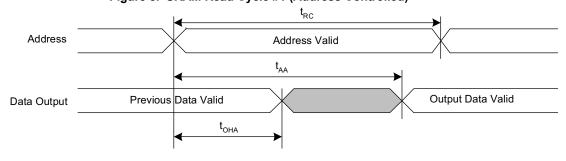

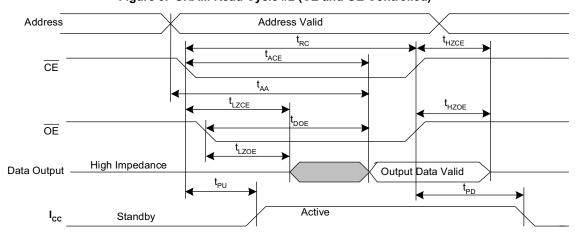

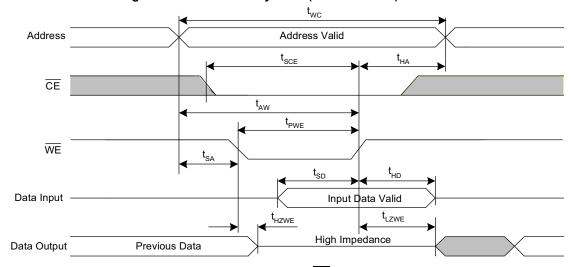

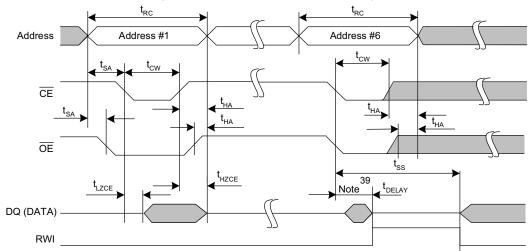

| SRAM Read Cycle                         | 19 |

| SRAM Write Cycle                        | 19 |

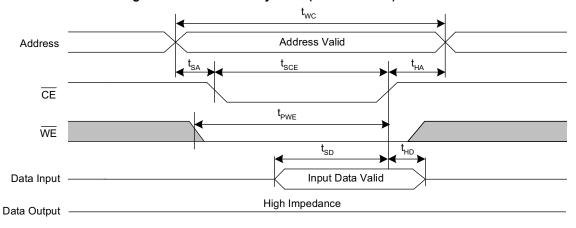

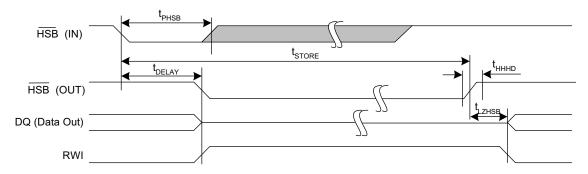

| AutoStore/Power-Up RECALL               | 21 |

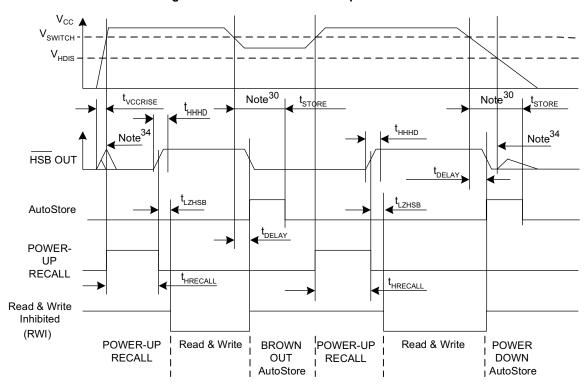

| Switching Waveforms                     |    |

| Software Controlled STORE/RECALL Cycle  | 22 |

| Switching Waveforms                     | 22 |

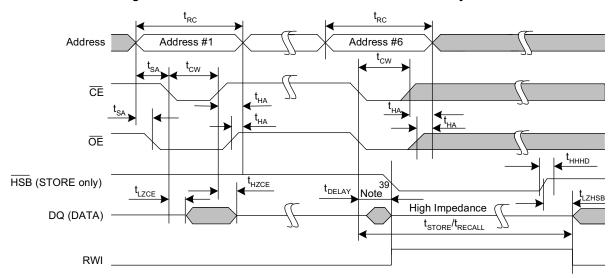

| Hardware STORE Cycle                    | 23 |

| Switching Waveforms                     | 23 |

| Truth Table For SRAM Operations         | 24 |

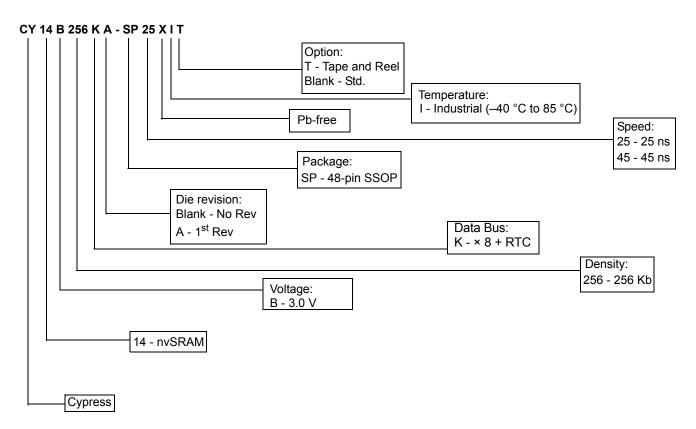

| Ordering Information                    | 24 |

| Ordering Code Definitions               | 24 |

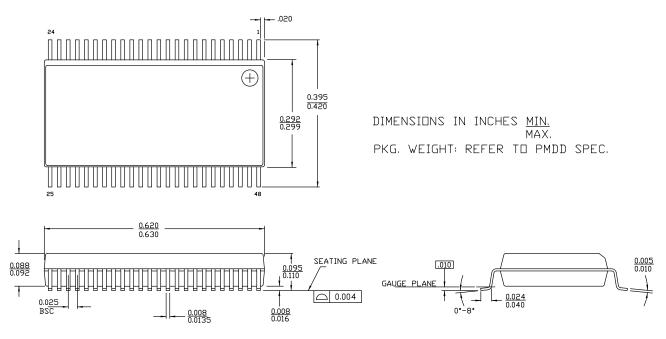

| Package Diagram                         | 25 |

| Acronyms                                | 26 |

| Document Conventions                    |    |

| Units of Measure                        | 26 |

| Document History Page                   |    |

| Sales, Solutions, and Legal Information | 28 |

| Worldwide Sales and Design Support      |    |

| Products                                |    |

| PSoC® Solutions                         |    |

| Cypress Developer Community             | 28 |

| Technical Support                       | 28 |

# **Pinouts**

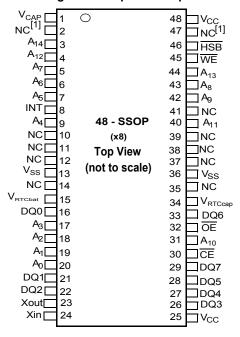

Figure 1. 48-pin SSOP pinout

# **Pin Definitions**

| Pin Name                           | I/O Type     | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>0</sub> -A <sub>14</sub>    | Input        | Address inputs. Used to select One of the 32,768 bytes of the nvSRAM.                                                                                                                                                                                                                                                                                                                                         |

| DQ <sub>0</sub> –DQ <sub>7</sub>   | Input/Output | Bidirectional data I/O Lines. Used as input or output lines depending on operation.                                                                                                                                                                                                                                                                                                                           |

| NC                                 | No connect   | No connect. This pin is not connected to the die.                                                                                                                                                                                                                                                                                                                                                             |

| WE                                 | Input        | Write Enable input, Active LOW. When the chip is enabled and $\overline{\text{WE}}$ is LOW, data on the I/O pins is written to the specific address location.                                                                                                                                                                                                                                                 |

| CE                                 | Input        | Chip Enable input, Active LOW. When LOW, selects the chip. When HIGH, deselects the chip.                                                                                                                                                                                                                                                                                                                     |

| ŌĒ                                 | Input        | Output Enable, Active LOW. The active LOW OE input enables the data output buffers during read cycles. Deasserting OE HIGH causes the I/O pins to tristate.                                                                                                                                                                                                                                                   |

| X <sub>out</sub> <sup>[2]</sup>    | Output       | Crystal connection. Drives crystal on start up.                                                                                                                                                                                                                                                                                                                                                               |

| $X_{in}^{[2]}$                     | Input        | Crystal connection. For 32.768 kHz crystal.                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>RTCcap</sub> <sup>[2]</sup> | Power supply | Capacitor supplied backup RTC supply voltage. Left unconnected if V <sub>RTCbat</sub> is used.                                                                                                                                                                                                                                                                                                                |

| V <sub>RTCbat</sub> <sup>[2]</sup> | Power supply | Battery supplied backup RTC supply voltage. Left unconnected if V <sub>RTCcap</sub> is used.                                                                                                                                                                                                                                                                                                                  |

| INT <sup>[2]</sup>                 | Output       | Interrupt output. Programmable to respond to the clock alarm, the watchdog timer, and the power monitor. Also programmable to either active HIGH (push or pull) or LOW (open drain).                                                                                                                                                                                                                          |

| $V_{SS}$                           | Ground       | Ground for the device. Must be connected to the ground of the system.                                                                                                                                                                                                                                                                                                                                         |

| V <sub>CC</sub>                    | Power supply | Power supply inputs to the Device. 3.0 V +20%, –10%                                                                                                                                                                                                                                                                                                                                                           |

| HSB                                | Input/Output | Hardware STORE Busy (HSB) Output: Indicates busy status of nvSRAM when LOW. After each Hardware and Software STORE operation, HSB is driven HIGH for a short time (t <sub>HHHD</sub> ) with standard output high current and then a weak internal pull-up resistor keeps this pin HIGH (external pull-up resistor connection optional). Input: Hardware STORE implemented by pulling this pin LOW externally. |

| V <sub>CAP</sub>                   | Power supply | AutoStore capacitor. Supplies power to the nvSRAM during power loss to store data from SRAM to nonvolatile elements.                                                                                                                                                                                                                                                                                          |

- Address expansion for 1-Mbit. NC pin not connected to die.

Left unconnected if RTC feature is not used.

# **Device Operation**

The CY14B256KA nvSRAM is made up of two functional components paired in the same physical cell. These are a SRAM memory cell and a nonvolatile QuantumTrap cell. The SRAM memory cell operates as a standard fast static RAM. Data in the SRAM is transferred to the nonvolatile cell (the STORE operation), or from the nonvolatile cell to the SRAM (the RECALL operation). Using this unique architecture, all cells are stored and recalled in parallel. During the STORE and RECALL operations SRAM read and write operations are inhibited. The CY14B256KA supports infinite reads and writes similar to a typical SRAM. In addition, it provides infinite RECALL operations from the nonvolatile cells and up to 1 million STORE operations. Refer the Truth Table For SRAM Operations on page 24 for a complete description of read and write modes.

#### **SRAM Read**

The CY14B256KA performs a read cycle whenever  $\overline{\text{CE}}$  and  $\overline{\text{OE}}$  are LOW, and  $\overline{\text{WE}}$  and  $\overline{\text{HSB}}$  are HIGH. The address specified on pins  $A_{0-14}$  determines which of the 32,768 data bytes are accessed. When the read is initiated by an address transition, the outputs are valid after a delay of  $t_{AA}$  (read cycle #1). If the read is initiated by  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$ , the outputs are valid at  $t_{ACE}$  or at  $t_{DOE}$ , whichever is later (read cycle #2). The data output repeatedly responds to address changes within the  $t_{AA}$  access time without the need for transitions on any control input pins. This remains valid until another address change or until  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  is brought HIGH, or  $\overline{\text{WE}}$  or  $\overline{\text{HSB}}$  is brought LOW.

#### **SRAM Write**

A write cycle is performed when  $\overline{\text{CE}}$  and  $\overline{\text{WE}}$  are LOW and  $\overline{\text{HSB}}$  is HIGH. The address inputs must be stable before entering the write cycle and must remain stable until  $\overline{\text{CE}}$  or  $\overline{\text{WE}}$  goes HIGH at the end of the cycle. The data on the common I/O pins IO $_{0-7}$  are written into the memory if it is valid  $t_{SD}$  before the end of a WE-controlled write, or before the end of an  $\overline{\text{CE}}$ -controlled write. It is recommended that  $\overline{\text{OE}}$  be kept HIGH during the entire write cycle to avoid data bus contention on common I/O lines. If  $\overline{\text{OE}}$  is left LOW, internal circuitry turns off the output buffers  $t_{HZWE}$  after  $\overline{\text{WE}}$  goes LOW.

#### **AutoStore Operation**

The CY14B256KA stores data to the nvSRAM using one of three storage operations. These three operations are: Hardware STORE, activated by the HSB; Software STORE, activated by an address sequence; AutoStore, on device power-down. The AutoStore operation is a unique feature of QuantumTrap technology and is enabled by default on the CY14B256KA.

During normal operation, the device draws current from  $V_{CC}$  to charge a capacitor connected to the  $V_{CAP}$  pin. This stored charge is used by the chip to perform a single STORE operation. If the voltage on the  $V_{CC}$  pin drops below  $V_{SWITCH}$ , the part automatically disconnects the  $V_{CAP}$  pin from  $V_{CC}$ . A STORE operation is initiated with power provided by the  $V_{CAP}$  capacitor.

**Note** If the capacitor is not connected to  $V_{CAP}$  pin, AutoStore must be disabled using the soft sequence specified in Preventing AutoStore on page 6. In case AutoStore is enabled without a capacitor on  $V_{CAP}$  pin, the device attempts an AutoStore operation without sufficient charge to complete the Store. This corrupts the data stored in nvSRAM.

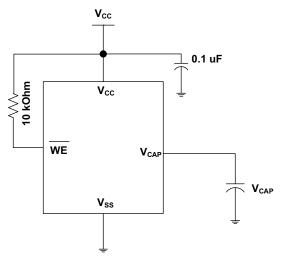

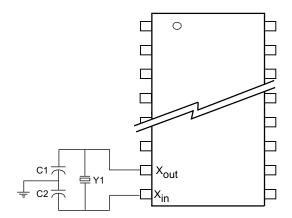

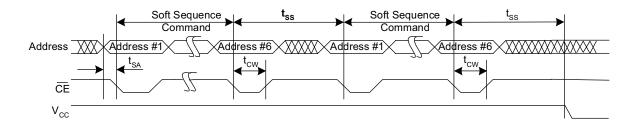

Figure 2. AutoStore Mode

Figure 2 shows the proper connection of the storage capacitor (V<sub>CAP</sub>) for automatic STORE operation. Refer to DC Electrical Characteristics on page 16 for the size of the V<sub>CAP</sub>. The voltage on the V<sub>CAP</sub> pin is driven to V<sub>CC</sub> by a regulator on the chip. Place a pull-up on WE to hold it inactive during power-up. This pull-up is only effective if the WE signal is tristate during power-up. Many MPUs tristate their controls on power-up. This must be verified when using the pull-up. When the nvSRAM comes out of power-on-RECALL, the MPU must be active or the WE held inactive until the MPU comes out of reset.

To reduce unnecessary nonvolatile stores, AutoStore and Hardware STORE operations are ignored unless at least one write operation has taken place since the most recent STORE or RECALL cycle. Software initiated STORE cycles are performed regardless of whether a write operation has taken place.

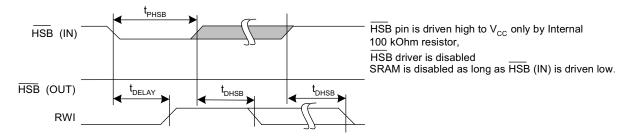

# Hardware STORE (HSB) Operation

The CY14B256KA provides the  $\overline{\text{HSB}}$   $\overline{\text{pin}}$  to control and acknowledge the STORE operations. The  $\overline{\text{HSB}}$   $\overline{\text{pin}}$  is used to request a Hardware STORE cycle. When the HSB pin is driven LOW, the CY14B256KA conditionally initiates a STORE operation after t<sub>DELAY</sub>. An actual STORE cycle begins only if a write to the SRAM <u>has</u> taken place since the last STORE or RECALL cycle. The  $\overline{\text{HSB}}$  pin also acts as an open drain driver (internal 100 k $\Omega$  weak pull-up resistor) that is internally driven LOW to indicate a busy condition when the STORE (initiated by any means) is in progress.

Note After each Hardware and Software STORE operation  $\overline{\text{HSB}}$  is driven HIGH for a short time (t<sub>HHHD</sub>) with standard output high current and then remains HIGH by internal 100 k $\Omega$  pull-up resistor.

SRAM write operations that are in progress when HSB is driven LOW by any means are given time (t<sub>DELAY</sub>) to complete before the STORE operation <u>is initiated</u>. However, any SRAM <u>write</u> cycles requested after HSB goes LOW are in<u>hibited</u> until HSB returns HIGH. In case the write latch is not set, HSB is not driven LOW by the CY14B256KA. But any SRAM read and write cycles are inhibited until HSB is returned HIGH by MPU or other external source.

During any STORE operation, regardless of how it is initiated, the CY14B256KA continues to drive the HSB pin LOW, releasing

it only when the STORE is complete. Upon completion of the STORE operation, the nvSRAM memory access is inhibited for  $t_{\rm LZHSB}$  time after HSB pin returns HIGH. Leave the HSB unconnected if it is not used.

#### Hardware RECALL (Power-Up)

During power-up or after any low power condition ( $V_{CC}$ <  $V_{SWITCH}$ ), an internal RECALL request is latched. When  $V_{CC}$  again exceeds the  $V_{SWITCH}$  on powerup, a RECALL cycle is automatically initiated and takes  $t_{HRECALL}$  to complete. During this time, the HSB pin is driven LOW by the HSB driver and all reads and writes to nvSRAM are inhibited.

#### Software STORE

Data is transferred from the SRAM to the nonvolatile memory by a software address sequence. The CY14B256KA Software STORE cycle is initiated by executing sequential CE or OE controlled read cycles from six specific address locations in exact order. During the STORE cycle, an erase of the previous nonvolatile data is first performed, followed by a program of the nonvolatile elements. After a STORE cycle is initiated, further input and output are disabled until the cycle is completed.

Because a sequence of reads from specific addresses is used for STORE initiation, it is important that no other read or write accesses intervene in the sequence, or the sequence is aborted and no STORE or RECALL takes place.

To initiate the Software STORE cycle, the following read sequence must be performed:

- 1. Read address 0x0E38 Valid READ

- 2. Read address 0x31C7 Valid READ

- 3. Read address 0x03E0 Valid READ

- 4. Read address 0x3C1F Valid READ

- 5. Read address 0x303F Valid READ

- 6. Read address 0x0FC0 Initiate STORE cycle

The software sequence may be clocked with CE controlled reads or OE controlled reads, with WE kept HIGH for all the six READ sequences. After the sixth address in the sequence is entered, the STORE cycle commences and the chip is disabled. HSB is driven LOW. After the t<sub>STORE</sub> cycle time is fulfilled, the SRAM is activated again for the read and write operation.

#### **Software RECALL**

Data is transferred from the nonvolatile memory to the SRAM by a software address sequence. A Software RECALL cycle is initiated with a sequence of read operations in a manner similar to the Software STORE initiation. To initiate the RECALL cycle, the following sequence of  $\overline{\text{CE}}$  or  $\overline{\text{OE}}$  controlled read operations must be performed:

- 1. Read address 0x0E38 Valid READ

- 2. Read address 0x31C7 Valid READ

- 3. Read address 0x03E0 Valid READ

- 4. Read address 0x3C1F Valid READ

- 5. Read address 0x303F Valid READ

- 6. Read address 0x0C63 Initiate RECALL cycle

Internally, RECALL is a two step procedure. First, the SRAM data is cleared. Next, the nonvolatile information is transferred into the SRAM cells. After the  $t_{RECALL}$  cycle time, the SRAM is again ready for read and write operations. The RECALL operation does not alter the data in the nonvolatile elements.

Table 1. Mode Selection

| CE | WE | OE | A <sub>14</sub> -A <sub>0</sub> <sup>[3]</sup>           | Mode                                                                                  | I/O                                                                                   | Power                                  |

|----|----|----|----------------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|

| Н  | X  | Χ  | X                                                        | Not Selected                                                                          | Output High Z                                                                         | Standby                                |

| L  | Н  | L  | Х                                                        | Read SRAM                                                                             | Output Data                                                                           | Active                                 |

| L  | L  | Х  | Х                                                        | Write SRAM                                                                            | Input Data                                                                            | Active                                 |

| L  | Н  | L  | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0B45 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>AutoStore<br>Disable | Output Data   | Active <sup>[4]</sup>                  |

| L  | Н  | L  | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0B46 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>AutoStore Enable     | Output Data   | Active <sup>[4]</sup>                  |

| L  | Н  | L  | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0FC0 | Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Read SRAM<br>Nonvolatile<br>STORE | Output Data Output Data Output Data Output Data Output Data Output Data Output High Z | Active I <sub>CC2</sub> <sup>[4]</sup> |

| L  | Н  | L  | 0x0E38<br>0x31C7<br>0x03E0<br>0x3C1F<br>0x303F<br>0x0C63 | Read SRAM Read SRAM Read SRAM Read SRAM Read SRAM Nonvolatile RECALL                  | Output Data Output Data Output Data Output Data Output Data Output Data Output High Z | Active <sup>[4]</sup>                  |

#### **Preventing AutoStore**

The AutoStore function is disabled by initiating an AutoStore disable sequence. A sequence of read operations is performed in a manner similar to the Software STORE initiation. To initiate the AutoStore disable sequence, the following sequence of CE or OE controlled read operations must be performed:

- 1. Read address 0x0E38 Valid READ

- 2. Read address 0x31C7 Valid READ

- 3. Read address 0x03E0 Valid READ

- 4. Read address 0x3C1F Valid READ

- 5. Read address 0x303F Valid READ

- 6. Read address 0x0B45 AutoStore Disable

The AutoStore is reenabled by initiating an AutoStore enable sequence. A sequence of read operations is performed in a manner similar to the Software RECALL initiation.

To initiate the AutoStore enable sequence, the following sequence of CE or OE controlled read operations must be performed:

- 1. Read address 0x0E38 Valid READ

- 2. Read address 0x31C7 Valid READ

- 3. Read address 0x03E0 Valid READ

- 4. Read address 0x3C1F Valid READ

- 5. Read address 0x303F Valid READ

- 6. Read address 0x0B46 AutoStore Enable

If the AutoStore function is disabled or re-enabled, a manual STORE operation (Hardware or Software) issued to save the AutoStore state through subsequent power-down cycles. The part comes from the factory with AutoStore enabled and 0x00 written in all cells.

#### **Data Protection**

The CY14B256KA protects data from corruption during low voltage conditions by inhibiting all externally initiated STORE and write operations. The low voltage condition is detected when  $V_{CC}$  is less than  $V_{SWITCH}.$  If the CY14B256KA is in a write mode (both CE and WE are LOW) at power-up, after a RECALL or STORE, the write is inhibited until the SRAM is enabled after  $t_{LZHSB}$  (HSB to output active). This protects against inadvertent writes during power-up or brown out conditions.

- 3. While there are 15 address lines on the CY14B256KA, only the lower 14 are used to control software modes.

- 4. The six consecutive address locations must be in the order listed. WE must be HIGH during all six cycles to enable a nonvolatile cycle.

# **Real Time Clock Operation**

#### nvTIME Operation

The CY14B256KA offers internal registers that contain clock, alarm, watchdog, interrupt, and control functions. RTC registers use the last 16 address locations of the SRAM. Internal double buffering of the clock and timer information registers prevents accessing transitional internal clock data during a read or write operation. Double buffering also circumvents disrupting normal timing counts or the clock accuracy of the internal clock when accessing clock data. Clock and alarm registers store data in BCD format.

RTC functionality is described in the following sections. The RTC register addresses for CY14B256KA range from 0x7FF0 to 0x7FFF. Refer to Table 3 on page 12 and Table 4 on page 13 for a detailed Register Map description.

#### **Clock Operations**

The clock registers maintain time up to 9,999 years in one-second increments. The time can be set to any calendar time and the clock automatically keeps track of days of the week and month, leap years, and century transitions. There are eight registers dedicated to the clock functions, which are used to set time with a write cycle and to read time with a read cycle. These registers contain the time of day in BCD format. Bits defined as '0' are currently not used and are reserved for future use by Cypress.

#### Reading the Clock

The double buffered RTC register structure reduces the chance of reading incorrect data from the clock. Internal updates to the CY14B256KA time keeping registers are stopped when the read bit 'R' (in the flags register at 0x7FF0) is set to '1' before reading clock data to prevent reading of data in transition. Stopping the register updates does not affect clock accuracy.

When a read sequence of RTC device is initiated, the update of the user timekeeping registers stops and does not restart until a '0' is written to the read bit 'R' (in the flags register at 0x7FF0). After the end of read sequence, all the RTC registers are simultaneously updated within 20 ms.

#### Setting the Clock

A write access to the RTC device stops updates to the time keeping registers and enables the time to be set when the write bit 'W' (in the flags register at 0x7FF0) is set to '1'. The correct day, date, and time is then written into the registers and must be in 24 hour BCD format. The time written is referred to as the "Base Time". This value is stored in nonvolatile registers and used in the calculation of the current time. When the write bit 'W' is cleared by writing '0' to it, the values of timekeeping registers are transferred to the actual clock counters after which the clock resumes normal operation.

If the time written to the timekeeping registers is not in the correct BCD format, each invalid nibble of the RTC registers continue counting to 0xF before rolling over to 0x0 after which RTC resumes normal operation.

**Note** After 'W' bit is set to '0', values written into the timekeeping, alarm, calibration, and interrupt registers are transferred to the RTC time keeping counters in  $t_{RTCp}$  time. These counter values must be saved to nonvolatile memory either by initiating a

Software/Hardware STORE or AutoStore operation. While working in AutoStore disabled mode, perform a STORE operation after  $t_{\text{RTCp}}$  time while writing into the RTC registers for the modifications to be correctly recorded.

#### **Backup Power**

The RTC in the CY14B256KA is intended for permanently powered operation. The  $V_{RTCcap}$  or  $V_{RTCbat}$  pin is connected depending on whether a capacitor or battery is chosen for the application. When the primary power,  $V_{CC}$ , fails and drops below  $V_{SWITCH}$  the device switches to the backup power supply.

The clock oscillator uses very little current, which maximizes the backup time available from the backup source. Regardless of the clock operation with the primary source removed, the data stored in the nvSRAM is secure, having been stored in the nonvolatile elements when power was lost.

During backup operation, the CY14B256KA consumes a  $0.35 \,\mu\text{A}$  (Typ) at room temperature. The user must choose capacitor or battery values according to the application.

**Note**: If a battery is applied to  $V_{RTCbat}$  pin prior to  $V_{CC}$ , the chip will draw high  $I_{BAK}$  current. This occurs even if the oscillator is disabled. In order to maximize battery life,  $V_{CC}$  must be applied before a battery is applied to  $V_{RTCbat}$  pin.

Backup time values based on maximum current specifications are shown in the following Table 2. Nominal backup times are approximately two times longer.

Table 2. RTC Backup Time

| Capacitor Value | Backup Time |

|-----------------|-------------|

| 0.1 F           | 72 hours    |

| 0.47 F          | 14 days     |

| 1.0 F           | 30 days     |

Using a capacitor has the obvious advantage of recharging the backup source each time the system is powered up. If a battery is used, a 3 V lithium is recommended and the CY14B256KA sources current only from the battery when the primary power is removed. However, the battery is not recharged at any time by the CY14B256KA. The battery capacity must be chosen for total anticipated cumulative down time required over the life of the system.

### Stopping and Starting the Oscillator

The OSCEN bit in the calibration register at 0x7FF8 controls the enable and disable of the oscillator. This bit is nonvolatile and is shipped to customers in the "enabled" (set to '0') state. To preserve the battery life when the system is in storage, OSCEN must be set to '1'. This turns off the oscillator circuit, extending the battery life. If the OSCEN bit goes from disabled to enabled, it takes approximately one second (two seconds maximum) for the oscillator to start.

While system power is off, if the voltage on the backup supply ( $V_{RTCcap}$  or  $V_{RTCbat}$ ) falls below their respective minimum level, the oscillator may fail. The CY14B256KA has the ability to detect oscillator failure when system power is restored. This is recorded in the Oscillator Fail Flag (OSCF) of the flags register at the address 0x7FF0. When the device is powered on ( $V_{CC}$  goes above  $V_{SWITCH}$ ) the OSCEN bit is checked for the 'enabled' status. If the OSCEN bit is enabled and the oscillator is not active

within the first 5 ms, the OSCF bit is set to '1'. The system must check for this condition and then write '0' to clear the flag.

Note that in addition to setting the OSCF flag bit, the time registers are reset to the 'Base Time', which is the value last written to the timekeeping registers. The control or calibration registers and the OSCEN bit are not affected by the 'oscillator failed' condition.

The value of OSCF must be reset to '0' when the time registers are written for the first time. This initializes the state of this bit which may have become set when the system was first powered on.

To reset OSCF, set the write bit 'W' (in the flags register at 0x7FF0) to a '1' to enable writes to the flags register. Write a '0' to the OSCF bit and then reset the write bit to '0' to disable writes.

#### Calibrating the Clock

The RTC is driven by a quartz controlled crystal with a nominal frequency of 32.768 kHz. Clock accuracy depends on the quality of the crystal and calibration. The crystals available in market typically have an error of  $\pm 20$  ppm to  $\pm 35$  ppm. However, CY14B256KA employs a calibration circuit that improves the accuracy to  $\pm 1/-2$  ppm at 25 °C. This implies an error of  $\pm 2.5$  seconds to  $\pm 3$ 0 seconds per month.

The calibration circuit adds or subtracts counts from the oscillator divider circuit to achieve this accuracy. The number of pulses that are suppressed (subtracted, negative calibration) or split (added, positive calibration) depends upon the value loaded into the five calibration bits found in Calibration register at 0x7FF8. The calibration bits occupy the five lower order bits in the Calibration register. These bits are set to represent any value between '0' and 31 in binary form. Bit D5 is a sign bit, where a '1' indicates positive calibration and a '0' indicates negative calibration. Adding counts speeds the clock up and subtracting counts slows the clock down. If a binary '1' is loaded into the register, it corresponds to an adjustment of 4.068 or –2.034 ppm offset in oscillator error, depending on the sign.

Calibration occurs within a 64-minute cycle. The first 62 minutes in the cycle may, once every minute, have one second shortened by 128 or lengthened by 256 oscillator cycles. If a binary '1' is loaded into the register, only the first two minutes of the 64-minute cycle are modified. If a binary 6 is loaded, the first 12 are affected, and so on. Therefore, each calibration step has the effect of adding 512 or subtracting 256 oscillator cycles for every 125,829,120 actual oscillator cycles, that is, 4.068 or –2.034 ppm of adjustment per calibration step in the Calibration register.

To determine the required calibration, the CAL bit in the flags register (0x7FF0) must be set to '1'. This causes the INT pin to toggle at a nominal frequency of 512 Hz. Any deviation measured from the 512 Hz indicates the degree and direction of the required correction. For example, a reading of 512.01024 Hz indicates a +20 ppm error. Hence, a decimal value of -10 (001010b) must be loaded into the Calibration register to offset this error

**Note** Setting or changing the Calibration register does not affect the test output frequency.

To set or clear CAL, set the write bit 'W' (in the flags register at 0x7FF0) to '1' to enable writes to the flags register. Write a value to CAL, and then reset the write bit to '0' to disable writes.

#### Alarm

The alarm function compares user programmed values of alarm time and date (stored in the registers 0x7FF1-5) with the corresponding time of day and date values. When a match occurs, the alarm internal flag (AF) is set and an interrupt is generated on INT pin if Alarm Interrupt Enable (AIE) bit is set.

There are four alarm match fields – date, hours, minutes, and seconds. Each of these fields has a match bit that is used to determine if the field is used in the alarm match logic. Setting the match bit to '0' indicates that the corresponding field is used in the match process. Depending on the match bits, the alarm occurs as specifically as once a month or as frequently as once every minute. Selecting none of the match bits (all 1s) indicates that no match is required and therefore, alarm is disabled. Selecting all match bits (all 0s) causes an exact time and date match

There are two ways to detect an alarm event: by reading the AF flag or monitoring the INT pin. The AF flag in the flags register at 0x7FF0 indicates that a date or time match has occurred. The AF bit is set to '1' when a match occurs. Reading the flags register clears the alarm flag bit (and all others). A hardware interrupt pin may also be used to detect an alarm event.

To set, clear or enable an alarm, set the 'W' bit (in flags register -0x7FF0) to '1' to enable writes to Alarm Registers. After writing the alarm value, clear the 'W' bit back to '0' for the changes to take effect.

**Note** CY14B256KA requires the alarm match bit for seconds (bit 'D7' in Alarm-Seconds register 0x7FF2) to be set to '0' for proper operation of Alarm Flag and Interrupt..

### **Watchdog Timer**

The watchdog timer is a free running down counter that uses the 32 Hz clock (31.25 ms) derived from the crystal oscillator. The oscillator must be running for the watchdog to function. It begins counting down from the value loaded in the watchdog timer register.

The timer consists of a loadable register and a free running counter. On power-up, the watchdog time out value in register 0x7FF7 is loaded into the counter load register. Counting begins on power-up and restarts from the loadable value any time the watchdog strobe (WDS) bit is set to '1'. The counter is compared to the terminal value of '0'. If the counter reaches this value, it causes an internal flag and an optional interrupt output. You can prevent the time out interrupt by setting WDS bit to '1' prior to the counter reaching '0'. This causes the counter to reload with the watchdog time out value and to be restarted. As long as the user sets the WDS bit prior to the counter reaching the terminal value, the interrupt and WDT flag never occur.

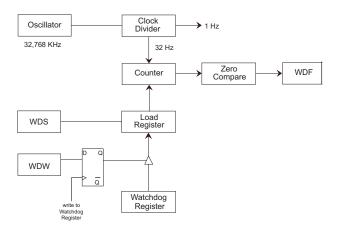

New time out values are written by setting the watchdog write bit to '0'. When the WDW is '0', new writes to the watchdog time out value bits D5–D0 are enabled to modify the time out value. When WDW is '1', writes to bits D5–D0 are ignored. The WDW function enables a user to set the WDS bit without concern that the watchdog timer value is modified. A logical diagram of the watchdog timer is shown in Figure 3. Note that setting the watchdog time out value to '0' disables the watchdog function.

The output of the watchdog timer is the flag bit WDF that is set if the watchdog is allowed to time out. If the watchdog interrupt enable (WIE) bit in the interrupt register is set, a hardware

interrupt on INT pin is also generated on watchdog timeout. The flag and the hardware interrupt are both cleared when user reads the flags register.

Figure 3. Watchdog Timer Block Diagram

#### **Power Monitor**

The CY14B256KA provides a power management scheme with power fail interrupt capability. It also controls the internal switch to backup power for the clock and protects the memory from low  $V_{CC}$  access. The power monitor is based on an internal band gap reference circuit that compares the  $V_{CC}$  voltage to  $V_{SWITCH}$  threshold.

As described in the AutoStore Operation on page 4, when  $V_{SWITCH}$  is reached as  $V_{CC}$  decays from power loss, a data STORE operation is initiated from SRAM to the nonvolatile elements, securing the last SRAM data state. Power is also switched from  $V_{CC}$  to the backup supply (battery or capacitor) to operate the RTC oscillator.

When operating from the backup source, read and write operations to nvSRAM are inhibited and the RTC functions are not available to the user. The RTC clock continues to operate in the background. The updated RTC time keeping registers data are available to the user after  $V_{CC}$  is restored to the device (see AutoStore/Power-Up RECALL on page 21).

#### Interrupts

The CY14B256KA has flags register, interrupt register and interrupt logic that can signal interrupt to the microcontroller. There are three potential sources for interrupt: watchdog timer, power monitor, and alarm timer. Each of these can be individually enabled to drive the INT pin by appropriate setting in the interrupt register (0x7FF6). In addition, each has an associated flag bit in the flags register (0x7FF0) that the host processor uses to determine the cause of the interrupt. The INT pin driver has two bits that specify its behavior when an interrupt occurs.

An interrupt is raised only if both a flag is raised by one of the three sources and the respective interrupt enable bit in interrupts register is enabled (set to '1'). After an interrupt source is active, two programmable bits, H/L and P/L, determine the behavior of the output pin driver on INT pin. These two bits are located in the interrupt register and can be used to drive level or pulse mode output from the INT pin. In pulse mode, the pulse width is

internally fixed at approximately 200 ms. This mode is intended to reset a host microcontroller. In the level mode, the pin goes to its active polarity until the flags register is read by the user. This mode is used as an interrupt to a host microcontroller. The control bits are summarized in the following section.

Interrupts are only generated while working on normal power and are not triggered when system is running in backup power mode.

**Note** CY14B256KA generates valid interrupts only after the Powerup RECALL sequence is completed. All events on INT pin must be ignored for t<sub>HRECALL</sub> duration after powerup.

#### Interrupt Register

**Watchdog Interrupt Enable (WIE).** When set to '1', the watchdog timer drives the INT pin and an internal flag when a watchdog time out occurs. When WIE is set to '0', the watchdog timer only affects the WDF flag in flags register.

**Alarm Interrupt Enable (AIE).** When set to '1', the alarm match drives the INT pin and an internal flag. When AIE is set to '0', the alarm match only affects the AF flag in flags register.

**Power Fail Interrupt Enable (PFE).** When set to '1', the power fail monitor drives the pin and an internal flag. When PFE is set to '0', the power fail monitor only affects the PF flag in flags register.

**High/Low (H/L)**. When set to a '1', the INT pin is active HIGH and the driver mode is push pull. The INT pin drives high only when  $V_{CC}$  is greater than  $V_{SWITCH}$ . When set to a '0', the INT pin is active LOW and the drive mode is open drain. The INT pin must be pulled up to Vcc by a 10 k resistor while using the interrupt in active LOW mode.

**Pulse/Level (P/L).** When set to a '1' and an interrupt occurs, the INT pin is driven for approximately 200 ms. When P/L is set to a '0', the INT pin is driven high or low (determined by H/L) until the flags register is read.

When an enabled interrupt source activates the INT pin, an external host reads the flags register to determine the cause. All flags are cleared when the register is read. If the INT pin is programmed for level mode, then the condition clears and the INT pin returns to its inactive state. If the pin is programmed for pulse mode, then reading the flag also clears the flag and the pin. The pulse does not complete its specified duration if the flags register is read. If the INT pin is used as a host reset, then the flags register is not read during a reset.

#### Flags Register

The flags register has three flag bits: WDF, AF, and PF, which can be used to generate an interrupt. These flags are set by the watchdog timeout, alarm match, or power fail monitor respectively. The processor can either poll this register or enable interrupts to be informed when a flag is set. These flags are automatically reset when the register is read. The flags register is automatically loaded with the value 0x00 on power-up (except for the OSCF bit; see Stopping and Starting the Oscillator on page 7).

WDF Watchdog Timer WIE P/L PF Power Pin Monitor INT PFE Driver VINT H/L Vss AF Clock Alarm AIE

Figure 4. Interrupt Block Diagram

WDF - Watchdog Timer Flag WIE - Watchdog Interrupt Enable

PF - Power Fail Flag

PFE - Power Fail Enable

AF - Alarm Flag

AIE - Alarm Interrupt Enable

P/L - Pulse Level

H/L - High/Low

# **RTC External Components**

The RTC requires connecting an external 32.768 kHz crystal and  $C_1$ ,  $C_2$  load capacitance as shown in the Figure 5. The figure shows the recommnded RTC external component values. The

load capacitances  $C_1$  and  $C_2$  are inclusive of parasitic of the printed circuit board (PCB). The PCB parasitic includes the capacitance due to land pattern of crystal pads/pins,  $X_{\text{in}}/X_{\text{out}}$  pads and copper traces connecting crystal and device pins.

Figure 5. RTC Recommended Component Configuration [5]

### Recommended Values

$Y_1 = 32.768 \text{ kHz } (12.5 \text{ pF})$   $C_1 = 10 \text{ pF}$  $C_2 = 67 \text{ pF}$

Note: The recommended values for C1 and C2 include board trace capacitance.

#### Note

<sup>5.</sup> For nonvolatile static random access memory (nvSRAM) real time clock (RTC) design guidelines and best practices, see application note AN61546.

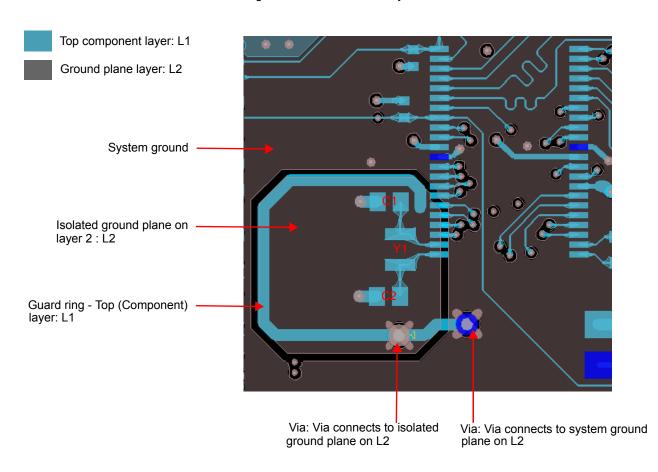

# PCB Design Considerations for RTC

RTC crystal oscillator is a low current circuit with high impedance nodes on their crystal pins. Due to lower timekeeping current of RTC, the crystal connections are very sensitive to noise on the board. Hence it is necessary to isolate the RTC circuit from other signals on the board.

It is also critical to minimize the stray capacitance on the PCB. Stray capacitances add to the overall crystal load capacitance and therefore cause oscillation frequency errors. Proper bypassing and careful layout are required to achieve the optimum RTC performance.

#### Layout requirements

The board layout must adhere to (but not limited to) the following guidelines during routing RTC circuitry. Following these guidelines help you achieve optimum performance from the RTC design.

It is important to place the crystal as close as possible to the X<sub>in</sub> and X<sub>out</sub> pins. Keep the trace lengths between the crystal and RTC equal in length and as short as possible to reduce the probability of noise coupling by reducing the length of the antenna.

- Keep X<sub>in</sub> and X<sub>out</sub> trace width lesser than 8 mils. Wider trace width leads to larger trace capacitance. The larger these bond pads and traces are, the more likely it is that noise can couple from adjacent signals.

- Shield the X<sub>in</sub> and X<sub>out</sub> signals by providing a guard ring around the crystal circuitry. This guard ring prevents noise coupling from neighboring signals.

- Take care while routing any other high speed signal in the vicinity of RTC traces. The more the crystal is isolated from other signals on the board, the less likely it is that noise is coupled into the crystal. Maintain a minimum of 200 mil separation between the X<sub>in</sub>, X<sub>out</sub> traces and any other high speed signal on the board.

- No signals should run underneath crystal components on the same PCB layer.

Create an isolated solid copper plane on adjacent PCB layer and underneath the crystal circuitry to prevent unwanted noise coupled from traces routed on the other signal layers of the PCB. The local plane should be separated by at least 40 mils from the neighboring plane on the same PCB layer. The solid plane should be in the vicinity of RTC components only and its perimeter should be kept equal to the guard ring perimeter. Figure 6 shows the recommended layout for RTC circuit.

Figure 6. Recommended Layout for RTC

Table 3. RTC Register Map [6, 7]

| Register   |              |             |                 | BCD Format Data <sup>[6]</sup> |           |                |          | Function/Dance   |                            |

|------------|--------------|-------------|-----------------|--------------------------------|-----------|----------------|----------|------------------|----------------------------|

| CY14B256KA | D7           | D6          | D5              | D4                             | D3        | D2             | D1       | D0               | - Function/Range           |

| 0x7FFF     |              | 10s y       | ears            |                                |           | Ye             | ears     |                  | Years: 00-99               |

| 0x7FFE     | 0            | 0           | 0               | 10s<br>months                  |           | Мс             | nths     |                  | Months: 01–12              |

| 0x7FFD     | 0            | 0           | 10s day         | of month                       |           | Day o          | f month  |                  | Day of month: 01–31        |

| 0x7FFC     | 0            | 0           | 0               | 0                              | 0         |                | Day of w | reek             | Day of week: 01–07         |

| 0x7FFB     | 0            | 0           | 10s             | hours                          |           | Н              | ours     |                  | Hours: 00-23               |

| 0x7FFA     | 0            | •           | 10s minut       | tes                            |           | Mir            | nutes    |                  | Minutes: 00–59             |

| 0x7FF9     | 0            | 10s seconds |                 |                                |           | Sec            | onds     |                  | Seconds: 00-59             |

| 0x7FF8     | OSCEN<br>(0) | 0           | Cal<br>sign (0) |                                | Calib     | ration (00     | 0000)    |                  | Calibration values [8]     |

| 0x7FF7     | WDS (0)      | WDW (0)     |                 | 1                              | WDT (0    | 00000)         |          |                  | Watchdog <sup>[8]</sup>    |

| 0x7FF6     | WIE (0)      | AIE (0)     | PFE (0)         | 0                              | H/L (1)   | P/L (0)        | 0        | 0                | Interrupts [8]             |

| 0x7FF5     | M (1)        | 0           | 10s ala         | arm date                       |           | Alar           | m day    |                  | Alarm, Day of month: 01–31 |

| 0x7FF4     | M (1)        | 0           | 10s ala         | rm hours                       |           | Alarn          | n hours  |                  | Alarm, hours: 00-23        |

| 0x7FF3     | M (1)        | 10s         | alarm mi        | inutes                         |           | Alarm          | minutes  |                  | Alarm, minutes: 00-59      |

| 0x7FF2     | M (1)        | 10s         | alarm se        | conds                          |           | Alarm, seconds |          |                  | Alarm, seconds: 00–59      |

| 0x7FF1     |              | 10s cer     | nturies         |                                | Centuries |                |          | Centuries: 00–99 |                            |

| 0x7FF0     | WDF          | AF          | PF              | OSCF <sup>[9]</sup>            | 0         | CAL<br>(0)     | W (0)    | R (0)            | Flags <sup>[8]</sup>       |

The unused bits of RTC registers are reserved for future use and should be set to '0'.

() designates values shipped from the factory.

This is a binary value, not a BCD value.

When the user resets OSCF flag bit, the flags register will be updated after t<sub>RTCp</sub> time.

Table 4. Register Map Detail

| Register<br>Y14B256KA |                                                                                                                                                                                                                                        |                  |                  | Descri                                       | ption                                                                                                             |                 |                 |              |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|--------------|--|

|                       | Time Keeping - Years                                                                                                                                                                                                                   |                  |                  |                                              |                                                                                                                   |                 |                 |              |  |

| 0x7FFF                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       |                                                                                                                                                                                                                                        | 10s              | s years          | 1                                            |                                                                                                                   | Ye              | ears            |              |  |

|                       | Contains the lower two BCD digits of the year. Lower nibble (four bits) contains the value for years; upper (four bits) contains the value for 10s of years. Each nibble operates from 0 to 9. The range for the register is           |                  |                  |                                              |                                                                                                                   |                 |                 |              |  |

|                       | (lour bits) co                                                                                                                                                                                                                         | intains the valu | 103 01 908       | Time Keepin                                  | -                                                                                                                 | 10 10 3. 1110 1 | ange for the re | gister is 0— |  |

| 0x7FFE                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      | 0                | 0                | 10s month                                    |                                                                                                                   |                 | onths           |              |  |

|                       | Contains the                                                                                                                                                                                                                           | BCD digits of    | the month. Lo    | wer nibble (four                             |                                                                                                                   | s the lower di  | git and operat  |              |  |

|                       | upper Hibble                                                                                                                                                                                                                           | (One bit) con    | airis trie upper |                                              |                                                                                                                   | i. The range    | ioi the registe | 115 1-12.    |  |

| 0x7FFD                | D7                                                                                                                                                                                                                                     | D6               | D5               | Time Keep                                    | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      |                  |                  |                                              | บง                                                                                                                |                 |                 | D0           |  |

|                       | _                                                                                                                                                                                                                                      | 0                | -                | of month                                     | :  -  -   - /f                                                                                                    |                 | of month        |              |  |

|                       | from 0 to 9;                                                                                                                                                                                                                           | upper nibble (   |                  | ins the 10s digit                            | rer nibble (four bits) contains the lower digit and operagit and operates from 0 to 3. The range for the register |                 |                 |              |  |

| 07550                 | Time Keeping - Day                                                                                                                                                                                                                     |                  |                  |                                              |                                                                                                                   |                 |                 |              |  |

| 0x7FFC                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      | 0                | 0                | 0                                            | 0                                                                                                                 |                 | Day of week     |              |  |

|                       |                                                                                                                                                                                                                                        | rom 1 to 7 the   |                  | e that correlates The user must a Time Keepi | issign meanin                                                                                                     |                 |                 |              |  |

| 0x7FFB                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      | 0                | 10s              | hours                                        |                                                                                                                   | Н               | ours            |              |  |

|                       |                                                                                                                                                                                                                                        |                  |                  | ur format. Lowe<br>ins the upper di          |                                                                                                                   |                 |                 |              |  |

| 0x7FFA                |                                                                                                                                                                                                                                        |                  |                  | Time Keepin                                  | g - Minutes                                                                                                       |                 |                 |              |  |

| VATITA                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      |                  | 10s minutes      |                                              |                                                                                                                   | Mir             | nutes           |              |  |

|                       | Contains the BCD value of minutes. Lower nibble (four bits) contains the lower digit and operates from 0 to 9 upper nibble (three bits) contains the upper minutes digit and operates from 0 to 5. The range for the register is 0–59. |                  |                  |                                              |                                                                                                                   |                 |                 |              |  |

| 0.7550                |                                                                                                                                                                                                                                        |                  |                  | Time Keeping                                 | g - Seconds                                                                                                       |                 |                 |              |  |

| 0x7FF9                | D7                                                                                                                                                                                                                                     | D6               | D5               | D4                                           | D3                                                                                                                | D2              | D1              | D0           |  |

|                       | 0                                                                                                                                                                                                                                      |                  | 10s seconds      |                                              |                                                                                                                   | Sec             | conds           |              |  |

|                       |                                                                                                                                                                                                                                        |                  |                  | ver nibble (four<br>per digit and ope        |                                                                                                                   |                 |                 |              |  |

Table 4. Register Map Detail (continued)

| Register<br>CY14B256KA | Description                                    |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |                                            |                                     |                  |                  |                    |  |  |

|------------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------------------------------|-------------------------------------|------------------|------------------|--------------------|--|--|

|                        | Calibration/Control                            |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          |                                            |                                     |                  |                  |                    |  |  |

| 0x7FF8                 | D7                                             | D6                                                                                                                                                                                                                                                                                                                                                                                                | D5                                                                       | D4                                         | D3                                  | D2               | D1               | D0                 |  |  |

|                        | OSCEN                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                 | Calibration sign                                                         |                                            |                                     | Calibration      |                  |                    |  |  |

| OSCEN                  |                                                | Oscillator Enable. When set to '1', the oscillator is stopped. When set to '0', the oscillator runs. Disabling the oscillator saves battery or capacitor power during storage.                                                                                                                                                                                                                    |                                                                          |                                            |                                     |                  |                  |                    |  |  |

| Calibration Sign       | Determines i                                   | f the calibratio                                                                                                                                                                                                                                                                                                                                                                                  | n adjustment is                                                          | applied as an a                            | addition (1) to                     | or as a subtra   | ction (0) from   | the time-base      |  |  |

| Calibration            | These five b                                   | its control the                                                                                                                                                                                                                                                                                                                                                                                   | calibration of th                                                        | ie clock.                                  |                                     |                  |                  |                    |  |  |

| 07557                  |                                                |                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                          | WatchDo                                    | g Timer                             |                  |                  |                    |  |  |

| 0x7FF7                 | D7                                             | D6                                                                                                                                                                                                                                                                                                                                                                                                | D5                                                                       | D4                                         | D3                                  | D2               | D1               | D0                 |  |  |

|                        | WDS                                            | WDW                                                                                                                                                                                                                                                                                                                                                                                               |                                                                          |                                            | WE                                  | T                | I                | ı                  |  |  |

| WDS                    |                                                |                                                                                                                                                                                                                                                                                                                                                                                                   | his bit to '1' relo<br>ically after the                                  |                                            |                                     |                  |                  |                    |  |  |