# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

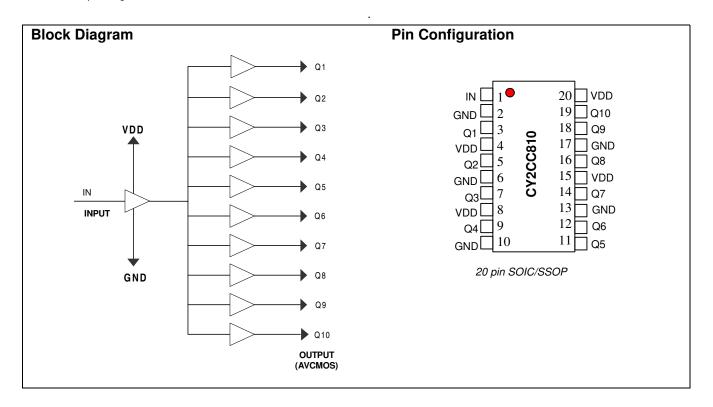

# CY2CC810

# 1:10 Clock Fanout Buffer

#### Features

- · Low-voltage operation

- V<sub>DD</sub> range from 2.5V to 3.3V

- 1:10 fanout

- · Over voltage tolerant input hot swappable

- Drives either a 50-Ohm or 75-Ohm transmission line

- · Low-input capacitance

- · 250 ps typical output-to-output skew

- 19 ps typical DJ jitter

- Typical propagation delay < 3.5 ns

- High-speed operation > 500 MHz

- · Industrial versions available

- · Available packages include: SOIC, SSOP

#### Description

The Cypress series of network circuits are produced using advanced 0.35-micron CMOS technology, achieving the industry's fastest logic and buffers.

The Cypress CY2CC810 fanout buffer features one input and ten outputs. Designed for data communications clock management applications, the large fanout from a single input reduces loading on the input clock.

AVCMOS-type outputs dynamically adjust for variable impedance matching and reduce noise overall.

#### Pin Description

| Pin Number                         | Pin Name        | Descr        | iption |

|------------------------------------|-----------------|--------------|--------|

| 1                                  | IN              | Input        | LVCMOS |

| 2, 6, 10, 13, 17                   | GND             | Ground       | Power  |

| 4, 8, 15, 20                       | V <sub>DD</sub> | Power Supply | Power  |

| 3, 5, 7, 9, 11, 12, 14, 16, 18, 19 | Q1 Q10          | Output       | AVCMOS |

٠

Cypress Semiconductor Corporation Document #: 38-07056 Rev. \*E 198 Champion Court • San Jose, CA 95134-1709 • 408-943-2600 Revised September 5, 2006

# Absolute Maximum Conditions<sup>[1, 2]</sup>

| Parameter        | Description                               | Min. | Max.               | Unit |

|------------------|-------------------------------------------|------|--------------------|------|

| V <sub>DD</sub>  | V <sub>DD</sub> Ground Supply voltage     | -0.5 | 4.6                | V    |

| V <sub>IN</sub>  | Input Supply Voltage to Ground Potential  | -0.5 | 5.8                | V    |

| V <sub>OUT</sub> | Output Supply Voltage to Ground Potential | -0.5 | V <sub>DD</sub> +1 | V    |

| Τ <sub>S</sub>   | Temperature, Storage                      | -65  | 150                | °C   |

| T <sub>A</sub>   | Temperature, Operating Ambient            | -40  | 85                 | °C   |

|                  | Power Dissipation                         | 0.7  | '5                 | W    |

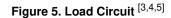

#### DC Electrical Characteristics @ 3.3V (see Figure 5)

| Parameter        | Description              | Conditions                                       | Conditions                 |     | Тур. | Max. | Unit |

|------------------|--------------------------|--------------------------------------------------|----------------------------|-----|------|------|------|

| V <sub>OH</sub>  | Output High Voltage      | $V_{DD}$ = Min., $V_{IN}$ = $V_{IH}$ or $V_{IL}$ | $I_{OH} = -12 \text{ mA}$  | 2.3 | 3.3  |      | V    |

| V <sub>OL</sub>  | Output Low Voltage       | $V_{DD}$ = Min., $V_{IN}$ = $V_{IH}$ or $V_{IL}$ | I <sub>OL</sub> = 12 mA    |     | 0.2  | 0.5  | V    |

| V <sub>IH</sub>  | Input High Voltage       | Guaranteed Logic High Level                      |                            | 2   |      | 5.8  | V    |

| V <sub>IL</sub>  | Input Low Voltage        | Guaranteed Logic Low Level                       | Guaranteed Logic Low Level |     |      | 0.8  | V    |

| I <sub>IH</sub>  | Input High Current       | $V_{DD} = Max.$ $V_{IN} = 2.7V$                  |                            |     |      | 1    | μA   |

| IIL              | Input Low Current        | V <sub>DD</sub> = Max.                           | $V_{IN} = 0.5V$            |     |      | -1   | μA   |

| l <sub>l</sub>   | Input High Current       | $V_{DD} = Max., V_{IN} = V_{DD}(Max.)$           |                            |     |      | 20   | μA   |

| V <sub>IK</sub>  | Clamp Diode Voltage      | $V_{DD} = Min., I_{IN} = -18 \text{ mA}$         |                            |     | -0.7 | -1.2 | V    |

| I <sub>OK</sub>  | Continuous Clamp Current | V <sub>DD</sub> = Max., V <sub>OUT</sub> = GND   |                            |     |      | -50  | mA   |

| O <sub>OFF</sub> | Power down Disable       | $V_{DD} = GND, V_{OUT} = < 4.5V$                 |                            |     |      | 100  | μA   |

| V <sub>H</sub>   | Input Hysteresis         | $V_{DD}$ = Min., $V_{IN}$ = $V_{IH}$ or $V_{IL}$ |                            |     | 80   |      | mV   |

# DC Electrical Characteristics @ 2.5V (see Figure 1)

| Parameter        | Description              | Conditions                                          |                          | Min. | Тур. | Max. | Unit |

|------------------|--------------------------|-----------------------------------------------------|--------------------------|------|------|------|------|

| V <sub>OH</sub>  | Output High Voltage      | $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | $I_{OH} = -7 \text{ mA}$ | 1.8  |      |      | V    |

|                  |                          |                                                     | I <sub>OH</sub> = 12 mA  | 1.6  |      |      | V    |

| V <sub>OL</sub>  | Output Low Voltage       | $V_{DD} = Min., V_{IN} = V_{IH} \text{ or } V_{IL}$ | I <sub>OL</sub> = 12 mA  |      |      | 0.65 | V    |

| V <sub>IH</sub>  | Input High Voltage       | Guaranteed Logic High Level                         |                          | 1.6  |      | 5.0  | V    |

| V <sub>IL</sub>  | Input Low Voltage        | Guaranteed Logic Low Level                          |                          |      |      | 0.8  | V    |

| I <sub>IH</sub>  | Input High Current       | V <sub>DD</sub> = Max.                              | V <sub>IN</sub> = 2.4V   |      |      | 1    | μΑ   |

| IIL              | Input Low Current        | V <sub>DD</sub> = Max.                              | V <sub>IN</sub> = 0.5V   |      |      | -1   | μΑ   |

| l                | Input High Current       | $V_{DD} = Max., V_{IN} = V_{DD}(Max.)$              |                          |      |      | 20   | μΑ   |

| V <sub>IK</sub>  | Clamp Diode Voltage      | $V_{DD} = Min., I_{IN} = -18 \text{ mA}$            |                          |      | -0.7 | -1.2 | V    |

| I <sub>OK</sub>  | Continuous Clamp Current | V <sub>DD</sub> = Max., V <sub>OUT</sub> = GND      |                          |      |      | -50  | mA   |

| O <sub>OFF</sub> | Power-down Disable       | $V_{DD} = GND, V_{OUT} = < 4.5V$                    |                          |      |      | 100  | μΑ   |

| V <sub>H</sub>   | Input Hysteresis         |                                                     |                          |      | 80   |      | mV   |

# Capacitance

| Parameter | ter Description Test Conditions |                       | Min. | Тур. | Max. | Unit |

|-----------|---------------------------------|-----------------------|------|------|------|------|

| Cin       | Input Capacitance               | V <sub>IN</sub> = 0V  |      | 2.5  |      | pF   |

| Cout      | Output Capacitance              | V <sub>OUT</sub> = 0V |      | 6.5  |      | pF   |

Note

1. Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device. This is intended to be a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

<sup>2.</sup> Multiple Supplies: The voltage on any input or I/O pin cannot exceed the power pin during power-up. Power supply sequencing is NOT required.

# Power Supply Characteristics (see Figure 5)

| Parameter       | Description                                             | Test Conditions                                                                                      | Min. | Тур. | Max. | Unit       |

|-----------------|---------------------------------------------------------|------------------------------------------------------------------------------------------------------|------|------|------|------------|

| $\Delta_{ICC}$  | Delta I <sub>CC</sub> Quiescent Power<br>Supply Current | $(I_{DD} @ V_{DD} = Max. and V_{IN} = V_{DD}) - (I_{DD} @ V_{DD} = Max. and V_{IN} = V_{DD} - 0.6V)$ |      |      | 50   | μA         |

| ICCD            | Dynamic Power Supply<br>Current                         | V <sub>DD</sub> = Max.<br>Input toggling 50% Duty Cycle, Outputs Open                                |      |      | 0.63 | mA/<br>MHz |

| I <sub>C</sub>  | Total Power Supply Current                              | V <sub>DD</sub> = Max.<br>Input toggling 50% Duty Cycle, Outputs Open<br>fL = 40 MHZ                 |      |      | 25   | mA         |

| t <sub>PU</sub> | Power-up time for all $V_{DD}$ s                        | Power-up to reach minimum specified voltage (power ramp must be monotonic)                           | 0.05 |      | 500  | ms         |

# **High-frequency Parametrics**

| Parameter              | Description                                  | Test Conditions                                                                                               |              | Min. | Тур. | Max. | Unit |

|------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------|------|------|------|------|

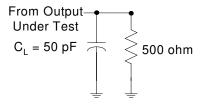

| DJ                     | Jitter, Deterministic                        | 50% duty cycle t <sub>W</sub> (50–50)                                                                         | 2.5V         |      | 23   | 35   | ps   |

|                        |                                              | The "point to point load circuit"<br>Output Jitter – Input Jitter                                             | 3.3V         |      | 19   | 30   | ps   |

| F <sub>max(3.3V)</sub> | Maximum frequency<br>V <sub>DD</sub> = 3.3V  | 50% duty cycle t <sub>W</sub> (50–50)<br>Standard Load Circuit.                                               | See Figure 5 |      |      | 160  | MHz  |

|                        |                                              | 50% duty cycle t <sub>W</sub> (50–50)<br>The "point to point load circuit"                                    | See Figure 7 |      |      | 650  |      |

| F <sub>max(2.5V</sub>  | Maximum frequency<br>V <sub>DD</sub> = 2.5 V | The "point to point load circuit" See Figure 7 $V_{IN} = 2.4V/0.0V V_{OUT} = 1.7V/0.7V$                       |              |      |      | 200  | MHz  |

| F <sub>max(20)</sub>   | Maximum frequency<br>V <sub>DD</sub> = 3.3 V | 20% duty cycle $t_W$ (20–80)<br>The "point to point load circuit"<br>$V_{IN} = 3.0V/0.0V V_{OUT} = 2.3V/0.4V$ | See Figure 7 |      |      | 250  | MHz  |

|                        | Maximum frequency<br>V <sub>DD</sub> = 2.5 V | The "point to point load circuit"<br>$V_{IN} = 2.4V/0.0V V_{OUT} = 1.7V/0.7V$                                 | See Figure 3 |      |      | 200  | MHz  |

| tw                     | Minimum pulse<br>V <sub>DD</sub> = 3.3 V     | The "point to point load circuit"<br>$V_{IN} = 3.0V/0.0V F = 100 MHz$<br>$V_{OUT} = 2.0V/0.8V$                | See Figure 7 | 1    |      |      | ns   |

|                        | Minimum pulse<br>V <sub>DD</sub> = 2.5 V     | The "point to point load circuit"<br>$V_{IN} = 2.4V/0.0V F = 100 MHz$<br>$V_{OUT} = 1.7V/0.7V$                | See Figure 3 | 1    |      |      |      |

# AC Switching Characteristics @ 3.3V, $V_{DD}$ = 3.3V ±5%, Temperature = -40°C to +85°C

| Parameter          | Description                                                                                                              | Min.          | Тур. | Max. | Unit |      |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|------|------|------|------|

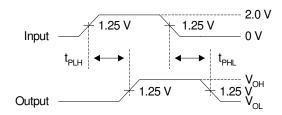

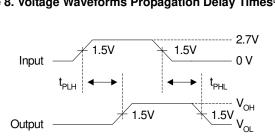

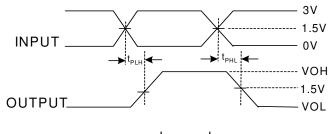

| t <sub>PLH</sub>   | Propagation Delay – Low to High                                                                                          | See Figure 4  | 1.5  | 2.7  | 3.5  | ns   |

| t <sub>PHL</sub>   | Propagation Delay – High to Low                                                                                          |               | 1.5  | 2.7  | 3.5  | ns   |

| t <sub>R</sub>     | Output Rise Time                                                                                                         |               |      | 0.8  |      | V/ns |

| t <sub>F</sub>     | Output Fall Time                                                                                                         |               |      | 0.8  |      | V/ns |

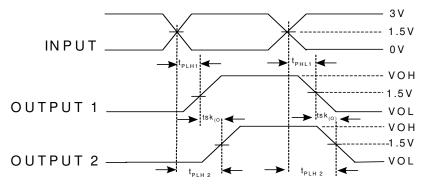

| t <sub>SK(0)</sub> | Output Skew: Skew between outputs of the same package (in phase)                                                         | See Figure 10 |      | 0.25 | 0.38 | ns   |

| t <sub>SK(p)</sub> | Pulse Skew: Skew between opposite transitions of the same output $(t_{PHL} - t_{PLH})$ .                                 | See Figure 9  |      |      | 0.2  | ns   |

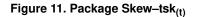

| t <sub>SK(t)</sub> | Package Skew: Skew between outputs of different packages at the same power supply voltage, temperature and package type. | See Figure 11 |      |      | 0.42 | ns   |

#### AC Switching Characteristics @ 2.5V, $V_{DD}$ = 2.5V ±5%, Temperature = -40°C to +85°C

| Parameter          | Description                                                                                                              |               | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------------------------------------------------------------------------------------------------------|---------------|------|------|------|------|

| t <sub>PLH</sub>   | Propagation Delay – Low to High                                                                                          | See Figure 4  | 1.5  | 2.0  | 3.5  | ns   |

| t <sub>PHL</sub>   | Propagation Delay – High to Low                                                                                          |               | 1.5  | 2.0  | 3.5  | ns   |

| t <sub>R</sub>     | Output Rise Time                                                                                                         |               |      | 0.8  |      | V/ns |

| t <sub>F</sub>     | Output Fall Time                                                                                                         |               |      | 0.8  |      | V/ns |

| t <sub>SK(0)</sub> | Output Skew: Skew between outputs of the same package (in phase)                                                         | See Figure 10 |      | 0.25 | 0.38 | ns   |

| t <sub>SK(p)</sub> | Pulse Skew: Skew between opposite transitions of the same output See Figure 9 $(t_{PHL} - t_{PLH})$ .                    |               |      |      | 0.4  | ns   |

| t <sub>SK(t)</sub> | Package Skew: Skew between outputs of different packages at the same power supply voltage, temperature and package type. | See Figure 11 |      |      | 0.65 | ns   |

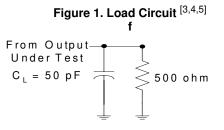

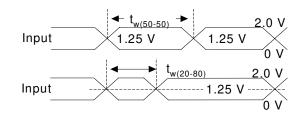

# Parameter Measurement Information: V<sub>DD</sub> @ 2.5V

#### Figure 2. Voltage Waveforms Pulse Duration<sup>[6]</sup>

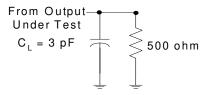

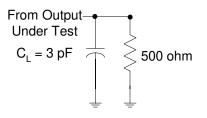

#### Figure 3. Point to Point Load Circuit<sup>[3,4,5]</sup>

#### Notes

- 3.  $C_L$  includes probe and jig capacitance.

- 4. All input pulses are supplied by generators having the following characteristics: PRR < 100 MHz,  $Z_0 = 50W$ ,  $t_R < 2.5$  nS,  $t_F < 2.5$  nS.

- 5. The outputs are measured one at a time with one transition per measurement.

- 6.  $T_{PLH}$  and  $T_{PHL}$  are the same as  $t_{pd}$ .

#### Figure 4. Voltage WaveformsPropagation Delay Times<sup>[4]</sup>

# Parameter Measurement Information: V<sub>DD</sub> @ 3.3V

#### Figure 6. Voltage Waveforms–Pulse Duration<sup>[6]</sup>

Figure 8. Voltage Waveforms Propagation Delay Times<sup>[4]</sup>

# Figure 9. Pulse Skew-tsk<sub>(p)</sub>

$tsk_{(P)} = It_{PHL} - t_{PLH}I$

$tsk_{(P)} = It_{PLH2} - t_{PLH1} I \text{ or } t_{PHL2} - t_{PHL1} I$

$\mathsf{tsk}_{(t)} = \mathbf{I} \mathbf{t}_{\mathsf{PLH2}} - \mathbf{t}_{\mathsf{PLH1}} \mathbf{I} \text{ or } \mathbf{t}_{\mathsf{PHL2}} - \mathbf{t}_{\mathsf{PHL1}} \mathbf{I}$

# **Ordering Information**

| Part Number  | Package Type              | Product Flow              |

|--------------|---------------------------|---------------------------|

| CY2CC810OI   | 20-pin SSOP               | Industrial, -40°C to 85°C |

| CY2CC810OIT  | 20-pin SSOP–Tape and Reel | Industrial, -40°C to 85°C |

| CY2CC810OC   | 20-pin SSOP               | Commercial, 0°C to 70°C   |

| CY2CC810OCT  | 20-pin SSOP–Tape and Reel | Commercial, 0°C to 70°C   |

| Lead-free    |                           |                           |

| CY2CC810OXC  | 20-pin SSOP               | Commercial, 0°C to 70°C   |

| CY2CC810OXCT | 20-pin SSOP–Tape and Reel | Commercial, 0°C to 70°C   |

| CY2CC810OXI  | 20-pin SSOP               | Industrial, -40°C to 85°C |

| CY2CC810OXIT | 20-pin SSOP–Tape and Reel | Industrial, -40°C to 85°C |

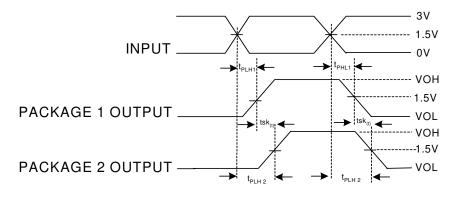

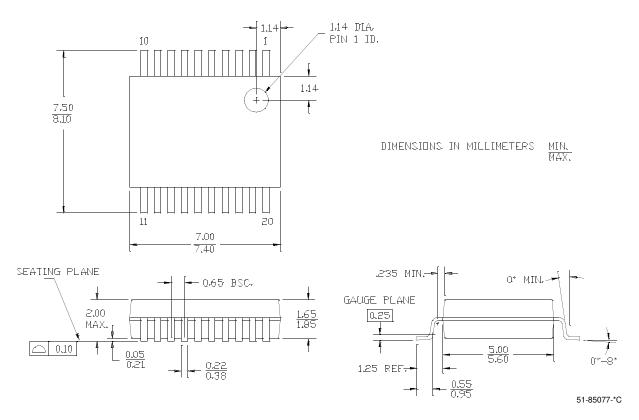

# **Package Drawing and Dimensions**

All product and company names mentioned in this document are the trademarks of their respective holders.

#### Document #: 38-07056 Rev. \*E

© Cypress Semiconductor Corporation, 2006. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

# **Document History Page**

|      | Document Title: CY2CC810 1:10 Clock Fanout Buffer<br>Document #: 38-07056 |            |                    |                                                                                                                                                                                                   |  |  |  |

|------|---------------------------------------------------------------------------|------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| REV. | ECN NO.                                                                   | Issue Date | Orig. of<br>Change | Description of Change                                                                                                                                                                             |  |  |  |

| **   | 107081                                                                    | 06/07/01   | IKA                | Convert from IMI to Cypress                                                                                                                                                                       |  |  |  |

| *A   | 114315                                                                    | 05/09/02   | TSM                | $\Delta I_{DD}$ Validation                                                                                                                                                                        |  |  |  |

| *В   | 119117                                                                    | 10/07/02   | RGL                | Added 5.8 as the Max. value of $V_{IH}$ in the DC Electrical Characteristics @3.3V table.<br>Changed the Max. value of $V_{IH}$ from 1.8 to 5.0 in the DC Electrical Characteristics @2.5V table. |  |  |  |

| *C   | 122743                                                                    | 12/14/02   | RBI                | Added power up requirements to maximum ratings information.                                                                                                                                       |  |  |  |

| *D   | 387761                                                                    | See ECN    | RGL                | Added typical values<br>Updated jitter and skew specs.<br>Removed devices with SOIC package<br>Added Lead-free SSOP package                                                                       |  |  |  |

| *E   | 499991                                                                    | See ECN    | RGL                | Added tpu parameter in the Power Supply Characteristics table                                                                                                                                     |  |  |  |