Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# LVPECL Voltage Controlled Crystal Oscillator (VCXO)

#### **Features**

- High-frequency VCXO with LVPECL output

- Any output frequency from 50 MHz to 690 MHz

- Available either factory configured or field programmable

- Integrated phase-locked loop (PLL)

- 1 ps typical RMS Phase Jitter

- Output Enable or Power-down function

- Supply voltage: 3.3 V or 2.5 V

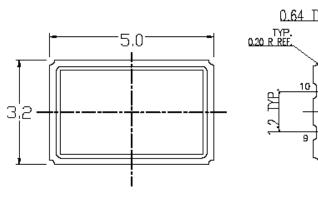

- Pb-free package: 5.0 × 3.2 mm LCC

- Commercial and industrial temperature ranges

#### **Benefits**

- Eliminates the need for external crystal

- Low-noise internal PLL

- Fast time to market

- Suitable for HDDs, consumer and networking applications

- Small footprint

- Application compatibility in standard and low-power systems

- Field-programmable for reduced inventory

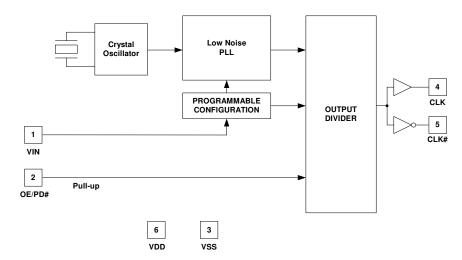

## **Logic Block Diagram**

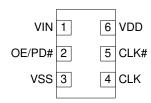

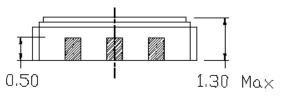

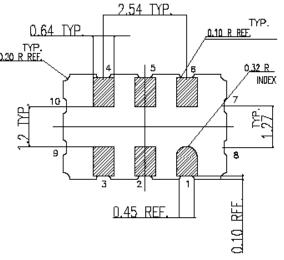

#### **Pinouts**

Figure 1. 6-Pin Ceramic LCC

#### **Pin Definitions**

| Pin  | Name            | I/O Type                     | Description                                                                                                                                                              |

|------|-----------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | V <sub>IN</sub> | Analog Input                 | VCXO control voltage. Positive slope.                                                                                                                                    |

| 2    | OE/PD#          | CMOS Input, internal pull-up | Output Enable pin: Active HIGH. If OE = 1, CLK is enabled. Power-down pin: Active LOW. If PD# = 0, Power-down is enabled. The functionality of this pin is programmable. |

| 3    | V <sub>SS</sub> | Power                        | Power supply ground                                                                                                                                                      |

| 4, 5 | CLK, CLK#       | Output                       | Clock output. LVPECL outputs. CLK# is the complement of CLK.                                                                                                             |

| 6    | $V_{DD}$        | Power                        | Positive power supply: 2.5 V or 3.3 V                                                                                                                                    |

### **Functional Description**

The CY2V014 is a high-performance high-frequency voltage-controlled crystal oscillator (VCXO).

The device uses a Cypress proprietary low-noise PLL to synthesize the frequency from an embedded crystal.

The output frequency is user adjustable by means of an analog control voltage applied to the  $V_{\text{IN}}$  pin.

## VCXO Control Voltage (V<sub>IN</sub>, pin 1)

$V_{IN}$  is an analog input that is used to adjust the output frequency. The nominal output frequency is defined when  $V_{IN} = V_{DD}/2$ . Increasing the voltage on  $V_{IN}$  increases the output frequency, while decreasing the voltage on  $V_{IN}$  decreases the output frequency. Any voltage between  $V_{SS}$  and  $V_{DD}$  is allowed on  $V_{IN}$ . The voltage/frequency slope is very linear over most of the control voltage range.

## **Programming Description**

#### Field-Programmable CY2V014

Field-programmable devices are shipped unprogrammed, and must be programmed before use. Customers can use Cyber-Clocks™ Online Software to specify the device configuration and generate a .JED programming file. Programming of samples and prototype quantities is available using the CY3672 programmer. Third-party vendors manufacture programmers for small to large volume applications. Cypress's value-added distribution partners also provide programming services. Field-programmable devices are designated with an "F" in the part number, and are intended for quick prototyping and inventory reduction.

#### Factory-Configured CY2V014

For customers wanting ready-to-use devices, the CY2V014 is available factory-configured, with no programming required. All requests must be submitted to the local Cypress Field Application Engineer (FAE) or sales representative. Once the request has been processed, you will receive a new part number, samples, and data sheet with the programmed values. This part number will be used for additional sample requests and production orders.

#### **Programming Variables**

#### **Output Frequency**

Any frequency between 50 MHz and 690 MHz may be specified.

#### **Absolute Pull Range**

The absolute pull range (APR) may be specified.

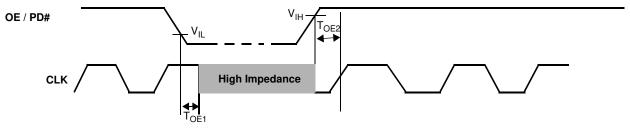

#### Pin 2: Output Enable or Power-Down (OE/PD#)

Pin 2 can be programmed as either output enable (OE) or Power-down (PD#). The OE function is used to enable or disable the CLK output very quickly, but it does not reduce core power consumption. The PD# function puts the device into a low-power state, but wake-up takes longer because the PLL must reacquire lock.

## **Absolute Maximum Conditions**

| Parameter          | Description                       | Condition                   | Min         | Max                  | Unit |

|--------------------|-----------------------------------|-----------------------------|-------------|----------------------|------|

| V <sub>CC</sub>    | Supply Voltage                    |                             | -0.5        | 4.4                  | V    |

| V <sub>IN</sub>    | Input Voltage                     | Relative to V <sub>SS</sub> | -0.5        | V <sub>DD</sub> +0.5 | VDC  |

| $T_S$              | Temperature, Storage              | Non Functional              | <b>–</b> 55 | 150                  | °C   |

| $T_J$              | Temperature, Junction             |                             | -40         | 125                  | °C   |

| ESD <sub>HBM</sub> | ESD Protection (Human Body Model) | MIL-STD-883, Method 3015    | 2000        |                      | V    |

| UL-94              | Flammability Rating               | At 1/8 in.                  | V-          | -0                   |      |

| MSL                | Moisture Sensitivity Level        |                             | -           | 1                    |      |

Note: The voltage on any input or I/O pin cannot exceed the power pin during power-up.

## **Operating Conditions**

| Parameter       | Description                                                                                                     | Min         | Тур        | Max         | Unit |

|-----------------|-----------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|------|

| $V_{DD}$        | Supply Voltage Range                                                                                            | 3.0<br>2.25 | 3.3<br>2.5 | 3.6<br>2.75 | V    |

| T <sub>PU</sub> | Power-up Time for $V_{\mbox{\scriptsize DD}}$ to Reach Minimum Specified Voltage (power ramp must be monotonic) | 0.05        | _          | 500         | ms   |

| T <sub>A</sub>  | Ambient Temperature (Commercial)                                                                                | 0           | _          | 70          | °C   |

| T <sub>A</sub>  | Ambient Temperature (Industrial)                                                                                | -40         | _          | 85          | °C   |

## **DC Electrical Characteristics**

| Parameter         | Description                                                                 | Condition                                                                                                      | Min                    | Тур | Max                        | Unit |

|-------------------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------------------------|-----|----------------------------|------|

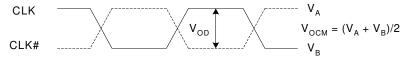

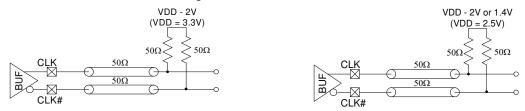

| V <sub>OH</sub>   | LVPECL High Output Voltage                                                  | $V_{DD}$ = 3.3 V or 2.5 V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0 V                                        | V <sub>DD</sub> – 1.15 | -   | V <sub>DD</sub> –<br>0.75  | V    |

| V <sub>OL</sub>   | LVPECL Low Output Voltage                                                   | $V_{DD}$ = 3.3 V or 2.5 V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0 V                                        | V <sub>DD</sub> – 2.0  | -   | V <sub>DD</sub> –<br>1.625 | V    |

| V <sub>OD1</sub>  | LVPECL Output Voltage Swing (V <sub>OH</sub> – V <sub>OL</sub> )            | $V_{DD}$ = 3.3 V or 2.5 V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 2.0 V                                        | 600                    | -   | 1000                       | mV   |

| V <sub>OD2</sub>  | LVPECL Output Voltage Swing (V <sub>OH</sub> – V <sub>OL</sub> )            | $V_{DD}$ = 2.5 V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ – 1.4 V                                                 | 500                    | -   | 1000                       | mV   |

| V <sub>OCM</sub>  | LVPECL Output Common Mode<br>Voltage (V <sub>OH</sub> + V <sub>OL</sub> )/2 | $V_{DD}$ = 2.5 V, $R_{TERM}$ = 50 $\Omega$ to $V_{DD}$ - 1.4 V                                                 | 1.2                    | -   | _                          | V    |

| $V_{IH}$          | CMOS Input High Voltage                                                     |                                                                                                                | $0.7 \times V_{DD}$    | -   | _                          | V    |

| $V_{IL}$          | CMOS Input Low Voltage                                                      |                                                                                                                | _                      | _   | $0.3 \times V_{DD}$        | V    |

| R <sub>UP</sub>   | Internal Pull-up Resistor                                                   |                                                                                                                | _                      | 100 | _                          | kΩ   |

| I <sub>IH</sub>   | CMOS Input High Current                                                     | $V_{IN} = V_{DD}$                                                                                              | _                      | -   | 10                         | μΑ   |

| I <sub>IL</sub>   | CMOS Input Low Current                                                      | $V_{IN} = V_{SS}$                                                                                              | _                      | -   | 120                        | μΑ   |

| $V_{VIN}$         | V <sub>IN</sub> Input Voltage                                               |                                                                                                                | 0                      | _   | $V_{DD}$                   | V    |

| I <sub>IVIN</sub> | V <sub>IN</sub> Input Current                                               | $V_{SS} \le V_{IN} \le V_{DD}$                                                                                 | _                      | -   | 10                         | μΑ   |

| L <sub>IN</sub>   | V <sub>IN</sub> to f <sub>OUT</sub> Linearity                               | $0.2 \times V_{DD} \le V_{IN} \le 0.8 \times V_{DD}$                                                           | _                      | 1   | _                          | %    |

| l <sub>OZ</sub>   | Output Leakage Current                                                      | Three-state output, PD#/OE = $V_{SS}$                                                                          | -35                    | -   | 35                         | μА   |

| I <sub>DD</sub>   | Operating Supply Current                                                    | $V_{DD} = 3.3 \text{ V or } 2.5 \text{ V, CLK} = 150 \text{ MHz,}$<br>$C_{LOAD} = 0, \text{ PD\#/OE} = V_{DD}$ | _                      | _   | 100                        | mA   |

| I <sub>SB</sub>   | Standby Supply Current                                                      | PD# = V <sub>SS</sub>                                                                                          | _                      | -   | 1                          | mΑ   |

Document #: 001-06458 Rev. \*B

## **AC Electrical Characteristics**

| Parameter                       | Description Condition                                 |                                                                                                                               | Min         | Тур | Max      | Unit |

|---------------------------------|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------|-----|----------|------|

| f <sub>OUT</sub>                | Output Frequency                                      |                                                                                                                               | 50          | _   | 690      | MHz  |

| FS <sub>FACT</sub>              | Frequency Stability – factory programmed devices      | $V_{IN} = V_{DD}/2^{[1]}$                                                                                                     | -60         | -   | 60       | ppm  |

| FS <sub>FIELD</sub>             | Frequency Stability – field program-<br>mable devices | $V_{IN} = V_{DD}/2^{[1]}$                                                                                                     | -100        | -   | 100      | ppm  |

| APR                             | Absolute Pull Range                                   | $V_{IN} = V_{DD}$ to $V_{SS}$ , relative to nominal $f_{OUT}$ , across operating temperature and voltage range <sup>[2]</sup> | ±100<br>±50 | -   | <u> </u> | ppm  |

| BW                              | Modulation Bandwidth (V <sub>IN</sub> )               | –3 dB                                                                                                                         | 10          | _   | _        | kHz  |

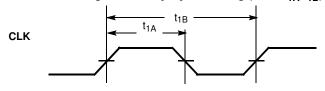

| DC                              | Output Duty Cycle                                     | Measured at zero crossing                                                                                                     | 45          | 50  | 55       | %    |

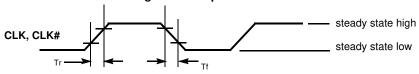

| T <sub>R</sub> , T <sub>F</sub> | Output Rise and Fall Time                             | 20% and 80% of full output swing                                                                                              | _           | 350 | _        | ps   |

| T <sub>OE1</sub>                | Output Disable Time                                   | Time from falling edge on OE to stopped outputs (Asynchronous)                                                                | _           | _   | 100      | ns   |

| T <sub>OE2</sub>                | Output Enable Time                                    | Time from rising edge on OE to outputs at a valid frequency (Asynchronous)                                                    | _           | _   | 100      | ns   |

| T <sub>LOCK</sub>               | Start-up Time                                         | Time for CLK to reach valid frequency measured from the time $V_{DD}$ = $V_{DD}$ (Min) or from PD# rising edge.               | _           | _   | 10       | ms   |

| T <sub>J1</sub>                 | RMS Phase Jitter                                      | f <sub>OUT</sub> = 106.25 MHz (12 kHz–20 MHz)                                                                                 | _           | 1   | _        | ps   |

| T <sub>J2</sub>                 | Peak-to-peak Period Jitter                            | f <sub>OUT</sub> = 106.25 MHz                                                                                                 | _           | 30  | _        | ps   |

## Notes

Frequency stability is the maximum variation in frequency from F<sub>0</sub>. It includes initial accuracy, plus variation from temperature, supply voltage, shock, vibration and first year aging.

APR is the minimum pull range under all conditions over the device lifetime, including aging for 10 years. APR is relative to F<sub>0</sub>.

## **Switching Waveforms**

Figure 2. Duty Cycle Timing (DC =  $t_{1A}/t_{1B}$ )

Figure 3. Output Differential Voltage

Figure 4. Output Rise/Fall Time

Output Rise time (Tr) =20 to 80% of full output swing Output Fall time (Tf) = 80 to 20% of full output swing

Figure 5. Output Enable/Disable Timing

## **Termination Circuits**

Figure 6. LVPECL Termination

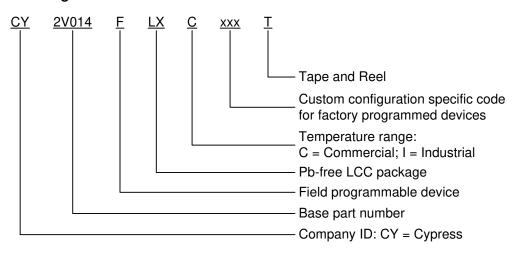

## Ordering Information

Table 1 lists the CY2V014 key package features and ordering codes. The table contains only the parts that are currently available. If you do not see what you are looking for, contact your local sales representative. For more information, visit the Cypress website at www.cypress.com and refer to the product summary page at http://www.cypress.com/products.

Table 1. Key Features and Ordering Information

| Part Number Configuration       |                    | Package description                   | Product Flow                |  |

|---------------------------------|--------------------|---------------------------------------|-----------------------------|--|

| Pb-free                         |                    |                                       |                             |  |

| CY2V014FLXCT                    | Field programmable | 6-Pin Ceramic LCC SMD – Tape and Reel | Commercial, 0 °C to 70 °C   |  |

| CY2V014FLXIT Field programmable |                    | 6-Pin Ceramic LCC SMD – Tape and Reel | Industrial, –40 °C to 85 °C |  |

#### **Possible Configurations**

Some product offerings are factory programmed customer specific devices with customized part numbers. The Possible Configurations table shows the available device types, but not complete part numbers. Contact your local Cypress FAE of Sales Representative for more information.

| Part Number <sup>[3]</sup> Configuration |                    | Package description                   | Product Flow                |  |

|------------------------------------------|--------------------|---------------------------------------|-----------------------------|--|

| Pb-free                                  |                    |                                       |                             |  |

| CY2V014LXCxxxT                           | Factory configured | 6-Pin Ceramic LCC SMD – Tape and Reel | Commercial, 0 °C to 70 °C   |  |

| CY2V014LXIxxxT Factory configured 6      |                    | 6-Pin Ceramic LCC SMD – Tape and Reel | Industrial, -40 °C to 85 °C |  |

## **Ordering Code Defintions**

#### Note

<sup>3. &</sup>quot;xxx" is a factory assigned code that identifies the programming option.

## **Package Diagram**

Figure 7. 6-Pin 3.2 × 5.0 mm Ceramic LCC LZ06A

001-10044 \*A

## **Acronyms**

Table 2. Acronyms Used in this Document

| Acronym | Description                             |

|---------|-----------------------------------------|

| CMOS    | complementary metal oxide semiconductor |

| ESD     | electro-static discharge                |

| FAE     | field applications engineer             |

| HDD     | hard disk drive                         |

| LCC     | leadless chip carrier                   |

| PLL     | phase-locked loop                       |

| RMS     | root mean square                        |

| SMD     | surface mount device                    |

| VCXO    | voltage-controlled crystal oscillator   |

## **Document Conventions**

#### **Units of Measure**

Table 3. Units of Measure

| Symbol | Unit of Measure   |  |  |

|--------|-------------------|--|--|

| °C     | degree celcius    |  |  |

| KHz    | kilo hertz        |  |  |

| ΚΩ     | kilo ohm          |  |  |

| MHz    | mega hertz        |  |  |

| μΑ     | micro ampere      |  |  |

| mA     | milli ampere      |  |  |

| ms     | milli second      |  |  |

| mV     | milli volt        |  |  |

| ns     | nano second       |  |  |

| Ω      | ohm               |  |  |

| ppm    | parts per million |  |  |

| %      | percent           |  |  |

| ps     | pico second       |  |  |

| V      | volt              |  |  |

## **Document History Page**

| Document Title: CY2V014 LVPECL Voltage Controlled Crystal Oscillator (VCXO) Document Number: 001-06458 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

|--------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Revision                                                                                               | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| **                                                                                                     | 504458  | RGL                | See ECN            | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| *A                                                                                                     | 2899939 | CXQ                | 03/26/10           | Updated ordering information table. Updated package diagram. Updated copyright section.                                                                                                                                                                                                                                                                                                                                                                                               |  |

| *B                                                                                                     | 3099970 | CXQ                | 12/02/10           | Updated template and styles. Changed from Preliminary to Final. Added Acronyms, Units of Measure, and Ordering Code Definitions sections. Changed 700 MHz to 690 MHz in second "Features" bullet. Changed from 700 MHz to 690 MHz in "Programming Variables" section Changed fOUT spec in AC specifications table from 700 max to 690 max. Changed FSfact in AC specifications from +/-60 ppm max to -60ppm min and 60 ppm max. Changed FSfield spec to -100 ppm min and 100 ppm max. |  |

## Sales, Solutions, and Legal Information

#### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

#### **Products**

Automotive

Clocks & Buffers

Interface

Lighting & Power Control

Memory

Optical & Image Sensing

PSoC

Touch Sensing

USB Controllers

Wireless/RF

cypress.com/go/automotive cypress.com/go/clocks cypress.com/go/interface cypress.com/go/powerpsoc

cypress.com/go/plc cypress.com/go/memory cypress.com/go/image cypress.com/go/psoc cypress.com/go/touch cypress.com/go/USB cypress.com/go/wireless

#### **PSoC Solutions**

psoc.cypress.com/solutions PSoC 1 | PSoC 3 | PSoC 5

© Cypress Semiconductor Corporation, 2006-2010. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

Document #: 001-06458 Rev. \*B

Revised December 2, 2010

Page 9 of 9

CyberClocks is a trademark of Cypress Semiconductor Corporation. All other products and company names mentioned in this document may be the trademarks of their respective holders