Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## CY3275

# Cypress Low Voltage Programmable Powerline Communication Development Kit Guide

Doc. # 001-53657 Rev. \*C

Cypress Semiconductor 198 Champion Court San Jose, CA 95134-1709

Phone (USA): 800.858.1810 Phone (Intnl): 408.943.2600 http://www.cypress.com

#### Copyrights

© Cypress Semiconductor Corporation, 2009-2011. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in a Cypress product. Nor does it convey or imply any license under patent or other rights. Cypress products are not warranted nor intended to be used for medical, life support, life saving, critical control or safety applications, unless pursuant to an express written agreement with Cypress. Furthermore, Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress products in life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Any Source Code (software and/or firmware) is owned by Cypress Semiconductor Corporation (Cypress) and is protected by and subject to worldwide patent protection (United States and foreign), United States copyright laws and international treaty provisions. Cypress hereby grants to licensee a personal, non-exclusive, non-transferable license to copy, use, modify, create derivative works of, and compile the Cypress Source Code and derivative works for the sole purpose of creating custom software and or firmware in support of licensee product to be used only in conjunction with a Cypress integrated circuit as specified in the applicable agreement. Any reproduction, modification, translation, compilation, or representation of this Source Code except as specified above is prohibited without the express written permission of Cypress.

Disclaimer: CYPRESS MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATE-RIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. Cypress reserves the right to make changes without further notice to the materials described herein. Cypress does not assume any liability arising out of the application or use of any product or circuit described herein. Cypress does not authorize its products for use as critical components in life-support systems where a malfunction or failure may reasonably be expected to result in significant injury to the user. The inclusion of Cypress' product in a life-support systems application implies that the manufacturer assumes all risk of such use and in doing so indemnifies Cypress against all charges.

Use may be limited by and subject to the applicable Cypress software license agreement.

PSoC® is a registered trademark of Cypress Semiconductor Corporation. All products and company names mentioned in this document may be the trademarks of their respective holders.

Purchase of I2C components from Cypress or one of its sublicensed Associated Companies conveys a license under the Philips I2C Patent Rights to use these components in an I2C system, provided that the system conforms to the I2C Standard Specification as defined by Philips. As from October 1st, 2006 Philips Semiconductors has a new trade name - NXP Semiconductors.

#### Flash Code Protection

Cypress products meet the specifications contained in their particular Cypress PSoC Data Sheets. Cypress believes that its family of PSoC products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

# Contents

| 1. | introdu     | ction                                            | 5  |

|----|-------------|--------------------------------------------------|----|

|    | 1.1         | Using the PLC Kit                                | 5  |

|    | 1.2         | The Cypress PLC Solution                         | 5  |

|    | 1.3         | Kit Contents                                     | 7  |

|    | 1.4         | Additional Learning Resources                    | 8  |

|    | 1.5         | Document Revision History                        | 8  |

|    | 1.6         | Documentation Conventions                        |    |

|    |             |                                                  |    |

| 2. | Getting     | Started                                          | 9  |

|    | 2.1         | Kit Installation                                 |    |

|    | 2.2         | PSoC Designer                                    |    |

|    | 2.3         | PSoC Programmer                                  |    |

|    | 2.4         | Software Installation                            | 15 |

|    |             | 2.4.1 Before You Begin                           | 15 |

|    |             | 2.4.2 Prerequisites                              | 15 |

|    |             | 2.4.3 Installing PLC Control Panel Software      | 15 |

| _  | <b>5.</b> 6 |                                                  |    |

| 3. | PLC LV      | Development Board                                | 17 |

|    | 3.1         | Features                                         |    |

|    | 3.2         | PLC Development Board Functional Overview        |    |

|    |             | 3.2.1 Operating Conditions                       |    |

|    | 3.3         | Hardware Description                             |    |

|    |             | 3.3.1 Development                                |    |

|    |             | 3.3.1.1 User I/Os, Bread Board, and GPIO Headers |    |

|    |             | 3.3.1.2 CY8CPLC20 Device                         |    |

|    |             | 3.3.1.3 Potentiometer and DIP Switches           |    |

|    |             | 3.3.2 LCD Daughter Card                          |    |

|    |             | 3.3.3 Debugger                                   |    |

|    |             | 3.3.4 RS-232 COM Port                            |    |

|    |             | 3.3.5 Power Supply Circuit                       | 24 |

|    |             | 3.3.6 Transmit Amplifier and Receive Filter      | 24 |

|    |             | 3.3.7 Low Voltage Coupling Circuit               | 25 |

|    | 3.4         | Code Example                                     | 26 |

|    | 3.5         | Technical Reference                              | 26 |

|    | A           | B                                                | 07 |

| Α. | Append      |                                                  | 27 |

|    | A.1         | Schematics                                       |    |

|    |             | A.1.1 Board Overview                             |    |

|    |             | A.1.2 User Interface                             |    |

|    |             | A.1.3 Transmit and Receive Filter Coupling       |    |

|    |             | A.1.4 Power Supply                               |    |

|    | A.2         | Layout                                           | 31 |

#### Contents

| A.2.1 | Top Layer                                 | .31             |

|-------|-------------------------------------------|-----------------|

|       |                                           |                 |

| A.2.3 | Power Layer                               | .33             |

|       |                                           |                 |

| A.2.5 | Top Silkscreen                            | .35             |

|       |                                           |                 |

|       |                                           |                 |

|       | A.2.2<br>A.2.3<br>A.2.4<br>A.2.5<br>A.2.6 | A.2.1 Top Layer |

## 1. Introduction

#### 1.1 Using the PLC Kit

Cypress's Powerline Communication (PLC) solution makes it possible to transmit command and control data over high-voltage and low-voltage powerlines. This solution is developed for low bandwidth powerline communication.

The CY3275 low-voltage (LV) PLC development kit provides the capability to develop an application on the Cypress CY8CPLC20 device that can transmit and receive data over low voltage (12 V to 24 V AC/DC) powerlines.

- Chapter 1 provides a brief overview of the Cypress PLC solution. It describes the contents of the development kit and lists its special features.

- Chapter 2 describes how to install and configure the PLC LV board.

- Chapter 3 gives the functional overview and describes the operating procedure of the PLC LV board. It provides a high-level hardware description of the board.

- The Appendix provides the schematics, layout, and bill of materials.

#### 1.2 The Cypress PLC Solution

Powerlines are available everywhere in the world. This makes them one of the most widely available communication media. The pervasiveness of powerlines also makes it difficult to predict their characteristics and noise. Because of the variability of powerline quality, implementing robust communication over powerline has been an engineering challenge for years. With this in mind, the Cypress PLC solution is designed to enable secure, reliable, and robust communication over powerlines. The key features of the Cypress PLC solution are:

- An integrated powerline PHY modem with optimized amplifiers that work with rugged high and low voltage powerlines

- Powerline optimized network protocol that supports bidirectional communication with acknowledgement based signaling and multiple retries

- Support for 8-bit packet CRC and 4-bit header CRC for error detection and data packet retransmission

- Carrier Sense Multiple Access (CSMA) scheme that minimizes collisions between packet transmissions on the powerline

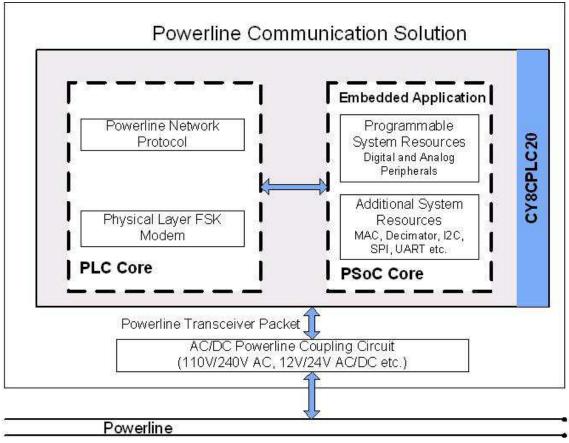

The Cypress PLC solution consists of three key elements, as shown in Figure 1-1.

- Powerline network protocol layer

- Physical layer FSK modem

- Power amplification and coupling circuits

Figure 1-1. Cypress PLC Solution Block Diagram

The powerline network protocol layer and the physical layer FSK modem are implemented on the CY8CPLC20 chip. The CY3275 board contains the CY8CPLC20 device along with the power amplification and coupling circuit for communicating on low voltage (12 V–24 V AC/DC) powerlines. For a detailed description of the circuit design parameters, see application note AN55427, Cypress Powerline Communication Board Design Analysis.

The network protocol layer allows addressing of multiple nodes on the network. This enables point-to-multipoint communication. The protocol layer also provides a defined packet structure for transmitting data packets from one node to the other as well as error detection and packet retransmit functions.

The chip also contains a PSoC® core in addition to the PLC core. The PSoC core includes configurable blocks of analog and digital logic as well as programmable interconnects. This architecture allows to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast CPU, flash program memory, SRAM data memory, and configurable I/Os are included.

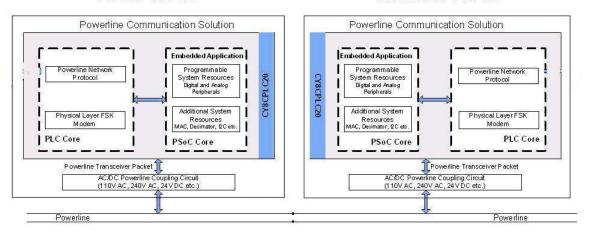

Figure 1-2 shows a two node system level diagram. To evaluate this kit, follow the steps in the quick start guide, which is provided in the kit.

**Note** To evaluate this kit, a second low voltage PLC kit is required. The compatible kits are CY3275 (this kit) and CY3273 Low Voltage PLC Evaluation Kit. For more information, visit <a href="http://www.cypress.com/go/CY3275">http://www.cypress.com/go/CY3275</a> and <a href="http://www.cypress.com/go/CY3275">http://www.cypress.com/go/CY3275</a> and <a href="http://www.cypress.com/go/CY3275">http://www.cypress.com/go/CY3275</a>.

Figure 1-2. PLC System Level Block Diagram - Two Nodes

#### Local Node

#### Remote Node

#### 1.3 Kit Contents

The CY3275 LV PLC Development Kit contains:

- CY3275 LV PLC development board

- CY3275 quick start guide

- CD-ROM containing:

- □ Packet test software PLC Control Panel application

- PLC Control Panel release notes

- □ CY3275 release notes

- □ CY8CPLC20 data sheet

- CY3275 development kit user guide

- CY3275 board Altium design project

- CY3275 board schematics, layout, and BOM

- □ Application note Using CY8CPLC20 in Powerline Communication (PLC) Applications

- □ PSoC Designer™

- PSoC Programmer

- 12 V DC power supply

- MiniProg1 to program the CY8CPLC20 device

- 25 jumper wires

- LCD module

- USB-I2C bridge

- Retractable USB cable

- Daisy chain cable

- Five CY8CPLC20-28PVXI SSOP device samples

#### 1.4 Additional Learning Resources

Visit <a href="http://www.cypress.com/go/plc">http://www.cypress.com/go/plc</a> for additional learning resources in the form of data sheets, technical reference manuals, and application notes.

- CY3275 Schematic.pdf: http://www.cypress.com/go/CY3275

- CY3275 Board Layout.zip: http://www.cypress.com/go/CY3275

- CY3275 Kit documentation: http://www.cypress.com/go/CY3275

- For a list of PSoC Designer-related trainings, see http://www.cypress.com/?rID=40543

- CY8CPLC20 data sheet: http://www.cypress.com/?rID=38201

- For more information regarding PSoC Designer functionality and releases, refer to the user guide and release notes on the PSoC Designer web page: http://www.cypress.com/go/psocdesigner

- For more information regarding PSoC Programmer, supported hardware, and COM layer, go to the PSoC Programmer web page: http://www.cypress.com/go/psocprogrammer

- AN54416, Using CY8CPLC20 in Powerline Communication (PLC) Applications http://www.cypress.com/?rID=37951

#### 1.5 Document Revision History

Table 1-1. Revision History

| Revision | PDF Creation<br>Date | Origin of Change | Description of Change                                                                                                                                                                                                                                                           |

|----------|----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| **       | 08/14/09             | IUS              | Initial release.                                                                                                                                                                                                                                                                |

| *A       | 09/03/09             | IUS              | Rework for external release.                                                                                                                                                                                                                                                    |

| *B       | 12/10/09             | RARP             | Content updates                                                                                                                                                                                                                                                                 |

| *C       | 08/04/11             | FRE              | Added references to the compatible low voltage PLC kits. Added a reference to the quick start guide for evaluation. Added clarifications to the text throughout the document. Removed reference to CY3277 and CY8CLED16P01. Updated section 1.4. Added Getting Started section. |

#### 1.6 Documentation Conventions

Table 1-2. Document Conventions for Guides

| Convention         | Usage                                                                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Courier New        | Displays file locations, user entered text, and source code: C:\cd\icc\                                                             |

| Italics            | Displays file names and reference documentation: Read about the <i>sourcefile.hex</i> file in the <i>PSoC Designer User Guide</i> . |

| [Bracketed, Bold]  | Displays keyboard commands in procedures: [Enter] or [Ctrl] [C]                                                                     |

| File > Open        | Represents menu paths:<br>File > Open > New Project                                                                                 |

| Bold               | Displays commands, menu paths, and icon names in procedures:<br>Click the <b>File</b> icon and then click <b>Open</b> .             |

| Times New Roman    | Displays an equation: $2 + 2 = 4$                                                                                                   |

| Text in gray boxes | Describes Cautions or unique functionality of the product.                                                                          |

# 2. Getting Started

This chapter describes how to install and configure the CY3275-LV PLC Development Kit.

#### 2.1 Kit Installation

To install the kit software, follow these steps:

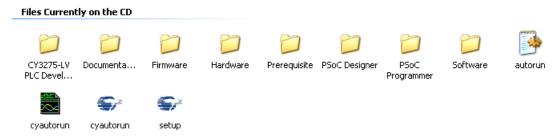

- 1. Insert the kit CD into the CD drive of your PC. The CD is designed to auto-run and the Kit Installer Startup screen appears.

- 2. Click **Install CY3275 Low Voltage PLC Kit** to start the installation, as shown in Figure 2-1.

**Note** If auto-run does not execute, double-click the *cyautorun.exe* file on the root directory of the CD, as shown in Figure 2-2.

Figure 2-2. Root Directory of CD

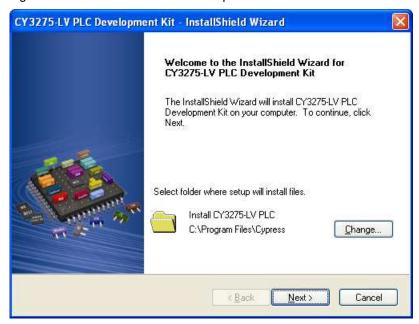

- The CY3275-LV PLC Development Kit InstallShield Wizard screen appears. Choose the folder location to install the setup files. You can change the location of the folder using **Change**, as shown in Figure 2-3.

- 4. Click **Next** to launch the kit installer.

Figure 2-3. CY3275-LV PLC Development Kit - InstallShield Wizard

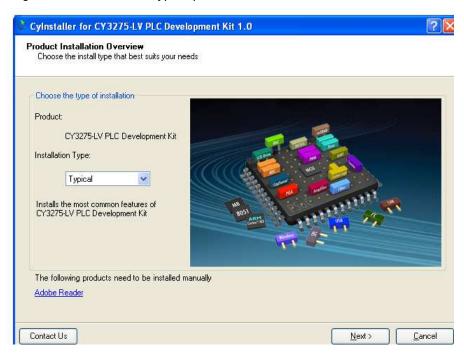

- 5. On the Product Installation Overview screen, select the installation type that best suits your requirement. The drop-down menu has the options **Typical**, **Complete**, and **Custom**, as shown in Figure 2-4.

- 6. Click **Next** to start the installation.

Figure 2-4. Installation Type Options

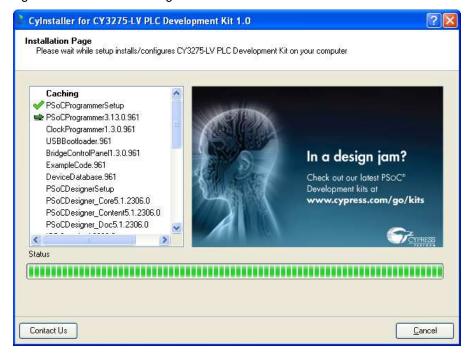

- 7. When the installation begins, a list of all packages appears on the Installation page.

- 8. A green check mark appears adjacent to every package that is downloaded and installed, as shown in Figure 2-5.

- 9. Wait until all the packages are downloaded and installed successfully.

Figure 2-5. Installation Page

10. Click Finish to complete the installation, as shown in Figure 2-6.

Figure 2-6. Installation Completion Page

#### 2.2 PSoC Designer

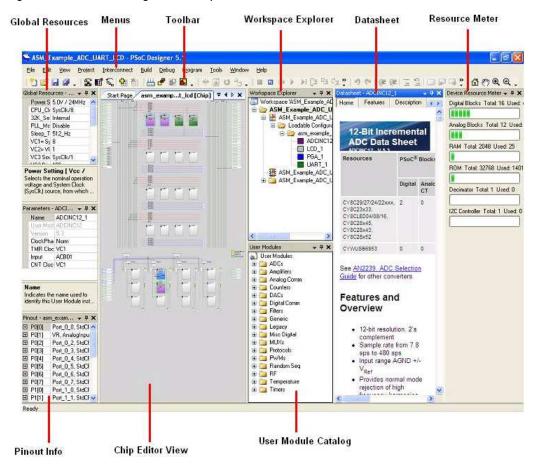

- 1. Click Start > All Programs > Cypress > PSoC Designer <version> > PSoC Designer <version>.

- 2. Click **File > New Project** to create a new project on the PSoC Designer menu or go to **File > Open Project/Workspace** to work with an existing project.

Figure 2-7. PSoC Designer Workspace

3. For more details on PSoC Designer, go to **Help Topics** from the following directory:

<Install\_Dir>:\Cypress\PSoC Designer\<version>\PSoC Designer 5\Help\

PSoCDesigner (Compiled HTML Help file)

#### 2.3 PSoC Programmer

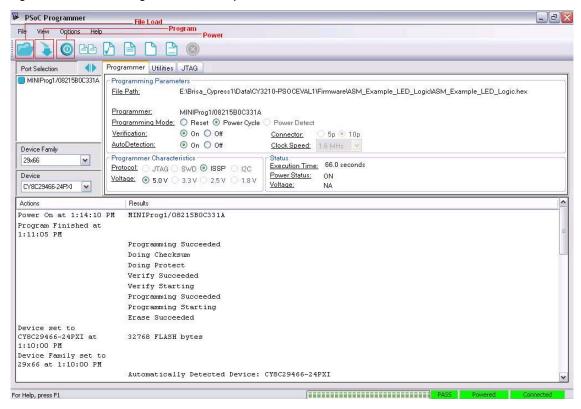

- 1. Click Start > All Programs > Cypress > PSoC Programmer <version> > PSoC Programmer <version>.

- 2. Connect the MiniProg from **Port Selection**, as shown in Figure 2-8.

Figure 2-8. PSoC Programmer Workspace

- 3. Click the File Load button to load the hex file.

- 4. Use the **Program** button to program the hex file on to the chip.

- 5. When the file is successfully programmed, 'Programming Succeeded' appears on the Actions pane.

- 6. Close PSoC Programmer.

**Note** For more details on PSoC Programmer, go to Help Topics from the following path: <Install\_Dir>:\Cypress\Programmer\<version>\PSoC\_Programmer Compiled HTML Help file.

#### 2.4 Software Installation

#### 2.4.1 Before You Begin

All Cypress software installations require administrator privileges; but this is not required to run the installed software.

- 1. Shut down any Cypress software that is currently running.

- 2. Disconnect any Cypress devices (USB-I2C bridge, ICE Cube, or MiniProg) from your computer.

#### 2.4.2 Prerequisites

The PLC Control Panel GUI requires the latest versions of Microsoft .NET Framework, Adobe Acrobat Reader, and a Windows Installer. If your computer does not have .NET Framework and Windows Installer, the installation automatically installs them. However, if your computer does not have Adobe Acrobat Reader, download and install it from the Adobe website.

#### 2.4.3 Installing PLC Control Panel Software

The PLC Control Panel GUI is installed as a prerequisite when you install the CY3275-LV PLC Development kit. Follow the steps shown on the screen to complete the installation.

To reinstall this application, select **Install PLC Control Panel GUI** from the installation screen, as shown in Figure 2-1.

Click Start > All Programs > Cypress > PLC Control Panel > PLC Control Panel.

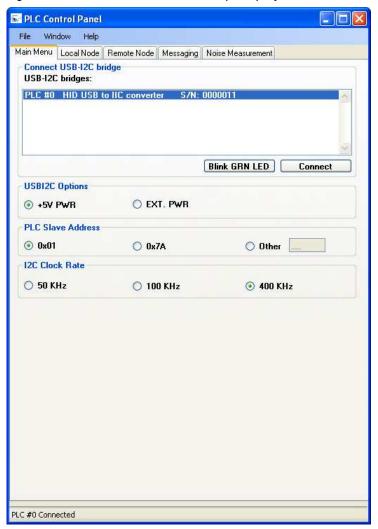

The PLC Control Panel application controls the CY3275-LV PLC Development Kit over USB interface from a PC. The application's startup display, when a board is attached and operating, is shown in the following figure.

Figure 2-9. PLC Control Panel Startup Display

After installing PLC Control Panel, refer to the required documentation at the following location:

- <CD Drive>:\Software\PLC Control Panel\PLC Control Panel Release Notes.pdf

- <CD Drive>:\Software\PLC Control Panel\User Guide for Cypress PLC Control Panel GUI.pdf

The PLC Control Panel user guide is also available in the installation directory. It contains additional information about installation and how to set up the kit to work with the GUI. It can also be accessed from the Help menu in the PLC Control Panel GUI.

# 3. PLC LV Development Board

This chapter explains the key features of the CY3275-LV development board.

#### 3.1 Features

The Cypress CY3275-LV CY8CPLC20 development board is a versatile tool with the following features:

- User friendly PLC Control Panel application available on the kit CD-ROM

- Chip power supply derived from 12 V to 24 V AC/DC

- CY8CPLC20-OCD chip 100-pin TQFP on chip debug (OCD) device that allows quick design and debug of PLC applications. The CY8CPLC20 100-pin TQFP is available for debug purposes only. For production quantities, CY8CPLC20 is available in 28-pin SSOP and 48-pin QFN packages

- User configurable general purpose LEDs

- General purpose 8-position DIP switch

- RJ-45 connector to use ICE debugger

- RS-232 COM port for serial communication

- Header to attach the LCD card

- I<sup>2</sup>C header for communicating to external devices

- ISSP header for programming the CY8CPLC20 chip

#### 3.2 PLC Development Board Functional Overview

The PLC development board is designed as a development platform for low bandwidth (up to 2400 bps) powerline communication applications.

The application on CY8CPLC20 generates the data. The PLC core encapsulates this data into a PLC network packet. The FSK modern modulates this packet and the coupling circuitry incorporates the resulting sinusoidal waveform onto the existing waveform on the low voltage bus.

#### 3.2.1 Operating Conditions

Input voltage: 12 V/24 V AC/DCInput current: 200 mA/150 mA

Operating temperature: 0 °C to 40 °C

Operating humidity condition: 5% to 95% RH, non-condensing

**Note** The board's ground reference is directly connected to the '-' input of the power. If the line voltage is AC, the same polarity should be maintained when connecting the boards (same as DC). This will prevent any potential shorts that may occur if the polarities are swapped and the PLC kits are connected to equipment that share the same ground reference (for example, a PC).

#### 3.3 Hardware Description

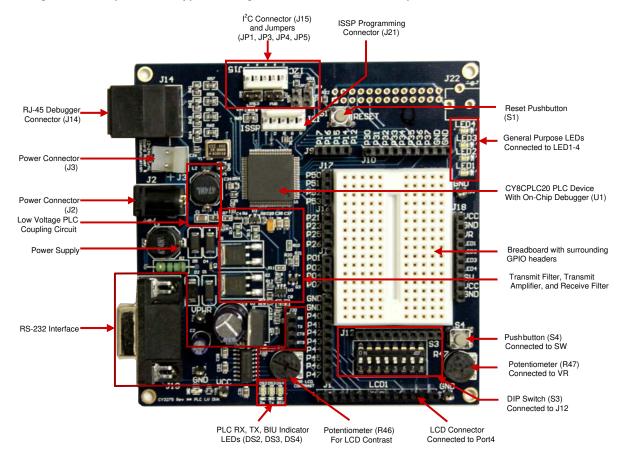

Figure 3-1 shows the programmable low voltage PLC development board. The key components and areas are highlighted. This section provides a description of the user-accessible components and how to use these components on the board. For a detailed description of the design parameters for the PLC circuit, see application note AN55427, *Cypress Powerline Communication Board Design Analysis*. The board is divided into seven main sections:

- Development

- LCD module

- Debugger

- RS-232 COM port

- Power supply

- Transmit amplifier and receive filter

- Low voltage coupling circuit

Figure 3-1. Top View of Cypress Programmable PLC LV Development Board

The core of the PLC LV board is the CY8CPLC20 chip. The communication signal flow on this LV board is as follows:

*Transmit*: CY8CPLC20 TX pin (FSK\_OUT) → Power Amplifier Circuitry → LV Coupling Circuitry → LV Powerline (12 V to 24 V AC/DC).

Receive: LV Powerline (12 V to 24 V AC/DC)  $\rightarrow$  LV Coupling Circuitry  $\rightarrow$  Passive Low Pass Filtering  $\rightarrow$  Vdd/2 Biasing  $\rightarrow$  CY8CPLC20 RX pin (FSK\_IN).

#### 3.3.1 Development

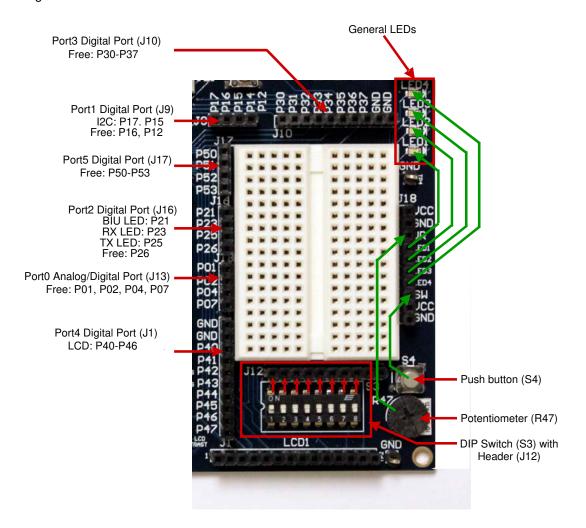

#### 3.3.1.1 User I/Os, Bread Board, and GPIO Headers

This section is the area where you create your custom design. All GPIO pins (excluding those required for PLC communication) are routed to this bread board area. Some of the pins are shared for other purposes (for example, the port 4 pins P4[6:0] are also connected to the LCD connector).

Header J18 has pins that are connected to user I/Os (potentiometer, pushbutton, and LEDs). In Figure 3-2, these connections are represented by the green arrows. To connect one of the user I/Os to a CY8CPLC20 pin, connect a jumper wire between the respective header pins. For example, to connect the pushbutton S4 to pin P1[6], place a jumper wire in SW on header J18 and the other end in P16 on header J9.

The DIP switch bank S3 is not connected directly to any of the CY8CPLC20 pins. The DIP switch is connected to header J12, so that a jumper wire can be connected to any of the pins. The DIP switch is active LOW (connected to GND when in the ON position).

Figure 3-2. Bread Board

#### 3.3.1.2 CY8CPLC20 Device

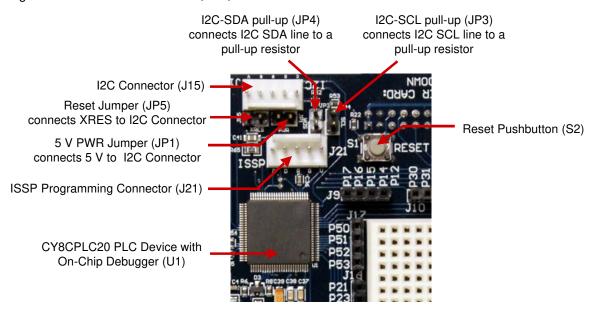

This section has the CY8CPLC20-OCD chip, which has the integrated transmit/receive modem, network protocol, and application layer. It also has an I2C header for optional communication with an external host processor. The ISSP header is provided to program the part. The part has a built-in debug support using the RJ-45 connector, which can be used with the ICE debugger. It also has three dedicated LEDs to indicate communication on the powerline: green LED for TX, red LED for RX, and yellow LED for BIU.

Figure 3-3. CY8CPLC20 Device, I<sup>2</sup>C, and ISSP Headers

Table 3-1. Headers and Jumpers

| Headers and Jumpers | Description                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIU LED[DS4]        | Yellow LED to indicate when the transmit frequency band is in use                                                                                                                                                                                                                                                                                                                                |

| CY8CPLC20-OCD       | Cypress powerline transceiver device. It is a 100-pin on-chip debugger (OCD) device                                                                                                                                                                                                                                                                                                              |

| J8                  | 2-pin header for connecting to Vcc and Gnd                                                                                                                                                                                                                                                                                                                                                       |

|                     | V – Vdd Pin: This pin can provide a maximum of 50 mA at 5 V to an external board only when the input to the board is 12 V. For input voltages greater than 12 V, do not use this pin to power another board. This pin is only to source the current. <b>Do not use this pin to power the CY8CPLC20 device.</b> Note that the PWR jumper (JP1) needs to be connected to enable this functionality |

|                     | G – Gnd Pin: This pin can provide the ground reference to an external board                                                                                                                                                                                                                                                                                                                      |

| J15                 | D-I2C Data (SDA): Data line for the I2C communication. This pin is directly connected to the CY8CPLC20 device                                                                                                                                                                                                                                                                                    |

|                     | C – I2C Clock (SCL): Clock line for the I2C communication. This pin is directly connected to the CY8CPLC20 device                                                                                                                                                                                                                                                                                |

|                     | R – Reset: Connecting this pin to an external board enables the CY8CPLC20 chip to be reset by an external board. Note that the RES jumper needs to be connected to enable this functionality                                                                                                                                                                                                     |

| JP1 (PWR)           | Connect this jumper to power an external board from the CY3275. The external board is powered through the V and G pins on the I2C connector (J15)                                                                                                                                                                                                                                                |

| Headers and Jumpers                   | Description                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JP3 (I2C-SCL)                         | I2C SCL pull up jumper. While communicating through I2C(J15), one side should pull up the line. When the jumper is connected, the SCL line is pulled high. This needs to be done when the user wants the I2C link to be pulled up by the CY3275 board. This jumper does not need to be placed if the USB-I2C bridge is used to communication with the host |

| JP4 (I2C-SDA)                         | I2C SDA pull up jumper. While communicating through I2C(J15), one side should pull up the line. When the jumper is connected, the SDA line is pulled high. This needs to be done when the user wants the I2C link to be pulled up by the CY3275 board. This jumper does not need to be placed if the USB-I2C bridge is used to communication with the host |

| JP5 (Reset)                           | The jumper is to enable reset of the PLC chip through an external board. When this jumper is connected, the external board reset can be connected to the R pin on the I2C header (J15)                                                                                                                                                                     |

| LED1-LED4                             | Headers connected to general purpose configurable LEDs                                                                                                                                                                                                                                                                                                     |

| P01,P02,P04, P07                      | Free analog/digital port pins                                                                                                                                                                                                                                                                                                                              |

| P21                                   | Port pin connected to yellow LED for BIU                                                                                                                                                                                                                                                                                                                   |

| P23                                   | Port pin connected to red LED for RX                                                                                                                                                                                                                                                                                                                       |

| P25                                   | Port pin connected to green LED for TX                                                                                                                                                                                                                                                                                                                     |

| P26                                   | Free port pin                                                                                                                                                                                                                                                                                                                                              |

| P40-P46                               | Port pins connected to LCD card                                                                                                                                                                                                                                                                                                                            |

| P15                                   | Port pin connected to I2C data line (SDA)                                                                                                                                                                                                                                                                                                                  |

| P16, P12                              | Free port pins                                                                                                                                                                                                                                                                                                                                             |

| P17                                   | Port pin connected to I2C clock line (SCL)                                                                                                                                                                                                                                                                                                                 |

| P30,P31,P32,P33,P34,<br>P35, P36, P37 | Free port pins                                                                                                                                                                                                                                                                                                                                             |

| P47                                   | Free port pin                                                                                                                                                                                                                                                                                                                                              |

| P50,P51,P52,P53                       | Free port pins                                                                                                                                                                                                                                                                                                                                             |

| PWR LED[DS1]                          | Blue LED that glows when the board is powered on                                                                                                                                                                                                                                                                                                           |

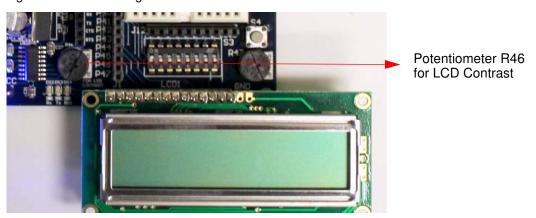

| R46                                   | Adjusting this potentiometer adjusts the contrast on the LCD daughter card                                                                                                                                                                                                                                                                                 |

| R47                                   | This is a variable resistor (potentiometer) that connects to the VR header. It is used to generate a voltage between +5 V and GND                                                                                                                                                                                                                          |

| RX LED[DS2]                           | Red LED to indicate when the board is receiving data                                                                                                                                                                                                                                                                                                       |

| S2                                    | Reset switch for the CY8CPLC20-OCD chip                                                                                                                                                                                                                                                                                                                    |

| S3[7-0]                               | These DIP switches are general purpose and can be routed to any port of the CY8CPLC20 chip. In the ON position, the switch is connected to ground. In the OFF position, the signal is high-Z                                                                                                                                                               |

| SW                                    | Header connected to the switch S4. S4 is a general-purpose switch. Active HIGH (connected to VDD when pressed)                                                                                                                                                                                                                                             |

| TP1, TP2, TP3, TP4                    | Grounded test points to facilitate probing/debugging                                                                                                                                                                                                                                                                                                       |

| TX LED[DS3]                           | Green LED to indicate when the board is transmitting data on to the powerline                                                                                                                                                                                                                                                                              |

| VR                                    | Header connected to the potentiometer R47                                                                                                                                                                                                                                                                                                                  |

| ·                                     |                                                                                                                                                                                                                                                                                                                                                            |

#### 3.3.1.3 Potentiometer and DIP Switches

The board has 8-position general purpose DIP switches (S3). A general-purpose potentiometer (R47) is provided next to the DIP switches. This potentiometer can be routed to the chip using the GPIO pins. The second potentiometer (R46) is specifically meant to control the contrast for the LCD daughter card in the LCD1 slot.

#### 3.3.2 LCD Daughter Card

This card is an LCD module easily connected to the board. It is connected and controlled by using the CY8CPLC20 port 4 pins P4[6:0].

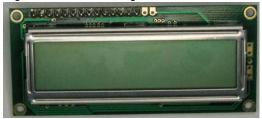

Figure 3-4. LCD Daughter Card

It is connected to the main board, as shown in Figure 3-4. The LCD contrast is controlled by the potentiometer R46.

Figure 3-5. LCD Daughter Card Connection

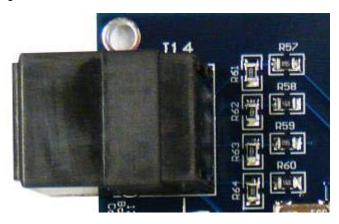

#### 3.3.3 Debugger

The RJ-45 ICE-Cube emulation connector provides a debug interface between the CY8CPLC20-OCD device and the ICE-Cube emulation tool using PSoC Designer. A CY3215-DK In-Circuit Emulation Development Kit is required to interface the PC to this board. This kit is available for purchase at: http://www.cypress.com/go/CY3215-DK.

Figure 3-6. RJ-45 Connector

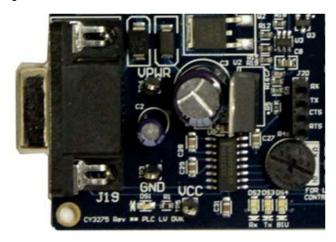

#### 3.3.4 RS-232 COM Port

The RS-232 COM port is used with a standard RS-232 cable to connect two RS-232 capable devices together. The RS-232 header (J20) is a 4-pin header that has connections for the RX, TX, RTS, and CTS lines. These are wired to port pins to connect the device to the respective pins on the RS-232 DB9 port.

Figure 3-7. RS-232 COM Port

The following table shows the controls associated with the RS-232 COM port.

Table 3-2. Key RS-232 COM Signals

| Control Description/Comment                                   |                                                                    |

|---------------------------------------------------------------|--------------------------------------------------------------------|

| RX The board receives the RS-232 information through this pin |                                                                    |

| TX                                                            | The board transmits RS-232 information through this pin            |

| RTS                                                           | The host asks the chip if it can send information through this pin |

| CTS                                                           | The chip signals that it is ready to accept information through RX |

#### 3.3.5 Power Supply Circuit

This section takes the power from the powerline and generates 5-V DC voltage for the operation of the PLC transceiver, transmit amplifier, and other components on the chip.

Table 3-3. Key Power Supply Circuitry Components

| Component | Description                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J2        | Connector for the wall wart, power adapter, and daisy chain cables                                                                                                                                                                                                                                                                                                                                                  |  |

| U2        | 5-V regulator                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| J3        | 2-pin header to connect other boards in daisy chain and power them. The cable for this is provided with the kit. Connect a maximum of five boards in one daisy chain. It is important to maintain the same polarity of the power for both DC and AC input voltages. The AC polarity must be the same for all boards because the '-' power input terminal is connected directly to the ground reference on the board |  |

| DS1       | Blue LED, which is on when the board is powered                                                                                                                                                                                                                                                                                                                                                                     |  |

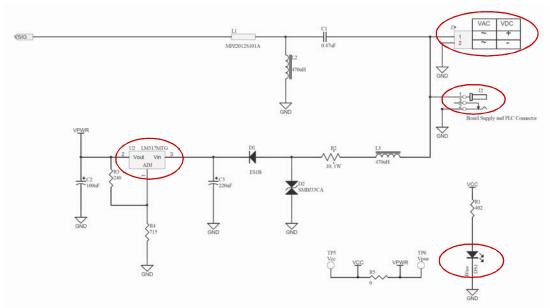

The key components are circled in the following schematic.

Figure 3-8. Power Supply Schematic

#### 3.3.6 Transmit Amplifier and Receive Filter

The transmit signal from the FSK\_OUT pin of the CY8CPLC20 device is amplified (to drive the signal on the powerline). The passive receive filter prepares the signal for the FSK\_IN pin of the CY8CPLC20 device.

Table 3-4. Key Transmit Amplifier Components

| Component  | nent Description                                                                                                                                  |  |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| U3, Q1, Q2 | These opamp and high-gain transistors are used for power amplification of the transmitted PLC signal.                                             |  |

| Q3         | This transistor controls whether the transmit circuit is enabled or is in a high-Z state. Its input is the TX_DISABLE signal from the PLC device. |  |

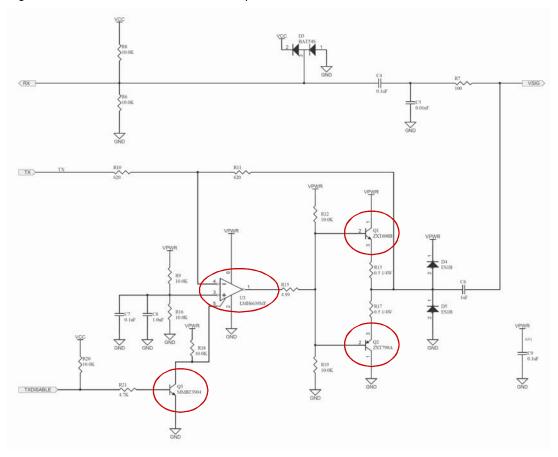

The key components are circled in the following schematic.

Figure 3-9. Transmit Filter, Transmit Amplifier, and Receive Filter

#### 3.3.7 Low Voltage Coupling Circuit

This circuit couples the signal from the board on to the powerline. On the receive side, the same circuit couples the carrier from the powerline into the board, while filtering out the power and low frequency content on the powerline.

Table 3-5. Key Transmit and Receive Coupling Components

| Component                                                                                                                                                                   | Description                                                                                                                                                           |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| L1 This inductor blocks high frequency signals (for example, FM radio) from entering the lt also offsets the impedance of capacitor C30 to have a lower transmit impedance. |                                                                                                                                                                       |  |

| L2                                                                                                                                                                          | This inductor, along with C1, filters out low frequency signals (for example, power) and presents a high impedance to the 132 kHz PLC signal.                         |  |

| C1                                                                                                                                                                          | This is the coupling capacitor that couples the PLC signal and blocks the low frequency signals. Its voltage rating must be higher than the voltage on the powerline. |  |

The key components are circled in the following schematic.