# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# CY7C68001

# EZ-USB SX2<sup>™</sup> High Speed USB Interface Device

# 1. Features

- USB 2.0-Certified Compliant

On the USB-IF Integrators List: Test ID Number 40000713

- Operates at High (480 Mbps) or Full (12 Mbps) Speed

- Supports Control Endpoint 0:

Used for handling USB device requests

- Supports Four Configurable Endpoints that share a 4-KB FIFO Space

- D Endpoints 2, 4, 6, 8 for application-specific control and data

- Standard 8- or 16-bit External Master Interface

- Glueless interface to most standard microprocessors DSPs, ASICs, and FPGAs

Synchronous or Asynchronous interface

- Synchronous of Asynchronous interna

- Integrated Phase-locked Loop (PLL)

- 3.3V Operation, 5V Tolerant I/Os

- 56-pin SSOP and QFN Package

- Complies with most Device Class Specifications

# 2. Applications

- DSL modems

- ATA interface

- Memory card readers

- Legacy conversion devices

- Cameras

- Scanners

- Home PNA

- Wireless LAN

- MP3 players

- Networking

- Printers

The "Reference Designs" section of the Cypress web site, www.cypress.com, provides additional tools for typical USB applications. Each reference design comes complete with firmware source code and object code, schematics, and documentation.

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised July 07, 2009

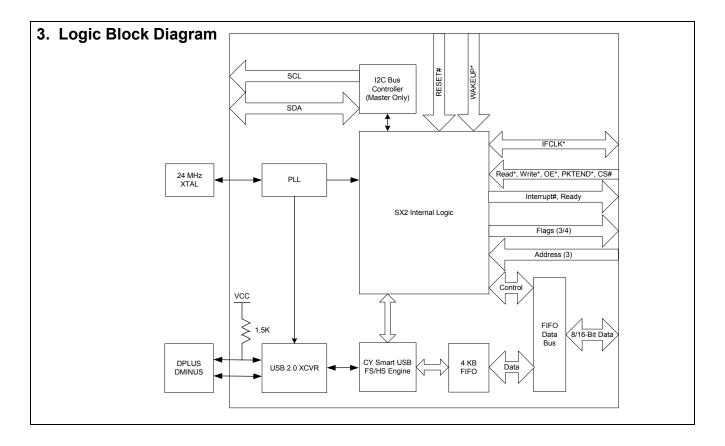

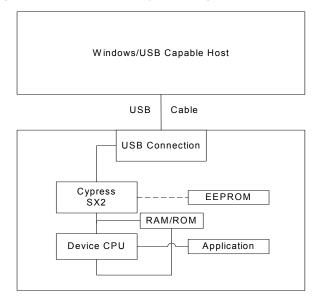

# 4. Introduction

The EZ-USB SX2<sup>™</sup> USB interface device is designed to work with any external master, such as standard microprocessors, DSPs, ASICs, and FPGAs to enable USB 2.0 support for any peripheral design. SX2 has a built in USB transceiver and Serial Interface Engine (SIE), along with a command decoder for sending and receiving USB data. The controller has four endpoints that share a 4 KB FIFO space for maximum flexibility and throughput, and Control Endpoint 0. SX2 has three address pins and a selectable 8- or 16- bit data bus for command and data input or output.

#### Figure 4-1. Example USB System Diagram

# 5. Functional Overview

# 5.1 USB Signaling Speed

SX2 operates at two of the three rates defined in the Universal Serial Bus Specification Revision 2.0, dated April 27, 2000:

- Full speed, with a signaling bit rate of 12 Mbits/s

- High speed, with a signaling bit rate of 480 Mbits/s.

- SX2 does not support the low speed signaling rate of 1.5 Mbits/s.

# 5.2 Buses

SX2 features:

- A selectable 8- or 16-bit bidirectional data bus

- An address bus for selecting the FIFO or Command Interface.

## 5.3 Boot Methods

During the power up sequence, internal logic of the *SX2* checks for the presence of an I<sup>2</sup>C EEPROM.<sup>[1,2]</sup> If it finds an EEPROM, it boots off the EEPROM. When the presence of an EEPROM is detected, the *SX2* checks the value of first byte. If the first byte is found to be a 0xC4, the *SX2* loads the next two bytes into the IFCONFIG and POLAR registers, respectively. If the fourth byte is also 0xC4, the *SX2* enumerates using the descriptor in the EEPROM, then signals to the external master when enumeration is complete through an ENUMOK interrupt (See "Interrupt System" on page 3.). If no EEPROM is detected, the *SX2* relies on the external master for the descriptors. After this descriptor information is received from the external master, the *SX2* connects to the USB and enumerates.

#### 5.3.1 EEPROM Organization

The valid sequence of bytes in the EEPROM are displayed in the following table.

# Table 5-1. Descriptor Length Set to 0x06: Default Enumeration

| Byte Index | Description                   |

|------------|-------------------------------|

| 0          | 0xC4                          |

| 1          | IFCONFIG                      |

| 2          | POLAR                         |

| 3          | 0xC4                          |

| 4          | Descriptor Length (LSB):0x06  |

| 5          | Descriptor Length (MSB): 0x00 |

| 6          | VID (LSB)                     |

| 7          | VID (MSB)                     |

| 8          | PID (LSB)                     |

| 9          | PID (MSB)                     |

| 10         | DID (LSB)                     |

| 11         | DID (MSB)                     |

#### Table 5-2. Descriptor Length Not Set to 0x06

| Byte Index | Description             |

|------------|-------------------------|

| 0          | 0xC4                    |

| 1          | IFCONFIG                |

| 2          | POLAR                   |

| 3          | 0xC4                    |

| 4          | Descriptor Length (LSB) |

| 5          | Descriptor Length (MSB  |

| 6          | Descriptor[0]           |

| 7          | Descriptor[1]           |

| 8          | Descriptor[2]           |

#### Notes

Because there is no direct way to detect which EEPROM type (single or double address) is connected, SX2 uses the EEPROM address pins A2, A1, and A0 to

determine whether to send out one or two bytes of address. Single-byte address EEPROMs (24LC01, etc.) should be strapped to address 000 and double-byte

EEPROMs (24LC64, etc.) should be strapped to address 001.

2. The SCL and SDA pins must be pulled up for this detection method to work properly, even if an EEPROM is not connected. Typical pull up values are 2.2K–10K Ohms.

- IFCONFIG: The IFCONFIG byte contains the settings for the IFCONFIG register. The IFCONFIG register bits are defined in IFCONFIG Register 0x01 on page 17. If the external master requires an interface configuration different from the default, that interface can be specified by this byte.

- POLAR: The Polar byte contains the polarity of the FIFO flag pin signals. The POLAR register bits are defined in POLAR Register 0x04 on page 18. If the external master requires signal polarity different from the default, the polarity can be specified by this byte.

- Descriptor: The Descriptor byte determines if the *SX2* loads the descriptor from the EEPROM. If this byte = 0xC4, the *SX2* loads the descriptor starting with the next byte. If this byte does not equal 0xC4, the *SX2* waits for descriptor information from the external master.

- Descriptor Length: The Descriptor length is within the next two bytes and indicate the length of the descriptor contained within the EEPROM. The length is loaded least significant byte (LSB) first, then most significant byte (MSB).

- Byte Index 6 Starts Descriptor Information: The descriptor can be a maximum of 500 bytes.

#### 5.3.2 Default Enumeration

An optional default descriptor can be used to simplify enumeration. Only the Vendor ID (VID), Product ID (PID), and Device ID (DID) need to be loaded by the *SX2* for it to enumerate with this default setup. This information is either loaded from an EEPROM in the case when the presence of an EEPROM (Table 5-1) is detected, or the external master may simply load a VID, PID, and DID when no EEPROM is present. In this default enumeration, the *SX2* uses the in-built default descriptor (refer to Default Descriptor on page 37).

If the descriptor length loaded from the EEPROM is 6, *SX2* loads a VID, PID, and DID from the EEPROM and enumerate. The VID, PID, and DID are loaded LSB, then MSB. For example, if the VID, PID, and DID are 0x0547, 0x1002, and 0x0001, respectively, then the bytes should be stored as:

#### ■ 0x47, 0x05, 0x02, 0x10, 0x01, 0x00.

If there is no EEPROM, *SX2* waits for the external master to provide the descriptor information. To use the default descriptor, the external master must write to the appropriate register (0x30) with descriptor length equal to 6 followed by the VID, PID, and DID. Refer to Default Enumeration on page 8 for further information on how the external master may load the values.

The default descriptor enumerates the following endpoints:

- Endpoint 2: Bulk out, 512 bytes in high speed mode, 64 bytes in full speed mode

- Endpoint 4: Bulk out, 512 bytes in high speed mode, 64 bytes in full speed mode

- Endpoint 6: Bulk in, 512 bytes in high speed mode, 64 bytes in full speed mode

- Endpoint 8: Bulk in, 512 bytes in high speed mode, 64 bytes in full speed mode.

The entire default descriptor is listed in Default Descriptor on page 37 of this data sheet.

#### 5.4 Interrupt System

#### 5.4.1 Architecture

The *SX2* provides an output signal that indicates to the external master that the *SX2* has an interrupt condition, or that the data from a register read request is available. The *SX2* has six interrupt sources: SETUP, EP0BUF, FLAGS, ENUMOK, BUSACTIVITY, and READY. Each interrupt can be enabled or disabled by setting or clearing the corresponding bit in the INTENABLE register.

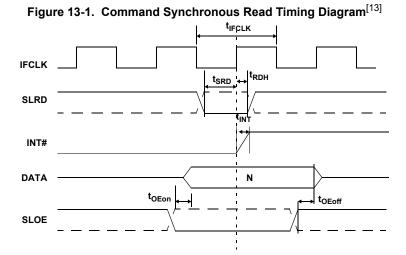

When an interrupt occurs, the INT# pin is asserted, and the corresponding bit is set in the Interrupt Status Byte. The external master reads the Interrupt Status Byte by strobing SLRD/SLOE. This presents the Interrupt Status Byte on the lower portion of the data bus (FD[7:0]). Reading the Interrupt Status Byte automatically clears the interrupt. Only one interrupt request occurs at a time; the *SX2* buffers multiple pending interrupts.

If the external master has initiated a register read request, the SX2 buffers interrupts until the external master has read the data. This insures that after a read sequence has begun, the next interrupt that is received from the SX2 indicates that the corresponding data is available. Following is a description of this INTENABLE register.

#### 5.4.2 INTENABLE Register Bit Definition

#### Bit 7: SETUP

If this interrupt is enabled, and the *SX2* receives a setup packet from the USB host, the *SX2* asserts the INT# pin and sets bit 7 in the Interrupt Status Byte. This interrupt only occurs if the setup request is not one that the *SX2* automatically handles. For complete details on how to handle the SETUP interrupt, refer to Endpoint 0 on page 8 of this data sheet.

#### Bit 6: EP0BUF

If this interrupt is enabled, and the Endpoint 0 buffer becomes available to the external master for read or write operations, the *SX2* asserts the INT# pin and sets bit 6 in the Interrupt Status Byte. This interrupt is used for handling the data phase of a setup request. For complete details on how to handle the EP0BUF interrupt, refer to Endpoint 0 on page 8 of this data sheet.

#### Bit 5: FLAGS

If this interrupt is enabled, and any OUT endpoint FIFO's state changes from empty to not empty and from not empty to empty, the *SX2* asserts the INT# pin and sets bit 5 in the Interrupt Status Byte. This is an alternate way to monitor the status of OUT endpoint FIFOs instead of using the FLAGA-FLAGD pins, and can be used to indicate when an OUT packet has been received from the host.

#### Bit 2: ENUMOK

If this interrupt is enabled and the *SX2* receives a SET\_CONFIGURATION request from the USB host, the *SX2* asserts the INT# pin and sets bit 2 in the Interrupt Status Byte. This event signals the completion of the *SX2* enumeration process.

#### Bit 1: BUSACTIVITY

If this interrupt is enabled, and the *SX2* detects either an absence or resumption of activity on the USB bus, the *SX2* asserts the INT# pin and sets bit 1 in the Interrupt Status Byte. This usually indicates that the USB host is either suspending or resuming or that a self-powered device has been plugged in or unplugged. If the *SX2* is bus-powered, the external master must put the *SX2* into a low power mode after detecting a USB suspend condition to be USB-compliant.

#### Bit 0: READY

If this interrupt is enabled, bit 0 in the Interrupt Status Byte is set when the *SX2* has powered up and performed a self-test. The external master should always wait for this interrupt before trying to read or write to the *SX2*, unless an external EEPROM with a valid descriptor is present. If an external EEPROM with a valid descriptor is present, the ENUMOK interrupt occurs instead of the READY interrupt after power up. A READY interrupt also occurs if the *SX2* is awakened from a low power mode via the WAKEUP pin. This READY interrupt indicates that the *SX2* is ready for commands or data.

#### 5.4.3 Qualify with READY Pin on Register Reads

It is true that all interrupts are buffered after a command read request has been initiated. However, in very rare conditions, there might be a situation when there is a pending interrupt already, when a read request is initiated by the external master. In this case it is the interrupt status byte that is output when the external master asserts the SLRD. So, a condition exists where the Interrupt Status Data Byte can be mistaken for the result of a command register read request. In order to get around this possible race condition, the first thing that the external master must do on getting an interrupt from the *SX2* is check the status of the READY pin. If the READY is low at the time the INT# was asserted, the data that is output when the external master strobes the SLRD is the interrupt status byte (not the actual data requested). If the READY pin is high at the time when the interrupt is asserted, the data output on strobing the SLRD is the actual data byte requested by the external master. So it is important that the state of the READY pin be checked at the time the INT# is asserted to ascertain the cause of the interrupt.

#### 5.5 Resets and Wakeup

#### 5.5.1 Reset

An input pin (RESET#) resets the chip. The internal PLL stabilizes after V<sub>CC</sub> has reached 3.3V. Typically, an external RC network (R = 100 KOhms, C =  $0.1 \ \mu$ F) is used to provide the RESET# signal. The Clock must be in a stable state for at least 200  $\mu$ s before the RESET is released.

#### 5.5.2 USB Reset

When the *SX2* detects a USB Reset condition on the USB bus, *SX2* handles it like any other enumeration sequence. This means that *SX2* enumerates again and assert the ENUMOK interrupt to let the external master know that it has enumerated. The external master is then responsible for configuring the *SX2* for the application. The external master should also check whether *SX2* enumerated at High or Full speed in order to adjust the EPxPKTLENH/L register values accordingly. The last initialization task is for the external master to flush all of the *SX2* FIFOs.

#### 5.5.3 Wakeup

The *SX2* exits its low power state when one of the following events occur:

- USB bus signals a resume. The *SX2* asserts a BUSACTIVITY interrupt.

- The external master asserts the WAKEUP pin. The SX2 asserts a READY interrupt<sup>[3]</sup>.

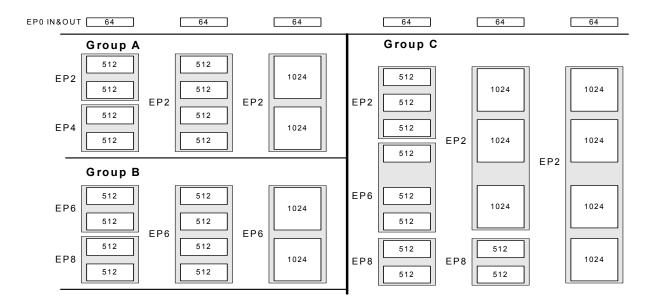

#### 5.6 Endpoint RAM

#### 5.6.1 Size

- Control endpoint: 64 Bytes: 1 × 64 bytes (Endpoint 0).

- FIFO Endpoints: 4096 Bytes: 8 × 512 bytes (Endpoint 2, 4, 6, 8).

#### Organization

- EP0–Bidirectional Endpoint 0, 64-byte buffer.

- EP2, 4, 6, 8–Eight 512-byte buffers, bulk, interrupt, or isochronous. EP2 and EP6 can be either double-, triple-, or quad-buffered. EP4 and EP8 can only be double-buffered. For high speed endpoint configuration options, see Figure 8-1. on page 11.

Note

<sup>3.</sup> If the descriptor loaded is set for remote wakeup enabled and the host does a set feature remote wakeup enabled, then the SX2 logic performs RESUME signalling after a WAKEUP interrupt.

Figure 5-1. Endpoint Configurations (High Speed Mode)

Endpoint 0 is the same for every configuration as it serves as the CONTROL endpoint. For Endpoints 2, 4, 6, and 8, refer to Figure 8-1. on page 11. Endpoints 2, 4, 6, and 8 may be configured by choosing either:

- One configuration from Group A and one from Group B

- One configuration from Group C.

- Some example endpoint configurations are as follows.

- EP2: 1024 bytes double-buffered, EP6: 512 bytes quad-buffered.

- EP2: 512 bytes double-buffered, EP4: 512 bytes double-buffered, EP6: 512 bytes double-buffered, EP8: 512 bytes double buffered.

- EP2: 1024 bytes quad-buffered.

#### 5.6.2 Default Endpoint Memory Configuration

At power-on-reset, the endpoint memories are configured as follows:

- EP2: Bulk OUT, 512 bytes/packet, 2x buffered.

- EP4: Bulk OUT, 512 bytes/packet, 2x buffered.

- EP6: Bulk IN, 512 bytes/packet, 2x buffered.

- EP8: Bulk IN, 512 bytes/packet, 2x buffered.

#### 5.7 External Interface

The SX2 presents two interfaces to the external master.

- 1. A FIFO interface through which EP2, 4, 6, and 8 data flows.

- 2. A command interface, which is used to set up the SX2, read status, load descriptors, and access Endpoint 0.

#### 5.7.1 Architecture

The SX2 slave FIFO architecture has eight 512-byte blocks in the endpoint RAM that directly serve as FIFO memories and are controlled by FIFO control signals (IFCLK, CS#, SLRD, SLWR, SLOE, PKTEND, and FIFOADR[2:0]).

The SX2 command interface is used to set up the SX2, read status, load descriptors, and access Endpoint 0. The command interface has its own READY signal for gating writes, and an INT# signal to indicate that the SX2 has data to be read, or that an interrupt event has occurred. The command interface uses the same control signals (IFCLK, CS#, SLRD, SLWR, SLOE, and FIFOADR[2:0]) as the FIFO interface, except for PKTEND.

#### 5.7.2 Control Signals

#### **FIFOADDR Lines**

The *SX2* has three address pins that are used to select either the FIFOs or the command interface. The addresses correspond to the following table.

Table 5-3. FIFO Address Lines Setting

| Address/Selection | FIFOADR2 | FIFOADR1 | FIFOADR0 |

|-------------------|----------|----------|----------|

| FIFO2             | 0        | 0        | 0        |

| FIFO4             | 0        | 0        | 1        |

| FIFO6             | 0        | 1        | 0        |

| FIFO8             | 0        | 1        | 1        |

| COMMAND           | 1        | 0        | 0        |

| RESERVED          | 1        | 0        | 1        |

| RESERVED          | 1        | 1        | 0        |

| RESERVED          | 1        | 1        | 1        |

The *SX2* accepts either an internally derived clock (30 MHz or 48 MHz) or externally supplied clock (IFCLK, 5 to 50 MHz), and SLRD, SLWR, SLOE, PKTEND, CS#, FIFOADR[2:0] signals from an external master. The interface can be selected for 8- or 16- bit operation by an internal configuration bit, and an Output Enable signal SLOE enables the data bus driver of the selected width. The external master must ensure that the output enable signal is inactive when writing data to the *SX2*. The interface can operate either asynchronously where the SLRD and SLWR signals act directly as strobes, or synchronously where the SLRD and SLWR act as clock qualifiers. The optional CS# signal tristates the data bus and ignore SLRD, SLWR, PKTEND.

The external master reads from OUT endpoints and writes to IN endpoints, and reads from or writes to the command interface.

#### Read: SLOE and SLRD

In synchronous mode, the FIFO pointer is incremented on each rising edge of IFCLK while SLRD is asserted. In asynchronous mode, the FIFO pointer is incremented on each asserted-to-deasserted transition of SLRD.

SLOE is a data bus driver enable. When SLOE is asserted, the data bus is driven by the *SX2*.

#### Write: SLWR

In synchronous mode, data on the FD bus is written to the FIFO (and the FIFO pointer is incremented) on each rising edge of IFCLK while SLWR is asserted. In asynchronous mode, data on the FD bus is written to the FIFO (and the FIFO pointer is incremented) on each asserted-to-deasserted transition of SLWR.

#### PKTEND

PKTEND commits the current buffer to USB. To send a short IN packet (one which has not been filled to max packet size determined by the value of PL[X:0] in EPxPKTLENH/L), the external master strobes the PKTEND pin.

All these interface signals have a default polarity of low. In order to change the polarity of PKTEND pin, the master may write to the POLAR register anytime. In order to switch the polarity of the SLWR/SLRD/SLOE, the master must set the appropriate bits 2, 3 and 4 respectively in the FIFOPINPOLAR register located at XDATA space 0xE609. Please note that the SX2 powers up with the polarities set to low. POLAR Register 0x04 on page 18 provides further information on how to access this register located at XDATA space.

#### 5.7.3 IFCLK

The IFCLK pin can be configured to be either an input (default) or an output interface clock. Bits IFCONFIG[7:4] define the behavior of the interface clock. To use the *SX2*'s internally-derived 30- or 48 MHz clock, set IFCONFIG.7 to 1 and set IFCONFIG.6 to 0 (30 MHz) or to 1 (48 MHz). To use an externally supplied clock, set IFCONFIG.7=0 and drive the IFCLK pin (5 MHz to 50 MHz). The input or output IFCLK signal can be inverted by setting IFCONFIG.4=1.

#### 5.7.4 FIFO Access

An external master can access the slave FIFOs either asynchronously or synchronously:

- Asynchronous–SLRD, SLWR, and PKTEND pins are strobes.

- Synchronous–SLRD, SLWR, and PKTEND pins are enables for the IFCLK clock pin.

An external master accesses the FIFOs through the data bus, FD [15:0]. This bus can be either 8- or 16-bits wide; the width is selected via the WORDWIDE bit in the EPxPKTLENH/L registers. The data bus is bidirectional, with its output drivers controlled by the SLOE pin. The FIFOADR[2:0] pins select which of the four FIFOs is connected to the FD [15:0] bus, or if the command interface is selected.

#### 5.7.5 FIFO Flag Pins Configuration

The FIFO flags are FLAGA, FLAGB, FLAGC, and FLAGD. These FLAGx pins report the status of the FIFO selected by the FIFOADR[2:0] pins. At reset, these pins are configured to report the status of the following:

- FLAGA reports the status of the programmable flag.

- FLAGB reports the status of the full flag.

- FLAGC reports the status of the empty flag.

- FLAGD defaults to the CS# function.

The FIFO flags can either be indexed or fixed. Fixed flags report the status of a particular FIFO regardless of the value on the FIFOADR [2:0] pins. Indexed flags report the status of the FIFO selected by the FIFOADR [2:0]pins.<sup>[4]</sup>

#### 5.7.6 Default FIFO Programmable Flag Setup

By default, FLAGA is the Programmable Flag (PF) for the endpoint being pointed to by the FIFOADR[2:0] pins. For EP2 and EP4, the default endpoint configuration is BULK, OUT, 512, 2x; the PF pin asserts when the entire FIFO has  $\geq$  512 bytes. For EP6 and EP8, the default endpoint configuration is BULK, IN, 512, 2x, and the PF pin asserts when the entire FIFO has less than/equal to 512 bytes. In other words, EP6/8 report a half-empty state, and EP2/4 report a half-full state.

#### 5.7.7 FIFO Programmable Flag (PF) Setup

Each FIFO's programmable-level flag (PF) asserts when the FIFO reaches a user-defined fullness threshold. That threshold is configured as follows:

- 1. For OUT packets: The threshold is stored in PFC12:0. The PF is asserted when the number of bytes *in the entire FIFO* is less than/equal to (DECIS = 0) or greater than/equal to (DE-CIS = 1) the threshold.

- 2. For IN packets, with PKTSTAT = 1: The threshold is stored in PFC9:0. The PF is asserted when the number of bytes written into *the current packet in the FIFO* is less than/equal to (DECIS = 0) or greater than/equal to (DECIS = 1) the threshold.

- For IN packets, with PKTSTAT = 0: The threshold is stored in two parts: PKTS2:0 holds the number of committed packets, and PFC9:0 holds the number of bytes in the current packet. The PF is asserted when the FIFO is at or less full than (DECIS = 0), or at or more full than (DECIS = 1), the threshold.

Note

4. In indexed mode, the value of the FLAGx pins is indeterminate except when addressing a FIFO (FIFOADR[2:0]={000,001,010,011}).

#### 5.7.8 Command Protocol

An address of [1 0 0] on FIFOADR [2:0] selects the command interface. The command interface is used to write to and read from the *SX2* registers and the Endpoint 0 buffer, as well as the descriptor RAM. Command read and write transactions occur over FD[7:0] only. Each byte written to the *SX2* is either an address or a data byte, as determined by bit7. If bit7 = 1, then the byte is considered an address byte. If bit7 = 0, then the byte is considered a data byte. If bit7 = 1, then bit6 determines whether the address byte is a read request or a write request. If bit6 = 1, then the byte is considered a read request. If bit6 = 0 then the byte is considered a write request. Bits [5:0] hold the register address of the request. The format of the command address byte is shown in Table 5-4.

#### Table 5-4. Command Address Byte

| Address/<br>Data# | Read/<br>Write# | A5    | A4    | A3    | A2    | A1    | A0    |

|-------------------|-----------------|-------|-------|-------|-------|-------|-------|

| Bit 7             | Bit 6           | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

Each Write request is followed by two or more data bytes. If another address byte is received before both data bytes are received, the *SX2* ignores the first address and any incomplete data transfers. The format for the data bytes is shown in Table 5-5 and Table 5-6. Some registers take a series of bytes. Each byte is transferred using the same protocol.

#### Table 5-5. Command Data Byte One

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | Х     | Х     | Х     | D7    | D6    | D5    | D4    |

#### Table 5-6. Command Data Byte Two

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| 0     | Х     | Х     | Х     | D3    | D2    | D1    | D0    |

The first command data byte contains the upper nibble of data, and the second command byte contains the lower nibble of data.

#### Write Request Example

Prior to writing to a register, two conditions must be met: FIFOADR[2:0] must hold [1 0 0], and the Ready line must be HIGH. The external master should not initiate a command if the READY pin is not in a HIgh state.

**Example**: to write the byte <10110000> into the IFCONFIG register (0x01), first send a command address byte as follows.

#### Table 5-7. Command Address Write Byte

| Ad-<br>dress/Da<br>ta# | Read/<br>Write# | A5 | A4 | A3 | A2 | A1 | A0 |

|------------------------|-----------------|----|----|----|----|----|----|

| 1                      | 0               | 0  | 0  | 0  | 0  | 0  | 1  |

- The first bit signifies an address transfer.

- The second bit signifies that this is a write command.

- The next six bits represent the register address (000001 binary = 0x01 hex).

After the byte has been received the *SX2* pulls the READY pin low to inform the external master not to send any more information. When the *SX2* is ready to receive the next byte, the *SX2* pulls the READY pin high again. This next byte, the upper nibble of the data byte, is written to the *SX2* as follows.

Table 5-8. Command Data Write Byte One

| Ad-<br>dress/Da<br>ta# | Don't<br>Care | Don't<br>Care | Don't<br>Care | D7 | D6 | D5 | D4 |

|------------------------|---------------|---------------|---------------|----|----|----|----|

| 0                      | Х             | Х             | Х             | 1  | 0  | 1  | 1  |

- The first bit signifies that this is a data transfer.

- The next three are don't care bits.

- The next four bits hold the upper nibble of the transferred byte.

After the byte has been received the SX2 pulls the READY pin low to inform the external master not to send any more information. When the SX2 is ready to receive the next byte, the SX2pulls the READY pin high again. This next byte, the lower nibble of the data byte is written to the SX2.

#### Table 5-9. Command Data Write Byte Two

| Address<br>Data# | / Don't<br>Care | Don't<br>Care | Don't<br>Care | D3 | D2 | D1 | D0 |

|------------------|-----------------|---------------|---------------|----|----|----|----|

| 0                | Х               | Х             | Х             | 0  | 0  | 0  | 0  |

At this point the entire byte <10110000> is transferred to register 0x01 and the write sequence is complete.

#### Read Request Example

The Read cycle is simpler than the write cycle. The Read cycle consists of a read request from the external master to the SX2. For example, to read the contents of register 0x01, a command address byte is written to the SX2 as follows.

#### Table 5-10. Command Address Read Byte

| Ad-<br>dress/Da<br>ta# | Read/<br>Write# | A5 | A4 | A3 | A2 | A1 | A0 |

|------------------------|-----------------|----|----|----|----|----|----|

| 1                      | 1               | 0  | 0  | 0  | 0  | 0  | 1  |

When the data is ready to be read, the *SX2* asserts the INT# pin to tell the external master that the data it requested is waiting on FD[7:0].<sup>[5]</sup>

#### Note

An important note: Once the SX2 receives a Read request, the SX2 allocates the interrupt line solely for the read request. If one of the six interrupt sources described in Interrupt System on page 3 is asserted, the SX2 buffers that interrupt until the read request completes.

# 6. Enumeration

The *SX2* has two modes of enumeration. The first mode is automatic through EEPROM boot load, as described in Boot Methods on page 2. The second method is a manual load of the descriptor or VID, PID, and DID as described in the following section.

#### 6.1 Standard Enumeration

The *SX2* has 500 bytes of descriptor RAM into which the external master may write its descriptor. The descriptor RAM is accessed through register 0x30. To load a descriptor, the external master does the following:

- Initiate a Write Request to register 0x30.

- Write two bytes (four command data transfers) that define the length of the entire descriptor about to be transferred. The LSB is written first, followed by the MSB.<sup>[6]</sup>

- Write the descriptor, one byte at a time until complete.<sup>[6]</sup> Note: the register address is only written once.

After the entire descriptor has been transferred, the *SX2* floats the pull up resistor connected to D+, and parse through the descriptor to locate the individual descriptors. After the *SX2* has parsed the entire descriptor, the *SX2* connects the pull up resistor and enumerate automatically. When enumeration is complete, the *SX2* notifies the external master with an ENUMOK interrupt.

The format and order of the descriptor should be as follows (see Default Descriptor on page 37 for an example):

- Device.

- Device qualifier.

- High speed configuration, high speed interface, high speed endpoints.

- Full speed configuration, full speed interface, full speed endpoints.

- String.

The SX2 can be set to run in full speed only mode. To force full speed only enumeration write a 0x02 to the unindexed register CT1 at address 0xE6FB before downloading the descriptors. This disables the chirp mechanism forcing the SX2 to come up in full speed only mode after the descriptors are loaded. The CT1 register can be accessed using the unindexed register mechanism. Examples of writing to unindexed registers are shown in Resetting Data Toggle on page 9. Each write consists of a command write with the target register followed by the write of the upper nibble of the value followed by the write of the lower nibble of the value.

## 6.2 Default Enumeration

The external master may simply load a VID, PID, and DID and use the default descriptor built into the *SX2*. To use the default descriptor, the descriptor length described in the previous section must equal 6. After the external master has written the length, the VID, PID, and DID must be written LSB, then MSB. For example, if the VID, PID, and DID are 0x04B4, 0x1002, and 0x0001 respectively, then the external master does the following:

- Initiates a Write Request to register 0x30.

- Writes two bytes (four command data transfers) that define the length of the entire descriptor about to be transferred. In this case, the length is always six.

- Writes the VID, PID, and DID bytes: 0xB4, 0x04, 0x02, 0x10, 0x01, 0x00 (in nibble format per the command protocol).

The default descriptor is listed in Default Descriptor on page 37. The default descriptor can be used as a starting point for a custom descriptor.

# 7. Endpoint 0

The SX2 automatically responds to USB chapter 9 requests without any external master intervention. If the SX2 receives a request to which it cannot respond automatically, the SX2 notifies the external master. The external master then has the choice of responding to the request or stalling.

After the *SX2* receives a setup packet to which it cannot respond automatically, the *SX2* asserts a SETUP interrupt. After the external master reads the Interrupt Status Byte to determine that the interrupt source was the SETUP interrupt, it can initiate a read request to the SETUP register, 0x32. When the *SX2* sees a read request for the SETUP register, it presents the first byte of setup data to the external master. Each additional read request presents the next byte of setup data, until all eight bytes have been read.

The external master can stall this request at this or any other time. To stall a request, the external master initiates a write request for the SETUP register, 0x32, and writes any non-zero value to the register.

If this setup request has a data phase, the SX2 then interrupts the external master with an EP0BUF interrupt when the buffer becomes available. The SX2 determines the direction of the setup request and interrupts when either:

- IN: the Endpoint 0 buffer becomes available to write to, or

- OUT: the Endpoint 0 buffer receives a packet from the USB host.

For an IN setup transaction, the external master can write up to 64 bytes at a time for the data phase. The steps to write a packet are as follows:

- 1. Wait for an EP0BUF interrupt, indicating that the buffer is available.

- 2. Initiate a write request for register 0x31.

- 3. Write one data byte.

- 4. Repeat steps 2 and 3 until either all the data or 64 bytes have been written, whichever is less.

- 5. Write the number of bytes in this packet to the byte count register, 0x33.

#### Note

<sup>6.</sup> These and all other data bytes must conform to the command protocol.

To send more than 64 bytes, the process is repeated. The SX2 internally stores the length of the data phase that was specified in the wLength field (bytes 6,7) of the setup packet. To send less than the requested amount of data, the external master writes a packet that is less than 64 bytes, or if a multiple of 64, the external master follows the data with a zero-length packet. When the SX2 sees a short or zero-length packet, it completes the setup transfer by automatically completing the handshake phase. The SX2 does not enable more data than the wLength field specified in the setup packet. Note: the PKTEND pin does not apply to Endpoint 0. The only way to send a short or zero length packet is by writing to the byte count register with the appropriate value.

For an OUT setup transaction, the external master can read each packet received from the USB host during the data phase. The steps to read a packet are as follows:

- 1. Wait for an EP0BUF interrupt, indicating that a packet was received from the USB host into the buffer.

- 2. Initiate a read request for the byte count register, 0x33. This indicates the amount of data received from the host.

- 3. Initiate a read request for register 0x31.

- 4. Read one byte.

- 5. Repeat steps 3 and 4 until the number of bytes specified in the byte count register has been read.

To receive more than 64 bytes, the process is repeated. The *SX2* internally stores the length of the data phase that was specified in the wLength field of the setup packet (bytes 6,7). When the *SX2* sees that the specified number of bytes have been received, it completes the set up transfer by automatically completing the handshake phase. If the external master does not wish to receive the entire transfer, it can stall the transfer.

If the *SX2* receives another setup packet before the current transfer has completed, it interrupts the external master with another SETUP interrupt. If the *SX2* receives a setup packet with no data phase, the external master can accept the packet and complete the handshake phase by writing zero to the byte count register.

The *SX2* automatically responds to all USB standard requests covered in chapter 9 of the USB 2.0 specification except the Set/Clear Feature Endpoint requests. When the host issues a Set Feature or a Clear feature request, the *SX2* triggers a SETUP interrupt to the external master. The USB spec requires that the device respond to the Set endpoint feature request by doing the following:

■ Set the STALL condition on that endpoint.

The USB spec requires that the device respond to the Clear endpoint feature request by doing the following:

Reset the Data Toggle for that endpoint

■ Clear the STALL condition of that endpoint.

The register that is used to reset the data toggle TOGCTL (located at XDATA location 0xE683) is not an index register that can be addressed by the command protocol presented in Command Protocol on page 7. The following section provides further information on this register bits and how to reset the data toggle accordingly using a different set of command protocol sequence.

#### 7.1 Resetting Data Toggle

| Table 7-1. Bi | it definition | of the | TOGCTL | reaister |

|---------------|---------------|--------|--------|----------|

|---------------|---------------|--------|--------|----------|

| TOGCTL     | - |   |   |     | 0xE683 |     |     |     |

|------------|---|---|---|-----|--------|-----|-----|-----|

| Bit #      | 7 | 6 | 5 | 4   | 3      | 2   | 1   | 0   |

| Bit Name   | Q | S | R | I/O | EP3    | EP2 | EP1 | EP0 |

| Read/Write | R | W | W | R/W | R/W    | R/W | R/W | R/W |

| Default    | 0 | 0 | 1 | 1   | 0      | 0   | 1   | 0   |

#### Bit 7: Q, Data Toggle Value

Q=0 indicates DATA0 and Q=1 indicates DATA1, for the endpoint selected by the I/O and EP3:0 bits. Write the endpoint select bits (IO and EP3:0), before reading this value.

#### Bit 6: S, Set Data Toggle to DATA1

After selecting the desired endpoint by writing the endpoint select bits (IO and EP3:0), set S=1 to set the data toggle to DATA1. The endpoint selection bits should not be changed while this bit is written.

#### Bit 5: R, Set Data Toggle to DATA0

Set R=1 to set the data toggle to DATA0. The endpoint selection bits should not be changed while this bit is written.

#### Bit 4: IO, Select IN or OUT Endpoint

Set this bit to select an endpoint direction prior to setting its R or S bit. IO=0 selects an OUT endpoint, IO = 1 selects an IN endpoint.

#### Bit 3-0: EP3:0, Select Endpoint

Set these bits to select an endpoint prior to setting its R or S bit. Valid values are 0, 1, 2, 6, and 8.

A two-step process is employed to clear an endpoint data toggle bit to 0. First, write to the TOGCTL register with an endpoint address (EP3:EP0) plus a direction bit (IO). Keeping the endpoint and direction bits the same, write a "1" to the R (reset) bit. For example, to clear the data toggle for EP6 configured as an "IN" endpoint, write the following values sequentially to TOGCTL:

#### 00010110b

#### 00110110b

Following is the sequence of events that the master should perform to set this register to 0x16:

#### ■ Send Low Byte of the Register (0x83)

- Command address write of address 0x3A

- Command data write of upper nibble of the Low Byte of Register Address (0x08)

- Command data write of lower nibble of the Low Byte of Register Address (0x03)

- Send High Byte of the Register (0xE6)

- Command address write of address 0x3B

- Command data write of upper nibble of the High Byte of Register Address (0x0E)

- Command data write of lower nibble of the High Byte of Register Address (0x06)

- Send the actual value to write to the register Register (in this case 0x16)

- Command address write of address0x3C

- Command data write of upper nibble of the register value (0x01)

- Command data write of lower nibble of the register value (0x06)

The same command sequence needs to be followed to set TOGCTL register to 0x36. The same command protocol sequence can be used to reset the data toggle for the other endpoints.

In order to read the status of this register, the external master must do the following sequence of events:

- Send Low Byte of the Register (0x83)

- Command address write of 0x3A

- Command data write of upper nibble of the Low Byte of Register Address (0x08)

- Command data write of lower nibble of the Low Byte of Register Address (0x03)

- Send High Byte of the Register (0xE6)

- Command **address** write of address 0x3B

- Command data write of upper nibble of the High Byte of Register Address (0x0E)

- Command data write of lower nibble of the High Byte of Register Address (0x06)

- Get the actual value from the TOGCTL register (0x16) □ Command address READ of 0x3C

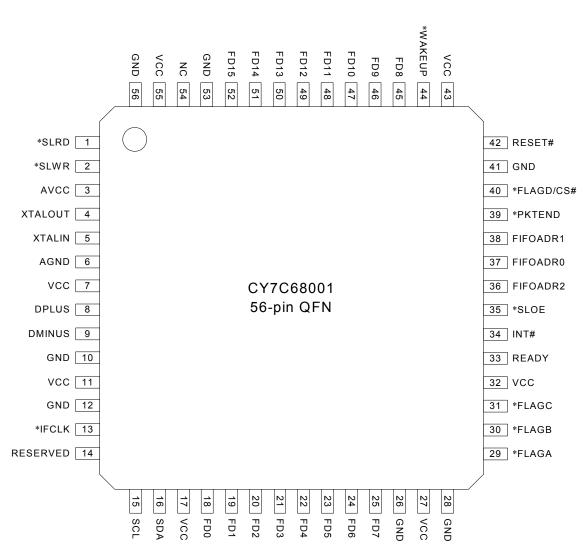

# 8. Pin Configurations

| Figure 8                                                                         | -1. CY7C68001                                                                                 | 56-Pin SSOP Pin Assig                                                                               | nment <sup>[7]</sup>                                                             |

|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1<br>2<br>3<br>4                                                                 | FD13<br>FD14<br>FD15<br>GND                                                                   | FD12<br>FD11<br>FD10<br>FD9                                                                         | 56<br>55<br>54<br>53                                                             |

| 5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13                                    | NC<br>VCC<br>GND<br>*SLRD<br>*SLWR<br>AVCC<br>XTALOUT<br>XTALIN<br>AGND                       | FD8<br>FD8<br>*WAKEUP<br>VCC<br>RESET#<br>GND<br>*FLAGD/CS#<br>*PKTEND<br>FIFOADR1<br>FIFOADR0      | 52<br>51<br>50<br>49<br>48<br>47<br>46<br>45<br>44                               |

| 14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>24<br>25<br>22 | VCC<br>DPLUS<br>DMINUS<br>GND<br>VCC<br>GND<br>*IFCLK<br>RESERVED<br>SCL<br>SDA<br>VCC<br>FD0 | FIFOADR2<br>*SLOE<br>INT#<br>READY<br>VCC<br>*FLAGC<br>*FLAGB<br>*FLAGA<br>GND<br>VCC<br>GND<br>FD7 | 43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35<br>35<br>34<br>33<br>32<br>24 |

| 26<br>27<br>28                                                                   | FD1<br>FD2<br>FD3                                                                             | FD6<br>FD5<br>FD4                                                                                   | 31<br>30<br>29                                                                   |

Figure 8-2. CY7C68001 56-pin QFN Assignment<sup>[7]</sup>

# 8.1 CY7C68001 Pin Definitions

# Table 8-1. SX2 Pin Definitions

| QFN<br>Pin | SSOP<br>Pin | Name          | Туре             | Default | Description                                                                                                                                                                                                                              |

|------------|-------------|---------------|------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | 10          | AVCC          | Power            | N/A     | Analog $V_{CC}$ . This signal provides power to the analog section of the chip.                                                                                                                                                          |

| 6          | 13          | AGND          | Power            | N/A     | Analog Ground. Connect to ground with as short a path as possible.                                                                                                                                                                       |

| 9          | 16          | DMINUS        | I/O/Z            | Z       | USB D- Signal. Connect to the USB D- signal.                                                                                                                                                                                             |

| 8          | 15          | DPLUS         | I/O/Z            | Z       | USB D+ Signal. Connect to the USB D+ signal.                                                                                                                                                                                             |

| 42         | 49          | RESET#        | Input            | N/A     | Active LOW Reset. Resets the entire chip. This pin is normally tied to $V_{CC}$ through a 100K resistor, and to GND through a 0.1-µF capacitor.                                                                                          |

| 5          | 12          | XTALIN        | Input            | N/A     | <b>Crystal Input</b> . Connect this signal to a 24 MHz parallel-resonant, fundamental mode crystal and 20 pF capacitor to GND. It is also correct to drive XTALIN with an external 24 MHz square wave derived from another clock source. |

| 4          | 11          | XTALOUT       | Output           | N/A     | <b>Crystal Output</b> . Connect this signal to a 24 MHz parallel-resonant, fundamental mode crystal and 20 pF capacitor to GND. If an external clock is used to drive XTALIN, leave this pin open.                                       |

| 54         | 5           | NC            | Output           | 0       | No Connect. This pin must be left unconnected.                                                                                                                                                                                           |

|            |             |               |                  |         |                                                                                                                                                                                                                                          |

| 33         | 40          | READY         | Output           | L       | <b>READY</b> is an output-only ready that gates external command reads and writes.<br>Active High.                                                                                                                                       |

| 34         | 41          | INT#          | Output           | Н       | <b>INT#</b> is an output-only external interrupt signal. Active Low.                                                                                                                                                                     |

| 35         | 42          | SLOE          | Input            | I       | <b>SLOE</b> is an input-only output enable with programmable polarity (POLAR.4) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                    |

| 36         | 43          | FIFOADR2      | Input            | I       | <b>FIFOADR2</b> is an input-only address select for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                    |

| 37         | 44          | FIFOADR0      | Input            | I       | <b>FIFOADR0</b> is an input-only address select for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                    |

| 38         | 45          | FIFOADR1      | Input            | I       | <b>FIFOADR1</b> is an input-only address select for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                    |

| 39         | 46          | PKTEND        | Input            | I       | <b>PKTEND</b> is an input-only packet end with programmable polarity (POLAR.5) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                     |

| 40         | 47          | FLAGD/C<br>S# | CS#:I<br>FLAGD:O | I       | <b>FLAGD</b> is a programmable slave-FIFO output status flag signal. CS# is a master chip select (default).                                                                                                                              |

| 18         | 25          | FD[0]         | I/O/Z            | I       | FD[0] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 19         | 26          | FD[1]         | I/O/Z            | I       | FD[1] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 20         | 27          | FD[2]         | I/O/Z            | I       | FD[2] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 21         | 28          | FD[3]         | I/O/Z            | I       | FD[3] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 22         | 29          | FD[4]         | I/O/Z            | I       | FD[4] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 23         | 30          | FD[5]         | I/O/Z            | I       | FD[5] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 24         | 31          | FD[6]         | I/O/Z            | I       | FD[6] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 25         | 32          | FD[7]         | I/O/Z            | I       | FD[7] is the bidirectional FIFO/Command data bus.                                                                                                                                                                                        |

| 45         | 52          | FD[8]         | I/O/Z            | I       | FD[8] is the bidirectional FIFO data bus.                                                                                                                                                                                                |

| 46         | 53          | FD[9]         | I/O/Z            | I       | FD[9] is the bidirectional FIFO data bus.                                                                                                                                                                                                |

| 47         | 54          | FD[10]        | I/O/Z            | I       | FD[10] is the bidirectional FIFO data bus.                                                                                                                                                                                               |

| 48         | 55          | FD[11]        | I/O/Z            | I       | FD[11] is the bidirectional FIFO data bus.                                                                                                                                                                                               |

| 49         | 56          | FD[12]        | I/O/Z            | Ι       | FD[12] is the bidirectional FIFO data bus.                                                                                                                                                                                               |

| 50         | 1           | FD[13]        | I/O/Z            | Ι       | FD[13] is the bidirectional FIFO data bus.                                                                                                                                                                                               |

| 51         | 2           | FD[14]        | I/O/Z            | Ι       | FD[14] is the bidirectional FIFO data bus.                                                                                                                                                                                               |

# Table 8-1. SX2 Pin Definitions (continued)

|    | SSOP<br>Pin | Name            | Туре   | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                   |

|----|-------------|-----------------|--------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 52 | 3           | FD[15]          | I/O/Z  | 1       | FD[15] is the bidirectional FIFO data bus.                                                                                                                                                                                                                                                                                                                                                                    |

| -  | -           | L - J           | -      |         |                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1  | 8           | SLRD            | Input  | N/A     | <b>SLRD</b> is the input-only read strobe with programmable polarity (POLAR.3) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                                                                                                                                                          |

| 2  | 9           | SLWR            | Input  | N/A     | <b>SLWR</b> is the input-only write strobe with programmable polarity (POLAR.2) for the slave FIFOs connected to FD[7:0] or FD[15:0].                                                                                                                                                                                                                                                                         |

| 29 | 36          | FLAGA           | Output | Н       | <b>FLAGA</b> is a programmable slave-FIFO output status flag signal.<br>Defaults to PF for the FIFO selected by the FIFOADR[2:0] pins.                                                                                                                                                                                                                                                                        |

| 30 | 37          | FLAGB           | Output | Н       | <b>FLAGB</b> is a programmable slave-FIFO output status flag signal.<br>Defaults to FULL for the FIFO selected by the FIFOADR[2:0] pins.                                                                                                                                                                                                                                                                      |

| 31 | 38          | FLAGC           | Output | Н       | <b>FLAGC</b> is a programmable slave-FIFO output status flag signal.<br>Defaults to EMPTY for the FIFO selected by the FIFOADR[2:0] pins.                                                                                                                                                                                                                                                                     |

| 13 | 20          | IFCLK           | I/O/Z  | Z       | <b>Interface Clock</b> , used for synchronously clocking data into or out of the slave FIFOs. IFCLK also serves as a timing reference for all slave FIFO control signals. When using the internal clock reference (IFCONFIG.7=1) the IFCLK pin can be configured to output 30/48 MHz by setting bits IFCONFIG.5 and IFCONFIG.6. IFCLK may be inverted by setting the bit IFCONFIG.4=1. Programmable polarity. |

| 14 | 21          | Reserved        | Input  | N/A     | Reserved. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                        |

| 44 | 51          | WAKEUP          | Input  | N/A     | <b>USB Wakeup</b> . If the <i>SX2</i> is in suspend, asserting this pin starts up the oscillator and interrupts the <i>SX2</i> to allow it to exit the suspend mode. During normal operation, holding WAKEUP asserted inhibits the <i>SX2</i> chip from suspending. This pin has programmable polarity (POLAR.7).                                                                                             |

| 15 | 22          | SCL             | OD     | Z       | <b>I<sup>2</sup>C Clock</b> . Connect to $V_{CC}$ with a 2.2K-10 KOhms resistor, even if no I <sup>2</sup> C EEPROM is attached.                                                                                                                                                                                                                                                                              |

| 16 | 23          | SDA             | OD     | Z       | $I^2C$ Data. Connect to V <sub>CC</sub> with a 2.2K-10 KOhms resistor, even if no $I^2C$ EEPROM is attached.                                                                                                                                                                                                                                                                                                  |

|    |             |                 |        |         |                                                                                                                                                                                                                                                                                                                                                                                                               |

| 55 | 6           | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 7  | 14          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 11 | 18          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 17 | 24          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 27 | 34          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 32 | 39          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 43 | 50          | V <sub>CC</sub> | Power  | N/A     | V <sub>CC</sub> . Connect to 3.3V power source.                                                                                                                                                                                                                                                                                                                                                               |

| 53 | 4           | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 56 | 7           | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 10 | 17          | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 12 | 19          | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 26 | 33          | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 28 | 35          | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

| 41 | 48          | GND             | Ground | N/A     | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                            |

# 9. Register Summary

# Table 9-1. SX2 Register Summary

| Hex | x Size Name |                      | Description                                | D7       | D6      | D5                              | D4                              | D3                              | D2      | D1        | D0     | Default  | Access      |

|-----|-------------|----------------------|--------------------------------------------|----------|---------|---------------------------------|---------------------------------|---------------------------------|---------|-----------|--------|----------|-------------|

|     |             | General Config       | guration                                   |          |         |                                 |                                 |                                 |         |           |        |          |             |

| 01  | 1           | IFCONFIG             | Interface Configuration                    | IFCLKSRC | 3048MHZ | IFCLKOE                         | IFCLKPOL                        | ASYNC                           | STANDBY | FLAGD/CS# | DISCON | 11001001 | bbbbbbbb    |

| 02  | 1           | FLAGSAB              | FIFO FLAGA and FLAGB<br>Assignments        | FLAGB3   | FLAGB2  | FLAGB1                          | FLAGB0                          | FLAGA3                          | FLAGA2  | FLAGA1    | FLAGA0 | 00000000 | bbbbbbbb    |

| 03  | 1           | FLAGSCD              | FIFO FLAGC and FLAGD<br>Assignments        | FLAGD3   | FLAGD2  | FLAGD1                          | FLAGD0                          | FLAGC3                          | FLAGC2  | FLAGC1    | FLAGC0 | 00000000 | bbbbbbbb    |

| 04  | 1           | POLAR                | FIFO polarities                            | WUPOL    | 0       | PKTEND                          | SLOE                            | SLRD                            | SLWR    | EF        | FF     | 00000000 | bbbrrrbb    |

| 05  | 1           | REVID                | Chip Revision                              | Major    | Major   | Major                           | Major                           | minor                           | minor   | minor     | minor  | XXXXXXXX | rrrrrr      |

|     |             | Endpoint Conf        | iguration <sup>[9]</sup>                   |          |         |                                 |                                 |                                 |         |           |        |          |             |

| 06  | 1           | EP2CFG               | Endpoint 2 Configuration                   | VALID    | dir     | TYPE1                           | TYPE0                           | SIZE                            | STALL   | BUF1      | BUF0   | 10100010 | bbbbbbbb    |

| 07  | 1           | EP4CFG               | Endpoint 4 Configuration                   | VALID    | dir     | TYPE1                           | TYPE0                           | 0                               | STALL   | 0         | 0      | 10100000 | bbbbrbrr    |

| 08  | 1           | EP6CFG               | Endpoint 6 Configuration                   | VALID    | dir     | TYPE1                           | TYPE0                           | SIZE                            | STALL   | BUF1      | BUF0   | 11100010 | bbbbbbbb    |

| 09  | 1           | EP8CFG               | Endpoint 8 Configuration                   | VALID    | dir     | TYPE1                           | TYPE0                           | 0                               | STALL   | 0         | 0      | 11100000 | bbbbrbrr    |

| 0A  | 1           | EP2PKTLEN<br>H       | Endpoint 2 Packet Length H                 | INFM1    | OEP1    | ZEROLEN                         | WORDWI<br>DE                    | 0                               | PL10    | PL9       | PL8    | 00110010 | bbbbbbbb    |

| 0B  | 1           |                      | Endpoint 2 Packet Length L<br>(IN only)    | PL7      | PL6     | PL5                             | PL4                             | PL3                             | PL2     | PL1       | PL0    |          | bbbbbbbb    |

| 0C  | 1           | EP4PKTLEN<br>H       | Endpoint 4 Packet Length H                 | INFM1    | OEP1    | ZEROLEN                         | WORDWI<br>DE                    | 0                               | 0       | PL9       | PL8    | 00110010 | bbbbbbbb    |

| 0D  | 1           |                      | Endpoint 4 Packet Length L<br>(IN only)    | PL7      | PL6     | PL5                             | PL4                             | PL3                             | PL2     | PL1       | PL0    | 00000000 | bbbbbbbb    |

| 0E  | 1           | Н                    | Endpoint 6 Packet Length H                 | INFM1    | OEP1    |                                 | WORDWI<br>DE                    | 0                               | PL10    | PL9       | PL8    |          | bbbbbbbb    |

| 0F  | 1           |                      | Endpoint 6 Packet Length L<br>(IN only)    | PL7      | PL6     | PL5                             | PL4                             | PL3                             | PL2     | PL1       | PL0    |          | bbbbbbbb    |

| 10  |             | Н                    | Endpoint 8 Packet Length H                 | INFM1    | OEP1    |                                 | WORDWI<br>DE                    | 0                               | 0       | PL9       | PL8    | 00110010 | bbbbbbbb    |

| 11  | 1           | EP8PKTLENL           | Endpoint 8 Packet Length L<br>(IN only)    | PL7      | PL6     | PL5                             | PL4                             | PL3                             | PL2     | PL1       | PL0    | 00000000 | bbbbbbbb    |

| 12  | 1           | EP2PFH               | EP2 Programmable Flag H                    | DECIS    | PKTSTAT | IN:<br>PKTS[2]<br>OUT:PFC<br>12 | IN:<br>PKTS[1]<br>OUT:PFC1<br>1 | IN:<br>PKTS[0]<br>OUT:PFC<br>10 | 0       | PFC9      | PFC8   | 10001000 | bbbbbbbb    |

| 13  | 1           | EP2PFL               | EP2 Programmable Flag L                    | PFC7     | PFC6    | PFC5                            | PFC4                            | PFC3                            | PFC2    | PFC1      | PFC0   | 00000000 | bbbbbbbb    |

| 14  | 1           | EP4PFH               | EP4 Programmable Flag H                    | DECIS    | PKTSTAT | 0                               | IN:<br>PKTS[1]<br>OUT:PFC1<br>0 | IN:<br>PKTS[0]<br>OUT:PFC<br>9  | 0       | 0         | PFC8   | 10001000 | bbbbbbbb    |

| 15  | 1           | EP4PFL               | EP4 Programmable Flag L                    | PFC7     | PFC6    | PFC5                            | PFC4                            | PFC3                            | PFC2    | PFC1      | PFC0   | 00000000 | bbbbbbbb    |

| 16  | 1           |                      | EP6 Programmable Flag H                    | DECIS    | PKTSTAT | IN:<br>PKTS[2]<br>OUT:PFC<br>12 | IN:<br>PKTS[1]<br>OUT:PFC1<br>1 | IN:<br>PKTS[0]<br>OUT:PFC<br>10 | 0       | PFC9      | PFC8   |          | bbbbbbbb    |

| 17  | 1           |                      | EP6 Programmable Flag L                    | PFC7     | PFC6    | PFC5                            | PFC4                            | PFC3                            | PFC2    | PFC1      | PFC0   | 00000000 | bbbbbbbb    |

| 18  | 1           | EP8PFH               | EP8 Programmable Flag H                    | DECIS    | PKTSTAT | 0                               | IN:<br>PKTS[1]<br>OUT:PFC1<br>0 | IN:<br>PKTS[0]<br>OUT:PFC<br>9  | 0       | 0         | PFC8   | 00001000 | bbbbbbbb    |

| 19  | 1           | EP8PFL               | EP8 Programmable Flag L                    | PFC7     | PFC6    | PFC5                            | PFC4                            | PFC3                            | PFC2    | PFC1      | PFC0   | 00000000 | bbbbbbbb    |

| 1A  | 1           |                      | EP2 (if ISO) IN Packets per<br>frame (1-3) | 0        | 0       | 0                               | 0                               | 0                               | 0       | INPPF1    | INPPF0 | 00000001 | bbbbbbbb    |

| 1B  |             | TS                   | EP4 (if ISO) IN Packets per<br>frame (1-3) | 0        | 0       | 0                               | 0                               | 0                               | 0       | INPPF1    | INPPF0 | 00000001 | bbbbbbbb    |

| 1C  |             | TS                   | EP6 (if ISO) IN Packets per frame (1-3)    | 0        | 0       | 0                               | 0                               | 0                               | 0       | INPPF1    | INPPF0 | 00000001 | bbbbbbbb    |

| 1D  | 1           | TS                   | EP8 (if ISO) IN Packets per<br>frame (1-3) | 0        | 0       | 0                               | 0                               | 0                               | 0       | INPPF1    | INPPF0 | 00000001 | bbbbbbbb    |

|     |             | FLAGS                |                                            |          |         |                                 |                                 |                                 |         |           |        |          |             |

| 1E  |             |                      | Endpoints 2,4 FIFO Flags                   | 0        | EP4PF   | EP4EF                           | EP4FF                           | 0                               | EP2PF   | EP2EF     | EP2FF  | 00100010 |             |