# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## PSoC<sup>®</sup> 3: CY8C36 **Automotive Family Datasheet**

## Programmable System-on-Chip (PSoC®

## General Description

With its unique array of configurable blocks, PSoC<sup>®</sup> 3 is a true system level solution providing microcontroller unit (MCU), memory, analog, and digital peripheral functions in a single chip while being AEC-Q100 compliant. The CY8C36 family offers a modern method of signal acquisition, signal processing, and control with high accuracy, high bandwidth, and high flexibility. Analog capability spans the range from thermocouples (near DC voltages) to ultrasonic signals. The CY8C36 family can handle dozens of data acquisition channels and analog inputs on every general-purpose input/output (GPIO) pin. The CY8C36 family is also a high-performance configurable digital system with some part numbers including interfaces such as USB, multimaster inter-integrated circuit (I<sup>2</sup>C), and controller area network (CAN). In addition to communication interfaces, the CY8C36 family has an easy to configure logic array, flexible routing to all I/O pins, and a high-performance single cycle 8051 microprocessor core. You can easily create system-level designs using a rich library of prebuilt components and boolean primitives using PSoC Creator™, a hierarchical schematic design entry tool. The CY8C36 family provides unparalleled opportunities for analog and digital bill of materials integration while easily accommodating last minute design changes through simple firmware updates.

#### Features

- Single cycle 8051 CPU

- DC to 67 MHz operation

- Multiply and divide instructions

- □ Flash program memory, up to 64 KB, 100,000 write cycles, 20 years retention, and multiple security features

- □ 512-byte flash cache

- □ Up to 8-KB flash error correcting code (ECC) or configuration storage

- D Up to 8 KB SRAM

- Up to 2 KB electrically erasable programmable read-only memory (EEPROM), 1 M cycles, and 20 years retention

- □ 24-channel direct memory access (DMA) with multilayer AHB<sup>[1]</sup> bus access

- · Programmable chained descriptors and priorities

- High bandwidth 32-bit transfer support

- Low voltage, ultra low-power

- Wide operating voltage range: 1.71 V to 5.5 V

- 0.8 mA at 3 MHz, 1.2 mA at 6 MHz, and 6.6 mA at 50 MHz Low-power modes including:

- 1-µA sleep mode with real time clock and low-voltage

- detect (LVD) interrupt 200-nA hibernate mode with RAM retention

- Versatile I/O system

- 29 to 72 I/O (62 GPIOs, eight special input/outputs (SIO), two USBIOs<sup>[2]</sup>)

- Any GPIO to any digital or analog peripheral routability

- LCD direct drive from any GPIO, up to  $46 \times 16$  segments<sup>[2]</sup> CapSense<sup>®</sup> support from any GPIO<sup>[3]</sup>

- □ 1.2-V to 5.5-V I/O interface voltages, up to four domains

- Maskable, independent IRQ on any pin or port

- Schmitt-trigger transistor-transistor logic (TTL) inputs

- □ All GPIO configurable as open drain high/low, pull-up/ pull-down, High Z, or strong output

- Configurable GPIO pin state at power-on reset (POR)

- □ 25 mÅ sink on SIO

- Digital peripherals

- □ 20 to 24 programmable logic device (PLD) based universal digital blocks (UDB)

- Full CAN 2.0b 16 Rx, 8 Tx buffers<sup>[2]</sup>

- uSB 2.0 certified Full-Speed (FS) 12 Mbps peripheral interface (TID#40770053) using internal oscillator<sup>[2]</sup>

- Dup to four 16-bit configurable timer, counter, and PWM blocks

- □ 67 MHz, 24-bit fixed point digital filter block (DFB) to implement FIR and IIR filters

- Library of standard peripherals

- 8-, 16-, 24-, and 32-bit timers, counters, and PWMs

Serial peripheral interface (SPI), universal asynchronous transmitter receiver (UART), and I<sup>2</sup>C

- Many others available in catalog

- Library of advanced peripherals

- Cyclic redundancy check (CRC)

- Pseudo random sequence (PRS) generator

- Local interconnect network (LIN) bus 2.0

- Quadrature decoder

- Analog peripherals (1.71 V  $\leq$  VDDA  $\leq$  5.5 V)

- □ 1.024 V ± 0.1% internal voltage reference across –40 °C to +85 °C

- Configurable delta-sigma ADC with 8- to 12-bit resolution

- Sample rates up to 192 ksps

- Programmable gain stage: ×0.25 to ×16 12-bit mode, 192 ksps, 66-dB signal to noise and distortion ratio (SINAD), ±1-bit INL/DNL

- □ Up to four 8-bit, 8-Msps IDACs or 1-Msps VDACs

- Four comparators with 95-ns response time

- D Up to four uncommitted opamps with 25-mA drive capability

- Up to four configurable multifunction analog blocks. Example configurations are programmable gain amplifier (PGA) transimpedance amplifier (TIA), mixer, and sample and hold CapSense support

- Programming, debug, and trace

- □ JTAG (4-wire), serial wire debug (SWD) (2-wire), and single wire viewer (ŚWV) interfaces

- Eight address and one data breakpoint

- 4-KB instruction trace buffer

- Bootloader programming supportable through I<sup>2</sup>C, SPI, UART, USB, and other interfaces

- Precision, programmable clocking

- 3- to 62-MHz internal oscillator over full temperature and voltage range

- 4- to 25-MHz crystal oscillator for crystal PPM accuracy

- Internal PLL clock generation up to 67 MHz

- □ 32.768-kHz watch crystal oscillator

- Low-power internal oscillator at 1, 33, and 100 kHz

- Temperature and packaging □ -40 °C to +85 °C degrees automotive temperature □ -40 °C to +125 °C Extended temperature range

- 48-pin SSOP, and 100-pin TQFP package options

- □ AEC-Q100 compliant.

#### Notes

- AHB AMBA (advanced microcontroller bus architecture) high-performance bus, an ARM data transfer bus This feature on select devices only. See Ordering Information on page 133 for details. GPIOs with opamp outputs are not recommended for use with CapSense.

- 3

## Contents

| 1. Architectural Overview             | 3  |

|---------------------------------------|----|

| 2. Pinouts                            | 5  |

| 3. Pin Descriptions                   | 9  |

| 4. CPU                                | 10 |

| 4.1 8051 CPU                          | 10 |

| 4.2 Addressing Modes                  | 10 |

| 4.3 Instruction Set                   |    |

| 4.4 DMA and PHUB                      |    |

| 4.5 Interrupt Controller              |    |

| 5. Memory                             | 21 |

| 5.1 Static RAM                        |    |

| 5.2 Flash Program Memory              |    |

| 5.3 Flash Security                    |    |

| 5.4 EEPROM                            |    |

| 5.5 Nonvolatile Latches (NVLs)        |    |

| 5.6 External Memory Interface         |    |

| 5.7 Memory Map                        |    |

| 6. System Integration                 |    |

| 6.1 Clocking System                   |    |

| 6.2 Power System<br>6.3 Reset         |    |

| 6.4 I/O System and Routing            |    |

| 7. Digital Subsystem                  |    |

| 7.1 Example Peripherals               |    |

| 7.2 Universal Digital Block           |    |

| 7.3 UDB Array Description             |    |

| 7.4 DSI Routing Interface Description |    |

| 7.5 CAN                               |    |

| 7.6 USB                               | 49 |

| 7.7 Timers, Counters, and PWMs        | 49 |

| 7.8 l <sup>2</sup> C                  | 50 |

| 7.9 Digital Filter Block              | 51 |

| 8. Analog Subsystem                   | 51 |

| 8.1 Analog Routing                    |    |

| 8.2 Delta-sigma ADC                   |    |

| 8.3 Comparators                       |    |

| 8.4 Opamps                            |    |

| 8.5 Programmable SC/CT Blocks         | 56 |

|       | 8.6 LCD Direct Drive                                   | 57 |

|-------|--------------------------------------------------------|----|

|       | 8.7 CapSense                                           |    |

|       | 8.8 Temp Sensor                                        |    |

|       | 8.9 DAC                                                |    |

|       | 8.10 Up/Down Mixer                                     |    |

|       | 8.11 Sample and Hold                                   |    |

| 9. F  | Programming, Debug Interfaces, Resources               |    |

|       | 9.1 JTAG Interface                                     |    |

|       | 9.2 Serial Wire Debug Interface                        |    |

|       | 9.3 Debug Features                                     |    |

|       | 9.4 Trace Features<br>9.5 Single Wire Viewer Interface |    |

|       | 9.6 Programming Features                               |    |

|       | 9.7 Device Security                                    |    |

| 40    | -                                                      |    |

| 10.   | Development Support                                    |    |

|       | 10.2 Online                                            |    |

|       | 10.3 Tools                                             |    |

| 11    | Electrical Specifications                              |    |

| • • • | 11.1 Absolute Maximum Ratings                          |    |

|       | 11.2 Device Level Specifications                       |    |

|       | 11.3 Power Regulators                                  |    |

|       | 11.4 Inputs and Outputs                                |    |

|       | 11.5 Analog Peripherals                                |    |

|       | 11.6 Digital Peripherals1                              | 14 |

|       | 11.7 Memory1                                           |    |

|       | 11.8 PSoC System Resources1                            |    |

|       | 11.9 Clocking1                                         |    |

| 12.   | Ordering Information1                                  |    |

|       | 12.1 Part Numbering Conventions1                       | 35 |

| 13.   | Packaging1                                             | 36 |

| 14.   | Acronyms1                                              | 38 |

|       | Reference Documents1                                   |    |

|       | Document Conventions1                                  |    |

|       | 16.1 Units of Measure                                  |    |

| 17.   | Revision History1                                      |    |

|       | Sales, Solutions, and Legal Information1               |    |

|       |                                                        |    |

## 1. Architectural Overview

Introducing the CY8C36 family of ultra low-power, flash Programmable System-on-Chip (PSoC<sup>®</sup>) devices, part of a scalable 8-bit PSoC 3 and 32-bit PSoC 5 platform. The CY8C36 family provides configurable blocks of analog, digital, and interconnect circuitry around a CPU subsystem. The combination of a CPU with a flexible analog subsystem, digital subsystem, routing, and I/O enables a high level of integration in a wide variety of automotive consumer, industrial, and medical applications.

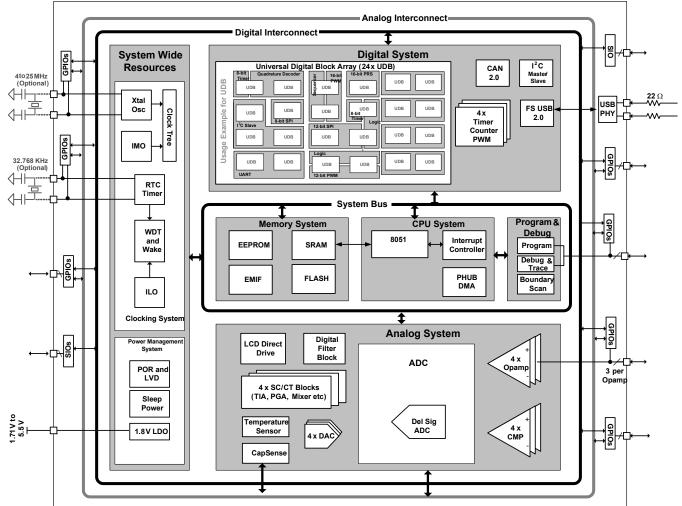

#### Figure 1-1. Simplified Block Diagram

Figure 1-1 illustrates the major components of the CY8C36 family. They are:

- 8051 CPU subsystem

- Nonvolatile subsystem

- Programming, debug, and test subsystem

- Inputs and outputs

- Clocking

- Power

- Digital subsystem

- Analog subsystem

PSoC's digital subsystem provides half of its unique configurability. It connects a digital signal from any peripheral to any pin through the digital system interconnect (DSI). It also provides functional flexibility through an array of small, fast, low-power UDBs. PSoC Creator provides a library of prebuilt and tested standard digital peripherals (UART, SPI, LIN, PRS, CRC, timer, counter, PWM, AND, OR, and so on) that are mapped to the UDB array. You can also easily create a digital circuit using boolean primitives by means of graphical design entry. Each UDB contains programmable array logic (PAL)/programmable logic device (PLD) functionality, together with a small state machine engine to support a wide variety of peripherals.

In addition to the flexibility of the UDB array, PSoC also provides configurable digital blocks targeted at specific functions. For the CY8C36 family these blocks can include four 16-bit timers, counters, and PWM blocks; I<sup>2</sup>C slave, master, and multimaster; FS USB; and Full CAN 2.0b.

For more details on the peripherals see the "Example Peripherals" section on page 40 of this data sheet. For information on UDBs, DSI, and other digital blocks, see the "Digital Subsystem" section on page 40 of this data sheet.

PSoC's analog subsystem is the second half of its unique configurability. All analog performance is based on a highly accurate absolute voltage reference with less than 0.1-percent error over temperature and voltage. The configurable analog subsystem includes:

- Analog muxes

- Comparators

- Voltage references

- Analog-to-digital converter (ADC)

- Digital-to-analog converters (DACs)

- Digital filter block (DFB)

All GPIO pins can route analog signals into and out of the device using the internal analog bus. This allows the device to interface up to 62 discrete analog signals. The heart of the analog subsystem is a fast, accurate, configurable delta-sigma ADC with these features <sup>[4]</sup>:

- Less than 100 µV offset

- A gain error of 0.2 percent

- INL less than ±2 LSB

- DNL less than ±1 LSB

- SINAD better than 84 dB in 16-bit mode

This converter addresses a wide variety of precision analog applications, including some of the most demanding sensors. The output of the ADC can optionally feed the programmable DFB through the DMA without CPU intervention. You can configure the DFB to perform IIR and FIR digital filters and several user-defined custom functions. The DFB can implement filters with up to 64 taps. It can perform a 48-bit multiply-accumulate (MAC) operation in one clock cycle.

Four high-speed voltage or current DACs support 8-bit output signals at an update rate of up to 8 Msps. They can be routed out of any GPIO pin. You can create higher resolution voltage PWM DAC outputs using the UDB array. This can be used to create a pulse width modulated (PWM) DAC of up to 10 bits, at up to 48 kHz. The digital DACs in each UDB support PWM, PRS, or delta-sigma algorithms with programmable widths. In addition to the ADC, DACs, and DFB, the analog subsystem provides multiple:

- Uncommitted opamps

- Configurable switched capacitor/continuous time (SC/CT) blocks. These support:

- Transimpedance amplifiers

- Programmable gain amplifiers

- Mixers

- Dother similar analog components

See the "Analog Subsystem" section on page 51 of this data sheet for more details.

PSoC's 8051 CPU subsystem is built around a single cycle pipelined 8051 8-bit processor running at up to 67 MHz. The CPU subsystem includes a programmable nested vector interrupt controller, DMA controller, and RAM. PSoC's nested vector interrupt controller provides low latency by allowing the CPU to vector directly to the first address of the interrupt service routine, bypassing the jump instruction required by other architectures. The DMA controller enables peripherals to exchange data without CPU involvement. This allows the CPU to run slower (saving power) or use those CPU cycles to improve the performance of firmware algorithms. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor. The processor speed itself is configurable, allowing you to tune active power consumption for specific applications.

PSoC's nonvolatile subsystem consists of flash, byte-writeable EEPROM, and nonvolatile configuration options. It provides up to 64 KB of on-chip flash. The CPU can reprogram individual blocks of flash, enabling bootloaders. You can enable an error correcting code (ECC) for high reliability applications. A powerful and flexible protection model secures the user's sensitive information, allowing selective memory block locking for read and write protection. Up to 2 KB of byte-writeable EEPROM is available on-chip to store application data. Additionally, selected configuration options such as boot speed and pin drive mode are stored in nonvolatile memory. This allows settings to activate immediately after POR.

The three types of PSoC I/O are extremely flexible. All I/Os have many drive modes that are set at POR. PSoC also provides up to four I/O voltage domains through the VDDIO pins. Every GPIO has analog I/O, LCD drive<sup>[5]</sup>, CapSense<sup>[6]</sup>, flexible interrupt generation, slew rate control, and digital I/O capability. The SIOs on PSoC allow V<sub>OH</sub> to be set independently of Vddio when used as outputs. When SIOs are in input mode they are high impedance. This is true even when the device is not powered or when the pin voltage goes above the supply voltage. This makes the SIO ideally suited for use on an I<sup>2</sup>C bus where the PSoC may not be powered when other devices on the bus are. The SIO pins also have high current sink capability for applications such as LED drives. The programmable input threshold feature of the SIO can be used to make the SIO function as a general purpose analog comparator. For devices with Full-Speed USB the USB physical interface is also provided (USBIO). When not using USB these pins may also be used for limited digital functionality and device programming. All of the features of the PSoC I/Os are covered in detail in the "I/O System and Routing" section on page 33 of this data sheet.

The PSoC device incorporates flexible internal clock generators, designed for high stability and factory trimmed for high accuracy. The internal main oscillator (IMO) is the clock base for the system, and has 1-percent accuracy at 3 MHz. The IMO can be configured to run from 3 MHz up to 62 MHz. Multiple clock derivatives can be generated from the main clock frequency to meet application needs. The device provides a PLL to generate clock frequencies up to 67 MHz from the IMO, external crystal, or external reference clock.

#### Notes

<sup>4.</sup> Refer Electrical Specifications on page 65 for the detailed ADC specification across entire voltage range and temperature.

<sup>5.</sup> This feature on select devices only. See Ordering Information on page 133 for details.

<sup>6.</sup> GPIOs with opamp outputs are not recommended for use with CapSense.

It also contains a separate, very low-power internal low-speed oscillator (ILO) for the sleep and watchdog timers. A 32.768-kHz external watch crystal is also supported for use in real-time clock (RTC) applications. The clocks, together with programmable clock dividers, provide the flexibility to integrate most timing requirements.

The CY8C36 family supports a wide supply operating range from 1.71 V to 5.5 V. This allows operation from regulated supplies such as 1.8 V  $\pm$  5%, 2.5 V  $\pm$ 10%, 3.3 V  $\pm$  10%, or 5.0 V  $\pm$  10%, or directly from a wide range of battery types.

PSoC supports a wide range of low-power modes. These include a 200-nA hibernate mode with RAM retention and a 1- $\mu$ A sleep mode with RTC. In the second mode, the optional 32.768-kHz watch crystal runs continuously and maintains an accurate RTC.

Power to all major functional blocks, including the programmable digital and analog peripherals, can be controlled independently by firmware. This allows low-power background processing when some peripherals are not in use. This, in turn, provides a total device current of only 1.2 mA when the CPU is running at 6 MHz, or 0.8 mA running at 3 MHz.

The details of the PSoC power modes are covered in the "Power System" section on page 29 of this data sheet.

PSoC uses JTAG (4-wire) or SWD (2-wire) interfaces for programming, debug, and test. The 1-wire SWV may also be used for 'printf' style debugging. By combining SWD and SWV, you can implement a full debugging interface with just three pins. Using these standard interfaces you can debug or program the PSoC with a variety of hardware solutions from Cypress or third party vendors. PSoC supports on-chip break points and 4-KB instruction and data race memory for debug. Details of the programming, test, and debugging interfaces are discussed in the "Programming, Debug Interfaces, Resources" section on page 60 of this data sheet.

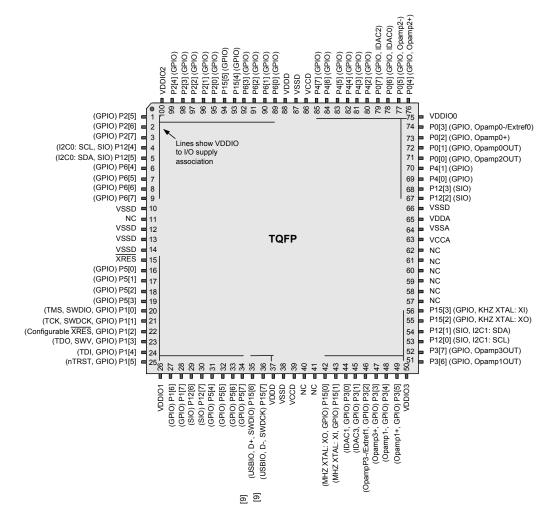

## 2. Pinouts

Each VDDIO pin powers a specific set of I/O pins. (The USBIOs are powered from VDDD.) Using the VDDIO pins, a single PSoC can support multiple voltage levels, reducing the need for off-chip level shifters. The black lines drawn on the pinout diagrams in Figure 2-3 through Figure 2-4 show the pins that are powered by each VDDIO.

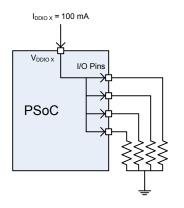

Each VDDIO may source up to 100 mA <sup>[7]</sup> total to its associated I/O pins, as shown in Figure 2-1.

#### Figure 2-1. VDDIO Current Limit

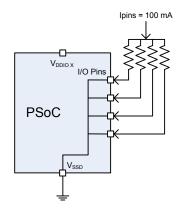

Conversely, for the 100-pin and 68-pin devices, the set of I/O pins associated with any VDDIO may sink up to 100 mA  $^{[7]}$  total, as shown in Figure 2-2.

#### Figure 2-2. I/O Pins Current Limit

For the 48-pin devices, the set of I/O pins associated with VDDIO0 plus VDDIO2 may sink up to 100 mA<sup>[7]</sup> total. The set of I/O pins associated with VDDIO1 plus VDDIO3 may sink up to a total of 100 mA.

Note

The 100 mA source/ sink current per Vddio is valid only for temperature range of -40 °C to +85 °C. For extended temperature range of -40 °C to +125 °C, the maximum source or sink current per Vddio is 40 mA.

#### Figure 2-3. 48-pin SSOP Part Pinout

#### Figure 2-4. 100-pin TQFP Part Pinout

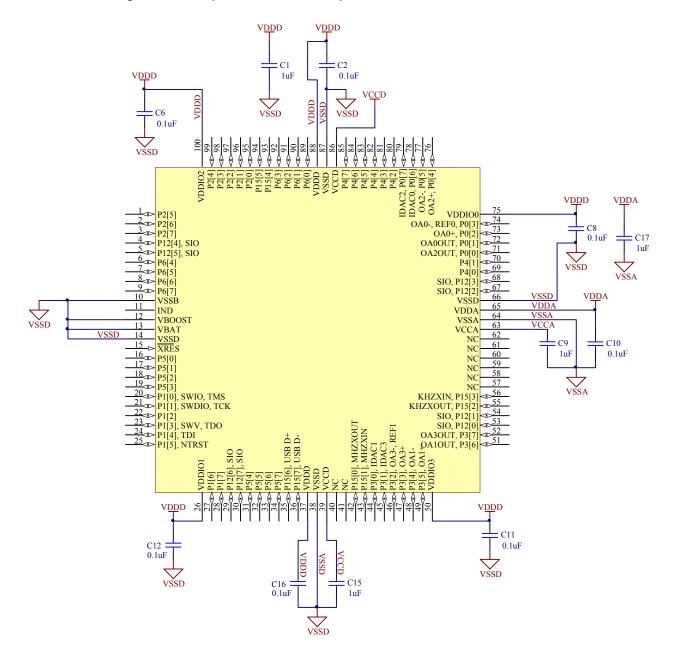

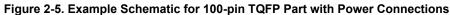

Figure 2-5 and Figure 2-6 show an example schematic and an example PCB layout, for the 100-pin TQFP part, for optimal analog performance on a two-layer board.

- The two pins labeled VDDD must be connected together.

- The two pins labeled VCCD must be connected together, with capacitance added, as shown in Figure 2-5 and Power System on page 29. The trace between the two VCCD pins should be as short as possible.

- The two pins labeled Vssd must be connected together.

For information on circuit board layout issues for mixed signals, refer to the application note, AN57821 - Mixed Signal Circuit Board Layout Considerations for PSoC® 3 and PSoC 5.

**Note** The two Vccd pins must be connected together with as short a trace as possible. A trace under the device is recommended, as shown in Figure 2-6 on page 9.

#### Figure 2-6. Example PCB Layout for 100-pin TQFP Part for Optimal Analog Performance

## 3. Pin Descriptions

#### IDAC0, IDAC1, IDAC2, IDAC3

Low resistance output pin for high current DACs (IDAC).

#### Opamp0OUT, Opamp1OUT, Opamp2OUT, Opamp3OUT

High current output of uncommitted opamp<sup>[10]</sup>.

#### Extref0, Extref1

External reference input to the analog system.

#### Opamp0–, Opamp1–, Opamp2–, Opamp3–

Inverting input to uncommitted opamp.

#### Opamp0+, Opamp1+, Opamp2+, Opamp3+

Noninverting input to uncommitted opamp.

#### GPIO

General purpose I/O pin provides interfaces to the CPU, digital peripherals, analog peripherals, interrupts, LCD segment drive, and CapSense<sup>[10]</sup>.

#### I2C0: SCL, I2C1: SCL

$I^2C$  SCL line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SCL if wake from sleep is not required.

#### I2C0: SDA, I2C1: SDA

$I^2C$  SDA line providing wake from sleep on an address match. Any I/O pin can be used for  $I^2C$  SDA if wake from sleep is not required.

#### kHz XTAL: Xo, kHz XTAL: Xi

32.768-kHz crystal oscillator pin.

#### MHz XTAL: Xo, MHz XTAL: Xi

4- to 25-MHz crystal oscillator pin.

#### nTRST

Optional JTAG test reset programming and debug port connection to reset the JTAG connection.

#### SIO

Special I/O provides interfaces to the CPU, digital peripherals and interrupts with a programmable high threshold voltage, analog comparator, high sink current, and high impedance state when the device is unpowered.

#### SWDCK

Serial wire debug clock programming and debug port connection.

#### SWDIO

Serial wire debug input and output programming and debug port connection.

#### SWV

Single wire viewer debug output.

#### тск

JTAG test clock programming and debug port connection.

#### TDI

JTAG test data in programming and debug port connection.

#### TDO

JTAG test data out programming and debug port connection.

#### TMS

JTAG test mode select programming and debug port connection.

#### Note

10. GPIOs with opamp outputs are not recommended for use with CapSense.

#### USBIO, D+

Provides D+ connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

#### USBIO, D-

Provides D– connection directly to a USB 2.0 bus. May be used as a digital I/O pin; it is powered from VDDD instead of from a VDDIO. Pins are Do Not Use (DNU) on devices without USB.

#### VCCA.

Output of the analog core regulator or the input to the analog core. Requires a 1uF capacitor to VSSA. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator, (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 29.

#### VCCD.

Output of the digital core regulator or the input to the digital core. The two VCCD pins must be shorted together, with the trace between them as short as possible, and a 1uF capacitor to VSSD. The regulator output is not designed to drive external circuits. Note that if you use the device with an external core regulator (externally regulated mode), the voltage applied to this pin must not exceed the allowable range of 1.71 V to 1.89 V. When using the internal core regulator (internally regulated mode, the default), do not tie any power to this pin. For details see Power System on page 29.

#### VDDA

Supply for all analog peripherals and analog core regulator. VDDA must be the highest voltage present on the device. All other supply pins must be less than or equal to VDDA.

#### VDDD

Supply for all digital peripherals and digital core regulator. VDDD must be less than or equal to VDDA.

#### VSSA

Ground for all analog peripherals.

#### VSSD

Ground for all digital logic and I/O pins.

#### VDDIO0, VDDIO1, VDDIO2, VDDIO3

Supply for I/O pins. Each VDDIO must be tied to a valid operating voltage (1.71 V to 5.5 V), and must be less than or equal to VDDA.

#### XRES (and configurable XRES)

External reset pin. Active low with internal pull-up. Pin P1[2] may be configured to be a XRES pin; see "Nonvolatile Latches (NVLs)" on page 22.

## 4. CPU

#### 4.1 8051 CPU

The CY8C36 devices use a single cycle 8051 CPU, which is fully compatible with the original MCS-51 instruction set. The CY8C36 family uses a pipelined RISC architecture, which executes most instructions in 1 to 2 cycles to provide peak performance of up to 33 MIPS with an average of 2 cycles per instruction. The single cycle 8051 CPU runs ten times faster than a standard 8051 processor.

The 8051 CPU subsystem includes these features:

- Single cycle 8051 CPU

- Up to 64 KB of flash memory, up to 2 KB of EEPROM, and up to 8 KB of SRAM

- 512-byte instruction cache between CPU and flash

- Programmable nested vector interrupt controller

- DMA controller

- Peripheral HUB (PHUB)

- External memory interface (EMIF)

#### 4.2 Addressing Modes

The following addressing modes are supported by the 8051:

- Direct Addressing: The operand is specified by a direct 8-bit address field. Only the internal RAM and the SFRs can be accessed using this mode.

- Indirect Addressing: The instruction specifies the register which contains the address of the operand. The registers R0 or R1 are used to specify the 8-bit address, while the data pointer (DPTR) register is used to specify the 16-bit address.

- Register Addressing: Certain instructions access one of the registers (R0 to R7) in the specified register bank. These instructions are more efficient because there is no need for an address field.

- Register Specific Instructions: Some instructions are specific to certain registers. For example, some instructions always act on the accumulator. In this case, there is no need to specify the operand.

- Immediate Constants: Some instructions carry the value of the constants directly instead of an address.

- Indexed Addressing: This type of addressing can be used only for a read of the program memory. This mode uses the Data Pointer as the base and the accumulator value as an offset to read a program memory.

- Bit Addressing: In this mode, the operand is one of 256 bits.

#### 4.3 Instruction Set

The 8051 instruction set is highly optimized for 8-bit handling and Boolean operations. The types of instructions supported include:

- Arithmetic instructions

- Logical instructions

- Data transfer instructions

- Boolean instructions

#### Program branching instructions

#### 4.3.1 Instruction Set Summary

#### 4.3.1.1 Arithmetic Instructions

Arithmetic instructions support the direct, indirect, register, immediate constant, and register-specific instructions. Arithmetic modes are used for addition, subtraction, multiplication, division, increment, and decrement operations. Table 4-1 lists the different arithmetic instructions.

| Mnemonic       | Description                                          | Bytes | Cycles |

|----------------|------------------------------------------------------|-------|--------|

| ADD A,Rn       | Add register to accumulator                          | 1     | 1      |

| ADD A,Direct   | Add direct byte to accumulator                       | 2     | 2      |

| ADD A,@Ri      | Add indirect RAM to accumulator                      | 1     | 2      |

| ADD A,#data    | Add immediate data to accumulator                    | 2     | 2      |

| ADDC A,Rn      | Add register to accumulator with carry               | 1     | 1      |

| ADDC A, Direct | Add direct byte to accumulator with carry            | 2     | 2      |

| ADDC A,@Ri     | Add indirect RAM to accumulator with carry           | 1     | 2      |

| ADDC A,#data   | Add immediate data to accumulator with carry         | 2     | 2      |

| SUBB A,Rn      | Subtract register from accumulator with borrow       | 1     | 1      |

| SUBB A, Direct | Subtract direct byte from accumulator with borrow    | 2     | 2      |

| SUBB A,@Ri     | Subtract indirect RAM from accumulator with borrow   | 1     | 2      |

| SUBB A,#data   | Subtract immediate data from accumulator with borrow | 2     | 2      |

| INC A          | Increment accumulator                                | 1     | 1      |

| INC Rn         | Increment register                                   | 1     | 2      |

| INC Direct     | Increment direct byte                                | 2     | 3      |

| INC @Ri        | Increment indirect RAM                               | 1     | 3      |

| DEC A          | Decrement accumulator                                | 1     | 1      |

| DEC Rn         | Decrement register                                   | 1     | 2      |

| DEC Direct     | Decrement direct byte                                | 2     | 3      |

| DEC @Ri        | Decrement indirect RAM                               | 1     | 3      |

| INC DPTR       | Increment data pointer                               | 1     | 1      |

| MUL            | Multiply accumulator and B                           | 1     | 2      |

| DIV            | Divide accumulator by B                              | 1     | 6      |

| DAA            | Decimal adjust accumulator                           | 1     | 3      |

#### Table 4-1. Arithmetic Instructions

#### 4.3.1.2 Logical Instructions

The logical instructions perform Boolean operations such as AND, OR, XOR on bytes, rotate of accumulator contents, and swap of nibbles in an accumulator. The Boolean operations on the bytes are performed on the bit-by-bit basis. Table 4-2 shows the list of logical instructions and their description.

#### Table 4-2. Logical Instructions

|     | Mnemonic      | Description                           | Bytes | Cycles |

|-----|---------------|---------------------------------------|-------|--------|

| ANL | A,Rn          | AND register to accumulator           | 1     | 1      |

| ANL | A,Direct      | AND direct byte to accumulator        | 2     | 2      |

| ANL | A,@Ri         | AND indirect RAM to accumulator       | 1     | 2      |

| ANL | A,#data       | AND immediate data to accumulator     | 2     | 2      |

| ANL | Direct, A     | AND accumulator to direct byte        | 2     | 3      |

| ANL | Direct, #data | AND immediate data to direct byte     | 3     | 3      |

| ORL | A,Rn          | OR register to accumulator            | 1     | 1      |

| ORL | A,Direct      | OR direct byte to accumulator         | 2     | 2      |

| ORL | A,@Ri         | OR indirect RAM to accumulator        | 1     | 2      |

| ORL | A,#data       | OR immediate data to accumulator      | 2     | 2      |

| ORL | Direct, A     | OR accumulator to direct byte         | 2     | 3      |

| ORL | Direct, #data | OR immediate data to direct byte      | 3     | 3      |

| XRL | A,Rn          | XOR register to accumulator           | 1     | 1      |

| XRL | A,Direct      | XOR direct byte to accumulator        | 2     | 2      |

| XRL | A,@Ri         | XOR indirect RAM to accumulator       | 1     | 2      |

| XRL | A,#data       | XOR immediate data to accumulator     | 2     | 2      |

| XRL | Direct, A     | XOR accumulator to direct byte        | 2     | 3      |

| XRL | Direct, #data | XOR immediate data to direct byte     | 3     | 3      |

| CLR | А             | Clear accumulator                     | 1     | 1      |

| CPL | А             | Complement accumulator                | 1     | 1      |

| RL  | А             | Rotate accumulator left               | 1     | 1      |

| RLC | А             | Rotate accumulator left through carry | 1     | 1      |

| RR  | А             | Rotate accumulator right              | 1     | 1      |

| RRC | А             | Rotate accumulator right though carry | 1     | 1      |

| SWA | PA            | Swap nibbles within accumulator       | 1     | 1      |

#### 4.3.1.3 Data Transfer Instructions

The data transfer instructions are of three types: the core RAM, xdata RAM, and the lookup tables. The core RAM transfer includes transfer between any two core RAM locations or SFRs. These instructions can use direct, indirect, register, and immediate addressing. The xdata RAM transfer includes only the transfer between the accumulator and the xdata RAM location. It can use only indirect addressing. The lookup tables involve nothing but the read of program memory using the Indexed

addressing mode. Table 4-3 lists the various data transfer instructions available.

#### 4.3.1.4 Boolean Instructions

The 8051 core has a separate bit-addressable memory location. It has 128 bits of bit addressable RAM and a set of SFRs that are bit addressable. The instruction set includes the whole menu of bit operations such as move, set, clear, toggle, OR, and AND instructions and the conditional jump instructions. Table 4-4 lists the available Boolean instructions.

#### Table 4-3. Data Transfer Instructions

| Mr       | nemonic       | Description                                            | Bytes | Cycles |

|----------|---------------|--------------------------------------------------------|-------|--------|

| MOV A,F  | Rn            | Move register to accumulator                           | 1     | 1      |

| MOV A,I  | Direct        | Move direct byte to accumulator                        | 2     | 2      |

| MOV A,(  | @Ri           | Move indirect RAM to accumulator                       | 1     | 2      |

| MOV A,#  | #data         | Move immediate data to accumulator                     | 2     | 2      |

| MOV Rn   | n,A           | Move accumulator to register                           | 1     | 1      |

| MOV Rn   | n,Direct      | Move direct byte to register                           | 2     | 3      |

| MOV Rn   | n, #data      | Move immediate data to register                        | 2     | 2      |

| MOV Dir  | irect, A      | Move accumulator to direct byte                        | 2     | 2      |

| MOV Dir  | irect, Rn     | Move register to direct byte                           | 2     | 2      |

| MOV Dir  | irect, Direct | Move direct byte to direct byte                        | 3     | 3      |

| MOV Dir  | irect, @Ri    | Move indirect RAM to direct byte                       | 2     | 3      |

| MOV Dir  | irect, #data  | Move immediate data to direct byte                     | 3     | 3      |

| MOV @    | Ri, A         | Move accumulator to indirect RAM                       | 1     | 2      |

| MOV @    | Ri, Direct    | Move direct byte to indirect RAM                       | 2     | 3      |

| MOV @    | Ri, #data     | Move immediate data to indirect RAM                    | 2     | 2      |

| MOV DF   | PTR, #data16  | Load data pointer with 16 bit constant                 | 3     | 3      |

| MOVC A,  | , @A+DPTR     | Move code byte relative to DPTR to accumulator         | 1     | 5      |

| MOVC A,  | , @A + PC     | Move code byte relative to PC to accumulator           | 1     | 4      |

| MOVX A,  | ,@Ri          | Move external RAM (8-bit) to accumulator               | 1     | 4      |

| MOVX A,  | , @DPTR       | Move external RAM (16-bit) to accumulator              | 1     | 3      |

| MOVX @   | )Ri, A        | Move accumulator to external RAM (8-bit)               | 1     | 5      |

| MOVX @   | )DPTR, A      | Move accumulator to external RAM (16-bit)              | 1     | 4      |

| PUSH Dir | rect          | Push direct byte onto stack                            | 2     | 3      |

| POP Di   | irect         | Pop direct byte from stack                             | 2     | 2      |

| XCH A,   | , Rn          | Exchange register with accumulator                     | 1     | 2      |

| XCH A,   | , Direct      | Exchange direct byte with accumulator                  | 2     | 3      |

| XCH A,   | , @Ri         | Exchange indirect RAM with accumulator                 | 1     | 3      |

| XCHD A,  | @Ri           | Exchange low order indirect digit RAM with accumulator | 1     | 3      |

#### Table 4-4. Boolean Instructions

| Mnemonic   | Description             | Bytes | Cycles |

|------------|-------------------------|-------|--------|

| CLR C      | Clear carry             | 1     | 1      |

| CLR bit    | Clear direct bit        | 2     | 3      |

| SETB C     | Set carry               | 1     | 1      |

| SETB bit   | Set direct bit          | 2     | 3      |

| CPL C      | Complement carry        | 1     | 1      |

| CPL bit    | Complement direct bit   | 2     | 3      |

| ANL C, bit | AND direct bit to carry | 2     | 2      |

#### Table 4-4. Boolean Instructions (continued)

| Mnemonic     | Description                             | Bytes | Cycles |

|--------------|-----------------------------------------|-------|--------|

| ANL C, /bit  | AND complement of direct bit to carry   | 2     | 2      |

| ORL C, bit   | OR direct bit to carry                  | 2     | 2      |

| ORL C, /bit  | OR complement of direct bit to carry    | 2     | 2      |

| MOV C, bit   | Move direct bit to carry                | 2     | 2      |

| MOV bit, C   | Move carry to direct bit                | 2     | 3      |

| JC rel       | Jump if carry is set                    | 2     | 3      |

| JNC rel      | Jump if no carry is set                 | 2     | 3      |

| JB bit, rel  | Jump if direct bit is set               | 3     | 5      |

| JNB bit, rel | Jump if direct bit is not set           | 3     | 5      |

| JBC bit, rel | Jump if direct bit is set and clear bit | 3     | 5      |

#### 4.3.1.5 Program Branching Instructions

The 8051 supports a set of conditional and unconditional jump instructions that help to modify the program execution flow. Table 4-5 shows the list of jump instructions.

#### Table 4-5. Jump Instructions

| Mnemonic             | Description                                                                | Bytes | Cycles |

|----------------------|----------------------------------------------------------------------------|-------|--------|

| ACALL addr11         | Absolute subroutine call                                                   | 2     | 4      |

| LCALL addr16         | Long subroutine call                                                       | 3     | 4      |

| RET                  | Return from subroutine                                                     | 1     | 4      |

| RETI                 | Return from interrupt                                                      | 1     | 4      |

| AJMP addr11          | Absolute jump                                                              | 2     | 3      |

| LJMP addr16          | Long jump                                                                  | 3     | 4      |

| SJMP rel             | Short jump (relative address)                                              | 2     | 3      |

| JMP @A + DPTR        | Jump indirect relative to DPTR                                             | 1     | 5      |

| JZ rel               | Jump if accumulator is zero                                                | 2     | 4      |

| JNZ rel              | Jump if accumulator is nonzero                                             |       | 4      |

| CJNE A,Direct, rel   | irect, rel Compare direct byte to accumulator and jump if not equal        |       | 5      |

| CJNE A, #data, rel   | rel Compare immediate data to accumulator and jump if not equal            |       | 4      |

| CJNE Rn, #data, rel  | #data, rel Compare immediate data to register and jump if not equal        |       | 4      |

| CJNE @Ri, #data, rel | i, #data, rel Compare immediate data to indirect RAM and jump if not equal |       | 5      |

| DJNZ Rn,rel          | Decrement register and jump if not zero                                    | 2     | 4      |

| DJNZ Direct, rel     | Decrement direct byte and jump if not zero                                 | 3     | 5      |

| NOP                  | No operation                                                               | 1     | 1      |

#### 4.4 DMA and PHUB

The PHUB and the DMA controller are responsible for data transfer between the CPU and peripherals, and also data transfers between peripherals. The PHUB and DMA also control device configuration during boot. The PHUB consists of:

- A central hub that includes the DMA controller, arbiter, and router

- Multiple spokes that radiate outward from the hub to most peripherals

There are two PHUB masters: the CPU and the DMA controller. Both masters may initiate transactions on the bus. The DMA channels can handle peripheral communication without CPU intervention. The arbiter in the central hub determines which DMA channel is the highest priority if there are multiple requests.

#### 4.4.1 PHUB Features

- CPU and DMA controller are both bus masters to the PHUB

- Eight multi-layer AHB bus parallel access paths (spokes) for peripheral access

- Simultaneous CPU and DMA access to peripherals located on different spokes

- Simultaneous DMA source and destination burst transactions on different spokes

- Supports 8-, 16-, 24-, and 32-bit addressing and data

#### Table 4-6. PHUB Spokes and Peripherals

| PHUB Spokes | Peripherals                                                                                         |

|-------------|-----------------------------------------------------------------------------------------------------|

| 0           | SRAM                                                                                                |

| 1           | IOs, PICU, EMIF                                                                                     |

| 2           | PHUB local configuration, Power manager,<br>Clocks, IC, SWV, EEPROM, Flash<br>programming interface |

| 3           | Analog interface and trim, Decimator                                                                |

| 4           | USB, CAN, I <sup>2</sup> C, Timers, Counters, and PWMs                                              |

| 5           | DFB                                                                                                 |

| 6           | UDBs group 1                                                                                        |

| 7           | UDBs group 2                                                                                        |

#### 4.4.2 DMA Features

- 24 DMA channels

- Each channel has one or more transaction descriptors (TD) to configure channel behavior. Up to 128 total TDs can be defined

- TDs can be dynamically updated

- Eight levels of priority per channel

- Any digitally routable signal, the CPU, or another DMA channel, can trigger a transaction

- Each channel can generate up to two interrupts per transfer

- Transactions can be stalled or canceled

- Supports transaction size of infinite or 1 to 64 KB

- TDs may be nested and/or chained for complex transactions

#### 4.4.3 Priority Levels

The CPU always has higher priority than the DMA controller when their accesses require the same bus resources. Due to the system architecture, the CPU can never starve the DMA. DMA channels of higher priority (lower priority number) may interrupt current DMA transfers. In the case of an interrupt, the current transfer is allowed to complete its current transaction. To ensure latency limits when multiple DMA accesses are requested simultaneously, a fairness algorithm guarantees an interleaved minimum percentage of bus bandwidth for priority levels 2 through 7. Priority levels 0 and 1 do not take part in the fairness algorithm and may use 100 percent of the bus bandwidth. If a tie occurs on two DMA requests of the same priority level, a simple round robin method is used to evenly share the allocated bandwidth. The round robin allocation can be disabled for each DMA channel, allowing it to always be at the head of the line. Priority levels 2 to 7 are guaranteed the minimum bus bandwidth shown in Table 4-7 after the CPU and DMA priority levels 0 and 1 have satisfied their requirements.

#### Table 4-7. Priority Levels

| Priority Level | % Bus Bandwidth |

|----------------|-----------------|

| 0              | 100.0           |

| 1              | 100.0           |

| 2              | 50.0            |

| 3              | 25.0            |

| 4              | 12.5            |

| 5              | 6.2             |

| 6              | 3.1             |

| 7              | 1.5             |

When the fairness algorithm is disabled, DMA access is granted based solely on the priority level; no bus bandwidth guarantees are made.

#### 4.4.4 Transaction Modes Supported

The flexible configuration of each DMA channel and the ability to chain multiple channels allow the creation of both simple and complex use cases. General use cases include, but are not limited to:

#### 4.4.4.1 Simple DMA

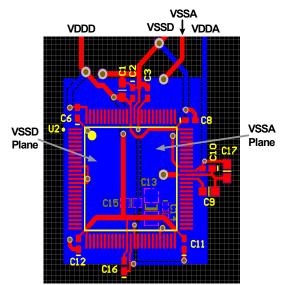

In a simple DMA case, a single TD transfers data between a source and sink (peripherals or memory location). The basic timing diagrams of DMA read and write cycles are shown in Figure 4-1. For more description on other transfer modes, refer to the Technical Reference Manual.

#### Figure 4-1. DMA Timing Diagram

#### 4.4.4.2 Auto Repeat DMA

Auto repeat DMA is typically used when a static pattern is repetitively read from system memory and written to a peripheral. This is done with a single TD that chains to itself.

#### 4.4.4.3 Ping Pong DMA

A ping pong DMA case uses double buffering to allow one buffer to be filled by one client while another client is consuming the data previously received in the other buffer. In its simplest form, this is done by chaining two TDs together so that each TD calls the opposite TD when complete.

#### 4.4.4.4 Circular DMA

Circular DMA is similar to ping pong DMA except it contains more than two buffers. In this case there are multiple TDs; after the last TD is complete it chains back to the first TD.

#### 4.4.4.5 Scatter Gather DMA

In the case of scatter gather DMA, there are multiple noncontiguous sources or destinations that are required to effectively carry out an overall DMA transaction. For example, a packet may need to be transmitted off of the device and the packet elements, including the header, payload, and trailer, exist in various noncontiguous locations in memory. Scatter gather DMA allows the segments to be concatenated together by using multiple TDs in a chain. The chain gathers the data from the multiple locations. A similar concept applies for the reception of data onto the device. Certain parts of the received data may need to be scattered to various locations in memory for software processing convenience. Each TD in the chain specifies the location for each discrete element in the chain.

#### 4.4.4.6 Packet Queuing DMA

Packet queuing DMA is similar to scatter gather DMA but specifically refers to packet protocols. With these protocols, there may be separate configuration, data, and status phases associated with sending or receiving a packet.

For instance, to transmit a packet, a memory mapped configuration register can be written inside a peripheral, specifying the overall length of the ensuing data phase. The CPU can set up this configuration information anywhere in system memory and copy it with a simple TD to the peripheral. After the configuration phase, a data phase TD (or a series of data phase TDs) can begin (potentially using scatter gather). When the data phase TD(s) finish, a status phase TD can be invoked that reads some memory mapped status information from the peripheral and copies it to a location in system memory specified by the CPU for later inspection. Multiple sets of configuration, data, and status phase 'subchains' can be strung together to create larger chains that transmit multiple packets in this way. A similar concept exists in the opposite direction to receive the packets.

#### 4.4.4.7 Nested DMA

One TD may modify another TD, as the TD configuration space is memory mapped similar to any other peripheral. For example, a first TD loads a second TD's configuration and then calls the second TD. The second TD moves data as required by the application. When complete, the second TD calls the first TD, which again updates the second TD's configuration. This process repeats as often as necessary.

#### 4.5 Interrupt Controller

The interrupt controller provides a mechanism for hardware resources to change program execution to a new address, independent of the current task being executed by the main code. The interrupt controller provides enhanced features not found on original 8051 interrupt controllers:

- Thirty-two interrupt vectors

- Jumps directly to ISR anywhere in code space with dynamic vector addresses

- Multiple sources for each vector

- Flexible interrupt to vector matching

- Each interrupt vector is independently enabled or disabled

- Each interrupt can be dynamically assigned one of eight priorities

- Eight level nestable interrupts

- Multiple I/O interrupt vectors

- Software can send interrupts

- Software can clear pending interrupts

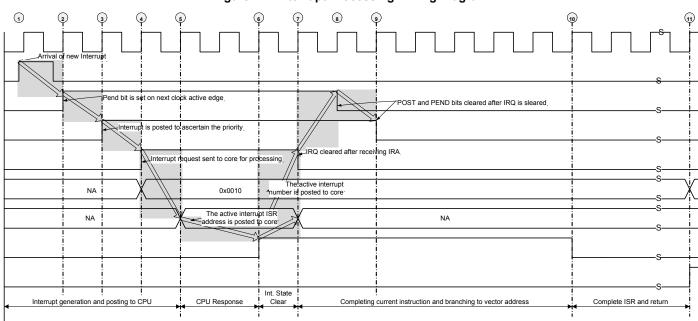

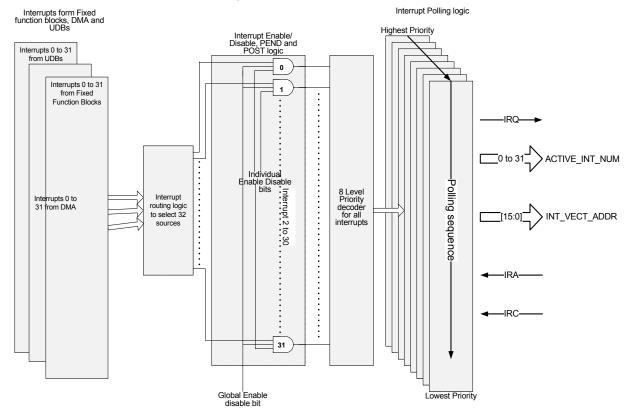

Figure 4-2 on page 18 represents typical flow of events when an interrupt triggered. Figure 4-3 on page 19 shows the interrupt structure and priority polling.

#### Figure 4-2. Interrupt Processing Timing Diagram

#### Notes

- 1: Interrupt triggered asynchronous to the clock

- 2: The PEND bit is set on next active clock edge to indicate the interrupt arrival

- 3: POST bit is set following the PEND bit

- 4: Interrupt request and the interrupt number sent to CPU core after evaluation priority (Takes 3 clocks)

- 5: ISR address is posted to CPU core for branching

- 6: CPU acknowledges the interrupt request

- 7: ISR address is read by CPU for branching

- 8, 9: PEND and POST bits are cleared respectively after receiving the IRA from core

- 10: IRA bit is cleared after completing the current instruction and starting the instruction execution from ISR location (Takes 7 cycles)

- 11: IRC is set to indicate the completion of ISR, Active int. status is restored with previous status

- The total interrupt latency (ISR execution)

- = POST + PEND + IRQ + IRA + Completing current instruction and branching

- = 1+1+1+2+7 cycles

= 12 cycles

## PSoC<sup>®</sup> 3: CY8C36 Automotive Family Datasheet

Figure 4-3. Interrupt Structure

When an interrupt is pending, the current instruction is completed and the program counter is pushed onto the stack. Code execution then jumps to the program address provided by the vector. After the ISR is completed, a RETI instruction is executed and returns execution to the instruction following the previously interrupted instruction. To do this the RETI instruction pops the program counter from the stack.

If the same priority level is assigned to two or more interrupts, the interrupt with the lower vector number is executed first. Each interrupt vector may choose from three interrupt sources: Fixed Function, DMA, and UDB. The fixed function interrupts are

direct connections to the most common interrupt sources and provide the lowest resource cost connection. The DMA interrupt sources provide direct connections to the two DMA interrupt sources provided per DMA channel. The third interrupt source for vectors is from the UDB digital routing array. This allows any digital signal available to the UDB array to be used as an interrupt source. Fixed function interrupts and all interrupt sources may be routed to any interrupt vector using the UDB interrupt source connections.

#### Table 4-8. Interrupt Vector Table

| #  | Fixed Function         | DMA               | UDB          |

|----|------------------------|-------------------|--------------|

| 0  | LVD                    | phub_termout0[0]  | udb_intr[0]  |

| 1  | Cache/ECC              | phub_termout0[1]  | udb_intr[1]  |

| 2  | Reserved               | phub_termout0[2]  | udb_intr[2]  |

| 3  | Sleep (Pwr Mgr)        | phub_termout0[3]  | udb_intr[3]  |

| 4  | PICU[0]                | phub_termout0[4]  | udb_intr[4]  |

| 5  | PICU[1]                | phub_termout0[5]  | udb_intr[5]  |

| 6  | PICU[2]                | phub_termout0[6]  | udb_intr[6]  |

| 7  | PICU[3]                | phub_termout0[7]  | udb_intr[7]  |

| 8  | PICU[4]                | phub_termout0[8]  | udb_intr[8]  |

| 9  | PICU[5]                | phub_termout0[9]  | udb_intr[9]  |

| 10 | PICU[6]                | phub_termout0[10] | udb_intr[10] |

| 11 | PICU[12]               | phub_termout0[11] | udb_intr[11] |

| 12 | PICU[15]               | phub_termout0[12] | udb_intr[12] |

| 13 | Comparators Combined   | phub_termout0[13] | udb_intr[13] |

| 14 | Switched Caps Combined | phub_termout0[14] | udb_intr[14] |

| 15 | l <sup>2</sup> C       | phub_termout0[15] | udb_intr[15] |

| 16 | CAN                    | phub_termout1[0]  | udb_intr[16] |

| 17 | Timer/Counter0         | phub_termout1[1]  | udb_intr[17] |

| 18 | Timer/Counter1         | phub_termout1[2]  | udb_intr[18] |

| 19 | Timer/Counter2         | phub_termout1[3]  | udb_intr[19] |

| 20 | Timer/Counter3         | phub_termout1[4]  | udb_intr[20] |

| 21 | USB SOF Int            | phub_termout1[5]  | udb_intr[21] |

| 22 | USB Arb Int            | phub_termout1[6]  | udb_intr[22] |

| 23 | USB Bus Int            | phub_termout1[7]  | udb_intr[23] |

| 24 | USB Endpoint[0]        | phub_termout1[8]  | udb_intr[24] |

| 25 | USB Endpoint Data      | phub_termout1[9]  | udb_intr[25] |

| 26 | Reserved               | phub_termout1[10] | udb_intr[26] |

| 27 | LCD                    | phub_termout1[11] | udb_intr[27] |

| 28 | DFB Int                | phub_termout1[12] | udb_intr[28] |

| 29 | Decimator Int          | phub_termout1[13] | udb_intr[29] |

| 30 | PHUB Error Int         | phub_termout1[14] | udb_intr[30] |

| 31 | EEPROM Fault Int       | phub_termout1[15] | udb_intr[31] |

## 5. Memory

#### 5.1 Static RAM

CY8C36 SRAM is used for temporary data storage. Up to 8 KB of SRAM is provided and can be accessed by the 8051 or the DMA controller. See Memory Map on page 24. Simultaneous access of SRAM by the 8051 and the DMA controller is possible if different 4-KB blocks are accessed.

#### 5.2 Flash Program Memory

Flash memory in PSoC devices provides nonvolatile storage for user firmware, user configuration data, bulk data storage, and optional ECC data. The main flash memory area contains up to 64 KB of user program space.

Up to an additional 8 KB of flash space is available for ECC. If ECC is not used this space can store device configuration data and bulk user data. User code may not be run out of the ECC flash memory section. ECC can correct one bit error and detect two bit errors per 8 bytes of firmware memory; an interrupt can be generated when an error is detected.

The CPU reads instructions located in flash through a cache controller. This improves instruction execution rate and reduces system power consumption by requiring less frequent flash access. The cache has 8 lines at 64 bytes per line for a total of 512 bytes. It is fully associative, automatically controls flash power, and can be enabled or disabled. If ECC is enabled, the cache controller also performs error checking and correction, and interrupt generation.

Flash programming is performed through a special interface and preempts code execution out of flash. The flash programming interface performs flash erasing, programming and setting code protection levels. Flash in-system serial programming (ISSP), typically used for production programming, is possible through both the SWD and JTAG interfaces. In-system programming, typically used for bootloaders, is also possible using serial interfaces such as I<sup>2</sup>C, USB, UART, and SPI, or any communications protocol.

#### 5.3 Flash Security

All PSoC devices include a flexible flash-protection model that prevents access and visibility to on-chip flash memory. This prevents duplication or reverse engineering of proprietary code. Flash memory is organized in blocks, where each block contains 256 bytes of program or data and 32 bytes of ECC or configuration data. A total of up to 256 blocks is provided on 64-KB flash devices.

The device offers the ability to assign one of four protection levels to each row of flash. Table 5-1 lists the protection modes available. Flash protection levels can only be changed by performing a complete flash erase. The Full Protection and Field Upgrade settings disable external access (through a debugging tool such as PSoC Creator, for example). If your application requires code update through a bootloader, then use the Field Upgrade setting. Use the Unprotected setting only when no security is needed in your application. The PSoC device also offers an advanced security feature called Device Security which permanently disables all test, programming, and debug ports, protecting your application from external access (see the "Device Security" section on page 63). For more information about how to take full advantage of the security features in PSoC, see the PSoC 3 TRM.

#### Table 5-1. Flash Protection

| Protection<br>Setting | Allowed                                              | Not Allowed                              |  |  |

|-----------------------|------------------------------------------------------|------------------------------------------|--|--|

| Unprotected           | External read and write<br>+ internal read and write | -                                        |  |  |

| Factory<br>Upgrade    | External write + internal read and write             | External read                            |  |  |

| Field Upgrade         | Internal read and write                              | External read and write                  |  |  |

| Full Protection       | Internal read                                        | External read and write + internal write |  |  |

#### Disclaimer

Note the following details of the flash code protection features on Cypress devices.

Cypress products meet the specifications contained in their particular Cypress data sheets. Cypress believes that its family of products is one of the most secure families of its kind on the market today, regardless of how they are used. There may be methods, unknown to Cypress, that can breach the code protection features. Any of these methods, to our knowledge, would be dishonest and possibly illegal. Neither Cypress nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as 'unbreakable'. Cypress is willing to work with the customer who is concerned about the integrity of their code. Code protection is constantly evolving. We at Cypress are committed to continuously improving the code protection features of our products.

#### 5.4 EEPROM

PSoC EEPROM memory is a byte-addressable nonvolatile memory. The CY8C36 has up to 2 KB of EEPROM memory to store user data. Reads from EEPROM are random access at the byte level. Reads are done directly; writes are done by sending write commands to an EEPROM programming interface. CPU code execution can continue from flash during EEPROM writes. EEPROM is erasable and writeable at the row level. The EEPROM is divided into 128 rows of 16 bytes each. The CPU can not execute out of EEPROM. There is no ECC hardware associated with EEPROM. If ECC is required it must be handled in firmware.

It can take as much as 20 milliseconds to write to EEPROM or flash. During this time the device should not be reset, or unexpected changes may be made to portions of EEPROM or flash. Reset sources (see Section 6.3.1) include XRES pin, software reset, and watchdog; care should be taken to make sure that these are not inadvertently activated. Also, the low voltage detect circuits should be configured to generate an interrupt instead of a reset.

#### 5.5 Nonvolatile Latches (NVLs)

PSoC has a 4-byte array of nonvolatile latches (NVLs) that are used to configure the device at reset. The NVL register map is shown in Table 5-2.

Table 5-2. Device Configuration NVL Register Map

| Register Address | 7                | 6     | 5            | 4       | 3            | 2         | 1            | 0        |

|------------------|------------------|-------|--------------|---------|--------------|-----------|--------------|----------|

| 0x00             | PRT3RDM[1:0]     |       | PRT2RDM[1:0] |         | PRT1RDM[1:0] |           | PRT0RDM[1:0] |          |

| 0x01             | PRT12RDM[1:0]    |       | PRT6R        | DM[1:0] | PRT5RDM[1:0] |           | PRT4RDM[1:0] |          |

| 0x02             | XRESMEN          | DBGEN | PRT15RDM[1:0 |         |              | 5RDM[1:0] |              |          |

| 0x03             | DIG_PHS_DLY[3:0] |       |              |         | ECCEN        | DPS[1:0]  |              | CFGSPEED |

The details for individual fields and their factory default settings are shown in Table 5-3:.

#### Table 5-3. Fields and Factory Default Settings

| Field            | Description                                                                                                                                        | Settings                                                                                                                      |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| PRTxRDM[1:0]     | Controls reset drive mode of the corresponding IO port.<br>See "Reset Configuration" on page 39. All pins of the port<br>are set to the same mode. | 00b (default) - high impedance analog<br>01b - high impedance digital<br>10b - resistive pull up<br>11b - resistive pull down |

| XRESMEN          | Controls whether pin P1[2] is used as a GPIO or as an external reset. See "Pin Descriptions" on page 9, XRES description.                          | 0 (default for 68-pin and 100-pin parts) - GPIO<br>1 (default for 48-pin parts) - external reset                              |

| DBGEN            | Debug Enable allows access to the debug system, for third-party programmers.                                                                       | 0 - access disabled<br>1 (default) - access enabled                                                                           |

| DPS{1:0]         | Controls the usage of various P1 pins as a debug port.<br>See "Programming, Debug Interfaces, Resources" on<br>page 60.                            | 00b - 5-wire JTAG<br>01b (default) - 4-wire JTAG<br>10b - SWD<br>11b - debug ports disabled                                   |

| ECCEN            | Controls whether ECC flash is used for ECC or for general configuration and data storage. See "Flash Program Memory" on page 21.                   | 0 - ECC disabled<br>1 (default) - ECC enabled                                                                                 |

| DIG_PHS_DLY[3:0] | Selects the digital clock phase delay.                                                                                                             | See the TRM for details.                                                                                                      |

Although PSoC Creator provides support for modifying the device configuration NVLs, the number of NVL erase / write cycles is limited – see Nonvolatile Latches (NVL) on page 120.

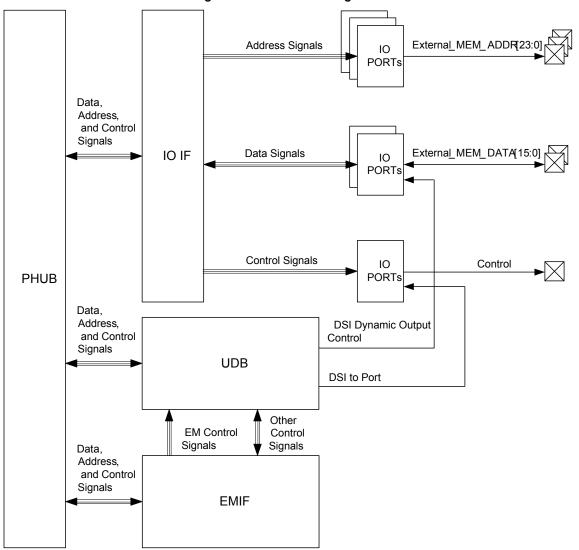

#### 5.6 External Memory Interface

CY8C36 provides an EMIF for connecting to external memory devices. The connection allows read and write accesses to external memories. The EMIF operates in conjunction with UDBs, I/O ports, and other hardware to generate external memory address and control signals. At 33 MHz, each memory access cycle takes four bus clock cycles. Figure 5-1 is the EMIF block diagram. The EMIF supports synchronous and asynchronous memories. The CY8C36 supports only one type of external memory device at a time. External memory can be accessed through the 8051 xdata space; up to 24 address bits can be used. See "xdata Space" section on page 25. The memory can be 8 or 16 bits wide.

Figure 5-1. EMIF Block Diagram

#### 5.7 Memory Map

The CY8C36 8051 memory map is very similar to the MCS-51 memory map.

#### 5.7.1 Code Space

The CY8C36 8051 code space is 64 KB. Only main flash exists in this space. See the Flash Program Memory on page 21.

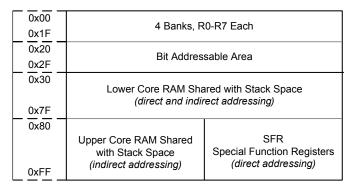

#### 5.7.2 Internal Data Space

The CY8C36 8051 internal data space is 384 bytes, compressed within a 256-byte space. This space consists of 256 bytes of RAM (in addition to the SRAM mentioned in Static RAM on page 21) and a 128-byte space for special function registers (SFR). See Figure 5-2. The lowest 32 bytes are used for 4 banks of registers R0-R7. The next 16 bytes are bit-addressable.

#### Figure 5-2. 8051 Internal Data Space

In addition to the register or bit address modes used with the lower 48 bytes, the lower 128 bytes can be accessed with direct or indirect addressing. With direct addressing mode, the upper 128 bytes map to the SFRs. With indirect addressing mode, the upper 128 bytes map to RAM. Stack operations use indirect addressing; the 8051 stack space is 256 bytes. See the "Addressing Modes" section on page 10.

#### 5.7.3 SFRs

The SFR space provides access to frequently accessed registers. The memory map for the SFR memory space is shown in Table 5-4.

| Address | 0/8        | 1/9        | 2/A         | 3/B  | 4/C  | 5/D  | 6/E | 7/F |

|---------|------------|------------|-------------|------|------|------|-----|-----|

| 0×F8    | SFRPRT15DR | SFRPRT15PS | SFRPRT15SEL | -    | -    | -    | _   | -   |

| 0×F0    | В          | -          | SFRPRT12SEL | -    | -    | -    | _   | -   |

| 0×E8    | SFRPRT12DR | SFRPRT12PS | MXAX        | -    | -    | -    | -   | -   |

| 0×E0    | ACC        | -          | -           | -    | -    | -    | -   | -   |

| 0×D8    | SFRPRT6DR  | SFRPRT6PS  | SFRPRT6SEL  | -    | -    | -    | _   | -   |

| 0×D0    | PSW        | -          | -           | -    | -    | -    | _   | -   |

| 0×C8    | SFRPRT5DR  | SFRPRT5PS  | SFRPRT5SEL  | -    | -    | -    | -   | -   |

| 0×C0    | SFRPRT4DR  | SFRPRT4PS  | SFRPRT4SEL  | -    | -    | -    | -   | -   |

| 0×B8    |            |            |             | -    | -    | -    | _   | -   |

| 0×B0    | SFRPRT3DR  | SFRPRT3PS  | SFRPRT3SEL  | -    | -    | -    | -   | -   |

| 0×A8    | IE         | -          | -           | -    | -    | -    | -   | -   |

| 0×A0    | P2AX       | -          | SFRPRT1SEL  | -    | -    | -    | -   | -   |

| 0×98    | SFRPRT2DR  | SFRPRT2PS  | SFRPRT2SEL  | -    | -    | -    | -   | -   |

| 0×90    | SFRPRT1DR  | SFRPRT1PS  | -           | DPX0 | -    | DPX1 | -   | -   |

| 0×88    | -          | SFRPRT0PS  | SFRPRT0SEL  | -    | -    | -    | -   | -   |

| 0×80    | SFRPRT0DR  | SP         | DPL0        | DPH0 | DPL1 | DPH1 | DPS | -   |

#### Table 5-4. SFR Map

The CY8C36 family provides the standard set of registers found on industry standard 8051 devices. In addition, the CY8C36 devices add SFRs to provide direct access to the I/O ports on the device. The following sections describe the SFRs added to the CY8C36 family.

#### 5.7.4 XData Space Access SFRs

The 8051 core features dual DPTR registers for faster data transfer operations. The data pointer select SFR, DPS, selects which data pointer register, DPTR0 or DPTR1, is used for the following instructions:

- MOVX @DPTR, A

- MOVX A, @DPTR

- MOVC A, @A+DPTR

- JMP @A+DPTR

- INC DPTR

- MOV DPTR, #data16

The extended data pointer SFRs, DPX0, DPX1, MXAX, and P2AX, hold the most significant parts of memory addresses during access to the xdata space. These SFRs are used only with the MOVX instructions.

During a MOVX instruction using the DPTR0/DPTR1 register, the most significant byte of the address is always equal to the contents of DPX0/DPX1.

During a MOVX instruction using the R0 or R1 register, the most significant byte of the address is always equal to the contents of MXAX, and the next most significant byte is always equal to the contents of P2AX.

#### 5.7.5 I/O Port SFRs

The I/O ports provide digital input sensing, output drive, pin interrupts, connectivity for analog inputs and outputs, LCD, and access to peripherals through the DSI. Full information on I/O ports is found in I/O System and Routing on page 33.

I/O ports are linked to the CPU through the PHUB and are also available in the SFRs. Using the SFRs allows faster access to a limited set of I/O port registers, while using the PHUB allows boot configuration and access to all I/O port registers.

Each SFR supported I/O port provides three SFRs:

- SFRPRTxDR sets the output data state of the port (where × is port number and includes ports 0–6, 12 and 15).

- The SFRPRTxSEL selects whether the PHUB PRTxDR register or the SFRPRTxDR controls each pin's output buffer within the port. If a SFRPRTxSEL[y] bit is high, the corresponding SFRPRTxDR[y] bit sets the output state for that pin. If a SFRPRTxSEL[y] bit is low, the corresponding PRTxDR[y] bit sets the output state of the pin (where y varies from 0 to 7).

- The SFRPRTxPS is a read only register that contains pin state values of the port pins.

#### 5.7.5.1 xdata Space

The 8051 xdata space is 24-bit, or 16 MB in size. The majority of this space is not 'external'—it is used by on-chip components. See Table 5-5. External, that is, off-chip, memory can be accessed using the EMIF. See External Memory Interface on page 23.

#### Table 5-5. XDATA Data Address Map

| Address Range         | Purpose                            |

|-----------------------|------------------------------------|

| 0×00 0000 – 0×00 1FFF | SRAM                               |

| 0×00 4000 – 0×00 42FF | Clocking, PLLs, and oscillators    |

| 0×00 4300 – 0×00 43FF | Power management                   |

| 0×00 4400 – 0×00 44FF | Interrupt controller               |

| 0×00 4500 – 0×00 45FF | Ports interrupt control            |

| 0×00 4700 – 0×00 47FF | Flash programming interface        |

| 0×00 4800 - 0×00 48FF | Cache controller                   |

| 0×00 4900 – 0×00 49FF | I <sup>2</sup> C controller        |

| 0×00 4E00 – 0×00 4EFF | Decimator                          |

| 0×00 4F00 – 0×00 4FFF | Fixed timer/counter/PWMs           |

| 0×00 5000 – 0×00 51FF | I/O ports control                  |

| 0×00 5400 – 0×00 54FF | EMIF control registers             |

| 0×00 5800 – 0×00 5FFF | Analog subsystem interface         |

| 0×00 6000 – 0×00 60FF | USB controller                     |

| 0×00 6400 – 0×00 6FFF | UDB Working Registers              |

| 0×00 7000 – 0×00 7FFF | PHUB configuration                 |

| 0×00 8000 – 0×00 8FFF | EEPROM                             |

| 0×00 A000 – 0×00 A400 | CAN                                |

| 0×00 C000 – 0×00 C800 | DFB                                |

| 0×01 0000 – 0×01 FFFF | Digital Interconnect configuration |

| 0×05 0220 – 0×05 02F0 | Debug controller                   |

| 0×08 0000 – 0×08 1FFF | Flash ECC bytes                    |

| 0×80 0000 – 0×FF FFFF | External memory interface          |