# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## CY8CLED16P01

## **Powerline Communication Solution**

## **Features**

- Powerline Communication Solution

- Integrated Powerline Modem PHY

- Frequency Shift Keying Modulation

- Configurable baud rates up to 2400 bps

- Powerline Optimized Network Protocol

- □ Integrates Data Link, Transport, and Network Layers

- Supports Bidirectional Half Duplex Communication

- □ 8-bit CRC Error Detection to Minimize Data Loss

- □ I<sup>2</sup>C enabled Powerline Application Layer

- □ Supports I<sup>2</sup>C Frequencies of 50, 100, and 400 kHz

- □ Reference Designs for 110V/240V AC and 12V/24V AC/DC Powerlines

- Reference Designs comply with CENELEC EN 50065-1:2001 and FCC Part 15

#### HB LED Controller

- Configurable Dimmers Support up to 16 Independent LED Channels

- □ 8 to 32 Bits of Resolution per Channel

- □ PrISM<sup>™</sup> Modulation technology to reduce radiated EMI and Low Frequency Blinking

- Additional communication interfaces for lighting control such as DALI, DMX512 etc.

- Powerful Harvard Architecture Processor

- M8C Processor Speeds to 24 MHz

- □ Two 8x8 Multiply, 32-Bit Accumulate

- Programmable System Resources (PSoC<sup>®</sup> Blocks)

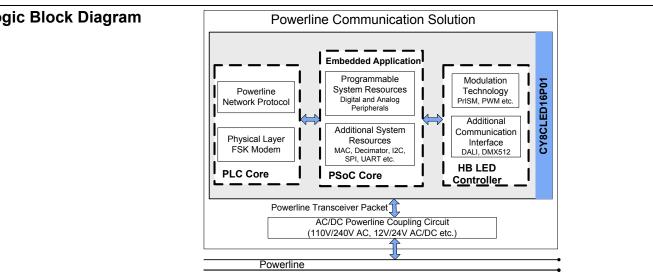

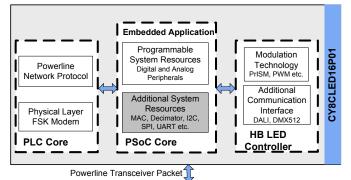

### Logic Block Diagram

- □ 12 Rail-to-Rail Analog PSoC Blocks provide:

- · Up to 14-Bit ADCs

- · Up to 9-Bit DACs

- · Programmable Gain Amplifiers

- Programmable Filters and Comparators

- □ 16 Digital PSoC Blocks provide:

- · 8 to 32-Bit Timers, Counters, and PWMs

- · CRC and PRS Modules

- Up to Four Full Duplex UARTs

- Multiple SPI<sup>TM</sup> Masters or Slaves

- · Connectable to all GPIO Pins

- Complex Peripherals by Combining Blocks

- Flexible On-Chip Memory

- □ 32 KB Flash Program Storage 50,000 Erase or Write Cycles

- □ 2 KB SRAM Data Storage

- **D EEPROM Emulation in Flash**

- Programmable Pin Configurations

- □ 25 mA Sink, 10 mA Source on all GPIO

- Pull Up, Pull Down, High Z, Strong, or Open Drain Drive Modes on all GPIO

- Up to 12 Analog Inputs on GPIO

- Configurable Interrupt on all GPIO

- Additional System Resources

- □ I<sup>2</sup>C Slave, Master, and Multi-Master to 400 kHz

- Watchdog and Sleep Timers

- User-Configurable Low Voltage Detection

San Jose, CA 95134-1709 408-943-2600 Revised October 05, 2009

## 1. PLC Functional Overview

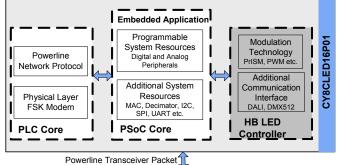

The CY8CLED16P01 is an integrated Powerline Communication (PLC) chip with the Powerline Modem PHY and Network Protocol Stack running on the same device. Apart from the PLC core, the CY8CLED16P01 also offers Cypress's revolutionary PSoC technology that enables system designers to integrate multiple functions on the same chip.

## 1.1 Robust Communication using Cypress's PLC Solution

Powerlines are available everywhere in the world and are a widely available communication medium for PLC technology. The pervasiveness of powerlines also makes it difficult to predict the characteristics and operation of PLC products. Because of the variable quality of powerlines around the world, implementing robust communication has been an engineering challenge for years. The Cypress PLC solution enables secure and reliable communications. Cypress PLC features that enable robust communication over powerlines include:

- Integrated Powerline PHY modem with optimized filters and amplifiers to work with lossy high voltage and low voltage powerlines.

- Powerline optimized network protocol that supports bidirectional communication with acknowledgement-based signaling. In case of data packet loss due to bursty noise on the powerline, the transmitter has the capability to retransmit data.

- The Powerline Network Protocol also supports an 8-bit CRC for error detection and data packet retransmission.

- A Carrier Sense Multiple Access (CSMA) scheme is built into the network protocol that minimizes collisions between packet transmissions on the powerline and supports multiple masters and reliable communication on a bigger network.

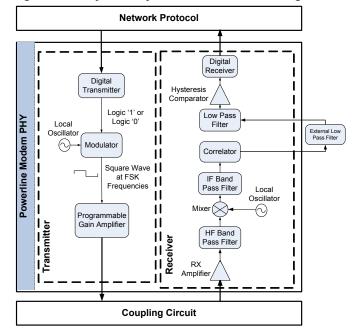

#### 1.2 Powerline Modem PHY

#### Figure 1-1. Physical Layer FSK Modem

Powerline Communication Solution

Powerline Transceiver Packet

The physical layer of the Cypress PLC solution is implemented using an FSK modem that enables half duplex communication on any high voltage and low voltage powerline. This modem supports raw data rates up to 2400 bps. A block diagram is shown in Figure 1-2.

#### Figure 1-2. Physical Layer FSK Modem Block Diagram

#### 1.2.1 Transmitter Section

Digital data from the network layer is serialized by the digital transmitter and fed as input to the modulator. The modulator divides the local oscillator frequency by a definite factor depending on whether the input data is high level logic '1' or low level logic '0'. It then generates a square wave at 133.3 kHz (logic '0') or 131.8 kHz (logic '1'), which is fed to the Programmable Gain Amplifier to generate FSK modulated signals. This enables tunable amplification of the signal depending on the noise in the channel. The logic '1' frequency can also be configured as 130.4 kHz for wider FSK deviation.

#### 1.2.2 Receiver Section

The incoming FSK signal from the powerline is input to a high frequency (HF) band pass filter that filters out-of-band frequency components and outputs a filtered signal within the desired spectrum of 125 kHz to 140 kHz for further demodulation. The mixer block multiplies the filtered FSK signals with a locally generated signal to produce heterodyned frequencies.

The intermediate frequency (IF) band pass filters further remove out-of-band noise as required for further demodulation. This signal is fed to the correlator, which produces a DC component (consisting of logic '1' and '0') and a higher frequency component.

The output of the correlator is fed to a low pass filter (LPF) that outputs only the demodulated digital data at 2400 baud and suppresses all other higher frequency components generated in the correlation process. The output of the LPF is digitized by the hysteresis comparator. This eliminates the effects of correlator delay and false logic triggers due to noise. The digital receiver deserializes this data and outputs to the network layer for interpretation.

#### 1.2.3 Coupling Circuit Reference Design

The coupling circuit couples low voltage signals from the CY8CLED16P01 to the powerline. The topology of this circuit is determined by the voltage on the powerline and design constraints mandated by powerline usage regulations.

Cypress provides reference designs for a range of powerline voltages including 110V/240V AC and 12V/24V AC/DC. The CY8CLED16P01 is capable of data communication over other AC/DC Powerlines as well with the appropriate external coupling circuit. The 110V AC and 240V AC designs are compliant to the following powerline usage regulations:

- FCC Part 15 for North America

- EN 50065-1:2001 for Europe

#### **1.3 Network Protocol**

Cypress's powerline optimized network protocol performs the functions of the data link, network, and transport layers in an ISO/OSI-equivalent model.

#### Figure 1-3. Powerline Network Protocol

Powerline Communication Solution

Powerline Transceiver Packet

The network protocol implemented on the CY8CLED16P01 supports the following features:

- Bidirectional half duplex communication

- Master-slave or peer-to-peer network topologies

- Multiple masters on powerline network

- 8-bit logical addressing supports up to 256 powerline nodes

- 16-bit extended logical addressing supports up to 65536 powerline nodes

- 64-bit physical addressing supports up to 2<sup>64</sup> powerline nodes

- Individual, broadcast or group mode addressing

- Carrier Sense Multiple Access (CSMA)

- Full control over transmission parameters

- Acknowledged

- Unacknowledged

- Repeated Transmit

#### 1.3.1 CSMA and Timing Parameters

- CSMA The protocol provides the random selection of a period between 85 and 115 ms (out of seven possible values in this range). Within this period, the Band-In-Use (BIU) detector must indicate that the line is not in use, before attempting a transmission.

- BIU A Band-In-Use detector, as defined under CENELEC EN 50065-1, is active whenever a signal that exceeds 86 dBµVrms anywhere in the range 131.5 kHz to 133.5 kHz is present for at least 4 ms. This threshold can be configured for different end-system applications not requiring CENELEC compliance. The modem tries to retransmit after every 85 to 115 ms when the band is in use. The transmitter times out after 1.1 seconds to 3 seconds (depending on the noise on the Powerline) and generates an interrupt to indicate that the transmitter was unable to acquire the powerline.

#### 1.3.2 Powerline Transceiver Packet

The powerline network protocol defines a Powerline Transceiver (PLT) packet structure, which is used for data transfers between nodes across the powerline. Packet formation and data transmission across the powerline network is implemented internally in the CY8CLED16P01.

A PLT packet is divided into a variable length header (minimum 6 bytes to maximum 20 bytes, depending on address type), variable length payload (minimum 0 bytes to maximum 31 bytes), and a packet CRC byte.

This packet (preceded by a one byte preamble "0xAB") is then transmitted by the powerline modem PHY and the external coupling circuit across the powerline.

The format of the PLT packet is shown in the following table.

#### Table 1-1. Powerline Transceiver (PLT) Packet Structure

| Byte<br>Offset | Bit Offset                                                                         |                                  |       |                 |       |          |            |       |  |  |  |

|----------------|------------------------------------------------------------------------------------|----------------------------------|-------|-----------------|-------|----------|------------|-------|--|--|--|

|                | 7                                                                                  | 6                                | 5     | 4 3 2 1 0       |       |          |            |       |  |  |  |

| 0x00           | SA<br>Type                                                                         | DA                               | Туре  | Service<br>Type | RSVD  | RSVD     | Response   | RSVD  |  |  |  |

| 0x01           | Destination Address<br>(8-Bit Logical, 16-Bit Extended Logical or 64-Bit Physical) |                                  |       |                 |       |          |            |       |  |  |  |

| 0x02           | Source Address<br>(8-Bit Logical, 16-Bit Extended Logical or 64-Bit Physical)      |                                  |       |                 |       |          |            |       |  |  |  |

| 0x03           |                                                                                    |                                  |       | С               | omman | d        |            |       |  |  |  |

| 0x04           | RSVD Payload Length                                                                |                                  |       |                 |       |          |            |       |  |  |  |

| 0x05           |                                                                                    | Sec                              | ן Num |                 | Powe  | rline Pa | cket Heade | r CRC |  |  |  |

| 0x06           | Payload (0 to 31 Bytes)                                                            |                                  |       |                 |       |          |            |       |  |  |  |

|                |                                                                                    | Powerline Transceiver Packet CRC |       |                 |       |          |            |       |  |  |  |

#### 1.3.3 Packet Header

The packet header contains the first 6 bytes of the packet when 1-byte logical addressing is used. When 8-byte physical addressing is used, the source and destination addresses each contain 8 bytes. In this case, the header can consist of a maximum of 20 bytes. Unused fields marked RSVD are for future expansion and are transmitted as bit 0. Table 1-2 describes the PLT packet header fields in detail.

Table 1-2. Powerline Transceiver (PLT) Packet Header

| Field<br>Name   | No. of<br>Bits                           | Tag                       | Description                                                                                                       |  |  |

|-----------------|------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|--|--|

| SA Type         | 1                                        | Source<br>Address<br>Type | 0 – Logical Addressing<br>1 – Physical Addressing                                                                 |  |  |

| DA Type         | DA Type 2 Destination<br>Address<br>Type |                           | 00 – Logical Addressing<br>01 – Group Addressing<br>10 – Physical Addressing<br>11 – Invalid                      |  |  |

| Service<br>Type | 1                                        |                           | 0 – Unacknowledged Messaging<br>1 – Acknowledged Messaging                                                        |  |  |

| Response        | 1                                        | Response                  | 0 - Not an acknowledgement or<br>response packet<br>1 - Acknowledgement or response<br>packet                     |  |  |

| Seq Num         | 4                                        | Sequence<br>Number        | 4-bit unique identifier for each<br>packet between source and desti-<br>nation.                                   |  |  |

| Header<br>CRC   | 4                                        |                           | 4-bit CRC value. This enables the receiver to suspend receiving the rest of the packet if its header is corrupted |  |  |

#### 1.3.4 Payload

The packet payload has a length of 0 to 31 bytes. Payload content is user defined and can be read or written through  $I^2C$ .

#### 1.3.5 Packet CRC

The last byte of the packet is an 8-bit CRC value used to check packet data integrity. This CRC calculation includes the header and payload portions of the packet and is in addition to the powerline packet header CRC.

#### 1.3.6 Sequence Numbering

The sequence number is increased for every new unique packet transmitted. If in acknowledged mode and an acknowledgment is not received for a given packet, that packet will be re-transmitted (if  $TX_Retry > 0$ ) with the same sequence number. If in unacknowledged mode, the packet will be transmitted ( $TX_Retry + 1$ ) times with the same sequence number.

If the receiver receives consecutive packets from the same source address with the same sequence number and packet CRC, it does not notify the host of the reception of the duplicate packet. If in acknowledged mode, it still sends an acknowledgment so that the transmitter knows that the packet was received.

#### 1.3.7 Addressing

The CY8CLED16P01 has three modes of addressing:

■ Logical addressing: Every CY8CLED16P01 node can have either a 8-bit logical address or a 16-bit logical address. The logical address of the PLC Node is set by the local application or by a remote node on the Powerline.

- Physical addressing: Every CY8CLED16P01 has a unique 64-bit physical address.

- Group addressing: This is explained in the next section.

#### 1.3.8 Group Membership

Group membership enables the user to multicast messages to select groups. The CY8CLED16P01 supports two types of group addressing:

- Single Group Membership The network protocol supports up to 256 different groups on the network in this mode. In this mode, each PLC node can only be part of a single group. For example, multiple PLC nodes can be part of Group 131.

- Multiple Group Membership The network protocol supports eight different groups in this mode and each PLC node can be a part of multiple groups. For example, a single PLC node can be a part of Group 3, Group 4, and Group 7 at the same time.

Both of these membership modes can also be used together for group membership. For example, a single PLC node can be a part of Group 131 and also multiple groups such as Group 3, Group 4, and Group 7.

The group membership ID for broadcasting messages to all nodes in the network is 0x00.

The service type is always set to Unacknowledgment Mode in Group Addressing Mode. This is to avoid acknowledgment flooding on the powerline during multicast.

#### 1.3.9 Remote Commands

In addition to sending normal data over the Powerline, the CY8CPLC10 can also send (and request) control information to (and from) another node on the network. The type of remote command to transmit is set by the TX\_CommandID register and when received, is stored in the RX\_CommandID register.

When a control command (Command ID = 0x01 - 0x08 and 0x0C - 0x0F) is received, the protocol will automatically process the packet (if Lock\_Configuration is '0'), respond to the initiator, and notify the host of the successful transmission and reception.

When the send data command (ID 0x09) or request for data command (ID 0x0A) is received, the protocol will reply with an acknowledgment packet (if TX\_Service\_Type = '1'), and notify the host of the new received data. If the initiator doesn't receive the acknowledgment packet within 500ms, it will notify the host of the no acknowledgment received condition.

When a response command (ID 0x0B) is received by the initiator within 1.5s of sending the request for data command, the protocol will notify the host of the successful transmission and reception. If the response command is not received by the initiator within 1.5s, it will notify the host of the no response received condition.

The host is notified by updating the appropriate values in the INT\_Status register (including Status\_Value\_Change).

The command IDs 0x30-0xff can be used for custom commands that would be processed by the external host (e.g. set an LED color, get a temperature/voltage reading). The available remote commands are described in Table 1-3 on page 5 with the respective Command IDs.

#### Table 1-3. Remote Commands

| Cmd ID | Command Name           | Description                                                                                           | Payload (TX Data)                                                                                                       | Response (RX Data)                                                                                                                                                                                                                                                       |

|--------|------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x01   | SetRemote_TXEnable     | Sets the TX Enable bit in the<br>PLC Mode Register. Rest of the<br>PLC Mode register is<br>unaffected | 0 - Disable Remote TX<br>1 - Enable Remote TX                                                                           |                                                                                                                                                                                                                                                                          |

| 0x03   | SetRemote_ExtendedAddr | Set the Addressing to<br>Extended Addressing Mode                                                     | 0 - Disable Extended<br>Addressing<br>1 - Enable Extended<br>Addressing                                                 | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                                            |

| 0x04   | SetRemote_LogicalAddr  | Assigns the specified logical<br>address to the remote PLC<br>node                                    | If Ext Address = 0,<br>Payload = 8-bit Logical<br>Address<br>If Ext Address = 1,<br>Payload = 16-bit<br>Logical Address | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                                            |

| 0x05   | GetRemote_LogicalAddr  | Get the Logical Address of the remote PLC node                                                        | None                                                                                                                    | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>{If Ext Address = 0,<br>Response = 8-bit Logical<br>Address<br>If Ext Address = 1, Response<br>= 16-bit Logical Address}                                                                      |

| 0x06   | GetRemote_PhysicalAddr | Get the Physical Address of the remote PLC node                                                       | None                                                                                                                    | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>Response = 64-bit Physical<br>Address                                                                                                                                                         |

| 0x07   | GetRemote_State        | Request PLC_Mode Register<br>content from a Remote PLC<br>node                                        | None                                                                                                                    | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>Response = Remote PLC<br>Mode register                                                                                                                                                        |

| 0x08   | GetRemote_Version      | Get the Version Number of the Remote Node                                                             | None                                                                                                                    | If TX Enable = 0, Response =<br>None<br>If TX Enable = 1, Response =<br>Remote Version register                                                                                                                                                                          |

| 0x09   | SendRemote_Data        | Transmit data to a Remote<br>Node.                                                                    | Payload = Local TX<br>Data                                                                                              | If Local Service Type = 0,<br>Response = None<br>If Local Service Type = 1,<br>Response = Ack                                                                                                                                                                            |

| 0x0A   | RequestRemote_Data     | Request data from a Remote<br>Node                                                                    | Payload = Local TX<br>Data                                                                                              | If Local Service Type = 1,<br>Response = Ack<br>Then, the remote node host<br>must send a<br>ResponseRemote_Data<br>command. The response must<br>be completely transmitted<br>within 1.5s of receiving the<br>request. Otherwise, the<br>requesting node will time out. |

| 0x0B   | ResponseRemote_Data    | Transmit response data to a Remote Node.                                                              | Payload = Local TX<br>Data                                                                                              | None                                                                                                                                                                                                                                                                     |

| 0x0C   | SetRemote_BIU          | Enables/Disables BIU function-<br>ality at the remote node                                            | 0 - Enable Remote BIU<br>1 - Disable Remote BIU                                                                         | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                                                                                            |

#### Table 1-3. Remote Commands (continued)

| Cmd ID         | Command Name                                                           | Description                                  | Payload (TX Data)                                                                                            | Response (RX Data)                                                                                                                                                                               |

|----------------|------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0D           | SetRemote_ThresholdValue                                               | Sets the Threshold Value at the Remote node  | 3-bit Remote<br>Threshold Value                                                                              | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                    |

| 0x0E           | SetRemote_GroupMembership                                              | Sets the Group Membership of the Remote node | Byte0 - Remote SIngle<br>Group Membership<br>Address<br>Byte1-Remote Multiple<br>Group Membership<br>Address | If Remote Lock Config = 0,<br>Response = 00 (Success)<br>If Remote Lock Config = 1,<br>Response = 01 (Denied)                                                                                    |

| 0x0F           | GetRemote_GroupMembership Gets the Group Membership of the Remote node |                                              | None                                                                                                         | If Remote TX Enable = 0,<br>Response = None<br>If Remote TX Enable = 1,<br>Response =<br>Byte0 - Remote SIngle Group<br>Membership Address<br>Byte1- Remote Multiple Group<br>Membership Address |

| 0x10 -<br>0x2F | Reserved                                                               |                                              |                                                                                                              |                                                                                                                                                                                                  |

| 0x30 -<br>0xFF | User Defined Command Set                                               |                                              |                                                                                                              |                                                                                                                                                                                                  |

## 2. High Brightness (HB) LED Controller

#### Figure 2-1. CY8CLED16P01: HB LED Controller

The HB LED Controller is based on Cypress's EZ-Color™ technology. EZ-Color offers the ideal control solution for high brightness (HB) LED applications requiring intelligent dimming control. EZ-Color devices combine the power and flexibility of PSoC (Programmable System-on-Chip) with Cypress's PrISM™ (Precise Illumination Signal Modulation) modulation technology providing lighting designers a fully customizable and integrated lighting solution platform.

The CY8CLED16P01 supports up to 16 independent LED channels with up to 32 bits of resolution per channel, giving lighting designers the flexibility to choose the LED array size and color quality. PSoC Designer software, with lighting-specific user modules, significantly cuts development time and simplifies implementation of fixed color points through temperature and LED binning compensation. EZ-Color's virtually limitless analog and digital customization enable simple integration of features in addition to intelligent lighting, such as battery charging, image stabilization, and motor control during the development process. These features, along with Cypress's best-in-class quality and design support, make EZ-Color the ideal choice for intelligent HB LED control applications.

The list of functions that EZ-Color devices implement are:

- LED Dimming Modulation

- Pulse Density Modulation Techniques DMX512 DALI

- Digital Communication for Lighting

- LED Temperature Compensation

- 3- and 4-Channel Color Mixing Including LED Binning Compensation

- Optical Feedback Algorithms

#### 2.1 LED Dimming Modulation

The LED Dimming modulators are an important part of any HB LED application. All EZ-Color controllers are capable of three primary types of LED dimming modulations. These are:

- Pulse Width Modulation (PWM)

- Precise Illumination Signal Modulation (PrISM)

- Delta Sigma Modulated PWM (DSPWM)

PWM is among the most commonly used and conventional methods of modulation. It is straightforward to use and effective in practice. There are two additional techniques of modulation supported by EZ-Color that are superior to using the PWM alone:

- PrISM is a modulation technique that is developed and patented by Cypress. It results in reduced EMI as compared to the PWM technique while still providing adequate dimming control for LEDs.

- The Delta Sigma Modulated PWM technique provides higher resolution while using the same hardware resources as a conventional PWM.

LED dimming modulators use digital block resources. Digital blocks are configurable 8-bit digital peripherals. There are two types of digital blocks in the CY8CLED16P01: basic and communication. Usually, there are equal numbers of each. Any communication functions must be implemented using communication blocks but basic, noncommunication functions are implemented using either kind of block.

PWM and DSPWM modulators can have a dimming resolution of up to 16 bits. A PrISM modulator can theoretically have a dimming resolution of up to 32 bits, but the maximum recommended resolution for these modulators is 13 bits. This is because the output signal of a PrISM modulator has a frequency output range that increases with the resolution of the modulator. This increase in frequency output range is undesirable as it goes beyond the switching frequency of the current driver. Therefore, a resolution of 13 bits or lower is recommended for a PrISM modulator. Refer to application note AN47372, PrISM Technology for LED Dimming on http://www.cypress.com, for details.

To determine the number of digital blocks used by one PWM or PrISM modulator, use Equation 1. Note that a partial digital block cannot be used, so the result must always be rounded up. In Equation 1, n is the dimming resolution of the modulator. The resolution of dimming is determined by the color accuracy needed for the end application.

$$DigBlocks_{PWM,PRISM} = \frac{n}{8}$$

Equation 1

Powerline Communication Solution

Equations 2 and 3 are used to determine how many digital blocks are needed by a DSPWM. The total dimming resolution of a DSPWM modulator is the total of the hardware PWM modulation resolution and extra resolution added by Delta Sigma modulation in the software. Equation 3 shows that the number of digital blocks needed is only determined by the hardware resolution.

$$DigBlocks_{DSPWM} = \frac{n_{HW}}{8}$$

Equation 2

$$n_{Total} = n_{SW} + n_{HW}$$

Equation 3

These equations show that more dimming resolution is achieved with a DSPWM modulator than with a PWM or PrISM modulator. A DSPWM modulator requires more code space and execution time to use.

Equations 1, 2, and 3 determine the number of digital blocks required by one modulator. The total number of blocks for all modulators is determined by adding up the digital blocks needed by each modulator used in the device.

The CY8CLED16P01 device has a variety of LED dimming configurations. Because it has 16 digital blocks, it can implement eight 16-bit PWM modulators, eight 12-bit PrISM modulators, or sixteen 12-bit DSPWM modulators (assuming the software resolution is 4 bits). As another example, it can implement four 10-bit PrISM modulators and still have 8 digital blocks left over to implement other digital functions.

The CY8CLED16P01 is a one-device solution for powerline communication and HB LED control. For an application that runs powerline communication and HB LED control simultaneously, the CY8CLED16P01 can implement four 16-bit PWM modulators, four 12-bit PrISM modulators, or eight 12-bit DSPWM modulators (assuming the software resolution is 4 bits).

#### 2.2 Color Mixing Algorithm

Code algorithms to implement color mixing functionality work well with EZ-Color controllers. Color mixing algorithms convert a set of color coordinates that specify a color into the appropriate 8-bit dimming values for the LED dimming modulators. This enables the EZ-Color controller to be communicated on a higher level and maintain desired color and brightness levels.

The basic 3-channel color mixing firmware performing 8-bit LED dimming requires three 8-bit dimming blocks. The discussion on LED dimming modulation implies that it consumes three digital blocks. The addition of a simple temperature compensation algorithm using a thermistor consumes an additional digital block and analog block (for the ADC).

If the dimming resolution is increased, the number of digital blocks needed should be calculated accordingly.

#### 2.3 LED Temperature Compensation

Many HB LED systems need to measure analog signals. One or more thermistors are often present to measure temperatures of the system and the LEDs. The CY8CLED16P01 measures an analog signal with an analog-to-digital converter (ADC). The device can implement a variety of flexible ADC implementations. The ADCs cover a wide range of resolutions and techniques and use varied number of digital and analog block resources. For help in selecting from this multitude of ADCs, refer to application note AN2239, *Analog – ADC Selection* on http://www.cypress.com. When designing with an EZ-Color device, the number of digital and analog blocks used by an ADC must be factored into the total number of digital and analog blocks that are used.

In a typical case, such as the 3-channel color mixing firmware IP developed by Cypress, the simple 8-bit incremental ADC is used. This module occupies one digital and one switched capacitor analog block.

Analog blocks come in two types: continuous time and switched capacitor blocks. The former enables continuous time functions such as comparators and programmable gain amplifiers. The switched capacitor blocks enable functions such as ADCs and filters.

Temperature sensors with an  $I^2C$  interface can also be used instead of raw thermistors, thereby eliminating the need for ADCs and complicated processing.

#### 2.4 ColorLock Algorithm

ColorLock functionality uses feedback from an optical sensor in the system to adjust the LED dimming modulators correctly to "lock on" to a target color. This is similar to the concept of temperature compensation because it compensates for change in color. Instead of indirectly measuring change in color through temperature, it senses actual change in color and compensates for it.

The ColorLock algorithm implemented by Cypress requires the use of 10 digital blocks. Due to a 9-bit PrISM implementation, 6 digital blocks are used for dimming as in Equation 1. A 16-bit PWM and two 8-bit timers are also used to form the frame generator, pulse counter, and debounce counter.

#### 2.5 Digital Communication

Most HB LED-based lighting systems require some form of digital communication to send and receive data to and from the light fixtures to control them. The CY8CLED16P01 is a one-device solution for HB LED lighting control and powerline communication. However, the CY8CLED16P01 supports several other data communication protocols, apart from powerline communication. These are listed in Table 2-1. Some of the hardware is dedicated for a protocol and does not use any digital blocks. Some protocols use digital blocks to implement the communication.

A DMX512 protocol receiver can be implemented using two digital blocks. This is a standard protocol that is common in stage and concert lighting systems. The receiver has a software programmable address and programmable number of channels that it can control. A typical DMX512 receiver implementation (developed by Cypress) controlling three LED channels consumes five digital blocks (three for the LED modulators).

Table 2-1. Digital Communication Resource Usage

| Data Protocol                    | Digital Blocks | Communication<br>Digital Blocks |

|----------------------------------|----------------|---------------------------------|

| DMX512 (Receiver)                | 2              | 1                               |

| DALI (Slave)                     | 3              | 0                               |

| I <sup>2</sup> C Master or Slave | 0              | 0                               |

| Half Duplex UART                 | 1              | 1                               |

| SPI Master or Slave              | 1              | 1                               |

DALI is another lighting communication protocol that is common for large commercial buildings. The DALI slave can be implemented in EZ-Color consuming six digital blocks (three for the DALI slave and three to modulate 3 LED channels). The three blocks used to implement DALI need not be communication blocks as the Manchester encoding is performed in the software. Apart from these specific lighting communication protocols, the industry standard communication protocols such as  $I^2C$ , UART, and SPI can be implemented in any of the devices in the family. As examples, SPI can be used to interface to external WUSB devices, while  $I^2C$  can be used to interface to external microcontrollers.

Table 2-1 also shows the number of digital block resources that each type of communication block consumes.

#### 2.6 Other Functions

The CY8CLED16P01 is capable of functions other than those previously discussed. Most functions that can be implemented with a standard microcontroller can be also implemented with the CY8CLED16P01.

Similar to regular PSoC devices, the CY8CLED16P01 also has dynamic reconfiguration ability. This is a technique that enables the device's digital and analog resources to be reused for different functions that may not be available simultaneously. For instance, consider the application to remotely control LED color/intensity (with current feedback) over powerlines using the CY8CLED16P01 for both PLC and LED color control. The PLC functionality and the current feedback do not necessarily need to happen at the same time. Therefore, the digital and analog blocks that implement the PLC functionality can dynamically reconfigure into resources that implement current feedback. By doing this, the CY8CLED16P01 device gets more functionality out of a fixed number of resources than would otherwise be possible. The only constraint on this technique is the amount of Flash and SRAM size required for the code to implement these functions. For more details on dynamic reconfiguration, refer to application note AN2104, PSoC Dynamic Reconfiguration.

## 3. PSoC Core

The CY8CLED16P01 is based on the Cypress PSoC<sup>®</sup> 1 architecture. The PSoC platform consists of many *Programmable System-on-chip Controller* devices. These devices are designed to replace multiple traditional MCU-based system components with one, low cost single-chip programmable device. PSoC devices include configurable blocks of analog and digital logic, and programmable interconnects. This architecture enables the user to create customized peripheral configurations that match the requirements of each individual application. Additionally, a fast CPU, Flash program memory, SRAM data memory, and configurable I/Os are included in a range of convenient pinouts and packages.

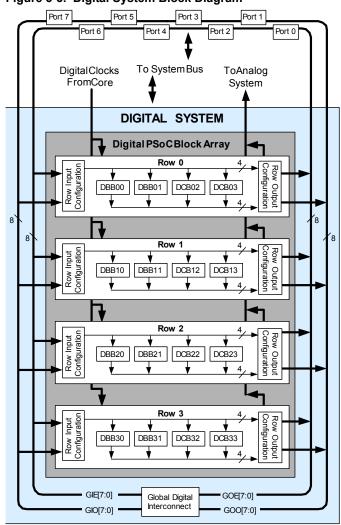

The PSoC architecture, as shown in Figure 3-1., consists of four main areas: PSoC Core, Digital System, Analog System, and System Resources. Configurable global busing enables all the device resources to be combined into a complete custom system. The CY8CLED16P01 family can have up to five I/O ports that connect to the global digital and analog interconnects, providing access to 16 digital blocks and 12 analog blocks.

The PSoC Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable GPIO (General Purpose I/O).

#### Analog Port 7 Port 6 Port 5 Port 4 Port 3 Port 2 Port 1 Port 0 Drivers YSTEM BUS Global Digital Interconnect Global Analog Interconned SRAM **PSoC CORE** SROM Flash 32K 2K CPU Core (M8C) Sleep and Interrupt Watchdog Controller Multiple Clock Sources (Includes IMO, ILO, PLL, and ECO) DIGITAL SYSTEM ANALOG SYSTEM Analog Ref. Digital Analog Block Block Arrav Arrav Analog Input Muxing POR and LVD Internal Two Digital Multiply Decimator I<sup>2</sup>C Voltage Clocks System Resets Accums. Ref. SYSTEM RESOURCES

#### Figure 3-1. PSoC Architecture

The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a 4 MIPS 8-bit Harvard architecture microprocessor. The CPU uses an interrupt controller with 25 vectors, to simplify programming of realtime embedded events. Program execution is timed and protected using the included Sleep and Watchdog timers (WDT).

Memory encompasses 32 KB of Flash for program storage, 2 KB of SRAM for data storage, and up to 2 KB of EEPROM emulated using Flash. Program Flash uses four protection levels on blocks of 64 bytes, enabling customized software IP protection.

The PSoC device incorporates flexible internal clock generators, including a 24 MHz IMO (internal main oscillator) accurate to 2.5 percent over temperature and voltage. The 24 MHz IMO can also be doubled to 48 MHz for the digital system use. A low power 32 kHz ILO (internal low speed oscillator) is provided for the sleep timer and WDT. If crystal accuracy is desired, the ECO (32.768 kHz external crystal oscillator) is available for use as a Real Time Clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL. When operating the Powerline Transceiver (PLT) user module, the ECO must be selected to ensure accurate protocol timing. The clocks, together with programmable clock dividers (as a System Resource), provide the flexibility to integrate almost any timing requirement into the PSoC device.

PSoC GPIOs provide connection to the CPU, digital, and analog resources of the device. Each pin's drive mode may be selected from eight options, enabling great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

#### 3.1 Programmable System Resources

#### Figure 3-2. Programmable System Resources

Powerline Communication Solution

Powerline Transceiver Packet

#### 3.1.1 The Digital System

The digital system contains 16 digital PSoC blocks. Each block is an 8-bit resource that can be used alone, or combined with other blocks to form 8-, 16-, 24-, and 32-bit peripherals called user module references. Digital peripheral configurations include:

- PWMs (8 to 32 bit)

- PWMs with Dead Band (8 to 32 bit)

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- UART 8 bit with selectable parity (up to four)

- SPI master and slave (up to four each)

- I<sup>2</sup>C slave and multi-master (one available as a System Resource)

- Cyclical Redundancy Checker and Generator (8 to 32 bit)

- IrDA (up to 4)

- Pseudo Random Sequence Generators (8 to 32 bit)

The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin. The buses also enable signal multiplexing and perform logic operations. This configurability frees your designs from the constraints of a fixed peripheral controller.

#### Figure 3-3. Digital System Block Diagram

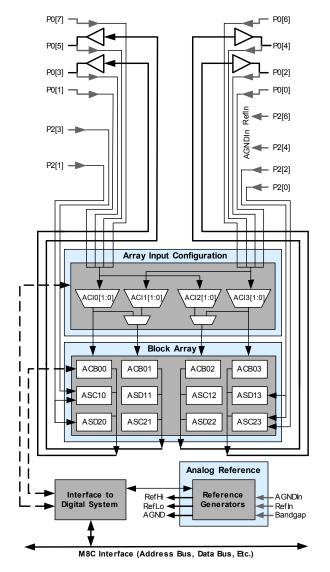

#### 3.1.2 The Analog System

The analog system contains 12 configurable blocks, each containing an opamp circuit, enabling the creation of complex analog signal flows. Analog peripherals are very flexible and can be customized to support specific application requirements. Some of the more common PSoC analog functions (most available as user modules) are:

- Analog-to-digital converters (up to 4, with 6- to 14-bit resolution, selectable as Incremental, Delta Sigma, and SAR)

- Filters (2, 4, 6, or 8 pole band pass, low pass, and notch)

- Amplifiers (up to 4, with selectable gain to 48x)

- Instrumentation amplifiers (up to 2, with selectable gain to 93x)

- Comparators (up to 4, with 16 selectable thresholds)

- DACs (up to 4, with 6- to 9-bit resolution)

- Multiplying DACs (up to 4, with 6- to 9-bit resolution)

- High current output drivers (4 with 40 mA drive as a Core Resource)

- 1.3V reference (as a System Resource)

- DTMF Dialer

- Modulators

- Correlators

- Peak detectors

- Many other topologies possible

Analog blocks are provided in columns of three, which includes one CT (continuous time) and two SC (switched capacitor) blocks, as shown in the Figure 3-4. on page 12.

#### Figure 3-4. Analog System Block Diagram

#### 3.1 Additional System Resources

#### Figure 3-5. Additional System Resources

**Powerline Communication Solution**

System Resources, some of which have been previously described, provide additional capability useful to complete systems. Resources include a multiplier, decimator, low voltage detection, and power on reset. The following statements describe the merits of each system resource.

- Digital clock dividers provide three customizable clock frequencies for use in applications. The clocks can be routed to both the digital and analog systems. Additional clocks are generated using digital PSoC blocks as clock dividers.

- Multiply accumulate (MAC) provides a fast 8-bit multiplier with 32-bit accumulate, to assist in general math and digital filters.

- The decimator provides a custom hardware filter for digital signal processing applications including the creation of Delta Sigma ADCs.

- The I<sup>2</sup>C module provides 100 and 400 kHz communication over two wires. Slave, master, and multi-master modes are supported.

- Low Voltage Detection (LVD) interrupts signal the application of falling voltage levels, while the advanced POR (Power On Reset) circuit eliminates the need for a system supervisor.

- An internal 1.3V reference provides an absolute reference for the analog system, including ADCs and DACs.

### 4. Getting Started

The quickest way to understand Cypress's Powerline Communication offering is to read this data sheet and then use the PSoC Designer Integrated Development Environment (IDE). The latest version of PSoC Designer can be downloaded from www.cypress.com/PSoCDesigner. PSoC Designer 5.0 SP5 or later provides support for CY8CLED16P01 devices. This data sheet is an overview of the CY8CLED16P01 integrated circuit and presents specific pin, register, and electrical specifications.

For in depth information, along with detailed programming details, see the PLC Technical Reference Manual.

For up to date ordering, packaging, and electrical specification information, see the latest PLC device data sheets on the web at www.cypress.com/go/plc.

#### 4.1 Application Notes

Application notes are an excellent introduction to the wide variety of possible PLC designs. They are located here: www.cypress.com/go/plc. Select Application Notes under the Support tab.

#### 4.2 Development Kits

PLC Development Kits are available online from Cypress at www.cypress.com/shop and through a growing number of regional and global distributors, which include Arrow, Avnet, Digi-Key, Farnell, Future Electronics, and Newark.

#### 4.3 Training

Free PLC technical training (on demand, webinars, and workshops) is available online at www.cypress.com/training. The training covers a wide variety of topics and skill levels to assist you in your designs.

#### 4.4 CYPros Consultants

Certified PSoC Consultants offer everything from technical assistance to completed PSoC designs. To contact or become a PSoC Consultant go to www.cypress.com/cypros.

#### 4.5 Solutions Library

Visit our growing library of solution focused designs at www.cypress.com/solutions. Here you can find various application designs that include firmware and hardware design files that enable you to complete your designs quickly.

#### 4.6 Technical Support

For assistance with technical issues, search KnowledgeBase articles and forums at www.cypress.com/support. If you cannot find an answer to your question, call technical support at 1-800-541-4736.

## 5. Development Tools

PSoC Designer is a Microsoft<sup>®</sup> Windows-based, integrated development environment for the Programmable System-on-Chip (PSoC) devices. The PSoC Designer IDE runs on Windows XP or Windows Vista.

This system provides design database management by project, an integrated debugger with In-Circuit Emulator, in-system programming support, and built in support for third party assemblers and C compilers.

PSoC Designer also supports C language compilers developed specifically for the devices in the PSoC family.

#### 5.1 PSoC Designer Software Subsystems

#### 5.1.1 System-Level View

A drag-and-drop visual embedded system design environment based on PSoC Express. In the system level view you create a model of your system inputs, outputs, and communication interfaces. You define when and how an output device changes state based upon any or all other system devices. Based upon the design, PSoC Designer automatically selects one or more PSoC Programmable System-on-Chip Controllers that match your system requirements.

PSoC Designer generates all embedded code, then compiles and links it into a programming file for a specific PSoC device.

#### 5.1.2 Chip-Level View

The chip-level view is a more traditional integrated development environment (IDE) based on PSoC Designer 4.4. Choose a base device to work with and then select different onboard analog and digital components called user modules that use the PSoC blocks. Examples of user modules are ADCs, DACs, Amplifiers, and Filters. Configure the user modules for your chosen application and connect them to each other and to the proper pins. Then generate your project. This prepopulates your project with APIs and libraries that you can use to program your application.

The device editor also supports easy development of multiple configurations and dynamic reconfiguration. Dynamic configuration allows for changing configurations at run time.

#### 5.1.3 Hybrid Designs

You can begin in the system-level view, allow it to choose and configure your user modules, routing, and generate code, then switch to the chip-level view to gain complete control over on-chip resources. All views of the project share a common code editor, builder, and common debug, emulation, and programming tools.

#### 5.1.4 Code Generation Tools

PSoC Designer supports multiple third party C compilers and assemblers. The code generation tools work seamlessly within the PSoC Designer interface and have been tested with a full range of debugging tools. The choice is yours.

**Assemblers.** The assemblers allow assembly code to merge seamlessly with C code. Link libraries automatically use absolute addressing or are compiled in relative mode, and linked with other software modules to get absolute addressing.

**C Language Compilers.** C language compilers are available that support the PSoC family of devices. The products allow you to create complete C programs for the PSoC family devices.

The optimizing C compilers provide all the features of C tailored to the PSoC architecture. They come complete with embedded libraries providing port and bus operations, standard keypad and display support, and extended math functionality.

#### 5.1.5 Debugger

The PSoC Designer Debugger subsystem provides hardware in-circuit emulation, allowing you to test the program in a physical system while providing an internal view of the PSoC device. Debugger commands allow the designer to read and program and read and write data memory, read and write IO registers, read and write CPU registers, set and clear breakpoints, and provide program run, halt, and step control. The debugger also allows the designer to create a trace buffer of registers and memory locations of interest.

#### 5.1.6 Online Help System

The online help system displays online, context-sensitive help for the user. Designed for procedural and quick reference, each functional subsystem has its own context-sensitive help. This system also provides tutorials and links to FAQs and an Online Support Forum to aid the designer in getting started.

#### 5.2 In-Circuit Emulator (ICE)

A low cost, high functionality In-Circuit Emulator (ICE) is available for development support. This hardware has the capability to program single devices.

The emulator consists of a base unit that connects to the PC by way of a USB port. The base unit is universal and operates with all PSoC devices. Emulation pods for each device family are available separately. The emulation pod takes the place of the PSoC device in the target board and performs full speed (24 MHz) operation.

## 6. Designing with User Modules

The development process for the PSoC device differs from that of a traditional fixed function microprocessor. The configurable analog and digital hardware blocks give the PSoC architecture a unique flexibility that pays dividends in managing specification change during development and by lowering inventory costs. These configurable resources, called PSoC Blocks, have the ability to implement a wide variety of user selectable functions.

The PSoC development process can be summarized in the following four steps:

- 1. Select Components

- 2. Configure Components

- 3. Organize and Connect

- 4. Generate, Verify, and Debug

#### 6.1 Select Components

Both the system-level and chip-level views provide a library of prebuilt, pretested hardware peripheral components. In the system-level view, these components are called "drivers" and correspond to inputs (a thermistor, for example), outputs (a brushless DC fan, for example), communication interfaces (I<sup>2</sup>C-bus, for example), and the logic to control how they interact with one another (called valuators).

In the chip-level view, the components are called "user modules". User modules make selecting and implementing peripheral devices simple, and come in analog, digital, and programmable system-on-chip varieties.

#### 6.2 Configure Components

Each of the components you select establishes the basic register settings that implement the selected function. They also provide parameters and properties that allow you to tailor their precise configuration to your particular application. For example, a Pulse Width Modulator (PWM) User Module configures one or more digital PSoC blocks, one for each 8 bits of resolution. The user module parameters permit you to establish the pulse width and duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by selecting values from drop-down menus.

Both the system-level drivers and chip-level user modules are documented in data sheets that are viewed directly in the PSoC Designer. These data sheets explain the internal operation of the component and provide performance specifications. Each data sheet describes the use of each user module parameter or driver property, and other information you may need to successfully implement your design.

#### 6.3 Organize and Connect

You can build signal chains at the chip level by interconnecting user modules to each other and the IO pins, or connect system level inputs, outputs, and communication interfaces to each other with valuator functions.

In the system-level view, selecting a potentiometer driver to control a variable speed fan driver and setting up the valuators to control the fan speed based on input from the pot selects, places, routes, and configures a programmable gain amplifier (PGA) to buffer the input from the potentiometer, an analog to digital converter (ADC) to convert the potentiometer's output to a digital signal, and a PWM to control the fan.

In the chip-level view, perform the selection, configuration, and routing so that you have complete control over the use of all on-chip resources.

#### 6.4 Generate, Verify, and Debug

When you are ready to test the hardware configuration or move on to developing code for the project, perform the "Generate Application" step. This causes PSoC Designer to generate source code that automatically configures the device to your specification and provides the software for the system.

Both system-level and chip-level designs generate software based on your design. The chip-level design provides application programming interfaces (APIs) with high level functions to control and respond to hardware events at run time and interrupt service routines that you can adapt as needed. The system-level design also generates a C main() program that completely controls the chosen application and contains placeholders for custom code at strategic positions allowing you to further refine the software without disrupting the generated code.

A complete code development environment allows you to develop and customize your applications in C, assembly language, or both.

The last step in the development process takes place inside the PSoC Designer's Debugger subsystem. The Debugger downloads the HEX image to the ICE where it runs at full speed. Debugger capabilities rival those of systems costing many times more. In addition to traditional single-step, run-to-breakpoint and watch-variable features, the Debugger provides a large trace buffer and allows you define complex breakpoint events that include monitoring address and data bus values, memory locations and external signals.

#### 6.5 PLC User Modules

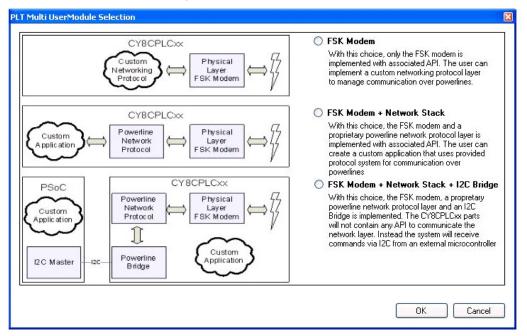

The CY8CLEDP01 has the Powerline Transceiver (PLT) User Module in PSoC Designer 5.0 SP5 or later. The PLT User Module (UM) enables data communication over powerlines up to baud rates of 2400 bps. This UM also exposes all the APIs from the network protocol for ease of application development. The UM, when instantiated, provides the user with three implementation modes:

- FSK Modem Only This mode enables the user to use the raw FSK modem and build any network protocol or application with the help of the APIs generated by the modem PHY.

- FSK Modem + Network Stack This mode allows the user to use the Cypress network protocol for PLC and build any application with the APIs provided by the network protocol.

- FSK Modem + Network Stack + I2C This mode allows the user to interface the CY8CLEDP01 with any other microcontroller or PSoC device. Users can also split the application between the PLC device and the external microcontroller. If the external microcontroller is a PSoC device, then the I2C UMs can be used to interface it with the PLC device.

Figure 6-1. shows the starting window for the PLT UM with the three implementation modes from which the user can choose.

#### Figure 6-1. PLT User Module

Refer to the application note AN55403 - "Estimating CY8CPLC20/CY8CLED16P01 Power Consumption" to determine the power consumption estimate of the CY8CLED16P01 chip with the PLT User Module, loaded along with the other User Modules.

#### 6.1 Intelligent Lighting User Modules

The CY8CLED16P01 has the intelligent lighting control user modules along with the PLC user modules. These user modules enable the user to do the following:

- Control multiple channels, anywhere between 1 and 16.

- Enable temperature compensation and color feedback

- Provide algorithms for high CRI

- Control color with 1931 or 1976 gamuts and through CCT

- Provide additional communication interfaces such as DALI and DMX512

## 7. Document Conventions

#### 7.1 Acronyms Used

This table lists the acronyms used in this data sheet.

#### Table 7-1. Acronyms

| Acronym | Description                                         |

|---------|-----------------------------------------------------|

| AC      | alternating current                                 |

| ADC     | analog-to-digital converter                         |

| API     | application programming interface                   |

| CPU     | central processing unit                             |

| СТ      | continuous time                                     |

| DAC     | digital-to-analog converter                         |

| DC      | direct current                                      |

| EEPROM  | electrically erasable programmable read-only memory |

| FSR     | full scale range                                    |

| GPIO    | general purpose IO                                  |

| ICE     | in-circuit emulator                                 |

| IDE     | integrated development environment                  |

| IO      | input/output                                        |

| ISSP    | in-system serial programming                        |

| IPOR    | imprecise power on reset                            |

| LSb     | least-significant bit                               |

| LVD     | low voltage detect                                  |

| MSb     | most-significant bit                                |

| PC      | program counter                                     |

| PGA     | programmable gain amplifier                         |

| POR     | power on reset                                      |

| PPOR    | precision power on reset                            |

| PSoC®   | Programmable System-on-Chip                         |

| PWM     | pulse width modulator                               |

| ROM     | read only memory                                    |

| SC      | switched capacitor                                  |

| SRAM    | static random access memory                         |

#### 7.2 Units of Measure

A units of measure table is located in the section Electrical Specifications on page 25.

#### 7.3 Numeric Naming

Hexadecimal numbers are represented with all letters in uppercase with an appended lowercase 'h' (for example, '14h' or '3Ah'). Hexadecimal numbers may also be represented by a '0x' prefix, the C coding convention. Binary numbers have an appended lowercase 'b' (for example, 01010100b' or '01000011b'). Numbers not indicated by an 'h', 'b', or 0x are decimal.

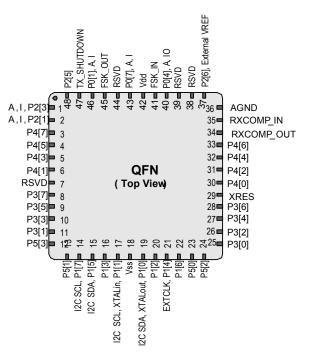

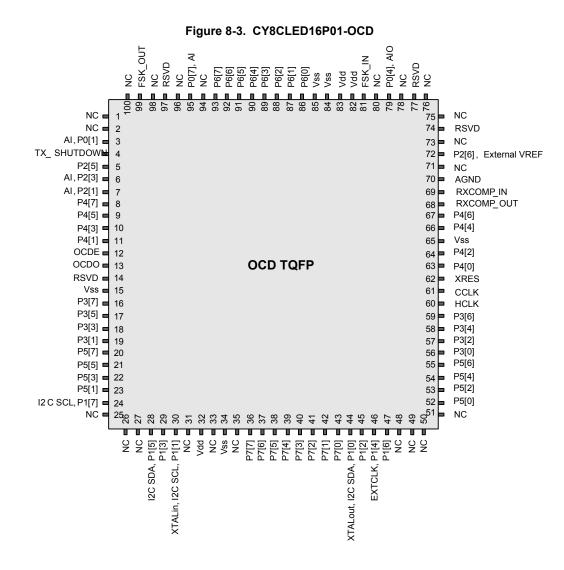

## 8. Pin Information

The CY8CLED16P01 PLC device is available in a variety of packages which are listed and illustrated in the following tables. Every port pin (labeled with a "P") is capable of Digital I/O. However, Vss, Vdd, and XRES are not capable of Digital I/O.

#### 8.1 28-Pin Part Pinout

| Table 8-1. 28-Pin Part Pinout (SSOP) |      |          |    |  |  |  |

|--------------------------------------|------|----------|----|--|--|--|

| Pin                                  | Туре | Din Nome | De |  |  |  |

| Dim        | Pin Type |        | •               | ,                                                                                                                                                                   | Figure 8-1. C                    | CY8CI                           | FD1              | 6P01 28-P     | in PLC Device                                                 |

|------------|----------|--------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------------------|------------------|---------------|---------------------------------------------------------------|

| Pin<br>No. | Digital  | Analog | Pin Name        | Description                                                                                                                                                         |                                  |                                 |                  | 01 01 20 1    |                                                               |

| 1          | 10       |        | P0[7]           | Analog Column Mux Input                                                                                                                                             |                                  |                                 | D,               | $\overline{}$ |                                                               |

| 2          | Rese     | erved  | RSVD            | Reserved                                                                                                                                                            |                                  | P0[7] <b>=</b><br>RSVD <b>=</b> | 1                |               | 28■ Vdd<br>27■ FSK_IN                                         |

| 3          |          | 0      | FSK_OUT         | Analog FSK Output                                                                                                                                                   |                                  |                                 | 2<br>3           |               | 2/ PSK_IN<br>26 P0[4],A,IO                                    |

| 4          | 10       | I      | P0[1]           | Analog Column Mux Input                                                                                                                                             |                                  | P0[1]                           | 3<br>4           |               | 25 <b>–</b> RSVD                                              |

| 5          | 0        |        | TX_SHUT<br>DOWN | Output to disable PLC transmit<br>circuitry in receive mode<br>Logic '0' - When the Modem is trans-<br>mitting<br>Logic '1' - When the Modem is not<br>transmitting | TX_ SHUTD<br>F<br>A,I,F<br>A,I,I |                                 | 5<br>6<br>7<br>8 | SSOP          | 24 RSVD<br>23 P2[6], External VREF<br>22 AGND<br>21 RXCOMP_IN |

| 6          | 10       |        | P2[5]           |                                                                                                                                                                     |                                  | ·                               | 9                |               | 20 RXCOMP_OUT                                                 |

| 7          | 10       | 1      | P2[3]           | Direct switched capacitor block input                                                                                                                               | I2C SCL, F<br>I2C SDA, I         |                                 | 10               |               | 19 <b>–</b> XRES<br>18 <b>–</b> P1[6]                         |

| 8          | 10       | I      | P2[1]           | Direct switched capacitor block input                                                                                                                               |                                  | P1[3]                           | 11               |               | 17 P1[4], EXTCLK                                              |

| 9          |          | erved  | RSVD            | Reserved                                                                                                                                                            | I2C SCL, XTALin, I               |                                 | 12<br>13         |               | 16 <b>-</b> P1[2]                                             |

| 10         | 10       |        | P1[7]           | I2C Serial Clock (SCL)                                                                                                                                              | IZC SCL, ATALIII,I               | Vss                             | 13<br>14         |               | 15 P1[0], XTALout, I2C SDA                                    |

| 11         | 10       |        | P1[5]           | I2C Serial Data (SDA)                                                                                                                                               |                                  | <sup>v 33</sup>                 | 14               |               | 15- 1 1[0], XTAL00, 120 3DA                                   |

| 12         | 10       |        | P1[3]           | XTAL_STABILITY. Connect a 0.1 uF capacitor between the pin and VSS.                                                                                                 |                                  |                                 |                  |               |                                                               |

| 13         | IO       |        | P1[1]           | Crystal (XTALin) <sup>[2]</sup> , ISSP-SCLK <sup>[1]</sup> ,<br>I2C SCL                                                                                             |                                  |                                 |                  |               |                                                               |

| 14         | Po       | wer    | Vss             | Ground connection.                                                                                                                                                  |                                  |                                 |                  |               |                                                               |

| 15         | IO       |        | P1[0]           | Crystal (XTALout) <sup>[2]</sup> , ISSP-SDATA <sup>[1]</sup> ,<br>I2C SDA                                                                                           |                                  |                                 |                  |               |                                                               |

| 16         | 10       |        | P1[2]           |                                                                                                                                                                     |                                  |                                 |                  |               |                                                               |

| 17         | 10       |        | P1[4]           | Optional External Clock Input<br>(EXTCLK) <sup>[2]</sup>                                                                                                            |                                  |                                 |                  |               |                                                               |

| 18         | 10       |        | P1[6]           |                                                                                                                                                                     |                                  |                                 |                  |               |                                                               |

| 19         | Inj      | put    | XRES            | Active high external reset with<br>internal pull down                                                                                                               |                                  |                                 |                  |               |                                                               |

| 20         |          | 0      | RXCOMP_<br>OUT  | Analog Output to external Low Pass<br>Filter Circuitry                                                                                                              |                                  |                                 |                  |               |                                                               |

| 21         |          | I      | RXCOMP_<br>IN   | Analog Input from the external Low<br>Pass Filter Circuitry                                                                                                         |                                  |                                 |                  |               |                                                               |

| 22         | Analog   | Ground | AGND            | Analog Ground                                                                                                                                                       |                                  |                                 |                  |               |                                                               |

| 23         | 10       |        | P2[6]           | External Voltage Reference (VREF)                                                                                                                                   |                                  |                                 |                  |               |                                                               |

| 24         | Rese     | erved  | RSVD            | Reserved                                                                                                                                                            |                                  |                                 |                  |               |                                                               |

| 25         | Rese     | erved  | RSVD            | Reserved                                                                                                                                                            |                                  |                                 |                  |               |                                                               |

| 26         | IO       | IO     | P0[4]           | Analog column mux input and column output                                                                                                                           |                                  |                                 |                  |               |                                                               |

| 27         |          | I      | FSK_IN          | Analog FSK Input                                                                                                                                                    |                                  |                                 |                  |               |                                                               |

| 28         | Po       | wer    | Vdd             | Supply Voltage                                                                                                                                                      | ]                                |                                 |                  |               |                                                               |