Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# EZ-BLE™ PSoC® Module

## **General Description**

The Cypress CYBLE-014008-00 is a fully certified and qualified module supporting Bluetooth® Low Energy (BLE) wireless communication. The CYBLE-014008-00 is a turnkey solution and includes onboard crystal oscillators, trace antenna, passive components, and the Cypress PSoC® 4 BLE. Refer to the PSoC® 4 BLE datasheet for additional details on the capabilities of the PSoC 4 BLE device used on this module.

The EZ-BLE<sup>TM</sup> PSoC<sup>®</sup> module is a scalable and reconfigurable platform architecture. It combines programmable and reconfigurable analog and digital blocks with flexible automatic routing. The CYBLE-014008-00 also includes digital programmable logic, high-performance analog-to-digital conversion (ADC), opamps with comparator mode, and standard communication and timing peripherals.

The CYBLE-014008-00 includes a royalty-free BLE stack compatible with Bluetooth 4.1 and provides up to 25 GPIOs in a small  $11 \times 11 \times 1.80$ -mm package.

The CYBLE-014008-00 is a complete solution and an ideal fit for applications seeking a highly integrated BLE wireless solution.

#### **Module Description**

- Module size: 11.0 mm × 11.0 mm × 1.80 mm (with shield)

- 128-KB flash memory, 16-KB SRAM memory

- Up to 25 GPIOs configurable as open drain high/low, pull-up/pull-down, HI-Z analog, HI-Z digital, or strong output

- Bluetooth 4.1 qualified single-mode module

- □ QDID: 79697

□ Declaration ID: D029647

- Certified to FCC, CE, MIC, KC, and IC regulations

- Industrial temperature range: -40 °C to +85 °C

- 32-bit processor (0.9 DMIPS/MHz) with single-cycle 32-bit multiply, operating at up to 48 MHz

- Watchdog timer with dedicated internal low-speed oscillator (II O)

- Two-pin SWD for programming

#### **Power Consumption**

- TX output power: -18 dbm to +3 dbm

- Received signal strength indicator (RSSI) with 1-dB resolution

- TX current consumption of 15.6 mA (radio only, 0 dbm)

- RX current consumption of 16.4 mA (radio only)

#### ■ Low power mode support

- Deep Sleep: 1.3 μA with watch crystal oscillator (WCO) on

- ☐ Hibernate: 150 nA with SRAM retention

- ☐ Stop: 60 nA with GPIO (P2.2) or XRES wakeup

#### **Programmable Analog**

- Four opamps with reconfigurable high-drive external and high-bandwidth internal drive, comparator modes, and ADC input buffering capability; can operate in Deep-Sleep mode

- 12-bit, 1-Msps SAR ADC with differential and single-ended modes; channel sequencer with signal averaging

- Two current DACs (IDACs) for general-purpose or capacitive sensing applications on any pin

- One low-power comparator that operate in Deep-Sleep mode

#### **Programmable Digital**

- Four programmable logic blocks called universal digital blocks, (UDBs), each with eight macrocells and datapath

- Cypress-provided peripheral Component library, user-defined state machines, and Verilog input

#### **Capacitive Sensing**

- Cypress CapSense Sigma-Delta (CSD) provides best-in-class SNR (> 5:1) and liquid tolerance

- Cypress-supplied software component makes capacitive-sensing design easy

- Automatic hardware-tuning algorithm (SmartSense<sup>TM</sup>)

#### Segment LCD Drive

- LCD drive supported on all GPIOs (common or segment)

- Operates in Deep-Sleep mode with four bits per pin memory

#### **Serial Communication**

■ Two independent runtime reconfigurable serial communication blocks (SCBs) with I<sup>2</sup>C, SPI, or UART functionality

#### Timing and Pulse-Width Modulation

- Four 16-bit timer, counter, pulse-width modulator (TCPWM) blocks

- Center-aligned, Edge, and Pseudo-random modes

- Comparator-based triggering of Kill signals for motor drive and other high-reliability digital logic applications

#### **Up to 25 Programmable GPIOs**

$\blacksquare$  Any GPIO pin can be CapSense, LCD, analog, or digital

Cypress Semiconductor Corporation Document Number: 002-00023 Rev. \*J

198 Champion Court • Sa

San Jose, CA 95134-1709

408-943-2600

Revised April 24, 2017

#### More Information

Cypress provides a wealth of data at www.cypress.com to help you to select the right module for your design, and to help you to quickly and effectively integrate the module into your design.

- Overview: EZ-BLE Module Portfolio, Module Roadmap

- EZ-BLE PSoC Product Overview

- PSoC 4 BLE Silicon Datasheet

- Application notes: Cypress offers a number of BLE application notes covering a broad range of topics, from basic to advanced level. Recommended application notes for getting started with EZ-BLE modules are:

- □ AN96841 Getting Started with EZ-BLE Module

- □ AN94020 Getting Started with PSoC® 4 BLE

- □ AN97060 PSoC® 4 BLE and PRoC™ BLE Over-The-Air (OTA) Device Firmware Upgrade (DFU) Guide

- □ AN91162 Creating a BLE Custom Profile

- □ AN91184 PSoC 4 BLE Designing BLE Applications

- AN92584 Designing for Low Power and Estimating Battery Life for BLE Applications

- □ AN85951 PSoC® 4 CapSense® Design Guide

- □ AN95089 PSoC® 4/PRoC™ BLE Crystal Oscillator Selection and Tuning Techniques

- □ AN91445 Antenna Design and RF Layout Guidelines

- Technical Reference Manual (TRM):

- □ PSoC® 4 BLE Technical Reference Manual

- ☐ PSOC® 4 BLE Registers Technical Reference Manual (TRM)

#### ■ Knowledge Base Articles

- □ KBA97279 Pin Mapping Differences Between the EZ-BLE™ PRoC™ Evaluation Board (CYBLE-014008-EVAL) and the BLE Pioneer Kit (CY8CKIT-042-BLE)

- □ KBA210574 RF Regulatory Certifications for CY-BLE-014008-00 and CYBLE-214009-00 EZ-BLE™ PSoC® Modules - KBA210574

- □ KBA97095 EZ-BLE™ Module Placement

- □ KBA213976 FAQ for BLE and Regulatory Certifications with EZ-BLE modules

- □ KBA210802 Queries on BLE Qualification and Declaration Processes

- Development Kits:

- □ CYBLE-014008-EVAL, CYBLE-014008-00 Evaluation Board

- □ CY8CKIT-042-BLE, Bluetooth<sup>®</sup> Low Energy (BLE) Pioneer Kit

- □ CY8CKIT-002, PSoC® MiniProg3 Program and Debug Kit

- Test and Debug Tools:

- □ CYSmart, Bluetooth® LE Test and Debug Tool (Windows)

- CYSmart Mobile, Bluetooth<sup>®</sup> LE Test and Debug Tool (Android/iOS Mobile App)

## Two Design Environments to Get You Started Quickly

## PSoC<sup>®</sup> Creator™ Integrated Design Environment (IDE)

PSoC Creator is an Integrated Design Environment (IDE) that enables concurrent hardware and firmware editing, compiling and debugging of PSoC 3, PSoC 4, PSoC 5LP, PSoC 4 BLE, PRoC BLE, and EZ-BLE module systems with no code size limitations. PSoC peripherals are designed using schematic capture and simple graphical user interface (GUI) with over 120 pre-verified, production-ready PSoC Components<sup>TM</sup>.

PSoC Components are analog and digital "virtual chips," represented by an icon that users can drag-and-drop into a design and configure to suit a broad array of application requirements.

#### Bluetooth Low Energy Component

The Bluetooth Low Energy Component inside PSoC Creator provides a comprehensive GUI-based configuration window that lets you quickly design BLE applications. The Component incorporates a Bluetooth Core Specification v4.1 compliant BLE protocol stack and provides API functions to enable user applications to interface with the underlying Bluetooth Low Energy Sub-System (BLESS) hardware via the stack.

#### **EZ-Serial™ BLE Firmware Platform**

The EZ-Serial Firmware Platform provides a simple way to access the most common hardware and communication features needed in BLE applications. EZ-Serial implements an intuitive API protocol over the UART interface and exposes various status and control signals through the module's GPIOs, making it easy to add BLE functionality quickly to existing designs.

Use a simple serial terminal and evaluation kit to begin development without requiring an IDE. Refer to the EZ-Serial webpage for User Manuals and instructions for getting started as well as detailed reference materials.

EZ-BLE modules are pre-flashed with the EZ-Serial Firmware Platform. If you do not have EZ-Serial pre-loaded on your module, you can download each EZ-BLE module's firmware images on the EZ-Serial webpage.

#### Technical Support

- Frequently Asked Questions (FAQs): Learn more about our BLE ecosystem.

- Forum: See if your question is already answered by fellow developers on the PSoC 4 BLE and PRoC BLE forums.

- Visit our support page and create a technical support case or contact a local sales representatives. If you are in the United States, you can talk to our technical support team by calling our toll-free number: +1-800-541-4736. Select option 2 at the prompt.

### **Contents**

| Overview                                        | . 4 |

|-------------------------------------------------|-----|

| Module Description                              | . 4 |

| Pad Connection Interface                        | . 6 |

| Recommended Host PCB Layout                     |     |

| Digital and Analog Capabilities and Connections | . 9 |

| Power Supply Connections and Recommended Exteri |     |

| Components                                      |     |

| Power Connections                               |     |

| Connection Options                              |     |

| External Component Recommendation               |     |

| Critical Components List                        |     |

| Antenna Design                                  |     |

| Electrical Specification                        |     |

| GPIO                                            |     |

| XRES                                            | 18  |

| Analog Peripherals                              | 18  |

| Digital Peripherals                             |     |

| Serial Communication                            |     |

| Memory                                          | 25  |

| System Resources                                |     |

| Environmental Specifications                    |     |

| Environmental Compliance                        |     |

| RF Certification                                |     |

| Environmental Conditions                        |     |

| ESD and EMI Protection                          | 31  |

| Regulatory Information                  | 32 |

|-----------------------------------------|----|

| FCC                                     | 32 |

| Industry Canada (IC) Certification      | 33 |

| · · ·                                   | 33 |

| MIC Japan                               | 34 |

|                                         | 34 |

|                                         | 35 |

| Ordering Information                    | 37 |

| Part Numbering Convention               | 37 |

|                                         | 38 |

|                                         | 40 |

| Units of Measure                        | 40 |

| Document History Page                   | 41 |

| Sales, Solutions, and Legal Information | 43 |

| Worldwide Sales and Design Support      | 43 |

| Products                                | 43 |

| PSoC®Solutions                          | 43 |

| Cypress Developer Community             | 43 |

| Technical Support                       | 43 |

### Overview

#### **Module Description**

The CYBLE-014008-00 module is a complete module designed to be soldered to the main host board.

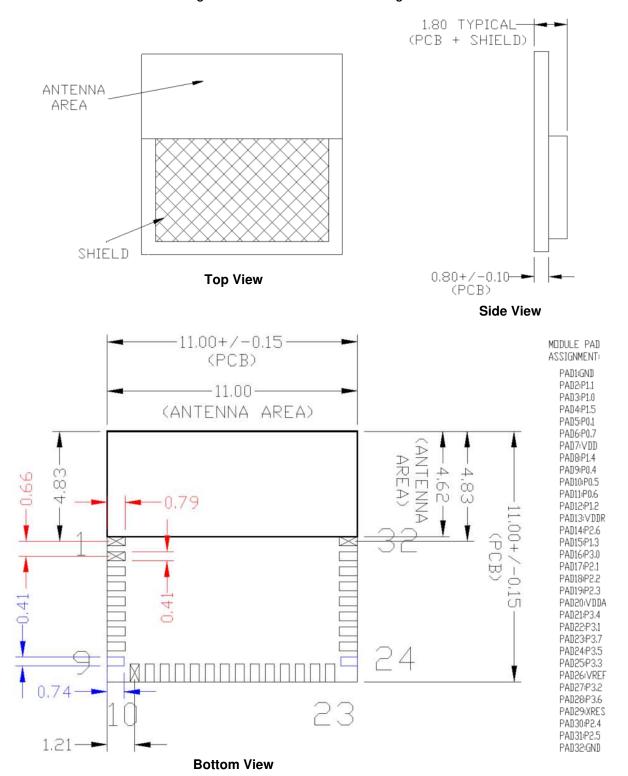

Module Dimensions and Drawing

Cypress reserves the right to select components (including the appropriate BLE device) from various vendors to achieve the BLE module functionality. Such selections will guarantee that all height restrictions of the component area are maintained. Designs should be completed with the physical dimensions shown in the mechanical drawings in Figure 1 on page 5. All dimensions are in millimeters (mm).

**Table 1. Module Design Dimensions**

| Dimension Item                                                 | Specification |                          |

|----------------------------------------------------------------|---------------|--------------------------|

| Module dimensions                                              | Length (X)    | 11.00 ± 0.15 mm          |

| iviodule difficisions                                          | Width (Y)     | 11.00 ± 0.15 mm          |

| Antenna location dimensions                                    | Length (X)    | 11.00 ± 0.15 mm          |

| Antenna location dimensions                                    | Width (Y)     | 4.62 ± 0.15 mm           |

| PCB thickness                                                  | Height (H)    | 0.80 ± 0.10 mm           |

| Shield height                                                  | Height (H)    | 1.00 ± 0.10 mm           |

| Maximum component height                                       | Height (H)    | 1.00 mm typical (shield) |

| Total module thickness (bottom of module to highest component) | Height (H)    | 1.80 mm typical          |

See Figure 1 on page 5 for the mechanical reference drawing for CYBLE-014008-00.

Figure 1. Module Mechanical Drawing

#### Note

<sup>1.</sup> No metal should be located beneath or above the antenna area. Only bare PCB material should be located beneath the antenna area. For more information on recommended host PCB layout, see Figure 3 on page 6, Figure 4 and Figure 5 on page 7, and Figure 6 and Table 3 on page 8.

#### **Pad Connection Interface**

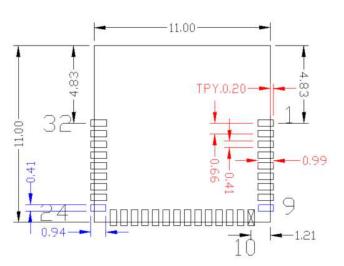

As shown in the bottom view of Figure 1 on page 5, the CYBLE-014008-00 connects to the host board via solder pads on the back of the module. Table 2 and Figure 2 detail the solder pad length, width, and pitch dimensions of the CYBLE-014008-00 module.

Table 2. Solder Pad Connection Description

| Name | Connections | Connection Type | Pad Length Dimension                       | Pad Width Dimension | Pad Pitch |

|------|-------------|-----------------|--------------------------------------------|---------------------|-----------|

| SP   | 32          | Solder Pads     | Pad9/Pad24: 0.74 mm<br>All Others: 0.79 mm | 0.41 mm             | 0.66 mm   |

14.0 14.0 10.74 1.21 23

Figure 2. Solder Pad Dimensions (Seen from Bottom)

To maximize RF performance, the host layout should follow these recommendations:

- The ideal placement of the Cypress BLE module is in a corner of the host board with the antenna located on the edge of the host board. This placement minimizes the additional recommended keep-out area stated in item 2. Refer to AN96841 for module placement best practices.

- 2. To maximize RF performance, the area immediately around the Cypress BLE module trace antenna should contain an additional keep-out area, where no grounding or signal traces are contained. The keep-out area applies to all layers of the host board. The recommended dimensions of the host PCB keep-out area are shown in Figure 3 (dimensions are in mm).

Figure 3. Recommended Host PCB Keep-Out Area Around the CYBLE-014008-00 Trace Antenna

## **Recommended Host PCB Layout**

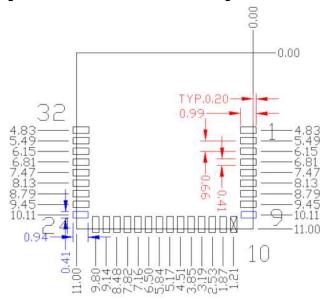

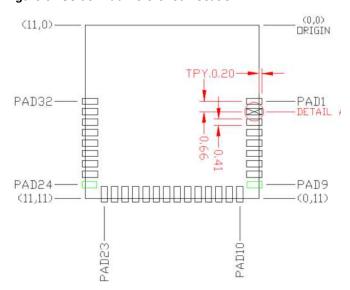

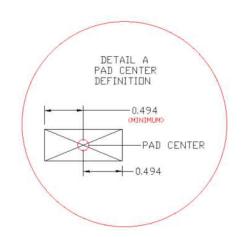

Figure 4 through Figure 6 and Table 3 provide details that can be used for the recommended host PCB layout pattern for the CYBLE-014008-00. Dimensions are in millimeters unless otherwise noted. Pad length of 0.99 mm (0.494 mm from center of the pad on either side) shown in Figure 6 is the minimum recommended host pad length. The host PCB layout pattern can be completed using either Figure 4, Figure 5, or Figure 6. It is not necessary to use all figures to complete the host PCB layout pattern.

Figure 4. Host Layout Pattern for CYBLE-014008-00

Top View (Seen on Host PCB)

Figure 5. Module Pad Location from Origin

Top View (Seen on Host PCB)

Table 3 provides the center location for each solder pad on the CYBLE-014008-00. All dimensions are referenced to the center of the solder pad. Refer to Figure 6 for the location of each module solder pad.

**Table 3. Module Solder Pad Location**

| Solder Pad<br>(Center of Pad) | Location (X,Y) from<br>Orign (mm) | Dimension from<br>Orign (mils) |

|-------------------------------|-----------------------------------|--------------------------------|

| 1                             | (0.30, 4.83)                      | (11.81, 190.16)                |

| 2                             | (0.30, 5.49)                      | (11.81, 216.14)                |

| 3                             | (0.30, 6.15)                      | (11.81, 242.13)                |

| 4                             | (0.30, 6.81)                      | (11.81, 268.11)                |

| 5                             | (0.30, 7.47)                      | (11.81, 294.09)                |

| 6                             | (0.30, 8.13)                      | (11.81, 320.08)                |

| 7                             | (0.30, 8.79)                      | (11.81, 346.06)                |

| 8                             | (0.30, 9.45)                      | (11.81, 372.05)                |

| 9                             | (0.27, 10.11)                     | (10.63, 398.03)                |

| 10                            | (1.21, 10.70)                     | (47.64, 421.26)                |

| 11                            | (1.87, 10.70)                     | (73.62, 421.26)                |

| 12                            | (2.53, 10.70)                     | (99.61, 421.26)                |

| 13                            | (3.19, 10.70)                     | (125.59, 421.26)               |

| 14                            | (3.85, 10.70)                     | (151.57, 421.26)               |

| 15                            | (4.51, 10.70)                     | (177.56, 421.26)               |

| 16                            | (5.17, 10.70)                     | (203.54, 421.26)               |

| 17                            | (5.84, 10.70)                     | (229.92, 421.26)               |

| 18                            | (6.50, 10.70)                     | (255.91, 421.26)               |

| 19                            | (7.16, 10.70)                     | (281.89, 421.26)               |

| 20                            | (7.82, 10.70)                     | (307.87, 421.26)               |

| 21                            | (8.48, 10.70)                     | (333.86, 421.26)               |

| 22                            | (9.14, 10.70)                     | (359.84, 421.26)               |

| 23                            | (9.80, 10.70)                     | (385.83, 421.26)               |

| 24                            | (10.73, 10.11)                    | (422.44, 398.03)               |

| 25                            | (10.70, 9.45)                     | (421.26, 372.05)               |

| 26                            | (10.70, 8.79)                     | (421.26, 346.06)               |

| 27                            | (10.70, 8.13)                     | (421.26, 320.08)               |

| 28                            | (10.70, 7.47)                     | (421.26, 294.09)               |

| 29                            | (10.70, 6.81)                     | (421.26, 268.11)               |

| 30                            | (10.70, 6.15)                     | (421.26, 242.13)               |

| 31                            | (10.70, 5.49)                     | (421.26, 216.14)               |

| 32                            | (10.70, 4.83)                     | (421.26, 190.16)               |

Figure 6. Solder Pad Reference Location

Top View (Seen on Host PCB)

## **Digital and Analog Capabilities and Connections**

Table 4 and Table 5 detail the solder pad connection definitions and available functions for each connection pad. Table 4 lists the solder pads on CYBLE-014008-00, the BLE device port-pin, and denotes whether the digital function shown is available for each solder pad. Table 5 denotes whether the analog function shown is available for each solder pad. Each connection is configurable for a single option shown with a  $\checkmark$ .

Table 4. Digital Peripheral Capabilities

| Pad<br>Number | Device<br>Port Pin | UART              | SPI          | I <sup>2</sup> C | <b>TCPWM</b> <sup>[2,3]</sup> | CapSense      | WCO<br>Out | ECO<br>OUT | LCD      | SWD                  | GPIO     |

|---------------|--------------------|-------------------|--------------|------------------|-------------------------------|---------------|------------|------------|----------|----------------------|----------|

| 1             | GND <sup>[4]</sup> | Ground Connection |              |                  |                               |               |            |            |          |                      |          |

| 2             | P1.1               |                   | ✓(SCB1_SS1)  |                  | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>\</b> |                      | <b>/</b> |

| 3             | P1.0               |                   |              |                  | ✓(TCPWM)                      | /             |            |            | <b>/</b> |                      | <b>✓</b> |

| 4             | P1.5               | ✓(SCB0_TX)        | . – ,        | ✓(SCB0_SCL)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>/</b> |                      | <b>/</b> |

| 5             | P0.1               | ✓(SCB1_TX)        | . – ,        | ✓(SCB1_SCL)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>\</b> |                      | <b>/</b> |

| 6             | P0.7               | ✓(SCB0_CTS)       | ✓(SCB0_SCLK) |                  | ✓(TCPWM)                      | /             |            |            | <b>\</b> | <b>√</b><br>(SWDCLK) | /        |

| 7             | VDD                |                   |              | -                | er Supply Input (1            | .71 to 5.5V)  | •          | •          |          |                      |          |

| 8             | P1.4               | ✓(SCB0_RX)        |              |                  | ✓(TCPWM)                      |               |            |            | <b>/</b> |                      | <b>/</b> |

| 9             | P0.4               | ✓(SCB0_RX)        | √(SCB0_MOSI) | ✓(SCB0_SDA)      | ✓(TCPWM)                      | <b>/</b>      |            | <b>/</b>   | <b>✓</b> |                      | <b>✓</b> |

| 10            | P0.5               | ✓(SCB0_TX)        | ✓(SCB0_MISO) | ✓(SCB0_SCL)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 11            | P0.6               | ✓(SCB0_RTS)       | ✓(SCB0_SS0)  |                  | <b>√</b> (TCPWM)              | 1             |            |            | 1        | (SWDIO)              | 1        |

| 12            | P1.2               |                   | ✓(SCB1_SS2)  |                  | ✓(TCPWM)                      | <b>✓</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 13            | $V_{\mathrm{DDR}}$ |                   |              | Radio Po         | ower Supply (1.9\             | / to 5.5V)    |            |            |          |                      |          |

| 14            | P2.6               |                   |              |                  | ✓(TCPWM)                      | <b>_</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 15            | P1.3               |                   | ✓(SCB1_SS3)  |                  | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 16            | P3.0               | ✓(SCB0_RX)        |              | ✓(SCB0_SDA)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>/</b> |                      | <b>✓</b> |

| 17            | P2.1               |                   | ✓(SCB0_SS2)  |                  | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>/</b> |                      | <b>/</b> |

| 18            | P2.2               |                   | ✓(SCB0_SS3)  |                  | ✓(TCPWM)                      | /             |            |            | <b>/</b> |                      | <b>✓</b> |

| 19            | P2.3               |                   |              |                  | ✓(TCPWM)                      | <b>/</b>      | /          |            | <b>/</b> |                      | <b>/</b> |

| 20            | VDDA               |                   |              | Analog Pow       | er Supply Input (             | 1.71 to 5.5V) | •          | •          |          |                      |          |

| 21            | P3.4               | ✓(SCB1_RX)        |              | ✓(SCB1_SDA)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>/</b> |                      | <b>/</b> |

| 22            | P3.1               | ✓(SCB0_TX)        |              | ✓(SCB0_SCL)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>/</b> |                      | <b>✓</b> |

| 23            | P3.7               | ✓(SCB1_CTS)       |              |                  | ✓(TCPWM)                      | <b>/</b>      | <b>/</b>   |            | <b>✓</b> |                      | <b>/</b> |

| 24            | P3.5               | ✓(SCB1_TX)        |              | ✓(SCB1_SCL)      | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 25            | P3.3               | ✓(SCB0_CTS)       |              |                  | ✓(TCPWM)                      | <b>/</b>      |            |            | <b>✓</b> |                      | <b>/</b> |

| 26            | VREF               |                   |              | Ret              | erence Voltage Ir             | nput          |            |            |          |                      |          |

| 27            | P3.2               | ✓(SCB0_RTS)       |              |                  | <b>√</b> (TCPWM)              | <b>/</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 28            | P3.6               | ✓(SCB1_RTS)       |              |                  | <b>√</b> (TCPWM)              | <b>✓</b>      |            |            | <b>/</b> |                      | <b>✓</b> |

| 29            | XRES               |                   |              | External Res     | et Hardware Con               | nection Input |            |            |          |                      |          |

| 30            | P2.4               |                   |              |                  | <b>√</b> (TCPWM)              | <b>/</b>      |            |            | <b>/</b> |                      | <b>✓</b> |

| 31            | P2.5               |                   |              |                  | <b>√</b> (TCPWM)              | <b>✓</b>      |            |            | <b>✓</b> |                      | <b>✓</b> |

| 32            | GND                |                   |              | C                | Ground Connection             | n             |            |            |          |                      |          |

#### Notes

- 2. TCPWM stands for timer, counter, and PWM. If supported, the pad can be configured to any of these peripheral functions.

- TCPWM connections on ports 0, 1, 2, and 3 can be routed through the Digital Signal Interconnect (DSI) to any of the TCPWM blocks and can be either positive

or negative polarity.

- 4. The main board needs to connect both GND connections (Pad 1 and Pad 32) on the module to the common ground of the system.

**Table 5. Analog Peripheral Capabilities**

| Pad Number | Device Port Pin    | SARMUX   | OPAMP                              | LPCOMP       |

|------------|--------------------|----------|------------------------------------|--------------|

| 1          | GND <sup>[5]</sup> |          | Ground Connection                  |              |

| 2          | P1.1               |          | ✓(CTBm1_OA0_INN)                   |              |

| 3          | P1.0               |          | ✓(CTBm1_OA0_INP)                   |              |

| 4          | P1.5               |          | ✓(CTBm1_OA1_INP)                   |              |

| 5          | P0.1               |          |                                    |              |

| 6          | P0.7               |          |                                    |              |

| 7          | VDD                |          | Digital Power Supply Input (1.71 t | o 5.5V)      |

| 8          | P1.4               |          | ✓(CTBm1_OA1_INN)                   |              |

| 9          | P0.4               |          |                                    | ✓(COMP1_INP) |

| 10         | P0.5               |          |                                    | ✓(COMP1_INN) |

| 11         | P0.6               |          |                                    |              |

| 12         | P1.2               |          | ✓(CTBm1_OA0_OUT)                   |              |

| 13         | V <sub>DDR</sub>   |          | Radio Power Supply (1.9V to 5      | 5.5V)        |

| 14         | P2.6               |          | ✓(CTBm0_OA0_INP)                   |              |

| 15         | P1.3               |          | ✓(CTBm1_OA1_OUT)                   |              |

| 16         | P3.0               | <b>√</b> |                                    |              |

| 17         | P2.1               |          | ✓(CTBm0_OA0_INN)                   |              |

| 18         | P2.2               |          | ✓(CTBm0_OA0_OUT)                   |              |

| 19         | P2.3               |          | ✓(CTBm0_OA1_OUT)                   |              |

| 20         | VDDA               |          | Analog Power Supply Input (1.71    | to 5.5V)     |

| 21         | P3.4               | <b>√</b> |                                    |              |

| 22         | P3.1               | <b>√</b> |                                    |              |

| 23         | P3.7               | <b>√</b> |                                    |              |

| 24         | P3.5               | <b>√</b> |                                    |              |

| 25         | P3.3               | <b>√</b> |                                    |              |

| 26         | VREF               |          | Reference Voltage Input (Option    | onal)        |

| 27         | P3.2               | <b>√</b> |                                    |              |

| 28         | P3.6               | <b>√</b> |                                    |              |

| 29         | XRES               |          | External Reset Hardware Connecti   | ion Input    |

| 30         | P2.4               |          | ✓(CTBm0_OA1_INN)                   |              |

| 31         | P2.5               |          | ✓(CTBm0_OA1_INP)                   |              |

| 32         | GND                |          | Ground Connection                  |              |

#### Note

<sup>5.</sup> The main board needs to connect both GND connections (Pad 1 and Pad 32) on the module to the common ground of the system.

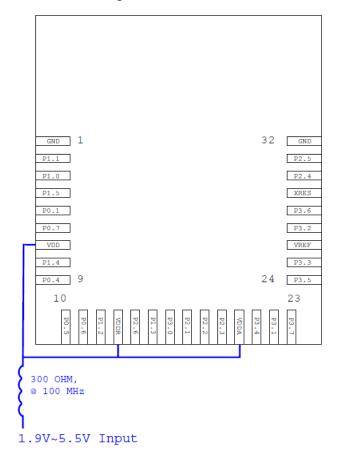

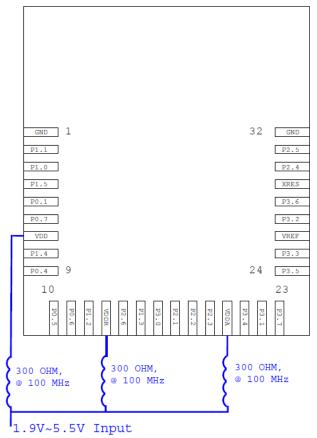

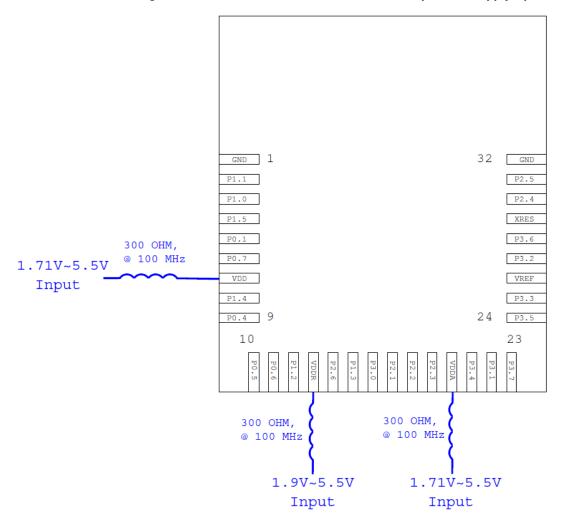

## **Power Supply Connections and Recommended External Components**

#### **Power Connections**

The CYBLE-014008-00 contains three power supply connections, VDD, VDDA, and VDDR. The VDD and VDDA connections supply power for the digital and analog device operation respectively. VDDR supplies power for the device radio.

VDD and VDDA accept a supply range of 1.71 V to 5.5 V. VDDR accepts a supply range of 1.9 V to 5.5 V. These specifications can be found in Table 10. The maximum power supply ripple for both power connections on the module is 100 mV, as shown in Table 8.

The power supply ramp rate of VDD and VDDA must be equal to or greater than that of VDDR when the radio is used.

#### **Connection Options**

Two connection options are available for any application:

- Single supply: Connect VDD, VDDA, and VDDR to the same supply.

- Independent supply: Power VDD, VDDA, and VDDR separately.

#### **External Component Recommendation**

In either connection scenario, it is recommended to place an external ferrite bead between the supply and the module connection. The ferrite bead should be positioned as close as possible to the module pin connection.

Figure 7 details the recommended host schematic options for a single supply scenario. The use of one or three ferrite beads will depend on the specific application and configuration of the CYBLE-014008-00.

Figure 8 details the recommended host schematic for an independent supply scenario.

The recommended ferrite bead value is 330  $\Omega$ , 100 MHz (Murata BLM21PG331SN1D).

Figure 7. Recommended Host Schematic Options for Single Supply Option

Single Ferrite Bead Option (Seen from Bottom)

Three Ferrite Bead Option (Seen from Bottom)

Figure 8. Recommended Host Schematic for Independent Supply Option

**Independent Power Supply Option (Seen from Bottom)**

The CYBLE-014008-00 schematic is shown in Figure 9.

Figure 9. CYBLE-014008-00 Schematic Diagram O P0.1 O P3.0 O P0.4 O P3.1 O P0.5 O P3.2 VDDF O P0.6 O P3.3 0.2pF,0201 O P0.7 O P3.4 L1 1.0nH,0201 L2 1.5nH,0201 O P1.0 O P3.5 O P1.1 O P3.6 O VDD O P1.2 O P3.7 O\_\_\_\_\_\_O VREF O P1.4 NC5 VSSD4 P0.7 P0.3 P1.0 P1.1 VSSR2 VSSR1 VDDR1 O P1.5 O P2.1 O P2.2 P2.3 P2.4 O P2.5 P2.6 O\_\_\_\_XRES P4.0 C16 2.2nF,0201 CMOD C14 0.1uF,0201 C3 0.1uF,0201 P4.1 C17 10nF,0201 VDDR O C7 1.0uF,0201 C4 1.0uF,0201 OVDDA VCCD 0 C10 1.0uF,0201 C12 0.1uF,0201 C9 0.1uF.0201 C6 0.1uF,0201 C8 1.0uF,0201 32 GND P2.5 XRES P3.6 P1.4 P3.3 P0.4 9 24 P3.5 10

Document Number: 002-00023 Rev. \*J

## **Critical Components List**

Table 6 details the critical components used in the CYBLE-014008-00 module.

#### **Table 6. Critical Component List**

| Component | Reference Designator | Description                                              |

|-----------|----------------------|----------------------------------------------------------|

| Silicon   | U1                   | 68-pin WLCSP Programmable System-on-Chip (PSoC) with BLE |

| Crystal   | Y1                   | 24.000 MHz, 10PF                                         |

| Crystal   | Y2                   | 32.768 kHz, 12.5PF                                       |

# **Antenna Design**

Table 7 details antenna used on the CYBLE-014008-00 module. The Cypress module performance improves many of these characteristics. For more information, see Table 9 on page 15.

**Table 7. Trace Antenna Specifications**

| Item            | Description       |

|-----------------|-------------------|

| Frequency Range | 2400 MHz-2500 MHz |

| Peak Gain       | 0.5-dBi typical   |

| Average Gain    | -0.5-dBi typical  |

| Return Loss     | 10-dB minimum     |

## **Electrical Specification**

Table 8 details the absolute maximum electrical characteristics for the Cypress BLE module.

Table 8. CYBLE-014008-00 Absolute Maximum Ratings

| Parameter                   | Description                                                                             | Min  | Тур | Max      | Unit | Details/Conditions                                        |

|-----------------------------|-----------------------------------------------------------------------------------------|------|-----|----------|------|-----------------------------------------------------------|

| V <sub>DDD_ABS</sub>        | $V_{DD}$ , $V_{DDA}$ or $V_{DDR}$ supply relative to $V_{SS}$ ( $V_{SSD} = V_{SSA}$ )   | -0.5 | ı   | 6        | ٧    | Absolute maximum                                          |

| V <sub>CCD_ABS</sub>        | Direct digital core voltage input relative to V <sub>SSD</sub>                          | -0.5 | _   | 1.95     | V    | Absolute maximum                                          |

| V <sub>DDD_RIPPLE</sub>     | Maximum power supply ripple for $V_{DD}$ , $V_{DDA}$ , and $V_{DDR}$ input voltage      | -    | -   | 100      | mV   | 3.0-V supply<br>Ripple frequency of 100 kHz<br>to 750 kHz |

| V <sub>GPIO_ABS</sub>       | GPIO voltage                                                                            | -0.5 | _   | VDD +0.5 | V    | Absolute maximum                                          |

| I <sub>GPIO_ABS</sub>       | Maximum current per GPIO                                                                | -25  | -   | 25       | mA   | Absolute maximum                                          |

| I <sub>GPIO_injection</sub> | GPIO injection current: Maximum for $V_{IH} > V_{DD}$ and minimum for $V_{IL} < V_{SS}$ | -0.5 | _   | 0.5      | mA   | Absolute maximum current injected per pin                 |

| LU                          | Pin current for latch up                                                                | -200 |     | 200      | mA   | -                                                         |

Table 9 details the RF characteristics for the Cypress BLE module.

Table 9. CYBLE-014008-00 RF Performance Characteristics

| Parameter        | Description                   | Min  | Тур  | Max  | Unit | Details/Conditions                 |

|------------------|-------------------------------|------|------|------|------|------------------------------------|

| RF <sub>O</sub>  | RF output power on ANT        | -18  | 0    | 3    | dBm  | Configurable via register settings |

| RX <sub>S</sub>  | RF receive sensitivity on ANT | 1    | -87  | -    | dBm  | Guaranteed by design simulation    |

| F <sub>R</sub>   | Module frequency range        | 2400 | _    | 2480 | MHz  | _                                  |

| G <sub>P</sub>   | Peak gain                     | _    | 0.5  | -    | dBi  | _                                  |

| G <sub>Avg</sub> | Average gain                  | _    | -0.5 | -    | dBi  | _                                  |

| RL               | Return loss                   | _    | -10  | -    | dB   | _                                  |

Table 10 through Table 51 list the module level electrical characteristics for the CYBLE-014008-00. All specifications are valid for −40 °C ≤ TA ≤ 85 °C and TJ ≤ 100 °C, except where noted. Specifications are valid for 1.71 V to 5.5 V, except where noted.

Table 10. CYBLE-014008-00 DC Specifications

| Parameter         | Description                                                                         | Min  | Тур | Max  | Unit | Details/Conditions                    |

|-------------------|-------------------------------------------------------------------------------------|------|-----|------|------|---------------------------------------|

| $V_{DD1}$         | Power supply input voltage (V <sub>DD</sub> = V <sub>DDA</sub> = V <sub>DDR</sub> ) | 1.71 | _   | 5.5  | V    | With regulator enabled                |

| $V_{DD2}$         | Power supply input voltage unregulated $(V_{DD} = V_{DDA} = V_{DDR})$               | 1.71 | 1.8 | 1.89 | V    | Internally unregulated supply         |

| V <sub>DDR1</sub> | Radio supply voltage (radio on)                                                     | 1.9  | _   | 5.5  | V    | _                                     |

| $V_{\rm DDR2}$    | Radio supply voltage (radio off)                                                    | 1.71 | _   | 5.5  | V    | _                                     |

| Active Mode,      | V <sub>DD</sub> = 1.71 V to 5.5 V                                                   |      |     |      |      |                                       |

| I <sub>DD3</sub>  | Execute from flash; CPU at 3 MHz                                                    | _    | 1.7 | _    | mA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

| I <sub>DD4</sub>  | Execute from flash; CPU at 3 MHz                                                    | _    | _   | _    | mA   | T = -40 °C to 85 °C                   |

| I <sub>DD5</sub>  | Execute from flash; CPU at 6 MHz                                                    | _    | 2.5 | _    | mA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

| I <sub>DD6</sub>  | Execute from flash; CPU at 6 MHz                                                    | _    | _   | _    | mA   | T = -40 °C to 85 °C                   |

| I <sub>DD7</sub>  | Execute from flash; CPU at 12 MHz                                                   | _    | 4   | _    | mA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V |

Document Number: 002-00023 Rev. \*J

Table 10. CYBLE-014008-00 DC Specifications (continued)

| Parameter         | Description                                           | Min                                   | Тур      | Max | Unit | Details/Conditions                                                                                                                      |

|-------------------|-------------------------------------------------------|---------------------------------------|----------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>DD8</sub>  | Execute from flash; CPU at 12 MHz                     | -                                     | _        | _   | mA   | T = -40 °C to 85 °C                                                                                                                     |

| I <sub>DD9</sub>  | Execute from flash; CPU at 24 MHz                     | -                                     | 7.1      | -   | mA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                                                                                   |

| I <sub>DD10</sub> | Execute from flash; CPU at 24 MHz                     | _                                     | _        | _   | mA   | T = -40 °C to 85 °C                                                                                                                     |

| I <sub>DD11</sub> | Execute from flash; CPU at 48 MHz                     | -                                     | 13.4     | _   | mA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                                                                                   |

| I <sub>DD12</sub> | Execute from flash; CPU at 48 MHz                     | _                                     | _        | _   | mA   | T = -40 °C to 85 °C                                                                                                                     |

|                   | V <sub>DD</sub> = 1.71 ∨ to 5.5 V                     | l .                                   | <u> </u> |     |      |                                                                                                                                         |

| I <sub>DD13</sub> | IMO on                                                | -                                     | _        | -   | mA   | T = 25 °C, V <sub>DD</sub> = 3.3 V,<br>SYSCLK = 3 MHz                                                                                   |

| Sleep Mode, \     | V <sub>DD</sub> and V <sub>DDR</sub> = 1.9 ∨ to 5.5 V | l l                                   | <u> </u> |     |      |                                                                                                                                         |

| I <sub>DD14</sub> | ECO on                                                | -                                     | _        | _   | mA   | T = 25 °C, V <sub>DD</sub> = 3.3 V,<br>SYSCLK = 3 MHz                                                                                   |

| Deep-Sleep M      | lode, V <sub>DD</sub> = 1.71 ∨ to 3.6 V               | <b>'</b>                              |          |     |      | l                                                                                                                                       |

| I <sub>DD15</sub> | WDT with WCO on                                       | _                                     | 1.3      | -   | μА   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                                                                                   |

| I <sub>DD16</sub> | WDT with WCO on                                       | _                                     | _        | _   | μΑ   | T = -40 °C to 85 °C                                                                                                                     |

| I <sub>DD17</sub> | WDT with WCO on                                       | _                                     | _        | _   | μА   | T = 25 °C,<br>V <sub>DD</sub> = 5 V                                                                                                     |

| I <sub>DD18</sub> | WDT with WCO on                                       | _                                     | _        | _   | μΑ   | T = -40 °C to 85 °C                                                                                                                     |

| Deep-Sleep M      | lode, V <sub>DD</sub> = 1.71 ∨ to 1.89 V (Regulator B | ypassed)                              |          |     |      | l                                                                                                                                       |

| I <sub>DD19</sub> | WDT with WCO on                                       | _                                     | _        | -   | μΑ   | T = 25 °C                                                                                                                               |

| I <sub>DD20</sub> | WDT with WCO on                                       | _                                     | _        | _   | μΑ   | T = -40 °C to 85 °C                                                                                                                     |

| Hibernate Mo      | de, V <sub>DD</sub> = 1.71 ∨ to 3.6 V                 | · · · · · · · · · · · · · · · · · · · |          |     |      |                                                                                                                                         |

| I <sub>DD27</sub> | GPIO and reset active                                 | _                                     | 150      | -   | nA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                                                                                   |

| I <sub>DD28</sub> | GPIO and reset active                                 | _                                     | _        | _   | nA   | T = -40 °C to 85 °C                                                                                                                     |

| Hibernate Mo      | de, V <sub>DD</sub> = 3.6 ∨ to 5.5 V                  | <b>'</b>                              |          |     |      | l                                                                                                                                       |

| I <sub>DD29</sub> | GPIO and reset active                                 | -                                     | _        | _   | nA   | T = 25 °C,<br>V <sub>DD</sub> = 5 V                                                                                                     |

| I <sub>DD30</sub> | GPIO and reset active                                 | _                                     | _        | _   | nA   | T = -40 °C to 85 °C                                                                                                                     |

|                   | <sub>DD</sub> = 1.71 ∨ to 3.6 V                       | l l                                   | <u> </u> |     |      |                                                                                                                                         |

| I <sub>DD33</sub> | Stop-mode current (V <sub>DD</sub> )                  | -                                     | 20       | -   | nA   | T = 25 °C,<br>V <sub>DD</sub> = 3.3 V                                                                                                   |

| I <sub>DD34</sub> | Stop-mode current (V <sub>DDR</sub> )                 | -                                     | 40       |     | nA   | T = 25 °C,<br>V <sub>DDR</sub> = 3.3 V                                                                                                  |

| I <sub>DD35</sub> | Stop-mode current (V <sub>DD</sub> )                  | _                                     | _        | _   | nA   | T = -40 °C to 85 °C                                                                                                                     |

| I <sub>DD36</sub> | Stop-mode current (V <sub>DDR</sub> )                 | -                                     | -        | _   | nA   | $T = -40 ^{\circ}\text{C} \text{ to } 85 ^{\circ}\text{C},$<br>$V_{\text{DDR}} = 1.9 ^{\circ}\text{V} \text{ to } 3.6 ^{\circ}\text{V}$ |

| Stop Mode, V      | DD = 3.6 ∨ to 5.5 V                                   | L                                     | 1        |     | 1    | ı                                                                                                                                       |

| I <sub>DD37</sub> | Stop-mode current (V <sub>DD</sub> )                  | _                                     | _        | _   | nA   | T = 25 °C,<br>V <sub>DD</sub> = 5 V                                                                                                     |

| I <sub>DD38</sub> | Stop-mode current (V <sub>DDR</sub> )                 | _                                     | _        | _   | nA   | T = 25 °C,<br>V <sub>DDR</sub> = 5 V                                                                                                    |

| I <sub>DD39</sub> | Stop-mode current (V <sub>DD</sub> )                  | _                                     | _        | _   | nA   | T = -40 °C to 85 °C                                                                                                                     |

| I <sub>DD40</sub> | Stop-mode current (V <sub>DDR</sub> )                 | _                                     | _        | _   | nA   | T = -40 °C to 85 °C                                                                                                                     |

Table 11. AC Specifications

| Parameter              | Description                 | Min | Тур | Max | Unit | Details/Conditions                         |

|------------------------|-----------------------------|-----|-----|-----|------|--------------------------------------------|

| F <sub>CPU</sub>       | CPU frequency               | DC  | _   | 48  | MHz  | 1.71 V ≤ V <sub>DD</sub> ≤ 5.5 V           |

| T <sub>SLEEP</sub>     | Wakeup from Sleep mode      | _   | 0   | _   | μs   | Guaranteed by characterization             |

| T <sub>DEEPSLEEP</sub> | Wakeup from Deep-Sleep mode | _   | _   | 25  |      | 24-MHz IMO. Guaranteed by characterization |

| T <sub>HIBERNATE</sub> | Wakeup from Hibernate mode  | _   | _   | 800 | μs   | Guaranteed by characterization             |

| T <sub>STOP</sub>      | Wakeup from Stop mode       | _   | _   | 2   | ms   | XRES wakeup                                |

## **GPIO**

Table 12. GPIO DC Specifications

| Parameter                      | Description                                         | Min                   | Тур | Max                 | Unit | Details/Conditions                               |

|--------------------------------|-----------------------------------------------------|-----------------------|-----|---------------------|------|--------------------------------------------------|

|                                | Input voltage HIGH threshold                        | $0.7 \times V_{DD}$   | -   | _                   | V    | CMOS input                                       |

| V <sub>IH</sub> <sup>[6]</sup> | LVTTL input, V <sub>DD</sub> < 2.7 V                | $0.7 \times V_{DD}$   | _   | _                   | V    | _                                                |

|                                | LVTTL input, $V_{DD} \ge 2.7 \text{ V}$             | 2.0                   | -   | _                   | V    | -                                                |

|                                | Input voltage LOW threshold                         | _                     | _   | $0.3 \times V_{DD}$ | V    | CMOS input                                       |

| $V_{IL}$                       | LVTTL input, V <sub>DD</sub> < 2.7 V                | _                     | _   | $0.3 \times V_{DD}$ | V    | _                                                |

|                                | LVTTL input, $V_{DD} \ge 2.7 \text{ V}$             | _                     | -   | 0.8                 | V    | -                                                |

| V <sub>OH</sub>                | Output voltage HIGH level                           | V <sub>DD</sub> – 0.6 | _   | _                   | V    | $I_{OH} = 4 \text{ mA at } 3.3\text{-V V}_{DD}$  |

| VOH                            | Output voltage HIGH level                           | V <sub>DD</sub> – 0.5 | _   | _                   | V    | $I_{OH} = 1 \text{ mA at } 1.8 \text{-V V}_{DD}$ |

|                                | Output voltage LOW level                            | _                     | _   | 0.6                 | V    | $I_{OL}$ = 8 mA at 3.3-V $V_{DD}$                |

| $V_{OL}$                       | Output voltage LOW level                            | _                     | _   | 0.6                 | V    | $I_{OL} = 4 \text{ mA at } 1.8 \text{-V V}_{DD}$ |

|                                | Output voltage LOW level                            | _                     | _   | 0.4                 | V    | $I_{OL} = 3 \text{ mA at } 3.3\text{-V V}_{DD}$  |

| R <sub>PULLUP</sub>            | Pull-up resistor                                    | 3.5                   | 5.6 | 8.5                 | kΩ   | _                                                |

| R <sub>PULLDOWN</sub>          | Pull-down resistor                                  | 3.5                   | 5.6 | 8.5                 | kΩ   | _                                                |

| I <sub>IL</sub>                | Input leakage current (absolute value)              | _                     | _   | 2                   | nA   | 25 °C, V <sub>DD</sub> = 3.3 V                   |

| I <sub>IL_CTBM</sub>           | Input leakage on CTBm input pins                    | _                     | -   | 4                   | nA   | -                                                |

| C <sub>IN</sub>                | Input capacitance                                   | _                     | _   | 7                   | pF   | _                                                |

| V <sub>HYSTTL</sub>            | Input hysteresis LVTTL                              | 25                    | 40  | _                   | mV   | V <sub>DD</sub> > 2.7 V                          |

| V <sub>HYSCMOS</sub>           | Input hysteresis CMOS                               | $0.05 \times V_{DD}$  | -   | _                   | 1    | _                                                |

| I <sub>DIODE</sub>             | Current through protection diode to $V_{DD}/V_{SS}$ | _                     | _   | 100                 | μΑ   | -                                                |

| I <sub>TOT_GPIO</sub>          | Maximum total source or sink chip current           | _                     | _   | 200                 | mA   | -                                                |

Document Number: 002-00023 Rev. \*J

Note 6.  $V_{IH}$  must not exceed  $V_{DD}$  + 0.2 V.

Table 13. GPIO AC Specifications

| Parameter            | Description                                                                        | Min | Тур | Max  | Unit | Details/Conditions                                  |

|----------------------|------------------------------------------------------------------------------------|-----|-----|------|------|-----------------------------------------------------|

| T <sub>RISEF</sub>   | Rise time in Fast-Strong mode                                                      | 2   | _   | 12   | ns   | $3.3\text{-V V}_{DDD}$ , $C_{LOAD} = 25 \text{ pF}$ |

| T <sub>FALLF</sub>   | Fall time in Fast-Strong mode                                                      | 2   | -   | 12   | ns   | $3.3-V V_{DDD}, C_{LOAD} = 25 pF$                   |

| T <sub>RISES</sub>   | Rise time in Slow-Strong mode                                                      | 10  | -   | 60   | ns   | $3.3-V V_{DDD}, C_{LOAD} = 25 pF$                   |

| T <sub>FALLS</sub>   | Fall time in Slow-Strong mode                                                      | 10  | _   | 60   | ns   | $3.3\text{-V V}_{DDD}$ , $C_{LOAD} = 25 \text{ pF}$ |

| F <sub>GPIOUT1</sub> | GPIO Fout; 3.3 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V Fast-Strong mode              | _   | _   | 33   | MHz  | 90/10%, 25 pF load, 60/40 duty cycle                |

| F <sub>GPIOUT2</sub> | GPIO Fout; 1.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.3 V Fast-Strong mode              | _   | _   | 16.7 | MHz  | 90/10%, 25 pF load, 60/40 duty cycle                |

| F <sub>GPIOUT3</sub> | GPIO Fout; $3.3 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V}$<br>Slow-Strong mode | _   | _   | 7    | MHz  | 90/10%, 25 pF load, 60/40 duty cycle                |

| F <sub>GPIOUT4</sub> | GPIO Fout; 1.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.3 V Slow-Strong mode              | _   | _   | 3.5  | MHz  | 90/10%, 25 pF load, 60/40 duty cycle                |

| F <sub>GPIOIN</sub>  | GPIO input operating frequency 1.71 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V          | _   | _   | 48   | MHz  | 90/10% V <sub>IO</sub>                              |

### **XRES**

## Table 14. XRES DC Specifications

| Parameter            | Description                                         | Min                  | Тур | Max                  | Unit | Details/Conditions |

|----------------------|-----------------------------------------------------|----------------------|-----|----------------------|------|--------------------|

| V <sub>IH</sub>      | Input voltage HIGH threshold                        | $0.7 \times V_{DDD}$ | -   | _                    | V    | CMOS input         |

| V <sub>IL</sub>      | Input voltage LOW threshold                         | _                    | -   | $0.3 \times V_{DDD}$ | V    | CMOS input         |

| R <sub>PULLUP</sub>  | Pull-up resistor                                    | 3.5                  | 5.6 | 8.5                  | kΩ   | _                  |

| C <sub>IN</sub>      | Input capacitance                                   | _                    | 3   | _                    | pF   | _                  |

| V <sub>HYSXRES</sub> | Input voltage hysteresis                            | _                    | 100 | _                    | mV   | -                  |

| I <sub>DIODE</sub>   | Current through protection diode to $V_{DD}/V_{SS}$ | _                    | _   | 100                  | μΑ   | -                  |

## Table 15. XRES AC Specifications

| Parameter               | Description       | Min | Тур | Max | Unit | Details/Conditions |

|-------------------------|-------------------|-----|-----|-----|------|--------------------|

| T <sub>RESETWIDTH</sub> | Reset pulse width | 1   | _   | 1   | μs   | -                  |

## **Analog Peripherals**

Opamp

Table 16. Opamp Specifications

| Parameter                                                               | Description                              | Min | Тур  | Max  | Unit | Details/Conditions |  |  |

|-------------------------------------------------------------------------|------------------------------------------|-----|------|------|------|--------------------|--|--|

| I <sub>DD</sub> (Opamp Block Current. V <sub>DD</sub> = 1.8 V. No Load) |                                          |     |      |      |      |                    |  |  |

| I <sub>DD_HI</sub>                                                      | Power = high                             | _   | 1000 | 1300 | μΑ   | -                  |  |  |

| I <sub>DD_MED</sub>                                                     | Power = medium                           | _   | 500  | _    | μΑ   | -                  |  |  |

| I <sub>DD_LOW</sub>                                                     | Power = low                              | _   | 250  | 350  | μΑ   | -                  |  |  |

| GBW (Load =                                                             | 20 pF, 0.1 mA. V <sub>DDA</sub> = 2.7 V) |     |      |      |      |                    |  |  |

| GBW_HI                                                                  | Power = high                             | 6   | -    | _    | MHz  | -                  |  |  |

| GBW_MED                                                                 | Power = medium                           | 4   | _    | -    | MHz  | -                  |  |  |

| GBW_LO                                                                  | Power = low                              | _   | 1    | 1    | MHz  | 1                  |  |  |

Table 16. Opamp Specifications (continued)

| Parameter                             | Description                                             | Min                    | Тур      | Max                      | Unit      | Details/Conditions                        |

|---------------------------------------|---------------------------------------------------------|------------------------|----------|--------------------------|-----------|-------------------------------------------|

| I <sub>OUT_MAX</sub> (V <sub>DE</sub> | <sub>DA</sub> ≥ 2.7 V, 500 mV from Rail)                |                        |          |                          |           |                                           |

| I <sub>OUT_MAX_HI</sub>               | Power = high                                            | 10                     | _        | _                        | mA        | _                                         |

| I <sub>OUT_MAX_MID</sub>              | Power = medium                                          | 10                     | _        | -                        | mA        | _                                         |

| I <sub>OUT_MAX_LO</sub>               | Power = low                                             | _                      | 5        | _                        | mA        | _                                         |

|                                       | I.71 V, 500 mV from Rail)                               |                        |          |                          |           |                                           |

| I <sub>OUT_MAX_HI</sub>               | Power = high                                            | 4                      | _        | _                        | mA        | -                                         |

| I <sub>OUT_MAX_MID</sub>              | Power = medium                                          | 4                      | _        | _                        | mA        | -                                         |

| I <sub>OUT_MAX_LO</sub>               | Power = low                                             | _                      | 2        | _                        | mA        | _                                         |

| V <sub>IN</sub>                       | Charge pump on, V <sub>DDA</sub> ≥ 2.7 V                | -0.05                  | _        | $V_{DDA} - 0.2$          | V         | -                                         |

| V <sub>CM</sub>                       | Charge pump on, V <sub>DDA</sub> ≥ 2.7 V                | -0.05                  | _        | $V_{DDA} - 0.2$          | V         | -                                         |

| V <sub>OUT</sub> (V <sub>DDA</sub> ≥  | 2.7 V)                                                  |                        | ı        |                          |           |                                           |

| V <sub>OUT 1</sub>                    | Power = high, I <sub>LOAD</sub> = 10 mA                 | 0.5                    | _        | $V_{DDA} - 0.5$          | V         | -                                         |

| <br>V <sub>OUT_2</sub>                | Power = high, I <sub>LOAD</sub> = 1 mA                  | 0.2                    | _        | V <sub>DDA</sub> – 0.2   | V         | _                                         |

| V <sub>OUT_3</sub>                    | Power = medium, I <sub>LOAD</sub> = 1 mA                | 0.2                    | _        | V <sub>DDA</sub> – 0.2   | V         | _                                         |

| <br>V <sub>OUT_4</sub>                | Power = low, I <sub>LOAD</sub> =0.1 mA                  | 0.2                    | _        | V <sub>DDA</sub> - 0.2   | V         | _                                         |

| V <sub>OS_TR</sub>                    | Offset voltage, trimmed                                 | 1                      | ±0.5     | 1                        | mV        | High mode                                 |

| V <sub>OS_TR</sub>                    | Offset voltage, trimmed                                 | _                      | ±1       | _                        | mV        | Medium mode                               |

| V <sub>OS_TR</sub>                    | Offset voltage, trimmed                                 | _                      | ±2       | _                        | mV        | Low mode                                  |

| Vos_dr_tr                             | Offset voltage drift, trimmed                           | -10                    | ±3       | 10                       | μV/°C     | High mode                                 |

| V <sub>OS_DR_TR</sub>                 | Offset voltage drift, trimmed                           | _                      | ±10      | _                        | μV/°C     | Medium mode                               |

| V <sub>OS_DR_TR</sub>                 | Offset voltage drift, trimmed                           | _                      | ±10      | _                        | μV/°C     | Low mode                                  |

| CMRR                                  | DC                                                      | 65                     | 70       | _                        | dB        | V <sub>DDD</sub> = 3.6 V, High-power mode |

| PSRR                                  | At 1 kHz, 100-mV ripple                                 | 70                     | 85       | _                        | dB        | V <sub>DDD</sub> = 3.6 V                  |

| Noise                                 | · ·                                                     |                        | l        |                          |           |                                           |

| $V_{N1}$                              | Input referred, 1 Hz-1 GHz, power = high                | _                      | 94       | _                        | μVrms     | _                                         |

| $V_{N2}$                              | Input referred, 1 kHz, power = high                     | _                      | 72       | _                        | nV/rtHz   | _                                         |

| V <sub>N3</sub>                       | Input referred, 10 kHz, power = high                    | _                      | 28       | _                        | nV/rtHz   | _                                         |

| $V_{N4}$                              | Input referred, 100 kHz, power = high                   | _                      | 15       | _                        | nV/rtHz   | _                                         |

| C <sub>LOAD</sub>                     | Stable up to maximum load. Performance specs at 50 pF.  | _                      | _        | 125                      | pF        | _                                         |

| Slew_rate                             | Cload = 50 pF, Power = High,<br>V <sub>DDA</sub> ≥ 2.7V | 6                      | -        | -                        | V/µs      | _                                         |

| T_op_wake                             | From disable to enable, no external RC dominating       | _                      | 300      | -                        | μs        | _                                         |

| Comp_mode                             | (Comparator Mode; 50-mV Drive, T <sub>RISE</sub> :      | = T <sub>FALL</sub> (A | Approx   | .)                       |           |                                           |

| Γ <sub>PD1</sub>                      | Response time; power = high                             | _                      | 150      | _                        | ns        | _                                         |

| Γ <sub>PD2</sub>                      | Response time; power = medium                           | _                      | 400      | -                        | ns        | _                                         |

| Γ <sub>PD3</sub>                      | Response time; power = low                              | _                      | 2000     | -                        | ns        | _                                         |

| Vhyst_op                              | Hysteresis                                              | _                      | 10       | -                        | mV        | _                                         |

| Deen-Sleen M                          | lode (Deep-Sleep mode operation is onl                  | y guaran               | teed fo  | r V <sub>DDA</sub> > 2.5 | 5 V)      |                                           |

| Deep Gleep IV                         |                                                         |                        |          |                          |           |                                           |

|                                       | Gain bandwidth product                                  | _                      | 50       | _                        | kHz       | _                                         |

| GBW_DS<br>IDD_DS                      | Gain bandwidth product Current                          |                        | 50<br>15 | _                        | kHz<br>μA | <u> </u>                                  |

### Table 16. Opamp Specifications (continued)

| Parameter | Description          | Min | Тур | Max                  | Unit  | Details/Conditions |

|-----------|----------------------|-----|-----|----------------------|-------|--------------------|

| Vos_dr_DS | Offset voltage drift | _   | 20  | _                    | μV/°C | -                  |

| Vout_DS   | Output voltage       | 0.2 | -   | V <sub>DD</sub> -0.2 | V     | _                  |

| Vcm_DS    | Common mode voltage  | 0.2 | _   | V <sub>DD</sub> -1.8 | V     | _                  |

## Table 17. Comparator DC Specifications

| Parameter            | Description                                       | Min | Тур | Max                        | Unit | Details/Conditions |

|----------------------|---------------------------------------------------|-----|-----|----------------------------|------|--------------------|

| V <sub>OFFSET1</sub> | Input offset voltage, Factory trim                | _   | _   | ±10                        | mV   | _                  |

| V <sub>OFFSET2</sub> | Input offset voltage, Custom trim                 | _   | _   | ±6                         | mV   | _                  |

| V <sub>OFFSET3</sub> | Input offset voltage, ultra-low-power mode        | _   | ±12 | -                          | mV   | -                  |

| V <sub>HYST</sub>    | Hysteresis when enabled                           | _   | 10  | 35                         | mV   | _                  |

| V <sub>ICM1</sub>    | Input common mode voltage in normal mode          | 0   | _   | V <sub>DDD</sub> – 0.1     | V    | Modes 1 and 2      |

| V <sub>ICM2</sub>    | Input common mode voltage in low-power mode       | 0   | _   | V <sub>DDD</sub>           | ٧    | -                  |

| V <sub>ICM3</sub>    | Input common mode voltage in ultra low-power mode | 0   | _   | V <sub>DDD</sub> –<br>1.15 | ٧    | -                  |

| CMRR                 | Common mode rejection ratio                       | 50  | _   | _                          | dB   | $V_{DDD} \ge 2.7V$ |

| CMRR                 | Common mode rejection ratio                       | 42  | _   | _                          | dB   | $V_{DDD} \le 2.7V$ |

| I <sub>CMP1</sub>    | Block current, normal mode                        | _   | _   | 400                        | μΑ   | -                  |

| I <sub>CMP2</sub>    | Block current, low-power mode                     | _   | _   | 100                        | μΑ   | _                  |

| I <sub>CMP3</sub>    | Block current in ultra-low-power mode             | _   | 6   | _                          | μΑ   | _                  |

| Z <sub>CMP</sub>     | DC input impedance of comparator                  | 35  | _   | _                          | MΩ   | _                  |

## Table 18. Comparator AC Specifications

| Parameter          | Description                                          | Min | Тур | Max | Unit | Details/Conditions |

|--------------------|------------------------------------------------------|-----|-----|-----|------|--------------------|

| T <sub>RESP1</sub> | Response time, normal mode, 50-mV overdrive          | _   | 38  | -   | ns   | 50-mV overdrive    |

| T <sub>RESP2</sub> | Response time, low-power mode, 50-mV overdrive       | _   | 70  | _   | ns   | 50-mV overdrive    |

| T <sub>RESP3</sub> | Response time, ultra-low-power mode, 50-mV overdrive | _   | 2.3 | _   | μs   | 200-mV overdrive   |

## Temperature Sensor

## Table 19. Temperature Sensor Specifications

| Parameter            | Description                 | Min        | Тур | Max | Unit | Details/Conditions |

|----------------------|-----------------------------|------------|-----|-----|------|--------------------|

| T <sub>SENSACC</sub> | Temperature-sensor accuracy | <b>-</b> 5 | ±1  | 5   | °C   | -40 to +85 °C      |

#### SAR ADC

## Table 20. SAR ADC DC Specifications

| Parameter | Description                           | Min      | Тур | Max                             | Unit | Details/Conditions                    |

|-----------|---------------------------------------|----------|-----|---------------------------------|------|---------------------------------------|

| A_RES     | Resolution                            | _        | _   | 12                              | bits | _                                     |

| A_CHNIS_S | Number of channels - single-ended     | _        | _   | 8                               | _    | 8 full-speed                          |

| A-CHNKS_D | Number of channels - differential - 4 |          | -   | Diff inputs use neighboring I/O |      |                                       |

| A-MONO    | Monotonicity                          | _        | _   | _                               | _    | Yes                                   |

| A_GAINERR | Gain error                            | _        | _   | ±0.1                            | %    | With external reference               |

| A_OFFSET  | Input offset voltage                  | _        | _   | 2                               | mV   | Measured with 1-V<br>V <sub>REF</sub> |

| A_ISAR    | Current consumption                   | _        | _   | 1                               | mA   | _                                     |