Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Single-Chip Bluetooth® Transceiver and Baseband Processor

## **General Description**

The Cypress CYW20710 is a monolithic, single-chip, Bluetooth 4.0 compliant, stand-alone baseband processor with an integrated 2.4 GHz transceiver. Manufactured using the industry's most advanced 65 nm CMOS low-power process, the CYW20710 employs the highest level of integration, eliminating all critical external components, and thereby minimizing the device's footprint and costs associated with the implementation of Bluetooth solutions.

The CYW20710 is the optimal solution for voice and data applications that require a Bluetooth SIG standard Host Controller Interface (HCI) via UART H4 or H5 and PCM audio interface support. The CYW20710 radio transceiver's enhanced radio performance meets the most stringent industrial temperature application requirements for compact integration into mobile handset and portable devices. The CYW20710 is fully compatible with all standard TCXO frequencies and provides full radio compatibility, enabling it to operate simultaneously with GPS and cellular radios.

## **Cypress Part Numbering Scheme**

Cypress is converting the acquired IoT part numbers from Cypress to the Cypress part numbering scheme. Due to this conversion, there is no change in form, fit, or function as a result of offering the device with Cypress part number marking. The table provides Cypress ordering part number that matches an existing IoT part number.

Table 1. Mapping Table for Part Number between Broadcom and Cypress

| Broadcom Part Number | Cypress Part Number |

|----------------------|---------------------|

| BCM20710             | CYW20710            |

| BCM20710A1KUFBXG     | CYW20710A1KUFBXG    |

| BCM20710A1KUBXG      | CYW20710A1KUBXG     |

#### **Features**

- Bluetooth 4.0 + EDR compliant

- Class 1 capable with built-in PA

- Programmable output power control meets Class 1, Class 2, or Class 3 requirements

- Use supply voltages up to 5.5V

- Supports Cypress SmartAudio<sup>TM</sup>, wide-band speech, SBC codec, and packet loss concealment.

- Fractional-N synthesizer supports frequency references from 12 MHz to 52 MHz

- Automatic frequency detection for standard crystal and TCXO values when an external 32.768 kHz reference clock is provided.

- Ultra-low power consumption

- Supports serial flash interfaces

- Available in 42-bump WLBGA and 50-ball FPBGA packages.

- ARM7TDMI-S™—based microprocessor with integrated ROM and RAM

- Supports mobile without external memory

## **Applications**

- Mobile handsets and smart phones

- Personal digital assistants

Automotive telematic systems

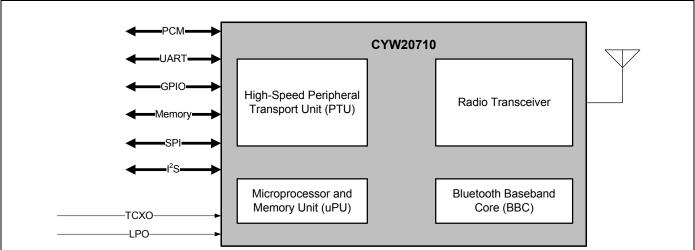

Figure 1. Functional Block Diagram

## **Contents**

| 1. | Ove  | erview                                                                                                           | 4           |

|----|------|------------------------------------------------------------------------------------------------------------------|-------------|

|    | 1.1  | Major Features                                                                                                   | 4           |

|    | 1.2  | Block Diagram                                                                                                    | 6           |

|    | 1.3  | Mobile Phone Usage Model                                                                                         | 7           |

| 2. | Inte | grated Radio Transceiver                                                                                         | 8           |

|    | 2.1  | Transmitter Path                                                                                                 |             |

|    |      | <ul><li>2.1.1 Digital Modulator</li><li>2.1.2 Power Amplifier</li></ul>                                          |             |

|    | 2.2  | Receiver Path                                                                                                    |             |

|    |      | <ul><li>2.2.1 Digital Demodulator and Bit Synchronize</li><li>2.2.2 Receiver Signal Strength Indicator</li></ul> | er 8        |

|    | 2.3  | Local Oscillator Generation                                                                                      | 8           |

|    | 2.4  | Calibration                                                                                                      | 9           |

|    | 2.5  | Internal LDO Regulator                                                                                           | 9           |

| 3. | Blu  | etooth Baseband Core                                                                                             | 10          |

|    | 3.1  | Transmit and Receive Functions                                                                                   | . 10        |

|    | 3.2  | Bluetooth 4.0 + EDR Features                                                                                     | . 10        |

|    | 3.3  | Frequency Hopping Generator                                                                                      | . 11        |

|    | 3.4  | Link Control Layer                                                                                               | . 11        |

|    | 3.5  | Test Mode Support                                                                                                | . 11        |

|    | 3.6  | Power Management Unit                                                                                            |             |

|    |      | 3.6.1 RF Power Management 3.6.2 Host Controller Power Management                                                 |             |

|    |      | 3.6.3 Bluetooth Baseband Core Power                                                                              |             |

|    |      | Management                                                                                                       |             |

|    | 3.7  | Adaptive Frequency Hopping                                                                                       |             |

|    | 3.8  | Collaborative Coexistence                                                                                        |             |

|    | 3.9  | Serial Enhanced Coexistence Interface                                                                            | . 14<br>. 1 |

|    |      | 3.9.2 SECI I/O                                                                                                   |             |

| 4. | Mic  | roprocessor Unit                                                                                                 | 15          |

|    | 4.1  | NVRAM Configuration Data and Storage4.1.1 Serial Interface                                                       |             |

|    | 4.2  | EEPROM                                                                                                           | . 15        |

|    | 4.3  | External Reset                                                                                                   | . 15        |

|    | 4.4  | One-Time Programmable Memory                                                                                     |             |

|    |      | 4.4.1 Contents                                                                                                   |             |

|    |      | 4.4.2 Programming                                                                                                | . 16        |

| •-             | Peri                                                 | pheral Transport Unit                                                                                                                                                                                                                                 | 17                                                              |

|----------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

|                | 5.1                                                  | PCM Interface                                                                                                                                                                                                                                         |                                                                 |

|                |                                                      | 5.1.1 System Diagram                                                                                                                                                                                                                                  | .17                                                             |

|                |                                                      | 5.1.2 Slot Mapping                                                                                                                                                                                                                                    |                                                                 |

|                |                                                      | 5.1.3 Wideband Speech                                                                                                                                                                                                                                 |                                                                 |

|                |                                                      | 5.1.4 Frame Synchronization                                                                                                                                                                                                                           |                                                                 |

|                |                                                      | 5.1.5 Data Formatting                                                                                                                                                                                                                                 |                                                                 |

|                | 5.2                                                  | HCI Transport Detection Configuration                                                                                                                                                                                                                 |                                                                 |

|                | 5.3                                                  | UART Interface                                                                                                                                                                                                                                        | .19                                                             |

|                |                                                      | 5.3.1 HCI 3-Wire Transport (UART H5)                                                                                                                                                                                                                  | .19                                                             |

|                | 5.4                                                  | SPI                                                                                                                                                                                                                                                   | .20                                                             |

| 6.             | Fred                                                 | quency References                                                                                                                                                                                                                                     | 21                                                              |

|                | 6.1                                                  | Crystal Interface and Clock Generation                                                                                                                                                                                                                | .21                                                             |

|                | 6.2                                                  | Crystal Oscillator                                                                                                                                                                                                                                    | .22                                                             |

|                | 6.3                                                  | External Frequency Reference                                                                                                                                                                                                                          | .22                                                             |

|                |                                                      | 6.3.1 TCXO Clock Request Support                                                                                                                                                                                                                      | .23                                                             |

|                | 6.4                                                  | Frequency Selection                                                                                                                                                                                                                                   | .24                                                             |

|                | 6.5                                                  | Frequency Trimming                                                                                                                                                                                                                                    | .24                                                             |

|                | 6.6                                                  | LPO Clock Interface                                                                                                                                                                                                                                   | .25                                                             |

| 7.             | Pin-                                                 | Out and Signal Descriptions                                                                                                                                                                                                                           | 26                                                              |

|                | 7.1                                                  | Pin Descriptions                                                                                                                                                                                                                                      | .26                                                             |

| 8.             | Ball                                                 | Grid Arrays                                                                                                                                                                                                                                           | 20                                                              |

|                | -                                                    | Ond Arrays                                                                                                                                                                                                                                            | 20                                                              |

| 9.             |                                                      | ctrical Characteristics                                                                                                                                                                                                                               |                                                                 |

| 9.             |                                                      | ctrical Characteristics                                                                                                                                                                                                                               | 30                                                              |

| 9.             | <b>Elec</b><br>9.1                                   | RF Specifications                                                                                                                                                                                                                                     | <b>30</b><br>.35                                                |

| 9.             | Elec                                                 | RF Specifications                                                                                                                                                                                                                                     | <b>30</b><br>.35<br>.38                                         |

| 9.             | <b>Elec</b><br>9.1                                   | RF Specifications Timing and AC Characteristics                                                                                                                                                                                                       | 30<br>.35<br>.38<br>.38                                         |

| 9.             | <b>Elec</b><br>9.1                                   | RF Specifications                                                                                                                                                                                                                                     | 30<br>.35<br>.38<br>.38<br>.39<br>.40                           |

| 9.             | <b>Elec</b><br>9.1                                   | RF Specifications                                                                                                                                                                                                                                     | 30<br>.35<br>.38<br>.38<br>.39<br>.40                           |

|                | 9.1<br>9.2                                           | RF Specifications                                                                                                                                                                                                                                     | 30<br>.35<br>.38<br>.38<br>.39<br>.40                           |

|                | 9.1<br>9.2                                           | RF Specifications                                                                                                                                                                                                                                     | 30<br>.35<br>.38<br>.39<br>.40<br>.44                           |

| 10             | 9.1<br>9.2<br>. <b>Mec</b>                           | RF Specifications Timing and AC Characteristics 9.2.1 Startup Timing 9.2.2 UART Timing 9.2.3 PCM Interface Timing 9.2.4 BSC Interface Timing                                                                                                          | 30<br>.35<br>.38<br>.39<br>.40<br>.44<br>45                     |

| 10             | 9.1<br>9.2<br>. <b>Med</b><br>10.1                   | RF Specifications Timing and AC Characteristics 9.2.1 Startup Timing 9.2.2 UART Timing 9.2.3 PCM Interface Timing 9.2.4 BSC Interface Timing Chanical Information Tape, Reel, and Packing Specification                                               | 30<br>.35<br>.38<br>.39<br>.40<br>.44<br>45<br>.47              |

| 10             | 9.1<br>9.2<br>. Med<br>10.1<br>. Ord                 | RF Specifications Timing and AC Characteristics 9.2.1 Startup Timing 9.2.2 UART Timing 9.2.3 PCM Interface Timing 9.2.4 BSC Interface Timing Tape, Reel, and Packing Specification ering Information                                                  | 30<br>.35<br>.38<br>.39<br>.40<br>.44<br>45<br>.47              |

| 10             | 9.1<br>9.2<br>. Med<br>10.1<br>. Ord<br>. Add        | RF Specifications Timing and AC Characteristics 9.2.1 Startup Timing 9.2.2 UART Timing 9.2.3 PCM Interface Timing 9.2.4 BSC Interface Timing Chanical Information Tape, Reel, and Packing Specification ering Information                             | 30<br>.35<br>.38<br>.39<br>.40<br>.44<br>45<br>.47<br>48        |

| 10<br>11<br>12 | 9.1<br>9.2<br>. Med<br>10.1<br>. Ord<br>12.1<br>12.2 | RF Specifications Timing and AC Characteristics 9.2.1 Startup Timing 9.2.2 UART Timing 9.2.3 PCM Interface Timing 9.2.4 BSC Interface Timing Chanical Information Tape, Reel, and Packing Specification ering Information  Acronyms and Abbreviations | 30<br>.35<br>.38<br>.39<br>.40<br>.44<br>45<br>.47<br>48<br>.48 |

## 1. Overview

The Cypress CYW20710 complies with the Bluetooth Core Specification, version 4.0 and is designed for use with a standard Host Controller Interface (HCI) UART. The combination of the Bluetooth Baseband Core (BBC), a Peripheral Transport Unit (PTU), and an ARM<sup>®</sup>-based microprocessor with on-chip ROM provides a complete lower layer Bluetooth protocol stack, including the Link Controller (LC), Link Manager (LM), and HCI.

## 1.1 Major Features

Major features of the CYW20710 include:

- Support for Bluetooth 4.0 + EDR, including the following options:

- A whitelist size of 25.

- □ Enhanced Power Control

- HCI Read Encryption Key Size command

- Full support for Bluetooth 2.1 + EDR additional features:

- Secure Simple Pairing (SSP)

- Encryption Pause Resume (EPR)

- ☐ Enhance Inquiry Response (EIR)

- □ Link Supervision Time Out (LSTO)

- □ Sniff SubRating (SSR)

- □ Erroneous Data (ED)

- □ Packet Boundary Flag (PBF)

- Built-in Low Drop-Out (LDO) regulators (2)

- □ 1.63 to 5.5V input voltage range

- □ 1.8 to 3.3V intermediate programmable output voltage

- Integrated RF section

- □ Single-ended, 50 ohm RF interface

- Built-in TX/RX switch functionality

- TX Class 1 output power capability

- □ -88 dBm RX sensitivity basic rate

- Supports maximum Bluetooth data rates over HCI UART and SPI interfaces

- Multipoint operation, with up to 7 active slaves

- Maximum of 7 simultaneous active ACL links

- Maximum of 3 simultaneous active SCO and eSCO links, with Scatternet support

- Scatternet operation, with up to 4 active piconets (with background scan and support for ScatterMode)

- High-speed HCI UART transport support

- ☐ H4 five-wire UART (four signal wires, one ground wire)

- □ H5 three-wire UART (two signal wires, one ground wire)

- Maximum UART baud rates of 4 Mbps

- Low-power out-of-band BT\_WAKE and HOST\_WAKE signaling

- VSC from host transport to UART

- Proprietary compressing scheme (allows more than two simultaneous A2DP packets and up to five devices at a time)

- Channel Quality-Driven Data Rate (CQDDR) and packet type selection

- Standard Bluetooth test modes

- Extended radio and production test mode features

- Full support for power savings modes:

- Bluetooth standard Hold and Sniff

- Deep sleep modes and regulator shutdown

- Supports Wide-Band Speech (WBS) over PCM and Packet Loss Concealment (PLC) for better audio quality

- 2-, 3-, and 4-wire coexistence

- Power Amplifier (PA) shutdown for externally controlled coexistence, such as WIMAX

- Built-in LPO clock or operation using an external LPO clock

- TCXO input and auto-detection of all standard handset clock frequencies (supports low-power crystal, which can be used during Power Saving mode with better timing accuracy)

- OR gate for combining a host clock request with a Bluetooth clock request (operates even when the Bluetooth core logic is powered

off)

- Larger patch RAM space to support future enhancements

- Serial flash Interface with native support for devices from several manufacturers

- One-Time Programmable (OTP) memory

## 1.2 Block Diagram

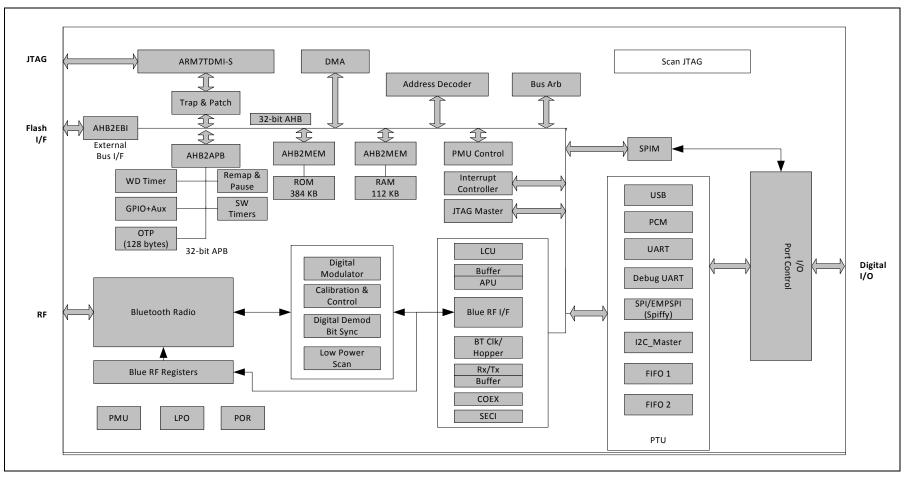

Figure 2 shows the interconnect of the major CYW20710 physical blocks and associated external interfaces.

Figure 2. Functional Block Diagram

Document No. 002-14804 Rev. \*H Page 6 of 50

## 1.3 Mobile Phone Usage Model

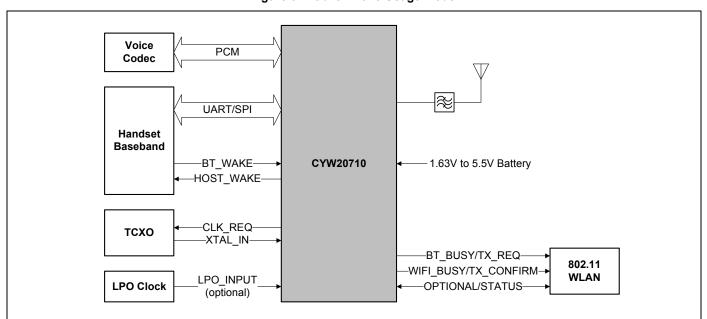

The CYW20710 is designed to provide a direct interface to new and existing handset designs, as shown in Figure 3. The device has flexible PCM and UART interfaces, enabling it to transparently connect to existing circuits. In addition, the TCXO and external LPO inputs allow the use of existing handset features, helping to minimize product size, power, and cost.

The device incorporates a number of unique features to accommodate integration into mobile phone platforms.

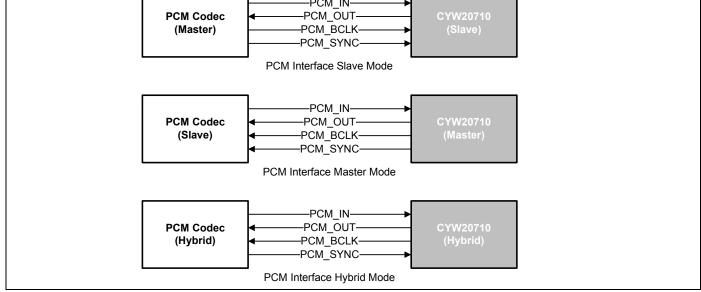

- The PCM interface provides multiple modes of operation to support both master and slave, as well as hybrid interfacing to one or more external codec devices.

- The UART interface supports hardware flow control with tight integration to power control sideband signaling to support the lowest power operation.

- The TCXO interface accommodates the typical reference frequencies used by cell phones.

- A programmable TCXO power-up or power-down signal (active-high or active-low) allows the device to indicate when the clock supplied to the device can be disabled for added power saving during Sleep mode.

- The TCXO and external LPO inputs are high-impedance with minimal loading on the driving source whether power is applied to the device or has been removed.

- The highly linear design of the radio transceiver ensures that the device has the lowest output spurious emissions, regardless of the state of operation, and has been fully characterized in the global cellular bands.

- The transceiver design has excellent blocking (eliminating desensitization of the Bluetooth receiver) and intermodulation performance (distortion of the transmitted signal caused by mixing the cellular and Bluetooth transmissions) in the presence of a cellular transmission (GSM, GPRS, CDMA, WCDMA, or iDEN). Minimal external filtering is required for integration within the handset.

- Few external components are required for integration and very compact WLBGA packaging is available.

Figure 3. Mobile Phone Usage Model

## 2. Integrated Radio Transceiver

The CYW20710 has an integrated radio transceiver that has been optimized for use in 2.4 GHz Bluetooth wireless systems. It has been designed to provide low-power, low-cost, robust communications for applications operating in the globally available 2.4 GHz unlicensed ISM band. The CYW20710 is fully compliant with the Bluetooth Radio Specification and enhanced data rate specification and meets or exceeds the requirements to provide the highest communication link quality of service.

#### 2.1 Transmitter Path

The CYW20710 features a fully integrated zero IF transmitter. The baseband transmitted data is digitally modulated in the modem block and up-converted to the 2.4 GHz ISM band in the transmitter path. The transmitter path consists of signal filtering, I/Q up-conversion, a high-output power amplifier (PA), and RF filtering.

The CYW20710 also incorporates modulation schemes to support enhanced data rates.

- P/4-DQPSK for 2 Mbps

- 8-DPSK for 3 Mbps

#### 2.1.1 Digital Modulator

The digital modulator performs the data modulation and filtering required for the GFSK,  $\Pi$ /4DQPSK, and 8-DPSK signals. The fully digital modulator minimizes any frequency drift or anomalies in the modulation characteristics of the transmitted signal and is much more stable than direct VCO modulation schemes.

#### 2.1.2 Power Amplifier

The CYW20710 has an integrated PA that can be configured for Class 2 operation, transmitting up to +4 dBm. The PA can also be configured for Class 1 operation, transmitting up +10 dBm at the chip in gFSK mode, when a minimum supply voltage of 2.5V is applied to VDDTF.

Because of the linear nature of the PA, combined with integrated filtering, minimal external filtering is required to meet Bluetooth and regulatory harmonic and spurious requirements.

Using a highly linearized, temperature compensated design, the PA can transmit +10 dBm for basic rate and +8 dBm for enhanced data rates (2 to 3 Mbps). A flexible supply voltage range allows the PA to operate from 1.2V to 3.3V. A minimum supply voltage of 2.5V is required at VDDTF to achieve +10 dBm of transmit power.

## 2.2 Receiver Path

The receiver path uses a low IF scheme to downconvert the received signal for demodulation in the digital demodulator and bit synchronizer. The receiver path provides a high degree of linearity, an extended dynamic range, and high order on-chip channel filtering to ensure reliable operation in the noisy 2.4 GHz ISM band. The front-end topology, with built-in out-of-band attenuation, enables the device to be used in most applications without off-chip filtering. For integrated handset operation where the Bluetooth function is integrated close to the cellular transmitter, minimal external filtering is required to eliminate the desensitization of the receiver by the cellular transmit signal.

#### 2.2.1 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer uses the low IF received signal to perform an optimal frequency tracking and bit synchronization algorithm.

## 2.2.2 Receiver Signal Strength Indicator

The CYW20710 radio provides a Receiver Signal Strength Indicator (RSSI) signal to the baseband so that the controller can take part in a Bluetooth power-controlled link by providing a metric of its own receiver signal strength to determine whether the transmitter should increase or decrease its output power.

## 2.3 Local Oscillator Generation

Local Oscillator (LO) generation provides fast frequency hopping (1600 hops/second) across the 79 maximum available channels. The LO generation subblock employs an architecture for high immunity to LO pulling during PA operation. The device uses fully-integrated PLL loop filters.

## 2.4 Calibration

The radio transceiver features an automated calibration scheme that is fully self-contained in the radio. User interaction is not required during normal operation or during manufacturing to provide the optimal performance. Calibration optimizes the performance of all major blocks in the radio, including gain and phase characteristics of filters, matching between key components, and key gain blocks. Calibration, which takes process and temperature variations into account, occurs transparently during the settling time of the hops, adjusting for temperature variations as the device cools and heats during normal operation.

## 2.5 Internal LDO Regulator

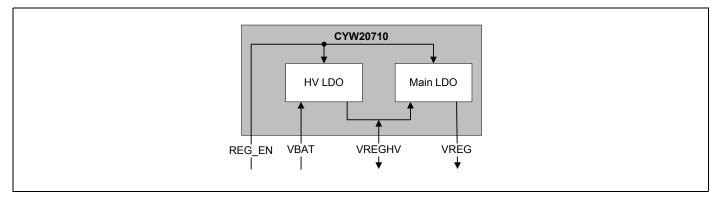

Two internal Low Drop-Out (LDO) voltage regulators eliminate the need for external voltage regulators and therefore reduce the BOM. The first LDO is a preregulator (HV LDO). The second LDO (Main LDO) supplies the main power to the CYW20710 (see Figure 2).

The HV LDO has an input voltage range of 2.3V to 5.5V. The input VBAT is ideal for batteries. The VREGHV output is programmable from 1.8V to 3.3V, in 100 mV steps. The dropout voltage is 200 mV. The HV LDO can supply up to 95 mA, which leaves spare power for external circuitry such as an RF power amp for higher transmit power. If the HV LDO is not used, to turn off the HV LDO and minimize current consumption, connect the VBAT input to the VREGHV output. Firmware can then disable the HV LDO, saving the quiescent current.

The HV LDO default output voltage is 2.9V, allowing this regulator to be used to power external NV memory devices, as well as the VDDO rail. The firmware can then adjust this output to as low as 1.8V, if desired, to power VDDTF.

The main LDO has a 1.22V output (VREG) and is used to supply main power to the CYW20710. The input of this LDO (VREGHV) has an input voltage range of from 1.63V to 3.63V. The output of the HV LDO is internally connected to the input to the main LDO. Power can be applied to VREGHV when the HV LDO is not used. The main LDO supplies power to the entire device for Class 2 operation. The main LDO can drive up to 60 mA, which leaves spare power for external circuitry. The main LDO is bypassed by not connecting anything to its output (VREG) and driving 1.12V–1.32V directly to VDDC and VDDRF.

REG\_EN provides a control signal for the host to control power to the CYW20710. When power is enabled, the CYW20710 will require complete initialization.

Figure 4. LDO Functional Block Diagram

## 3. Bluetooth Baseband Core

The Bluetooth Baseband Core (BBC) implements the time critical functions required for high-performance Bluetooth operation. The BBC manages buffering, segmentation, and data routing for all connections. It also buffers data that passes through it, handles data flow control, schedules SCO/ACL Tx/Rx transactions, monitors Bluetooth slot usage, optimally segments and packages data into baseband packets, manages connection status indicators, and composes and decodes HCI packets. In addition to these functions, it independently handles HCI event types and HCI command types.

#### 3.1 Transmit and Receive Functions

The following transmit and receive functions are implemented in the BBC hardware to increase the reliability and security of the Tx/Rx data before sending the data over the air:

In the transmitter:

- Data framing

- Forward Error Correction (FEC) generation

- Header Error Control (HEC) generation

- Cyclic Redundancy Check (CRC) generation

- Key generation

- Data encryption

- Data whitening

In the receiver:

- Symbol timing recovery

- Data deframing

- FEC

- HEC

- CRC

- Data decryption

- Data dewhitening

## 3.2 Bluetooth 4.0 + EDR Features

The CYW20710 supports Bluetooth 4.0 + EDR, including the following options:

- A whitelist size of 25

- Enhanced Power Control

- HCI Read Encryption Key Size command

The CYW20710 provides full support for Bluetooth 2.1 + EDR additional features:

- Secure Simple Pairing (SSP)

- Encryption Pause Resume (EPR)

- Enhance Inquiry Response (EIR)

- Link Supervision Time Out (LSTO)

- Sniff SubRating (SSR)

- Erroneous Data (ED)

- Packet Boundary Flag (PBF)

## 3.3 Frequency Hopping Generator

The frequency hopping sequence generator selects the correct hopping channel number, based on the link controller state, Bluetooth clock, and device address.

## 3.4 Link Control Layer

The Link Control layer is part of the Bluetooth link control functions implemented in dedicated logic in the Link Control Unit (LCU). This layer consists of the Command Controller that takes commands from the software and other controllers that are activated or configured by the Command Controller to perform the link control tasks.

There are two major states—Standby and Connection. Each task establishes a different state in the Bluetooth Link Controller. In addition, there are eight substates—Page, Page Scan, Inquiry, Inquiry Scan, Park, Sniff Subrate, and Hold.

## 3.5 Test Mode Support

The CYW20710 fully supports Bluetooth Test Mode, including the transmitter tests, normal and delayed Loopback tests, and the reduced hopping sequence.

In addition to the standard Bluetooth Test mode, the device supports enhanced testing features to simplify RF debugging and qualification and type approval testing.

These test features include:

- Fixed frequency carrier wave (unmodulated) transmission

- ☐ Simplifies some type approval measurements (Japan)

- Aids in transmitter performance analysis

- Fixed frequency constant receiver mode

- □ Directs receiver output to I/O pin

- Allows for direct BER measurements using standard RF test equipment

- Facilitates spurious emissions testing for receive mode

- Fixed frequency constant bit stream transmission

- □ Unmodulated, 8-bit fixed pattern, PRBS-9, or PRBS-15

- Enables modulated signal measurements with standard RF test equipment

- Packetized connectionless transmitter test

- Hopping or fixed frequency

- Multiple packet types supported

- Multiple data patterns supported

- Packetized connectionless receiver test

- Fixed frequency

- Multiple packet types supported

- Multiple data patterns supported

## 3.6 Power Management Unit

The Power Management Unit (PMU) provides power management features that can be invoked through power management registers or packet handling in the baseband core. This section contains descriptions of the PMU features.

#### 3.6.1 RF Power Management

The BBC generates power-down control signals for the transmit path, receive path, PLL, and power amplifier to the 2.4 GHz transceiver. The transceiver then processes the power-down functions, accordingly.

#### 3.6.2 Host Controller Power Management

The host can place the device in a sleep state, in which all nonessential blocks are powered off and all nonessential clocks are disabled. Power to the digital core is maintained so that the state of the registers and RAM is not lost. In addition, the LPO clock is applied to the internal sleep controller so that the chip can wake automatically at a specified time or based on signaling from the host. The goal is to limit the current consumption to a minimum, while maintaining the ability to wake up and resume a connection with minimal latency.

If a scan or sniff session is enabled while the device is in Sleep mode, the device automatically will wake up for the scan/sniff event, then go back to sleep when the event is done. In this case, the device uses its internal LPO-based timers to trigger the periodic wake up. While in Sleep mode, the transports are idle. However, the host can signal the device to wake up at any time. If signaled to wake up while a scan or sniff session is in progress, the session continues but the device will not sleep between scan/sniff events. Once Sleep mode is enabled, the wake signaling mechanism can also be thought of as a sleep signaling mechanism, since removing the wake status will often cause the device to sleep.

In addition to a Bluetooth device wake signaling mechanism, there is a host wake signaling mechanism. This feature provides a way for the Bluetooth device to wake up a host that is in a reduced power state.

There are two mechanisms for the device and the host to signal wake status to each other:

| Bluetooth WAKE (BT_WAKE) and Host WAKE (and HOST_WAKE) signaling | The BT_WAKE pin (GPIO_0) allows the host to wake the BT device, and HOST_WAKE (GPIO_1) is an output that allows the BT device to wake the host.                                                                         |

|------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| In-band UART signaling                                           | The CTS and RTS signals of the UART interface are used for BT wake (CTS) and Host wake (RTS) functions in addition to their normal function on the UART interface. Note that this applies for both H4 and H5 protocols. |

When running in SPI mode, the CYW20710 has a mode where it enters Sleep mode when there is no activity on the SPI interface for a specified (programmable) amount of time. Idle mode is detected when the SPI\_CSN is left deasserted. Whether to sleep on an idle interface and the amount of time to wait before entering Sleep mode can be programed by the host. Once the CYW20710 enters sleep, the host can wake it by asserting SPI\_CSN. If the host decides to sleep, the CYW20710 will wake up the host by asserting SPI\_INT when it has data for it.

**Note:** Successful operation of the power management handshaking signals requires coordinated support between the device firmware and the host software.

Table 2. Power Control Pin Summary

| Pin                | Direction               | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BT_WAKE (GPIO_0)   | Host output<br>BT input | Bluetooth device wake-up: Signal from the host to the Bluetooth device that the host requires attention.  • Asserted = Bluetooth device must wake up or remain awake.  • Deasserted = Bluetooth device may sleep when sleep criteria are met.  The polarity of this signal is software configurable and can be asserted high or low. By default, BT_WAKE is active-low (if BT-WAKE is low it requires the device to wake up or remain awake). |

| HOST_WAKE (GPIO_1) | BT output<br>Host input | Host wake-up. Signal from the Bluetooth device to the host indicating that Bluetooth device requires attention.  Asserted = Host device must wake up or remain awake.  Deasserted = Host device may sleep when sleep criteria are met. The polarity of this signal is software configurable and can be asserted high or low.                                                                                                                  |

| CLK_REQ (GPIO_5)   | BT output               | Clock request      Asserted = External clock reference required     Deasserted = External clock reference may be powered down The polarity of CLK_REQ is software configurable and can be set to active high (TM0 = 1) or active low (TM0 = 0).                                                                                                                                                                                               |

| REG_EN             | BT input                | <ul> <li>Enables the internal preregulator and main regulator outputs. REG_EN is active-high.</li> <li>1 = Enabled</li> <li>0 = Disabled</li> </ul>                                                                                                                                                                                                                                                                                           |

## 3.6.3 Bluetooth Baseband Core Power Management

The device provides the following low-power operations for the Bluetooth Baseband Core (BBC):

- Physical layer packet handling turns RF on and off dynamically within packet TX and RX.

- Bluetooth specified low-power connection modes—Sniff, Hold, and Park. While in these low-power connection modes, the device runs on the Low Power Oscillator and wakes up after a predefined time period.

## **Backdrive Protection**

The CYW20710 provides a backdrive protection feature that allows the device to be turned off while the host and other devices in the system remain operational. When the device is not needed in the system, VDD\_RF and VDDC are shut down and VDDO remains powered. This allows the device to be effectively off, while keeping the I/O pins powered so that they do not draw extra current from other devices connected to the I/O.

Note: VDD RF collectively refers to the VDDTF, VDDIF, VDDLNA, VDDPX, and VDDRF RF power supplies.

Note: Never apply voltage to I/O pins if VDDO is not applied.

During the low power shutdown state and as long as VDDO remains applied to the device, all outputs are tristated and all digital and analog clocks are disabled. Input voltages must remain within the limits defined for normal operation. This is done to either prevent current draw and back loading on digital signals in the system. It also enables the device to be fully integrated in an embedded device and take full advantage of the lowest power savings modes. If VDDC is powered up externally (not connected to VREG), VDDC requires 750K ohms to ground during low-power shutdown. If VDDC is powered up by VREG, VDDC does not require 750K ohms to ground because the internal main LDO has about 750 K ohms to ground when turned off.

Several signals, including the frequency reference input (XTAL\_IN) and external LPO input (LPO\_IN), are designed to be high-impedance inputs that will not load down the driving signal, even if VDDO power is not applied to the chip. The other signals with back drive prevention are RST\_N, COEX\_OUT0, COEX\_OUT1, COEX\_IN, PCM\_SYNC, PCM\_CLK, PCM\_OUT, PCM\_IN, UART\_RTS\_N, UART\_CTS\_N, UART\_RXD, UART\_TXD, GPIO\_0, GPIO\_1, GPIO\_2, GPIO\_4, GPIO\_7, CFG\_SEL, and OTP\_DIS.

All other IO signals must remain at VSS until VDDO is applied. Failing to do this can result in unreliable startup behavior.

When powered on, using REG\_EN is the same as applying power to the CYW20710. The device does not have information about its state before being powered-down.

## 3.7 Adaptive Frequency Hopping

The CYW20710 supports host channel classification and dynamic channel classification Adaptive Frequency Hopping (AFH) schemes, as defined in the Bluetooth specification.

Host channel classification enables the host to set a predefined hopping map for the device to follow.

If dynamic channel classification is enabled, the device gathers link quality statistics on a channel-by-channel basis to facilitate channel assessment and channel map selection. To provide a more accurate frequency hop map, link quality is determined using both RF and baseband signal processing.

## 3.8 Collaborative Coexistence

The CYW20710 provides extensions and collaborative coexistence to the standard Bluetooth AFH for direct communication with WLAN devices. Collaborative coexistence enables WLAN and Bluetooth to operate simultaneously in a single device. The device supports industry-standard coexistence signaling, including 802.15.2, and supports Cypress and third-party WLAN solutions.

Using a multitiered prioritization approach, relative priorities between data types and applications can be set. This approach maximizes the performance-WLAN data throughput vs. voice quality vs. link performance.

A PA shutdown pin is available to allow full external control of the RF output for other types of coexistence, such as WIMAX.

#### 3.9 Serial Enhanced Coexistence Interface

The Serial Enhanced Coexistence Interface (Serial ECI or SECI) is a proprietary Cypress interface between Cypress WLAN devices and Bluetooth devices. It is an optional replacement to the legacy 3- or 4-wire coexistence feature, which is also available.

The following key features are associated with the interface:

- Enhanced coexistence data can be exchanged over SECI\_IN and SECI\_OUT.

- It supports generic UART communication between WLAN and Bluetooth devices.

- To conserve power, it is disabled when inactive.

- It supports automatic resynchronizaton upon waking from sleep mode.

- It supports a baud rate of up to 4 Mbps.

## 3.9.1 SECI Advantages

The advantages of the SECI over the legacy 3-wire coexistence interface are:

- Only two wires are required: SECI\_IN and SECI\_OUT.

- Up to 48-bits of coexistence data can be exchanged.

Previous Cypress stand-alone Bluetooth devices such as the CYW2070 supported only a 3-wire or 4-wire coexistence interface. Previous Cypress WLAN and Bluetooth combination devices such as the CYW4325, CYW4329, and CYW4330 support an internal parallel enhanced coexistence interface for more efficient WLAN and Bluetooth information exchange. The SECI allows enhanced coexistence information to be passed to a companion Cypress WLAN chip through a serial interface using fewer I/O than the 3-wire coexistence scheme.

The 48-bits of the SECI significantly enhance WLAN and Bluetooth coexistence by sharing such information as frequencies used and radio usage times. The exact contents of the SECI are Cypress confidential.

#### 3.9.2 SECI I/O

The CYW20710 does not have dedicated SECI\_IN or SECI\_OUT pins, but the two pin functions can be mapped to the following digital I/O: the UART, GPIO, SPIM (or BSC), PCM, and COEX pins. Pin function mapping is controlled by the config file that is either stored in NVRAM or downloaded directly into on-chip RAM from the host.

## 4. Microprocessor Unit

The CYW20710 microprocessor unit runs software from the Link Control (LC) layer up to the Host Controller Interface (HCI). The microprocessor is based on the ARM7TDMIS 32-bit RISC processor with embedded ICE-RT debug and JTAG interface units. The microprocessor also includes 384 KB of ROM memory for program storage and boot ROM, 112 KB of RAM for data scratch-pad, and patch RAM code.

The internal boot ROM provides flexibility during power-on reset to enable the same device to be used in various configurations, including automatic host transport selection from SPI or UART, with or without external NVRAM. At power-up, the lower layer protocol stack is executed from the internal ROM.

External patches can be applied to the ROM-based firmware to provide flexibility for bug fixes and features additions. These patches can be downloaded from the host to the device through the SPI or UART transports, or using external NVRAM. The device can also support the integration of user applications and profiles using an external serial flash memory.

## 4.1 NVRAM Configuration Data and Storage

#### 4.1.1 Serial Interface

The CYW20710 includes an SPI master controller that can be used to access serial flash memory. The SPI master contains an AHB slave interface, transmit and receive FIFOs, and the SPI core PHY logic. Data is transferred to and from the module by the system CPU. DMA operation is not supported.

The CYW20710 supports serial flash vendors Atmel, MXIC, and Numonyx. The most commonly used parts from two of these vendors are:

- AT25BCM512B, manufactured by Atmel

- MX25V512ZUI-20G, manufactured by MXIC

#### 4.2 EEPROM

The CYW20710 includes a Broadcom® Serial Control (BSC) master interface. The BSC interface supports low-speed and fast mode devices and is compatible with I<sup>2</sup>C slave devices. Multiple I<sup>2</sup>C master devices and flexible wait state insertion by the master interface or slave devices are not supported. The CYW20710 provides 400 kHz, full speed clock support.

The BSC interface is programmed by the CPU to generate the following BSC transfer types on the bus:

- Read-only

- Write-only

- Combined read/write

- Combined write-read

NVRAM may contain configuration information about the customer application, including the following:

- Fractional-N information

- BD ADDR

- UART baud rate

- SDP service record

- File system information used for code, code patches, or data

#### 4.3 External Reset

The CYW20710 has an integrated power-on reset circuit which completely resets all circuits to a known power on state. This action can also be driven by an external reset signal, which can be used to externally control the device, forcing it into a power-on reset state. The RST\_N signal input is an active-low signal for all versions of the CYW20710. The CYW20710 requires an external pull-up resistor on the RST\_N input. Alternatively, the RST\_N input can be connected to REG\_EN or driven directly by a host GPIO.

## 4.4 One-Time Programmable Memory

The CYW20710 includes a One-Time Programmable (OTP) memory, allowing manufacturing customization and avoiding the need for an on-board NVRAM.If customization is not required, then the OTP does not need to be programmed. Whether the OTP is programmed or not, it is disabled after the boot process completes to save power.

The OTP size is 128 bytes.

The OTP is designed to store a minimal amount of information. Aside from OTP data, most user configuration information will be downloaded into RAM after the CYW20710 boots up and is ready for host transport communication. The OTP contents are limited to:

- Parameters required prior to downloading user configuration to RAM.

- Parameters unique to a customer design.

#### 4.4.1 Contents

The following are typical parameters programmed into the OTP memory:

- BD ADDR

- Software license key

- Output power calibration

- Frequency trimming

- Initial status LED drive configuration

The OTP contents also include a static error correction table to improve yield during the programming process as well as forward error correction codes to eliminate any long-term reliability problems. The OTP contents associated with error correction are not visible by customers.

## 4.4.2 Programming

OTP memory programming takes place through a combination of Cypress software integrated with the manufacturing test software and code embedded in CYW20710 firmware.

Programming the OTP requires a 3.3V supply. The OTP programming supply comes from the VDDO pin. The OTP power supply can be as low as 1.8V in order to read the OTP contents. OTP\_DIS is brought out to a pin on the WLBGA package but not on the FPBGA package, and is internally pulled low. If the OTP\_DIS pin is left floating or externally pulled low, then the OTP will be enabled. if the OTP\_DIS pins is externally pulled high, then the OTP will be disabled.

## 5. Peripheral Transport Unit

This section discusses the PCM, UART, and SPI peripheral interfaces. The CYW20710 has a 1040 byte transmit and receive fifo, which is large enough to hold the entire payload of the largest EDR BT packet (3-DH5).

#### 5.1 PCM Interface

The CYW20710 PCM interface can connect to linear PCM codec devices in master or slave mode. In master mode, the device generates the PCM\_BCLK and PCM\_SYNC signals. In slave mode, these signals are provided by another master on the PCM interface as inputs to the device.

The device supports up to three SCO or eSCO channels through the PCM interface and each channel can be independently mapped to any available slot in a frame.

The host can adjust the PCM interface configuration using vendor-specific HCI commands or it can be setup in the configuration file.

#### 5.1.1 System Diagram

Figure 5 shows options for connecting the device to a PCM codec device as a master or a slave.

-PCM\_IN-**PCM Codec** -PCM\_OUT-(Master) -PCM BCLK--PCM SYNC-PCM Interface Slave Mode

Figure 5. PCM Interface with Linear PCM Codec

#### 5.1.2 Slot Mapping

The device supports up to three simultaneous, full-duplex SCO or eSCO channels. These channels are time-multiplexed onto the PCM interface using a time slotting scheme based on the audio sampling rate, as described in Table 3.

Table 3. PCM Interface Time Slotting Scheme

| Audio Sample Rate | Time Slotting Scheme                                                    |                                                                         |  |

|-------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|--|

| 8 kHz             | The number of s                                                         | The number of slots depends on the selected interface rate, as follows: |  |

|                   | Interface rate                                                          | Slot                                                                    |  |

|                   | 128                                                                     | 1                                                                       |  |

|                   | 256                                                                     | 2                                                                       |  |

|                   | 512                                                                     | 4                                                                       |  |

|                   | 1024                                                                    | 8                                                                       |  |

|                   | 2048                                                                    | 16                                                                      |  |

| 16 kHz            | The number of slots depends on the selected interface rate, as follows: |                                                                         |  |

|                   | Interface rate                                                          | Slot                                                                    |  |

|                   | 256                                                                     | 1                                                                       |  |

|                   | 512                                                                     | 2                                                                       |  |

|                   | 1024                                                                    | 4                                                                       |  |

|                   | 2048                                                                    | 8                                                                       |  |

Transmit and receive PCM data from an SCO channel is always mapped to the same slot. The PCM data output driver tri-states its output on unused slots to allow other devices to share the same PCM interface signals. The data output driver tri-states its output after the falling edge of the PCM clock during the last bit of the slot.

## 5.1.3 Wideband Speech

The CYW20710 provides support for Wideband Speech (WBS) in two ways:

- Transparent mode The host encodes WBS packets and the encoded packets are transferred over the PCM bus for SCO or eSCO voice connections. In Transparent mode, the PCM bus is typically configured in master mode for a 4 kHz sync rate with 16-bit samples, resulting in a 64 kbps bit rate.

- On-chip SmartAudio® technologyThe CYW20710 can perform Subband-Codec (SBC) encoding and decoding of linear 16 bits at 16 kHz (256 kbps rate) transferred over the PCM bus.

## 5.1.4 Frame Synchronization

The device supports both short and long frame synchronization types in both master and slave configurations. In short frame synchronization mode, the frame synchronization signal is an active-high pulse at the 8 kHz audio frame rate (which is a single bit period in width) and synchronized to the rising edge of the bit clock. The PCM slave expects PCM\_SYNC to be high on the falling edge of the bit clock and the first bit of the first slot to start at the next rising edge of the clock. In the long frame synchronization mode, the frame synchronization signal is an active-high pulse at the 8 kHz audio frame rate. However, the duration is 3-bit periods and the pulse starts coincident with the first bit of the first slot.

## 5.1.5 Data Formatting

The device can be configured to generate and accept several different data formats. The device uses 13 of the 16 bits in each PCM frame. The location and order of these 13 bits is configurable to support various data formats on the PCM interface. The remaining three bits are ignored on the input, and may be filled with zeros, ones, a sign bit, or a programmed value on the output. The default format is 13-bit two's complement data, left justified, and clocked most significant bit first.

## 5.2 HCI Transport Detection Configuration

The CYW20710 supports the following interface types for the HCI transport from the host:

- UART (H4 and H5)

- SPI

Only one host interface can be active at a time. The firmware performs a transport detect function at boot-time to determine which host is the active transport. It can auto-detect the UART interface, but the SPI interface must be selected by strapping the SCL pin to 0.

The complete algorithm is summarized as follows:

- 1. Determine if SCL is pulled low. If it is, select SPI as HCl host transport.

- 2. Determine if any local NVRAM contains a valid configuration file. If it does and a transport configuration entry is present, select the active transport according to entry, and then exit the transport detection routine.

- 3. Look for CTS\_N = 0 on the UART interface. If it is present, select UART.

- 4. Repeat Step 3 until transport is determined.

#### 5.3 UART Interface

The UART physical interface is a standard, 4-wire interface (RX, TX, RTS, CTS) with adjustable baud rates from 9600 bps to 4.0 Mbps. The interface features an automatic baud rate detection capability that returns a baud rate selection. Alternatively, the baud rate can be selected via a vendor-specific UART HCI command. The interface supports Bluetooth UART HCI (H4) specifications. The default baud rate for H4 is 115.2 Kbaud.

The following baud rates are supported:

| 9600  | 115200  | 2000000 |

|-------|---------|---------|

| 14400 | 230400  | 3000000 |

| 19200 | 460800  | 3250000 |

| 28800 | 921600  | 3692000 |

| 38400 | 1444444 | 4000000 |

| 57600 | 1500000 |         |

Normally, the UART baud rate is set by a configuration record downloaded after reset or by automatic baud rate detection. The host does not need to adjust the baud rate. Support for changing the baud rate during normal HCI UART operation is provided through a vendor-specific command.

The CYW20710 UART operates with the host UART correctly, provided the combined baud rate error of the two devices is within ±2%.

## 5.3.1 HCI 3-Wire Transport (UART H5)

The CYW20710 supports H5 UART transport for serial UART communications. H5 reduces the number of signal lines required by eliminating CTS and RTS, when compared to H4. In addition, in-band sleep signaling is supported over the same interface so that the 4-wire UART and the 2-wire sleep signaling interface can be reduced to a 2-wire UART interface, saving four IOs on the host.

H5 requires the use of an external LPO. CTS must be pulled low.

## **PRELIMINARY**

## 5.4 SPI

The CYW20710 supports a slave SPI HCI transport with an input clock range of up to 16 MHz. Higher clock rates may be possible. The physical interface between the SPI master and the CYW20710 consists of the four SPI signals (SPI\_CSB, SPI\_CLK, SPI\_SI, and SPI\_SO) and one interrupt signal (SPI\_INT). The CYW20710 can be configured to accept active-low or active-high polarity on the SPI\_CSB chip select signal. It can also be configured to drive an active-low or active-high SPI\_INT interrupt signal. Bit ordering on the SPI\_SI and SPI\_SO data lines can be configured as either little-endian or big-endian. Additionally, proprietary sleep mode, half-duplex handshaking is implemented between the SPI master and the CYW20710.

SPI\_INT is required to negotiate the start of a transaction. The SPI interface does not require flow control in the middle of a payload. The FIFO is large enough to handle the largest packet size. Only the SPI master can stop the flow of bytes on the data lines, since it controls SPI\_CSB and SPI\_CLK. Flow control should be implemented in higher layer protocols.

## 6. Frequency References

The CYW20710 uses two different frequency references for normal and low-power operational modes. An external crystal or frequency reference driven by a Temperature Compensated Crystal Oscillator (TCXO) signal is used to generate the radio frequencies and normal operation clocking. Either an external 32.768 kHz or fully integrated internal Low-Power Oscillator (LPO) is used for low-power mode timing.

## 6.1 Crystal Interface and Clock Generation

The CYW20710 uses a fractional-N synthesizer to generate the radio frequencies, clocks, and data/packet timing, enabling it to operate from any of a multitude of frequency sources. The source can be external, such as a TCXO, or a crystal interfaced directly to the device.

The default frequency reference setting is for a 20 MHz crystal or TCXO. The signal characteristics for the crystal interface are listed in Table 4.

Table 4. Crystal Interface Signal Characteristics

| Parameter                                                       | Crystal                                                                                         | External Frequency Reference                                                                       | Units                                     |

|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-------------------------------------------|

| Acceptable frequencies                                          | 12–52 MHz in 2 ppm <sup>1</sup> steps                                                           | 12–52 MHz in 2 ppm <sup>1</sup> steps                                                              | _                                         |

| Crystal load capacitance                                        | 12 (typical)                                                                                    | N/A                                                                                                | pF                                        |

| ESR                                                             | 60 (max)                                                                                        | -                                                                                                  | Ω                                         |

| Power dissipation                                               | 200 (max)                                                                                       | -                                                                                                  | μW                                        |

| Input signal amplitude                                          | N/A                                                                                             | 400 to 2000<br>2000 to 3300 (requires a 10 pF DC<br>blocking capacitor to attenuate the<br>signal) | mVp-p                                     |

| Signal type                                                     | N/A                                                                                             | Square-wave or sine-wave                                                                           | _                                         |

| Input impedance                                                 | N/A                                                                                             | ≥ 1<br>≤ 2                                                                                         | MΩ<br>pF                                  |

| Phase noise<br>@ 1 kHz<br>@ 10 kHz<br>@ 100 kHz<br>@ 1 MHz      | N/A<br>N/A<br>N/A<br>N/A<br>N/A                                                                 | -<br>< -120 <sup>2</sup><br>< -131 <sup>2</sup><br>< -136 <sup>2</sup><br>< -136 <sup>2</sup>      | -<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz<br>dBc/Hz |

| Auto-detection frequencies when using external LPO <sup>3</sup> | 12, 13, 14.4, 15.36, 16.2, 16.8, 18, 19.2, 19.44, 19.68, 19.8, 20, 24, 26, 33.6, 37.4, and 38.4 | 12, 13, 14.4, 15.36, 16.2, 16.8, 18, 19.2, 19.44, 19.68, 19.8, 20, 24, 26, 33.6, 37.4, and 38.4    | MHz                                       |

| Tolerance without frequency trimming <sup>4</sup>               | ±20                                                                                             | ±20                                                                                                | ppm                                       |

| Initial frequency tolerance trimming range                      | ±50                                                                                             | ±50                                                                                                | ppm                                       |

- 1. The frequency step size is approximately 80 Hz resolution.

- 2. With a 26 MHz reference clock. For a 13 MHz clock, subtract 6 dB. For a 52 MHz clock, add 6 dB.

- 3. Auto-detection of the frequency requires the crystal or external frequency reference to have less than ±50 ppm of variation and also requires an external LPO frequency which has less than ±250 ppm of variation at the time of detection.

- 4. AT-Cut crystal or TXCO recommended.

## 6.2 Crystal Oscillator

The CYW20710 can use an external crystal to provide a frequency reference. The recommended configuration for the crystal oscillator, including all external components, is shown in Figure 6.

Crystal Oscillator

O to 18 pF\*

\*Capacitor value range depends on the manufacturer of the XTAL as well as board layout.

Figure 6. Recommended Oscillator Configuration

## 6.3 External Frequency Reference

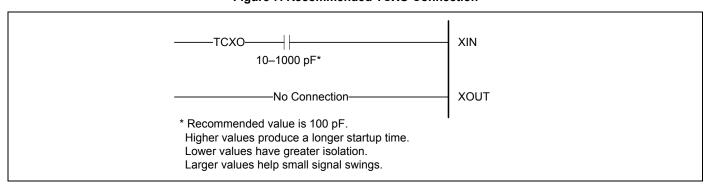

An external frequency reference generated by a TCXO signal that may be directly connected to the crystal input pin on the CYW20710, as shown in Figure 7. The external frequency reference input is designed to not change loading on the TCXO when the CYW20710 is powered up or powered down.

When using the CYW20710 with the TXCO OR gate option, GPIO 6 must be driven active high or active low. Excessive leakage current results if GPIO6 is allowed to float.

Figure 7. Recommended TCXO Connection

## 6.3.1 TCXO Clock Request Support

If the application utilizes an external TCXO as a clock reference, the CYW20710 provides a clock request output to allow the system to power off the TCXO when not in use. Optionally, some packages support a TCXO OR function that allows a clock request in the system to be combined with the CYW20710 clock request output, without requiring an extra component on the board.

## **Clock Request Output**

The CLK\_REQ signal on the GPIO\_5 lead is asserted whenever the CYW20710 is in the Awake state. It is deasserted when in Sleep state. When the CYW20710 is sleeping, it uses an LPO clock (external or internal) as the timing reference.

The TM0 lead controls the polarity of the CLK REQ output on GPIO 5 as follows:

TM0 = 0 CLK REQ is active low

TM0 = 1 CLK REQ is active high

If the clock request feature is not desired, GPIO 5 can be configured for other functions.

## **TCXO OR Option**

The CYW20710 has an optional feature that allows the application to perform a logical OR function on a system TCXO clock request signal and the CYW20710 clock request to form one clock request output to the TCXO device. This logical OR function is embedded in the pad ring so that it is available at any time, as long as the pad ring is receiving a VDDO supply. The function works even if the CYW20710's digital core is sleeping or completely powered off.

To use this feature, the TCXO\_MODE lead must be tied high. In this mode, the GPIO\_6 lead functions as the external clock request input. Without TCXO\_MODE asserted, GPIO\_5 functions as the clock request output (based only on the internal clock requirements of the CYW20710) and the state of GPIO\_6 is ignored.

As mentioned earlier, the TM0 lead controls the polarity of the CLK\_REQ output on GPIO\_5. However, it assumes that GPIO\_6 input polarity is already consistent with the desired polarity on GPIO\_5/CLK\_REQ. Therefore, when TM0 is 1 for an active high output, the function is a simple OR between the external GPIO\_6 and the internal clock request state. However, when TM0 is 0 for an active low output, the logic inverts the internal clock request signal and performs an AND between it and the GPIO\_6 input. Even though it is using an OR gate, it still provides a logical AND on the two clock request states.

Since the logic assumes that it is also active low (similar to GPIO\_5 output), it does not invert the GPIO\_6 input first. Table 5 shows the truth table.

Table 5. Truth Table

| GPIO_6<br>CLK_REQ_IN | Internal Clock Request State<br>(0 = sleep) | TM0<br>(0 = active low output) | GPIO_5<br>CLK_REQ |

|----------------------|---------------------------------------------|--------------------------------|-------------------|

| 0                    | 0                                           | 0                              | 0                 |

| 0                    | 1                                           | 0                              | 0                 |

| 1                    | 0                                           | 0                              | 1                 |

| 1                    | 1                                           | 0                              | 0                 |

| 0                    | 0                                           | 1                              | 0                 |

| 0                    | 1                                           | 1                              | 1                 |

| 1                    | 0                                           | 1                              | 1                 |

| 1                    | 1                                           | 1                              | 1                 |

## Package Options and TCXO Mode

Only a few package options bring out TM0 to balls, allowing the application to configure them. In most packages, these pins are already configured.

Table 6 lists available package options.

Table 6. Package Options

| Part Number      | Package Description                                  |                 |

|------------------|------------------------------------------------------|-----------------|

| CYW20710A1KUFBXG | 50-ball FPBGA, optimized for cell phone applications | Brought to ball |

| CYW20710A1KUBXG  | 42-ball WLBGA                                        | 1               |

## 6.4 Frequency Selection

Any frequency within the range specified for the crystal and TCXO reference can be used. These frequencies include standard handset reference frequencies (12, 13, 14.4, 15.36, 16.2, 16.8, 18, 19.2, 19.44, 19.68, 19.8, 20, 24, 26, 33.6, 37.4, and 38.4 MHz) and any frequency between these reference frequencies, as desired by the system designer. Since bit timing is derived from the reference frequency, the CYW20710 must have the reference frequency set correctly in order for the UART and PCM interfaces to function properly.

The CYW20710 reference frequency can be set in one of three ways.

- Use the default 20 MHz frequency

- Designate the reference frequency in external NVRAM