Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# 5x7mm **Precision TCXO** In Stock at Digi-Key

2111 Comprehensive Drive Aurora, Illinois 60505 Phone: 630-851-4722 Fax: 630-851-5040

www.conwin.com

US Headquarters: 630-851-4722 +353-61-472221

**Description:**

The Connor-Winfield's D75J is a 5x7mm Surface Mount Temperature Compensated Crystal Controlled Oscillator (TCXO) with a Tri-State LVCMOS output. Through the use of Analog Temperature Compensation, the D75J is capable of holding sub 1-ppm stabilities over the 0 to 70°C temperature range.

Features: Model: D75J 3.3 Vdc Operation LVCMOS Output Frequency Stability: ± 1.0 ppm Temperature Range: 0 to 70°C Low Jitter <1ps RMS Tri-State Enable/Disable Function 5x7mm Surface Mount Package Tape and Reel Packaging RoHS Compliant / Pb Free ✓ RoHS

#### **Absolute Maximum Ratings**

| Parameter            | Minimum | Nominal | Maximum | Units | Notes |

|----------------------|---------|---------|---------|-------|-------|

| Storage Temperature  | -55     | -       | 85      | °C    |       |

| Supply Voltage (Vcc) | -0.5    | -       | 6.0     | Vdc   |       |

| Input Voltage        | -0.5    | -       | Vcc+0.5 | Vdc   |       |

## **Operating Specifications**

| Parameter                           | Minimum | Nominal             | Maximum | Units    | Notes  |

|-------------------------------------|---------|---------------------|---------|----------|--------|

| Nominal Frequency (Fo)              | -       | 38.88, 40.0 or 50.0 | -       | MHz      | 140100 |

| Frequency Calibration @ 25 °C       | -1.0    | -                   | 1.0     | ppm      | 1      |

| Frequency Stability vs. Temperature | -1.0    | -                   | 1.0     | ppm      | 2      |

| Frequency vs. Load Stability        | -0.2    | -                   | 0.2     | ppm      | ±5%    |

| Frequency vs. Voltage Stability     | -0.2    | -                   | 0.2     | ppm      | ±5%    |

| Static Temperature Hysteresis       | -       | -                   | 0.4     | ppm      | 3      |

| Aging                               | -1.0    | -                   | 1.0     | ppm/year |        |

| Operating Temperature Range:        | 0       | -                   | 70      | °C       |        |

| Supply Voltage (Vcc)                | 3.135   | 3.3                 | 3.465   | Vdc      | ±5%    |

| Supply Current (Icc)                | -       | -                   | 6       | mA       |        |

| Period Jitter                       | -       | 3                   | 5       | ps rms   |        |

| Integrated Phase Jitter             | -       | 0.5                 | 1.0     | ps rms   | 4      |

| SSB Phase Noise at 10Hz offset      | -       | -70                 | -       | dBc/Hz   |        |

| SSB Phase Noise at 100Hz offset     | -       | -100                | -       | dBc/Hz   |        |

| SSB Phase Noise at 1KHz offset      | -       | -120                | -       | dBc/Hz   |        |

| SSB Phase Noise at 10KHz offset     | _       | -140                | _       | dBc/Hz   |        |

| SSB Phase Noise at 100KHz offset    | -       | -145                | -       | dBc/Hz   |        |

| Start-up Time                       | -       | -                   | 5       | ms       |        |

## Enable / Disable Input Characteristics (Pad 8)

| Parameter             | Minimum | Nominal | Maximum | Units | Notes |

|-----------------------|---------|---------|---------|-------|-------|

| Enable Voltage (High) | 70%Vcc  |         | -       | Vdc   | 5     |

| Disable Voltage (Low) | -       | -       | 30%Vcc  | Vdc   | 5     |

#### **LVCMOS Output Characteristics**

| Parameter                   | Minimum | Nominal | Maximum | Units | Notes |

|-----------------------------|---------|---------|---------|-------|-------|

| Load                        | -       | 15      | -       | рF    | 6     |

| Voltage (High) (Voh)        | 90%Vcc  | -       | -       | Vdc   |       |

| (Low) (Vol)                 | -       | -       | 10%Vcc  | Vdc   |       |

| Duty Cycle at 50% of Vcc    | 45      | 50      | 55      | %     |       |

| Rise / Fall Time 10% to 90% | -       | -       | 8       | ns    |       |

#### Package Characteristics

Hermetically spaled crystal mounted on a ceramic nackage

| _ r ackage                    | Hermetically sealed crystal mounted on a ceramic package          |  |

|-------------------------------|-------------------------------------------------------------------|--|

| Environmental Characteristics |                                                                   |  |

| Vibration:                    | Vibration per Mil Std 883E Method 2007.3 Test Condition A         |  |

| Shock:                        | Mechanical Shock per Mil Std 883E Method 2002.4 Test Condition B. |  |

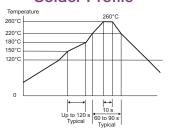

| Soldering Process;            | RoHS compliant lead free. See soldering profile on page 2.        |  |

#### Ordering Information D75J-038.88M\*, D75J-040.0M\* or D75J-050.0M\*

\* For the tape and reel option, add -T to the end of the part number. Example: D75J-038.88M-T

- 1. Initial calibration @ 25°C. Specifications at time of shipment after 48 hours of operation.

- 2. Frequency stability vs. change in temperature. [±(Fmax Fmin)/2.Fo].

3. Frequency change after reciprocal temperature ramped over the operating range. Frequency measured before and after at 25°C.

- 4. BW = 12 KHz to 20 MHz.

Package

- 5. Leave Pad 8 unconnected if enable / disable function is not required. When tri-stated, the output stage is disabled but the oscillator and compensation circuit are still active (current consumption < 1 mA).

- 6. For best performance it is recommended that the circuit connected to this output should have an equivalent input capacitance of 15pF.

| Bulletin | Tx238       |

|----------|-------------|

| Page     | 1 of 2      |

| Revision | 03          |

| Date     | 15 Nov 2011 |

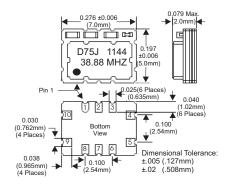

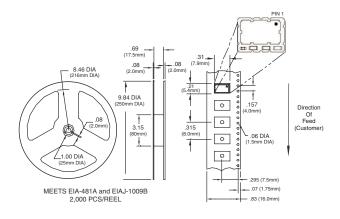

# **Package Layout**

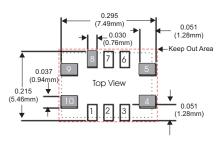

# **Suggested Pad Layout**

\* Do not route any traces in the keep out area. It is recommended the next layer under the keep out area is to be ground plane.

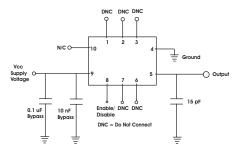

## **Pad Connections**

| _1: | Do Not Connect             |

|-----|----------------------------|

| 2:  | Do Not Connect             |

| _3: | Do Not Connect             |

| 4:  | Ground                     |

| 5:  | Output                     |

| _6: | Do Not Connect             |

| _7: | Do Not Connect             |

| _8: | Tri-State Enable / Disable |

| 9:  | Supply Voltage Vcc         |

| 10: | N/C                        |

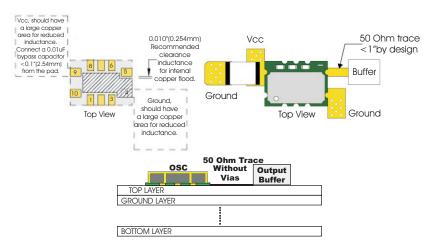

# **Design Recommendations**

Attention: To achieve optimal frequency stability, and in some cases to meet the specification stated on this data sheet, it is required that the circuit connected to this TCXO output must have the equivalent input capacitance that is specified by the nominal load capacitance. Deviations from the nominal load capacitance will have a graduated effect on the stability of approximately 20 ppb per pF load difference.

# **Output Waveform**

# **Test Circuit**

# **Tape and Reel Dimensions**

## Solder Profile

Meets IPC/JEDEC J-STD-020C

| Bulletin | Tx238       |

|----------|-------------|

| Page     | 2 of 2      |

| Revision | 03          |

| Date     | 15 Nov 2011 |