# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Dual 10-bit DAC; up to 650 Msps; 2×, 4× or 8× interpolating with JESD204A interface

Rev. 04 — 2 July 2012

**Product data sheet**

# 1. General description

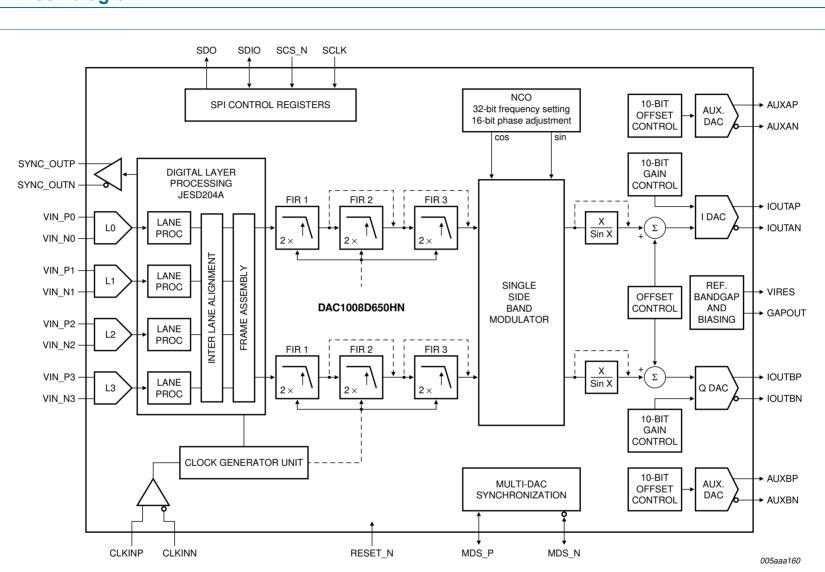

The DAC1008D650 is a high-speed 10-bit dual channel Digital-to-Analog Converter (DAC) with selectable  $2\times$ ,  $4\times$  or  $8\times$  interpolating filters optimized for multi-carrier WCDMA transmitters.

Because of its digital on-chip modulation, the DAC1008D650 allows the complex pattern provided through lane 0, lane 1, lane 2 and lane 3, to be converted up from baseband to IF. The mixing frequency is adjusted via a Serial Peripheral Interface (SPI) with a 32-bit Numerically Controlled Oscillator (NCO) and the phase is controlled by a 16-bit register.

The DAC1008D650 also includes a  $2\times$ ,  $4\times$  or  $8\times$  clock multiplier which provides the appropriate internal clocks and an internal regulation to adjust the output full-scale current.

The input data format is serial according to JESD204A specification. This new interface has numerous advantages over the traditional parallel one: easy PCB layout, lower radiated noise, lower pin count, self-synchronous link, skew compensation. The maximum number of lanes of the DAC1008D650 is 4 and its maximum serial data rate is 3.125 Gbps.

The Multiple Device Synchronization (MDS) guarantees a maximum skew of one output clock period between several DAC devices. MDS incorporates modes: Master/slave and All slave mode.

# 2. Features and benefits

- Dual 10-bit resolution

- 650 Msps maximum update rate

- Selectable 2×, 4× or 8× interpolation filters

- Input data rate up to 312.5 Msps

- Very low noise cap free integrated PLL

- 32-bit programmable NCO frequency

- Four JESD204A serial input lanes

- 1.8 V and 3.3 V power supplies

- LVDS compatible clock inputs

- IMD3: 80 dBc; f<sub>s</sub> = 640 Msps; f<sub>o</sub> = 140 MHz

- ACPR: 64 dBc; two carriers WCDMA; f<sub>s</sub> = 640 Msps; f<sub>o</sub> = 133 MHz

- Typical 1.20 W power dissipation at 4× interpolation, PLL off and 640 Msps

- Power-down mode and Sleep modes

- Differential scalable output current from 1.6 mA to 22 mA

- On-chip 1.29 V reference

- External analog offset control (10-bit auxiliary DACs)

- Internal digital offset control

- Inverse (sin x) / x function

#### $2\times$ , $4\times$ or $8\times$ interpolating DAC with JESD204A

- Two's complement or binary offset data Fully compatible SPI port format

- LMF = 421 or LMF = 211 support

- Differential CML receiver with embedded termination

- Industrial temperature range from -40 °C to +85 °C

- Integrated PLL can be bypassed

- Synchronization of multiple DAC outputs Embedded complex modulator

# 3. Applications

- Wireless infrastructure: LTE, WiMAX, GSM, CDMA, WCDMA, TD-SCDMA

- Communication: LMDS/MMDS, point-to-point

- Direct Digital Synthesis (DDS)

- Broadband wireless systems

- Digital radio links

- Instrumentation

- Automated Test Equipment (ATE)

# 4. Ordering information

#### Table 1.Ordering information

| Type number   | Package |                                                                                                                  |          |

|---------------|---------|------------------------------------------------------------------------------------------------------------------|----------|

|               | Name    | Description                                                                                                      | Version  |

| DAC1008D650HN | HVQFN64 | plastic thermal enhanced very thin quad flat package; no leads; 64 terminals; body 9 $\times$ 9 $\times$ 0.85 mm | SOT804-3 |

# 5. Block diagram

Fig 1.

**Block diagram**

DAC1008D650 2×, 4× or 8× interpolating DAC with JESD204A

2×, 4× or 8× interpolating DAC with JESD204A

# 6. Pinning information

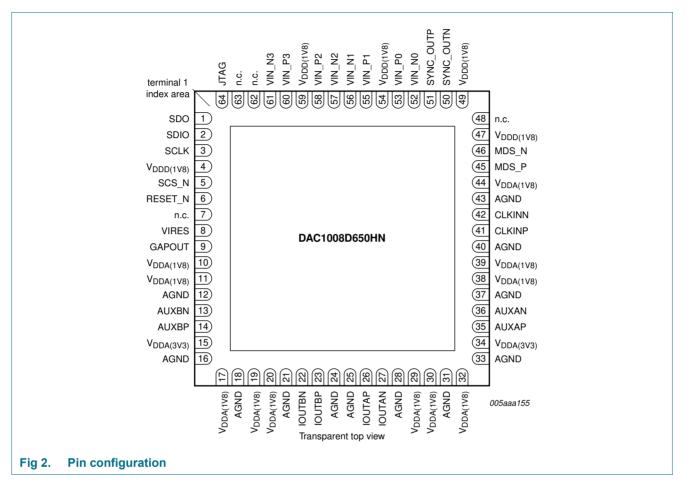

# 6.1 Pinning

# 6.2 Pin description

| Table 2.              | Pin description | on    |                    |                              |

|-----------------------|-----------------|-------|--------------------|------------------------------|

| Symbol                | P               | in Ty | 'pe <sup>[1]</sup> | Description                  |

| SDO                   | 1               | 0     |                    | SPI data output              |

| SDIO                  | 2               | I/C   | )                  | SPI data input/output        |

| SCLK                  | 3               | I     |                    | SPI clock                    |

| V <sub>DDD(1V8)</sub> | 4               | Р     |                    | digital supply voltage 1.8 V |

| SCS_N                 | 5               | I     |                    | SPI chip select (active LOW) |

| RESET_N               | 6               | I     |                    | general reset (active LOW)   |

| n.c.                  | 7               | -     |                    | not connected                |

| VIRES                 | 8               | I/C   | )                  | DAC biasing resistor         |

| GAPOUT                | 9               | I/C   | )                  | bandgap input/output voltage |

| V <sub>DDA(1V8)</sub> | 1(              | ) P   |                    | analog supply voltage 1.8 V  |

| V <sub>DDA(1V8)</sub> | 11              | I P   |                    | analog supply voltage 1.8 V  |

|                       |                 |       |                    |                              |

# 2×, 4× or 8× interpolating DAC with JESD204A

| Table 2.              | Pin description | continued           |                                                              |

|-----------------------|-----------------|---------------------|--------------------------------------------------------------|

| Symbol                | Pin             | Type <sup>[1]</sup> | Description                                                  |

| AGND                  | 12              | G                   | analog ground                                                |

| AUXBN                 | 13              | 0                   | complementary auxiliary DAC B output                         |

| AUXBP                 | 14              | 0                   | auxiliary DAC B output                                       |

| V <sub>DDA(3V3)</sub> | 15              | Р                   | analog supply voltage 3.3 V                                  |

| AGND                  | 16              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 17              | Р                   | analog supply voltage 1.8 V                                  |

| AGND                  | 18              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 19              | Р                   | analog supply voltage 1.8 V                                  |

| V <sub>DDA(1V8)</sub> | 20              | Р                   | analog supply voltage 1.8 V                                  |

| AGND                  | 21              | G                   | analog ground                                                |

| IOUTBN                | 22              | 0                   | complementary DAC B output current                           |

| IOUTBP                | 23              | 0                   | DAC B output current                                         |

| AGND                  | 24              | G                   | analog ground                                                |

| AGND                  | 25              | G                   | analog ground                                                |

| IOUTAP                | 26              | 0                   | DAC A output current                                         |

| IOUTAN                | 27              | 0                   | complementary DAC A output current                           |

| AGND                  | 28              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 29              | Р                   | analog supply voltage 1.8 V                                  |

| V <sub>DDA(1V8)</sub> | 30              | Р                   | analog supply voltage 1.8 V                                  |

| AGND                  | 31              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 32              | Р                   | analog supply voltage 1.8 V                                  |

| AGND                  | 33              | G                   | analog ground                                                |

| V <sub>DDA(3V3)</sub> | 34              | Р                   | analog supply voltage 3.3 V                                  |

| AUXAP                 | 35              | 0                   | auxiliary DAC A output current                               |

| AUXAN                 | 36              | 0                   | complementary auxiliary DAC A output current                 |

| AGND                  | 37              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 38              | Р                   | analog supply voltage 1.8 V                                  |

| V <sub>DDA(1V8)</sub> | 39              | Р                   | analog supply voltage 1.8 V                                  |

| AGND                  | 40              | G                   | analog ground                                                |

| CLKINP                | 41              | I                   | clock input                                                  |

| CLKINN                | 42              | I                   | complementary clock input                                    |

| AGND                  | 43              | G                   | analog ground                                                |

| V <sub>DDA(1V8)</sub> | 44              | Р                   | analog supply voltage 1.8 V                                  |

| MDS_P                 | 45              | I/O                 | multi-device synchronization                                 |

| MDS_N                 | 46              | I/O                 | complementary multi-device synchronization                   |

| V <sub>DDD(1V8)</sub> | 47              | Р                   | digital supply voltage 1.8 V                                 |

| n.c.                  | 48              | -                   | not connected                                                |

| V <sub>DDD(1V8)</sub> | 49              | Р                   | digital supply voltage 1.8 V                                 |

| SYNC_OUT              | TN 50           | 0                   | synchronization request to transmitter, complementary output |

| SYNC_OUT              | TP 51           | 0                   | synchronization request to transmitter                       |

| Table 2.              | Pin descrip | otion            | .continued          |                                          |

|-----------------------|-------------|------------------|---------------------|------------------------------------------|

| Symbol                |             | Pin              | Type <sup>[1]</sup> | Description                              |

| VIN_N0                |             | 52               | I                   | serial interface lane 0 negative input   |

| VIN_P0                |             | 53               | I                   | serial interface lane 0 positive input   |

| V <sub>DDD(1V8)</sub> |             | 54               | Р                   | digital supply voltage 1.8 V             |

| VIN_P1                |             | 55               | I                   | serial interface lane 1 positive input   |

| VIN_N1                |             | 56               | I                   | serial interface lane 1 negative input   |

| VIN_N2                |             | 57               | I                   | serial interface lane 2 negative input   |

| VIN_P2                |             | 58               | I                   | serial interface lane 2 positive input   |

| V <sub>DDD(1V8)</sub> |             | 59               | Р                   | digital supply voltage 1.8 V             |

| VIN_P3                |             | 60               | I                   | serial interface lane 3 positive input   |

| VIN_N3                |             | 61               | I                   | serial interface lane 3 negative input   |

| n.c.                  |             | 62               | -                   | not connected                            |

| n.c.                  |             | 63               | -                   | not connected                            |

| JTAG                  |             | 64               | I                   | JTAG test mode select (must be grounded) |

| GND                   |             | H <sup>[2]</sup> | G                   | ground                                   |

[1] P: power supply; G: ground; I: input; O: output.

[2] H = heatsink (exposed die pad to be soldered to GND. A minimum of 81 thermal vias are required).

# 7. Limiting values

#### Table 3.Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

|                       | • •                           | , ,        |      |      |      |

|-----------------------|-------------------------------|------------|------|------|------|

| Symbol                | Parameter                     | Conditions | Min  | Мах  | Unit |

| V <sub>DDA(3V3)</sub> | analog supply voltage (3.3 V) |            | -0.5 | +4.6 | V    |

| V <sub>DDA(1V8)</sub> | analog supply voltage (1.8 V) |            | -0.5 | +2.5 | V    |

| V <sub>DDD</sub>      | digital supply voltage        |            | -0.5 | +2.5 | V    |

| T <sub>stg</sub>      | storage temperature           |            | -55  | +150 | °C   |

| T <sub>amb</sub>      | ambient temperature           |            | -40  | +85  | °C   |

| Tj                    | junction temperature          |            | -40  | +125 | °C   |

|                       |                               |            |      |      |      |

# 8. Thermal characteristics

| Table 4.             | Thermal characteristics                     |            |                     |      |

|----------------------|---------------------------------------------|------------|---------------------|------|

| Symbol               | Parameter                                   | Conditions | Тур                 | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |            | <sup>[1]</sup> 18.7 | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | <sup>[1]</sup> 6.7  | K/W  |

[1] Complies with JEDEC test board, in free air.

# 9. Characteristics

#### Table 5. Characteristics

$V_{DDA(1V8)} = V_{DDD} = 1.7 \text{ V to } 1.9 \text{ V}; V_{DDA(3V3)} = 3.13 \text{ V to } 3.47 \text{ V}; \text{ AGND and GND are shorted together}; T_{amb} = -40 ^{\circ}\text{C to} +85 ^{\circ}\text{C}; \text{ typical values measured at } V_{DDA(1V8)} = V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = +25 ^{\circ}\text{C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA}; \text{ maximum sample rate; PLL off unless otherwise specified.}$

| Symbol                  | Parameter                         | Conditions                                                                                                  | Test <sup>[1]</sup> | Min   | Тур  | Max  | Unit |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------|---------------------|-------|------|------|------|

| V <sub>DDA(3V3)</sub>   | analog supply voltage<br>(3.3 V)  |                                                                                                             | I                   | 3.13  | 3.3  | 3.47 | V    |

| V <sub>DDD(1V8)</sub>   | digital supply voltage<br>(1.8 V) |                                                                                                             | I                   | 1.7   | 1.8  | 1.9  | V    |

| V <sub>DDA(1V8)</sub>   | analog supply voltage<br>(1.8 V)  |                                                                                                             | I                   | 1.7   | 1.8  | 1.9  | V    |

| I <sub>DDA(3V3)</sub>   | analog supply current<br>(3.3 V)  | $f_o$ = 19 MHz; $f_s$ = 640 Msps;<br>4× interpolation; NCO on                                               | I                   | -     | 41   | -    | mA   |

| I <sub>DDD(1V8)</sub>   | digital supply current<br>(1.8 V) | $f_o$ = 19 MHz; $f_s$ = 640 Msps;<br>4× interpolation; NCO on                                               | I                   | -     | 356  | -    | mA   |

| I <sub>DDA(1V8)</sub>   | analog supply current<br>(1.8 V)  | $f_o$ = 19 MHz; $f_s$ = 640 Msps;<br>4× interpolation; NCO on                                               | I                   | -     | 373  | -    | mA   |

| $\Delta I_{DDD}$        | digital supply current difference | x/sin x function on;<br>f <sub>s</sub> = 640 Msps                                                           | I                   | -     | 48   | -    | mA   |

| P <sub>tot</sub>        | total power dissipation           | $f_s = 640 \text{ Msps};$<br>4× interpolation; NCO off;<br>DAC Q off                                        | С                   | -     | 0.75 | -    | W    |

|                         |                                   | f <sub>s</sub> = 640 Msps;<br>4× interpolation; NCO off                                                     | С                   | -     | 1.20 | -    | W    |

|                         |                                   | f <sub>s</sub> = 640 Msps;<br>4× interpolation; NCO on                                                      | С                   | -     | 1.45 | -    | W    |

|                         |                                   | f <sub>s</sub> = 625 Msps;<br>2× interpolation; NCO off                                                     | С                   | -     | 1.29 | -    | W    |

|                         |                                   | f <sub>s</sub> = 625 Msps;<br>2× interpolation; NCO on                                                      | С                   | -     | 1.46 | -    | W    |

|                         |                                   | Power-down mode;<br>$f_o = 19 \text{ MHz}$ ; $f_s = 640 \text{ Msps}$ ;<br>$4 \times$ interpolation; NCO on |                     |       |      |      |      |

|                         |                                   | complete device;<br>Power-down mode                                                                         | I                   | -     | 0.04 | -    | W    |

|                         |                                   | DAC A and DAC B;<br>Power-down mode                                                                         | I                   | -     | 0.58 | -    | W    |

|                         |                                   | DAC A and DAC B;<br>Sleep mode                                                                              | I                   | -     | 0.75 | -    | W    |

| Timing spec             | ifications                        |                                                                                                             |                     |       |      |      |      |

| t <sub>d(startup)</sub> | start-up delay time               | from full Power-down mode                                                                                   | D                   | -     | 20   | -    | ms   |

| t <sub>d(restart)</sub> | restart delay time                | from Sleep mode                                                                                             | D                   | -     | 300  | -    | ns   |

| t <sub>lock</sub>       | lock time                         | maximum input rate                                                                                          | D                   | [2] _ | 11   | -    | μS   |

| Clock inputs            | s (CLKINN, CLKINP) <sup>[3]</sup> |                                                                                                             |                     |       |      |      |      |

| Vi                      | input voltage                     | range: CLK+ or CLK–<br> V <sub>gpd</sub>   < 50 mV <sup>[4]</sup>                                           | С                   | 825   | -    | 1575 | mV   |

#### Table 5. Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD} = 1.7 \text{ V to } 1.9 \text{ V}; V_{DDA(3V3)} = 3.13 \text{ V to } 3.47 \text{ V}; \text{ AGND and GND are shorted together}; T_{amb} = -40 \degree \text{C to} +85 \degree \text{C}; \text{ typical values measured at } V_{DDA(1V8)} = V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = +25 \degree \text{C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA}; \text{ maximum sample rate; PLL off unless otherwise specified.}$

| Symbol                   | Parameter                                      | Conditions                          | Test <sup>[1]</sup> | Min          | Тур              | Мах          | Unit |

|--------------------------|------------------------------------------------|-------------------------------------|---------------------|--------------|------------------|--------------|------|

| V <sub>idth</sub>        | input differential threshold voltage           | $ V_{gpd}  < 50 \text{ mV}^{[4]}$   | С                   | -100         | -                | +100         | mV   |

| R <sub>i</sub>           | input resistance                               |                                     | D                   | -            | 10               | -            | MΩ   |

| CI                       | input capacitance                              |                                     | D                   | -            | 0.5              | -            | pF   |

| Digital inpu             | ts (SDO, SDIO, SCLK, SC                        | S_N, RESET_N)                       |                     |              |                  |              |      |

| V <sub>IL</sub>          | LOW-level input voltage                        |                                     | С                   | GND          | -                | $0.3V_{DDD}$ | V    |

| V <sub>IH</sub>          | HIGH-level input voltage                       |                                     | С                   | $0.7V_{DDD}$ | -                | $V_{DDD}$    | V    |

| IIL                      | LOW-level input current                        | $V_{IL} = 0.3 V_{DDD} V$            | I                   | -            | 1                | -            | μA   |

| I <sub>IH</sub>          | HIGH-level input<br>current                    | $V_{IH} = 0.7 V_{DDD} V$            | I                   | -            | 1                | -            | μA   |

| Digital outp             | uts (SDO, SDIO)                                |                                     |                     |              |                  |              |      |

| V <sub>OL</sub>          | LOW-level output voltage                       | I <sub>load</sub> = 2 mA            | С                   | GND          | -                | 0.13         | V    |

| V <sub>OH</sub>          | HIGH-level output voltage                      | С                                   | 1.65                | -            | V <sub>DDD</sub> | V            |      |

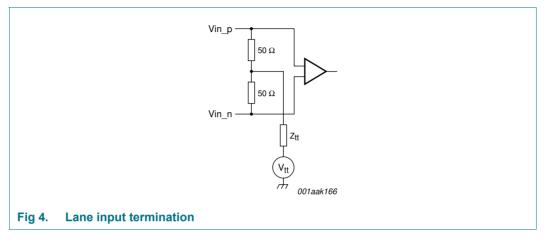

| Digital inpu             | ts (Vin_p/Vin_n) <sup>[5]</sup>                |                                     |                     |              |                  |              |      |

| V <sub>I(cm)</sub>       | common-mode input voltage                      |                                     | D                   | -            | 0.78             | -            | V    |

| V <sub>I(dif)(p-p)</sub> | peak-to-peak<br>differential input<br>voltage  |                                     | D                   | 175          | -                | 1000         | mV   |

| Z <sub>tt</sub>          | V <sub>tt</sub> source impedance               |                                     | D                   | -            | 0.7              | -            | Ω    |

| $\Delta Z_i$             | differential input impedance                   |                                     | D                   | -            | 100              | -            | Ω    |

| Digital outp             | uts (SYNC_OUTN/SYNC_                           | OUTP) <sup>[6]</sup>                |                     |              |                  |              |      |

| V <sub>o(cm)</sub>       | common-mode output<br>voltage                  |                                     | С                   | -            | 1.18             | -            | V    |

| V <sub>o(dif)(p-p)</sub> | peak-to-peak<br>differential output<br>voltage |                                     | С                   | -            | 0.45             | -            | V    |

| Digital inpu             | ts/outputs (MDS_N/MDS_                         | P)                                  |                     |              |                  |              |      |

| V <sub>o(dif)(p-p)</sub> | peak-to-peak<br>differential output<br>voltage |                                     | D                   | -            | 600              | -            | mV   |

| C <sub>o(L)</sub>        | Output load capacitance                        | between pins GND and MDS_N or MDS_P | D                   | -            | -                | 10           | pF   |

| Cl                       | Input capacitance                              | between pins GND and MDS_N or MDS_P | D                   | -            | 0.3              | -            | pF   |

#### Table 5. Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD} = 1.7 \text{ V to } 1.9 \text{ V}; V_{DDA(3V3)} = 3.13 \text{ V to } 3.47 \text{ V}; \text{ AGND and GND are shorted together}; T_{amb} = -40 ^{\circ}\text{C to} +85 ^{\circ}\text{C}; \text{ typical values measured at } V_{DDA(1V8)} = V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = +25 ^{\circ}\text{C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA}; \text{ maximum sample rate; PLL off unless otherwise specified.}$

| Symbol                     | Parameter                           | Conditions                                               | Test <sup>[1]</sup> | Min  | Тур   | Max                   | Unit   |

|----------------------------|-------------------------------------|----------------------------------------------------------|---------------------|------|-------|-----------------------|--------|

| Analog outpu               | ts (IOUTAP, IOUTAN, IO              | UTBP, IOUTBN)                                            |                     |      |       |                       |        |

| I <sub>O(fs)</sub>         | full-scale output<br>current        | register value = 00h<br>(see Table 13 and Table 14)      | D                   | -    | 1.6   | -                     | mA     |

|                            |                                     | register = default value<br>(see Table 13 and Table 14)  |                     | -    | 20    | -                     | mA     |

| V <sub>O</sub>             | output voltage                      | compliance range                                         | D                   | 1.8  | -     | V <sub>DDA(3V3)</sub> | V      |

| Ro                         | output resistance                   |                                                          | D                   | -    | 250   | -                     | kΩ     |

| Co                         | output capacitance                  |                                                          | D                   | -    | 3     | -                     | pF     |

| $\Delta E_O$               | offset error variation              |                                                          | С                   | -    | 6     | -                     | ppm/°C |

| $\Delta E_{G}$             | gain error variation                |                                                          | С                   | -    | 18    | -                     | ppm/°C |

| Reference vo               | tage output (GAPOUT)                |                                                          |                     |      |       |                       |        |

| V <sub>O(ref)</sub>        | reference output<br>voltage         |                                                          | С                   | 1.24 | 1.29  | 1.34                  | V      |

| I <sub>O(ref)</sub>        | reference output<br>current         | external voltage 1.2 V                                   | С                   | -    | 40    | -                     | μA     |

| $\Delta V_{O(\text{ref})}$ | reference output voltage variation  |                                                          | С                   | -    | 117   | -                     | ppm/°C |

| Analog auxilia             | ary outputs (AUXAP, AU              | XAN, AUXBP and AUXBN)                                    |                     |      |       |                       |        |

| I <sub>O(aux)</sub>        | auxiliary output current            | differential outputs                                     | I                   | -    | 2.2   | -                     | mA     |

| V <sub>O(aux)</sub>        | auxiliary output<br>voltage         | compliance range                                         | D                   | 0    | -     | 2                     | V      |

| N <sub>DAC(aux)</sub> mono | auxiliary DAC<br>monotonicity       | guaranteed                                               | D                   | -    | 10    | -                     | bits   |

| Input timing (             | Vin_p/Vin_n)                        |                                                          |                     |      |       |                       |        |

| f <sub>data</sub>          | data rate                           | 2× interpolation                                         | D                   | -    | -     | 312.5                 | Msps   |

|                            |                                     | 4× interpolation                                         | D                   | -    | -     | 162.5                 | Msps   |

|                            |                                     | 8× interpolation                                         | D                   | -    | -     | 81.25                 | Msps   |

| f <sub>bit</sub>           | bit rate                            | serial input                                             | D                   | 0.7  | -     | 3.125                 | Gbps   |

| Output timing              | (IOUTAP, IOUTAN, IOU                | TBP, IOUTBN)                                             |                     |      |       |                       |        |

| f <sub>s</sub>             | sampling rate                       |                                                          | D                   | -    | -     | 650                   | Msps   |

| ts                         | settling time                       | up to 0.5 LSB                                            | D                   | -    | 20    | -                     | ns     |

| NCO frequence              | cy range; f <sub>s</sub> = 650 Msps |                                                          |                     |      |       |                       |        |

| f <sub>NCO</sub>           | NCO frequency                       | register value = 00000000h<br>(see Table 21 to Table 24) | D                   | -    | 0     | -                     | MHz    |

|                            |                                     | register value = FFFFFFFh<br>(see Table 21 to Table 24)  | D                   | -    | 650   | -                     | MHz    |

| f <sub>step</sub>          | step frequency                      |                                                          | D                   | -    | 0.151 | -                     | Hz     |

|                            | CO frequency range; fs              | = 650 Msps                                               |                     |      |       |                       |        |

| f <sub>NCO</sub>           | NCO frequency                       | reg value = 00000000h<br>(see Table 21 to Table 24)      | D                   | -    | 0     | -                     | MHz    |

|                            |                                     | reg value = F8000000h<br>(see Table 21 to Table 24)      | D                   | -    | 630   | -                     | MHz    |

#### Table 5. Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD} = 1.7 \text{ V to } 1.9 \text{ V}; V_{DDA(3V3)} = 3.13 \text{ V to } 3.47 \text{ V}; \text{ AGND and GND are shorted together}; T_{amb} = -40 ^{\circ}\text{C to} +85 ^{\circ}\text{C}; \text{ typical values measured at } V_{DDA(1V8)} = V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = +25 ^{\circ}\text{C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA}; \text{ maximum sample rate; PLL off unless otherwise specified.}$

| Symbol            | Parameter                                              | Conditions                                                                                                                                                                | Test <sup>[1]</sup> | Min   | Тур  | Max | Unit |

|-------------------|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|------|-----|------|

| f <sub>step</sub> | step frequency                                         |                                                                                                                                                                           | D                   | -     | 20.3 | -   | MHz  |

| Dynamic perf      | ormances                                               |                                                                                                                                                                           |                     |       |      |     |      |

| SFDR              | spurious-free dynamic<br>range                         | $f_{data} = 80 \text{ Msps};$<br>$f_s = 640 \text{ Msps}; \times 8;$<br>BW = $f_{data}$ / 2; PLL on                                                                       |                     |       |      |     |      |

|                   |                                                        | f <sub>o</sub> = 4 MHz at –1 dBFS                                                                                                                                         | С                   | -     | 77   | -   | dBc  |

|                   |                                                        | $f_{data} = 160 \text{ Msps};$<br>$f_s = 640 \text{ Msps}; \times 4;$<br>BW = $f_{data} / 2$                                                                              |                     |       |      |     |      |

|                   |                                                        | f <sub>o</sub> = 19 MHz at –1 dBFS                                                                                                                                        | С                   | -     | 74   | -   | dBc  |

|                   |                                                        | $\begin{array}{l} f_{data} = 312.5 \text{ Msps}; \\ f_s = 625 \text{ Msps}; \ \times 2; \\ \text{BW} = f_{data} \ / \ 2 \end{array}$                                      |                     |       |      |     |      |

|                   |                                                        | $f_o$ = 19 MHz at –1 dBFS                                                                                                                                                 | I                   | -     | 75   | -   | dBc  |

| sp                | restricted bandwidth<br>spurious-free dynamic<br>range | $\begin{array}{l} f_{s} = 640 \text{ Msps;} \\ 4\times \text{ interpolation;} \\ f_{o} = 133 \text{ MHz at } -1 \text{ dBFS;} \\ \text{BW} = 100 \text{ MHz} \end{array}$ | I                   | -     | 81   | -   | dBc  |

|                   |                                                        | $f_s = 640 \text{ Msps};$<br>4× interpolation;<br>$f_o = 133 \text{ MHz at } -1 \text{ dBFS};$<br>BW = 20 Mhz                                                             | С                   | -     | 84   | -   | dBc  |

| IMD3              | third-order<br>intermodulation<br>distortion           | $\begin{array}{l} f_{o1} = 95 \text{ MHz}; \ f_{o2} = 97 \text{ MHz}; \\ f_s = 640 \text{ Msps}; \\ 4 \times \text{ interpolation} \end{array}$                           | С                   | [7] _ | 81   |     | dBc  |

|                   |                                                        | $f_{o1} = 153.1 \text{ MHz};$<br>$f_{o2} = 154.1 \text{ MHz};$<br>$f_{s} = 640 \text{ Msps};$<br>$4 \times \text{ interpolation}$                                         | I                   | [7] _ | 77   | -   | dBc  |

|                   |                                                        | $f_{o1}$ = 137 MHz;<br>$f_{o2}$ = 143 MHz;<br>$f_{s}$ = 640 Msps;<br>$4 \times$ interpolation                                                                             | С                   | [7] _ | 80   | -   | dBc  |

| ACPR              | adjacent channel<br>power ratio                        | NCO on; $4 \times$ interpolation;<br>$f_s = 640$ Msps; $f_o = 96$ MHz                                                                                                     |                     |       |      |     |      |

|                   |                                                        | 1 carrier; BW = 5 MHz                                                                                                                                                     | С                   | -     | 67   | -   | dBc  |

|                   |                                                        | 2 carriers; BW = 10 MHz                                                                                                                                                   | С                   | -     | 64   | -   | dBc  |

|                   |                                                        | 4 carriers; BW = 20 MHz                                                                                                                                                   | С                   | -     | 60   | -   | dBc  |

|                   |                                                        | NCO on; $4 \times$ interpolation;<br>f <sub>s</sub> = 640 Msps; f <sub>o</sub> = 133 MHz                                                                                  |                     |       |      |     |      |

|                   |                                                        | 1 carrier; BW = 5 MHz                                                                                                                                                     | С                   | -     | 67   | -   | dBc  |

|                   |                                                        | 2 carriers; BW = 10 MHz                                                                                                                                                   | С                   | -     | 64   | -   | dBc  |

|                   |                                                        | 4 carriers; BW = 20 MHz                                                                                                                                                   | С                   | -     | 59   | -   | dBc  |

#### Table 5. Characteristics ...continued

$V_{DDA(1V8)} = V_{DDD} = 1.7 \text{ V to } 1.9 \text{ V}; V_{DDA(3V3)} = 3.13 \text{ V to } 3.47 \text{ V}; \text{ AGND and GND are shorted together}; T_{amb} = -40 ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; typical values measured at  $V_{DDA(1V8)} = V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V}; T_{amb} = +25 ^{\circ}\text{C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA};$  maximum sample rate; PLL off unless otherwise specified.

| Symbol | Parameter              | Conditions                                                          | Test <sup>[1]</sup> | Min | Тур  | Max | Unit   |

|--------|------------------------|---------------------------------------------------------------------|---------------------|-----|------|-----|--------|

| NSD    | noise spectral density | $f_s = 640$ Msps;<br>4× interpolation;<br>$f_o = 133$ MHz at 0 dBFS | I                   | -   | -145 | -   | dBm/Hz |

[1] D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

- [2] Delay between the deassertion of bits FORCE\_RESET\_FCLK and FORCE\_RESET\_DCLK and the deassertion of the sync signal. It reflects the delay required by DAC1008D650 to lock to a JESD204A stream. It supposes that the TX is already transmitting K28.5 characters in error-free conditions.

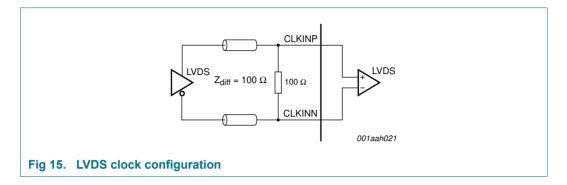

- [3] CLKINP/CLKINN inputs are at differential LVDS levels. An external termination resistor with a value of between 80  $\Omega$  and 120  $\Omega$  (see Figure 15) should be connected across the pins.

- [4] |V<sub>gpd</sub>| represents the ground potential difference voltage. This is the voltage that results from current flowing through the finite resistance and the inductance between the receiver and the driver circuit ground voltage.

- [5] Vin\_p and Vin\_n inputs are differential CML inputs. They are terminated internally to  $V_{tt}$  via 50  $\Omega$  (see Figure 4).

- [6] SYNC\_OUTP/SYNC\_OUTN outputs are differential LVDS outputs. They must be terminated by a resistor with a value of between 80  $\Omega$  and 120  $\Omega$ .

- [7] IMD3 rejection with -6 dBFS/tone.

# **10.** Application information

# **10.1 General description**

The DAC1008D650 is a dual 10-bit DAC operating up to 650 Msps. With a maximum input data rate of up to 312.5 Msps and a maximum output sampling rate of 650 Msps, the DAC1008D650 allows more flexibility for wide bandwidth and multi-carrier systems. Combined with its quadrature modulator and 32-bit NCO, the DAC1008D650 simplifies the frequency selection of the system. This is also possible because of the  $2\times$ ,  $4\times$  or  $8\times$  interpolation filters which remove undesired images.

DAC1008D650 supports the following JESD204A key features:

- 10-bit/8-bit decoding

- Code group synchronization

- · inter-lane alignment

- 1 + x<sup>14</sup> + x<sup>15</sup> scrambling polynomial

- Character replacement

- TX/RX synchronization management via SYNC signals

- Multiple Converter Device Alignment-Multiple Lanes (MCDA-ML) device

DAC1008D650 can be interfaced with any logic device that features high-speed SERDES functionality. This macro is now widely available in FPGA from different vendors. Standalone SERDES ICs can also be used.

To enhance the intrinsic board layout simplification of the JESD204A standard, IDT includes polarity swapping for each of the lanes and additionally offers lane swapping. Each physical lane can be configured logically as lane0, lane1, lane2 or lane3.

This device is MCDA-ML compliant and offers inter-lane alignment between several devices. Samples alignment between devices is maintained up to output level because of an IDT proprietary mechanism. One device is configured as the master and all the others are configured as slaves. These will automatically align their output samples to the master ones. Therefore, a system with several DAC1008D650s can produce data with a guaranteed alignment of less than 1 DAC output clock period.

Each DAC generates two complementary current outputs on pins IOUTAP/IOUTAN and IOUTBP/IOUTBN. This provides a full-scale output current of up to 20 mA. An internal reference is available for the reference current which is externally adjustable using pin VIRES.

The DAC1008D650 must be configured before operating. Therefore, it features an SPI slave interface to access internal registers. Some of these registers also provide information about the JESD204A interface status.

The DAC1008D650 requires supplies of both 3.3 V and 1.8 V. The 1.8 V supply has separate digital and analog power supply pins. The clock input is LVDS compliant.

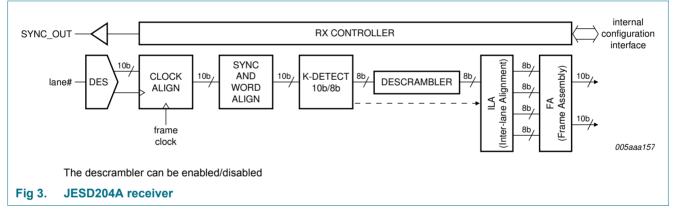

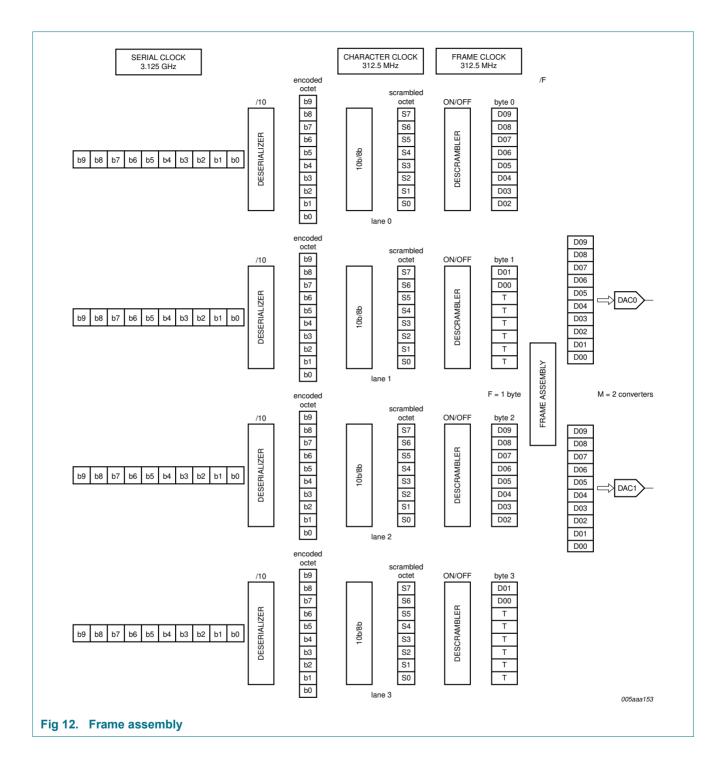

# 10.2 JESD204A receiver

The JEDEC204A defines the following parameters:

L is the number of lanes per link

M is the number of converters per device

F is the number of bytes per frame clock period

The DAC1008D650 supports both LMF = 421 and LMF = 211. The current setting is configurable via the SPI registers interface.

The complete Digital Layer Processing (DLP) adds a variable delay on each lane path. This is mainly because of the inter-lane alignment.

#### Table 6. Digital Layer Processing Latency

| Symbol         | Parameter  | Conditions                        | Test <sup>[1]</sup> | Min | Тур | Мах | Unit                 |

|----------------|------------|-----------------------------------|---------------------|-----|-----|-----|----------------------|

| t <sub>d</sub> | delay time | digital layer processing<br>delay | D                   | 13  | -   | 28  | cycle <sup>[2]</sup> |

- [1] D = guaranteed by design.

- [2] Frame clock cycle.

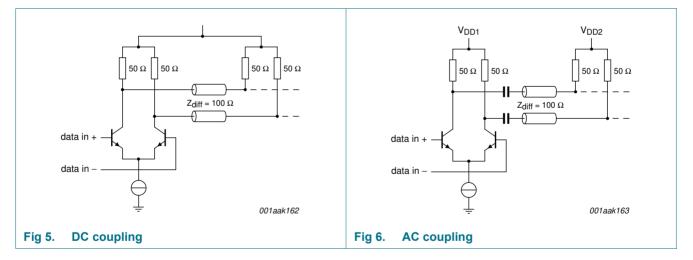

# 10.2.1 Lane input

Each lane is CML compliant. It is terminated to a common voltage with an integrated 50  $\Omega$  resistor.

The common-mode voltage is programmable by the SET\_VCM\_VOLTAGE register as shown in Table 75 on page 55.

DC coupling is only possible if both the DAC and the transmitter have the same common-mode voltage. If this is not the case AC coupling is required.

The deserializer performs the incoming data clock recovery and also the serial-to-parallel conversion. Therefore, each lane includes its own PLL that must first lock.

The clock alignment module transfers the data from the regenerated clock to the frame clock domain. The frequency of both clocks is the same but the phase relationship between the clocks is unknown.

# 10.2.2 Sync and word align

As stated in JESD204A, the transmitter and the receiver first have to synchronize. This is achieved through SYNC\_OUT signals and a sync pattern (K28.5 symbol). The receiver (i.e. DAC1008D650) first drives its SYNC\_OUT outputs. The sync pattern is continuously sent until the receiver deasserts the SYNC\_OUT signal.

DAC1008D650 4

The lane processing makes use of the sync patterns to synchronize the datastream, determine the initial running disparity and extract the 10-bit word from the incoming datastream (word-alignment).

The SYNC\_OUT signal is also used during normal operation by the DAC1008D650 to request a link reinitialization. This occurs when the 10b/8b module loses synchronization.

The SYNC\_OUT signal conforms to LVDS signaling. Its common-mode voltage and its single-ended peak amplitude can be programmed using SET\_SYNC\_LEVEL bits in the SET\_SYNC registers (see Table 77 on page 55).

SYNC\_OUT is asynchronous with the frame clock. There is no timing specification with respect to the CLKINP and CLKINN inputs.

# 10.2.3 Comma detection and word align

This stage monitors the datastream for code characters (comma detection), decodes the words to bytes (octets) and performs optional character replacement as part of frame/lane alignment monitoring and correction. This module provides the required control signals to the RX-controller and ILA.

This module decodes the 10-bit words into 8-bit words (octets). The decoding table is specified in the IEEE 802.3-2005 specification. During decoding, the disparity is calculated according to the disparity rules mentioned in the same specification IEEE 802.3-2005. When the disparity counter is more than +2 or less than –2, an error will be generated.

The following comma symbols are detected during data transmission irrespective of the running disparity:

A flag is sent to the control interface to reflect detected commas in registers.

The following flags are also triggered according to the following definitions:

- VALID: a code group that is found in the column of the 10b/8b decoding tables according to the current running disparity.

- DISPARITY ERROR: The received code group exists in the 10b/8b decoding table, but is not found in the proper column according to the current running disparity.

- NOT-IN-TABLE (NIT) ERROR: The received code group is not found in the 10b/8b decoding table for either disparity.

- INVALID: a code group that either shows a disparity error or that does not exist in the 10b/8b decoding table.

DAC1008D650 supports character replacement whatever the state of the descrambler. When scrambling is not active, the received K28.3 /A/ or K28.7 /F/ will be replaced by the previous sample. When scrambling is active, the corresponding data octet D28.3 (0xC) or D28.7 (0xFC) will be used.

DAC1008D650 4

# 10.2.4 Descrambler

The descrambler is a 16-bit parallel self-synchronous descrambler based on the polynomial  $1 + x^{14} + x^{15}$ . This processing can be turned off.

# 10.2.5 Inter-lane alignment

This feature removes strict PCB design skew compensation between the lanes.

### 10.2.5.1 Single device operation

This module handles the alignment of the four data streams. Because of inter-lane skew and each PLL per lane concept, these alignment characters may be received at different times by the receivers. After the synchronization period, the lock signal will be HIGH. This enables the receipt of K28.3 /A/ characters.

The ILA\_CNTRL register's SEL\_ILA[1:0] bits select which K28.3 /A/ symbol triggers the initial lane alignment:"00" = 1st /A/ symbol, "01" = 2nd /A/ symbol, "10" = 3rd /A/ symbol, "11" = 4th /A/ symbol; Table 86 on page 61. When all receivers have received their first selected /A/, they start propagating the received data to the frame assembly module at the same point in time.

This module can compensate for up to  $\pm 7$  frame clock period misalignments between the lanes.

When initial lane alignment is not supported, the manual alignment mode can be used.

After the initial ILA sequence, the lane alignment monitoring starts. If the received user data contains a K28.3 /A/ symbol:

- its position is compared to the value of the alignment monitor counter

- if two successive K28.3 /A/ symbols have been received at a wrong position, a realignment takes place

- if the buffers are empty or overflow, this is indicated by the registers ILA\_BUF\_ERR\_LN0 to ILA\_BUF\_ERR\_LN3

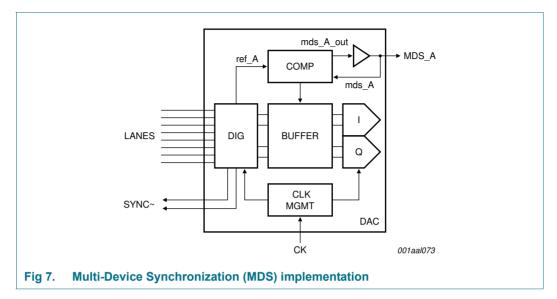

#### 10.2.5.2 Multi-device operation

DAC1008D650 implements a multi-device inter-lane alignment that guarantees a skew of less than one output period between them.

Two modes are available: master/slave and all slave. Both make use of the MDS\_P and MDS\_N pins.

### $2\times$ , $4\times$ or $8\times$ interpolating DAC with JESD204A

Each DAC device of the system generates its own reference (ref\_A in Figure 7).

If configured as a slave, an early-late comparator compares the internal reference with the external reference provided by the MDS pins. The comparator controls an internal buffer that is used to delay the samples.

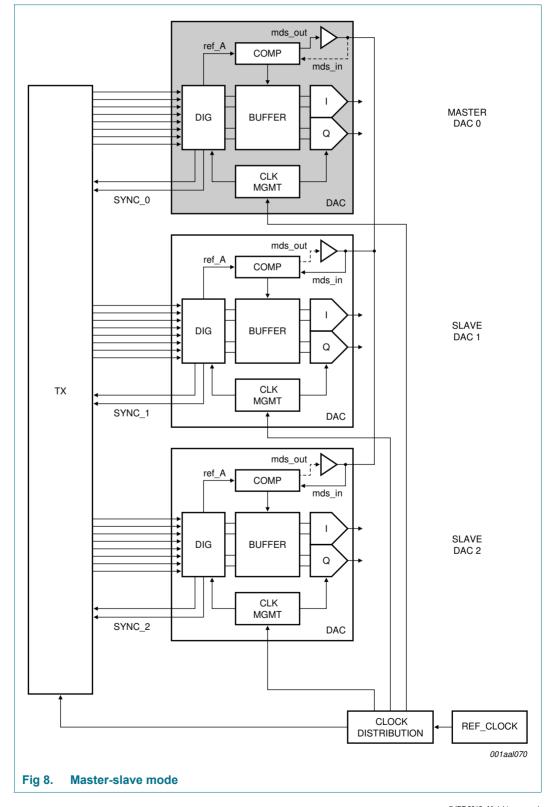

### 10.2.5.3 Master/slave mode

The external reference is provided by one of the DACs (the master DAC), which has to be configured to do this. The others are set to slave mode.

# 2×, 4× or 8× interpolating DAC with JESD204A

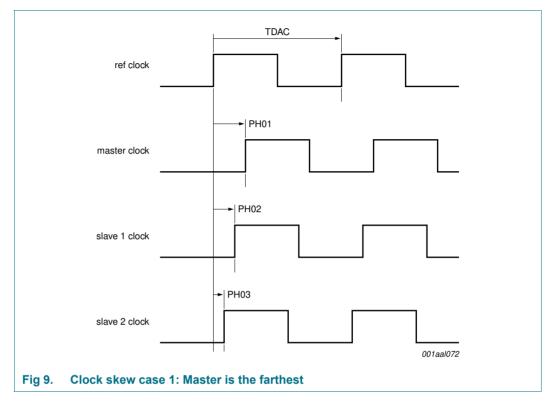

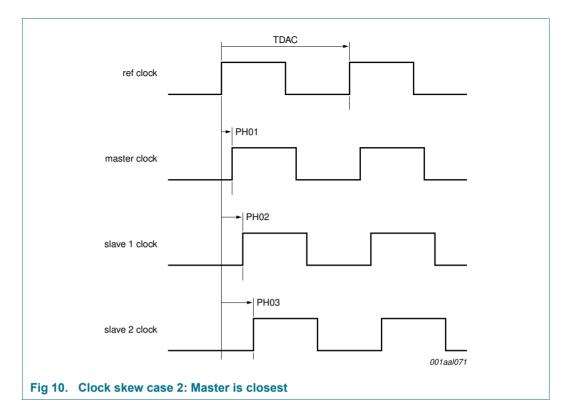

The MDS signal generated by the master DAC must reach all slaves within one DAC output clock period. This induces PCB layout constraints for the MDS signal and also for the clock distribution. Because trace lengths differ, the clock edges will reach each of the DACs at different times.

The worst case clock skew is given by  $\delta t_1$  = PH01 – PH03, where PH0x represents the sum of the trace delay and the clock skew at the output of the clock generator.

The maximum allowable trace delay for the MDS signal is given by  $\Delta t$  = TDAC –  $\delta t_1$ .

### 2×, 4× or 8× interpolating DAC with JESD204A

The worst case clock skew is given by  $\delta t_2$  = PH03 – PH01.

The minimum allowable trace delay for the MDS signal is given by  $\Delta t = \delta t_2$ .

In real applications, the master DAC can be anywhere and both conditions must be satisfied:  $\delta t_2 < \Delta t_{mds} < TDAC - \delta t_1$ .

Example:

- clock generator skew =  $\pm$  80 ps

- FR4 substrate ⇒ 15 cm/ns delay

- clock trace length difference = 3 cm and 4 cm

- Output sampling rate = 650 Msps

- $\Rightarrow$  200 ps + 80 ps <  $\Delta t_{mds}$  < 1538 ps (266 ps + 80 ps)

- $\Rightarrow$  280 ps <  $\Delta t_{mds}$  < 1192 ps

- $\Rightarrow$  4.2 cm < L<sub>mds</sub> < 17.8 cm

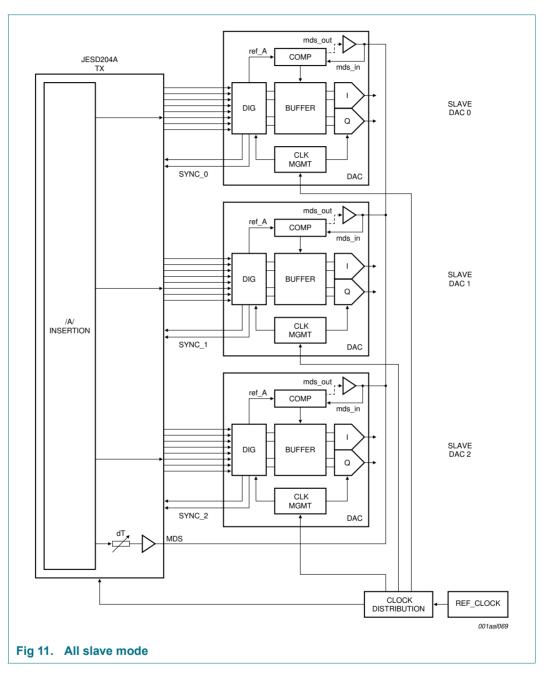

### 10.2.5.4 All slave mode

The external reference is provided by the JESD204A transmitter. All DACs are configured in slave mode.

The MDS signal is now driven from the transmitter. It is generated at the end of the inter-lane alignment phase (see the JESD204A standard for details).

The transmitter must also compensate for the DAC latency. Although the DAC has an internal samples delay line, it cannot handle large delays.

In this mode, PCB layout is also important. The following delay equation applies:  $\delta t < \Delta t_{mds} < TDAC - \delta t$ , where  $\delta t$  is the clock skew considered close to DAC pins.

# **10.2.6 Frame assembly**

DAC1008D650 supports only /F/ = 1, which means that every frame clock period carries one byte per lane. Frame assembly combines the octet of lane\_0 with the two MSB bits of lane\_1 and reassembles the original 10-bit sample. The same is done for lane\_2 and lane\_3. Tail bits are dropped.

The frame assembler also handles previously triggered errors.

If scrambling is enabled:

If a nit\_err (not-in-table error) or kout\_unexp (unexpected control character) occurs in lane\_0 and/or lane\_1, the previous 10-bit sample is repeated twice for I (lane\_0, lane 1). The same is done for Q (lane 2, lane 3).

If scrambling is disabled:

If a nit\_err (not-in-table error) or kout\_unexp (unexpected control character) occurs in lane\_0 and/or lane\_1, the previous 10-bit sample will be repeated once for I (lane\_0, lane\_1). The same is done for Q (lane\_2, lane\_3).

# Integrated Device Technology

# DAC1008D650

# $2\times$ , $4\times$ or $8\times$ interpolating DAC with JESD204A

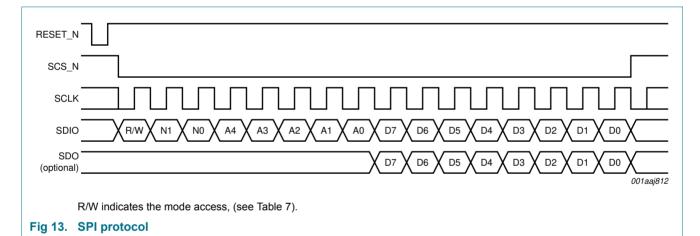

# **10.3 Serial Peripheral Interface (SPI)**

# **10.3.1 Protocol description**

The DAC1008D650 serial interface is a synchronous serial communication port allowing easy interfacing with many industry microprocessors. It provides access to the registers that define the operating modes of the chip in both Write mode and Read mode.

This interface can be configured as a 3-wire type (SDIO as bidirectional pin) or a 4-wire type (SDIO and SDO as unidirectional pin, input and output port respectively). In both configurations, SCLK acts as the serial clock and SCS\_N acts as the serial chip select bar.

Each read/write operation is sequenced by the SCS\_N signal and enabled by a LOW assertion to drive the chip with two bytes to five bytes, depending on the content of the instruction byte (see Table 8).

#### Table 7. Read or Write mode access description

| R/W | Description          |

|-----|----------------------|

| 0   | Write mode operation |

| 1   | Read mode operation  |

In Table 8 below, N1 and N0 indicate the number of bytes transferred after the instruction byte.

| •  |                             |                                       |

|----|-----------------------------|---------------------------------------|

| N0 | Number of bytes transferred |                                       |

| 0  | 1                           |                                       |

| 1  | 2                           |                                       |

| 0  | 3                           |                                       |

| 1  | 4                           |                                       |

|    | NO<br>0<br>1<br>0<br>1      | N0Number of bytes transferred01120314 |

A[4:0] indicates which register is being addressed. In the case of a multiple transfer, this address points to the first register to be accessed. The address is then internally decreased after each following data phase.

# 10.3.2 SPI timing description

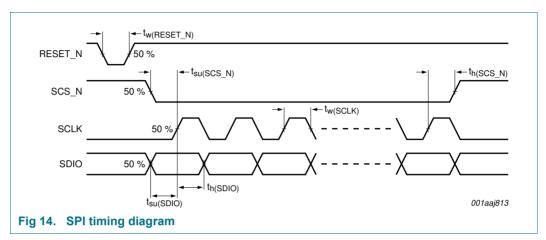

The SPI interface can operate at a frequency of up to 15 MHz. The SPI timing is shown in Figure 14.

The SPI timing characteristics are given in Table 9.

| $      f_{SCLK}  \begin{array}{ccccccccccccccccccccccccccccccccccc$                                                                                                                                                | Table J.                | or running characteristics |     |     |     |      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|----------------------------|-----|-----|-----|------|

| $t_{w(SCLK)}$ SCLK pulse width30ns $t_{su(SCS_N)}$ SCS_N set-up time20ns $t_{h(SCS_N)}$ SCS_N hold time20ns $t_{su(SDIO)}$ SDIO set-up time10ns $t_{h(SDIO)}$ SDIO hold time5ns                                    | Symbol                  | Parameter                  | Min | Тур | Max | Unit |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                             | f <sub>SCLK</sub>       | SCLK frequency             | -   | -   | 15  | MHz  |

| $\begin{array}{c c} t_{h(SCS_N)} & SCS_N \text{ hold time} & 20 & - & - & ns \\ t_{su(SDIO)} & SDIO \text{ set-up time} & 10 & - & - & ns \\ t_{h(SDIO)} & SDIO \text{ hold time} & 5 & - & - & ns \\ \end{array}$ | t <sub>w(SCLK)</sub>    | SCLK pulse width           | 30  | -   | -   | ns   |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                             | $t_{su(SCS_N)}$         | SCS_N set-up time          | 20  | -   | -   | ns   |

| $t_{h(SDIO)}$ SDIO hold time 5 ns                                                                                                                                                                                  | t <sub>h(SCS_N)</sub>   | SCS_N hold time            | 20  | -   | -   | ns   |

|                                                                                                                                                                                                                    | t <sub>su(SDIO)</sub>   | SDIO set-up time           | 10  | -   | -   | ns   |

| $t_{w(RESET_N)}$ RESET_N pulse width 30 ns                                                                                                                                                                         | t <sub>h(SDIO)</sub>    | SDIO hold time             | 5   | -   | -   | ns   |

|                                                                                                                                                                                                                    | t <sub>w(RESET_N)</sub> | RESET_N pulse width        | 30  | -   | -   | ns   |

#### Table 9. SPI timing characteristics

# 10.4 Clock input

The DAC1008D650 has one differential clock input, CLKINN/CLKINP.

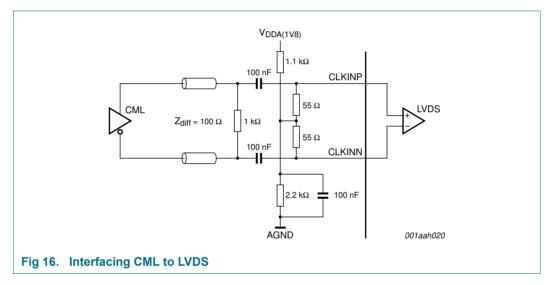

The DAC1008D650 can operate with a clock frequency up to 312.5 MHz or up to 650 MHz if the internal PLL is bypassed. The clock input can be LVDS (see Figure 15) but it can also be interfaced with CML (see Figure 16). Error free data transition from one internal clock domain to another one is handled by Clock Domain Interface (CDI) logic.

During the reset phase (RESET\_N asserted), the clock must be stable and running. This ensures a proper reset of the complete device.

The device has no embedded power-on-reset feature. Driving the RESET\_N pin to set the device to its default state is mandatory.