# imall

Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832 Email & Skype: info@chipsmall.com Web: www.chipsmall.com Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Dual 16-bit DAC, LVDS interface, up to 1 Gsps, x2, x4 and x8 interpolating

Rev. 4 — 12 December 2012

**Product data sheet**

### 1. General description

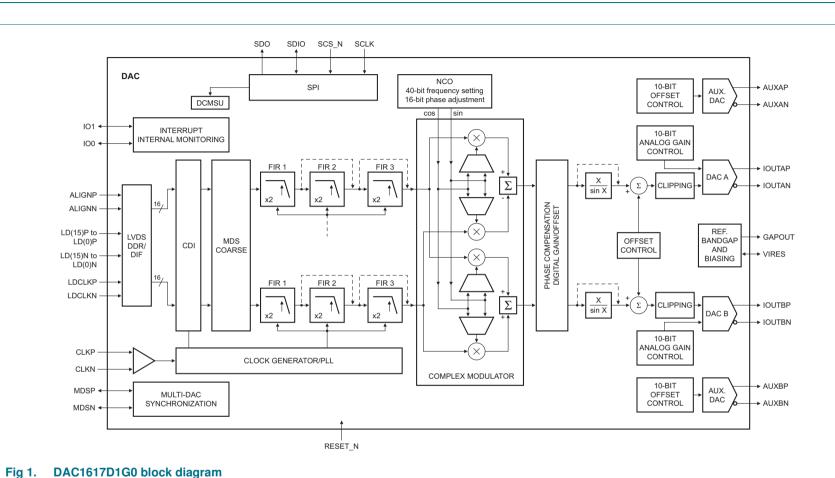

The DAC1617D1G0 is a high-speed 16-bit dual channel Digital-to-Analog Converter (DAC) with selectable  $\times 2$ ,  $\times 4$  and  $\times 8$  interpolation filters. The device is optimized for multi-carrier and broadband wireless transmitters at sample rates of up to 1 Gsps. Supplied from a 3.3 V and a 1.8 V source, the DAC1617D1G0 integrates a differential scalable output current up to 34 mA.

The Serial Peripheral Interface (SPI) provides full control of the DAC1617D1G0.

The DAC1617D1G0 integrates a Low Voltage Differential Signaling (LVDS) Double Data Rate (DDR) receiver interface, with an on-chip 100  $\Omega$  termination. The LVDS DDR interface accepts a multiplex input data stream such as interleaved or folded. An internal LVDS input auto-calibration ensures the robustness and stability of the interface.

Digital on-chip modulation converts the complex I and Q inputs from baseband to IF. A 40-bit Numerically Controlled Oscillator (NCO) sets the mixer frequency. High resolution internal gain, phase and offset control provide outstanding image and Local Oscillator (LO) signal rejection at the system analog modulator output.

An inverse  $(\sin x) / x$  function ensures a controlled flatness 0.5 dB for high bandwidths at the DAC output.

Multiple device synchronization allows synchronization of the outputs of multiple DAC devices. MDS guarantees a maximum skew of one output clock period between several devices.

The DAC1617D1G0 includes a very low noise capacitor-free integrated Phase-Locked Loop (PLL) multiplier which generates a DAC clock rate from the LVDS clock rate.

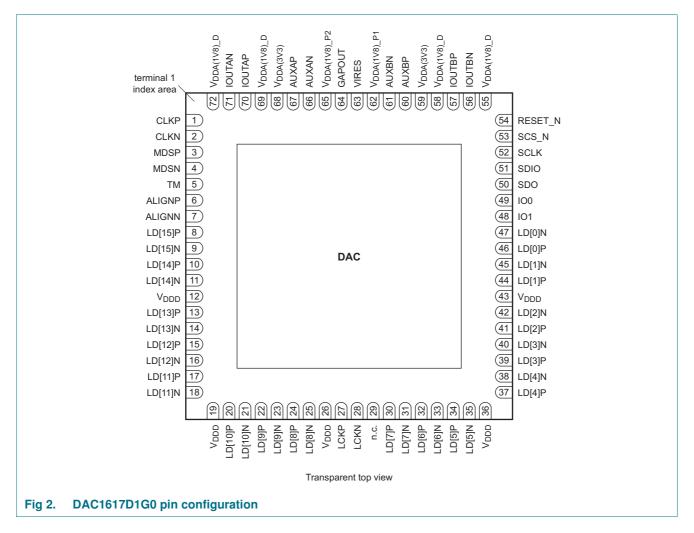

The DAC1617D1G0 is available in an HVQFN72 package (10 mm  $\times$  10 mm).

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### 2. Features and benefits

- Dual-channel 16-bit resolution

- 1 Gsps maximum update rate

- Selectable ×2, ×4 and ×8 interpolation filters

- Very low noise capacitor-free integrated External analog offset control Phase-Locked Loop (PLL)

- Embedded Numerically Controlled Oscillator (NCO) with 40-bit programmable frequency

- Embedded complex(I/Q) digital IF modulator

- 1.8 V and 3.3 V power supplies

- LVDS DDR compatible input interface with on-chip 100 Ω terminations

- LVDS DDR input clock up to 370 MHz

- LVDS or LVPECL compatible DAC clock

- Interleaved or folded I and Q data input 72 pins small form factor HVQFN mode

- Synchronization of multiple DAC devices

- 3-wire or 4-wire mode SPI interface

- Differential scalable output current from 8.1 mA to 34 mA

- (10-bit auxiliary DACs)

- High resolution internal digital gain and offset control to support high performance IQ-modulator image rejection

- Internal phase correction

- Inverse (sin x) / x function

- Power-down mode and Sleep mode; 5-bit NCO low-power mode

- On-chip 1.25 V reference

- Industrial temperature range -40 °C to +85 °C

- package

#### **Applications** 3.

- Wireless infrastructure: LTE, WiMAX, GSM, CDMA, WCDMA, TD-SCDMA

- Communications: LMDS/MMDS, point-to-point

- Direct Digital Synthesis (DDS)

- Broadband wireless systems

- Digital radio links

- Instrumentation

- Automated Test Equipment (ATE)

#### 4. Ordering information

#### Table 1. **Ordering information**

| Type number   | Package | Package                                                                                                          |          |  |  |  |  |  |  |  |

|---------------|---------|------------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

|               | Name    | Description                                                                                                      | Version  |  |  |  |  |  |  |  |

| DAC1617D1G0HN | HVQFN72 | plastic thermal enhanced very thin quad flat package; no leads; 72 terminals; body $10 \times 10 \times 0.85$ mm | SOT813-3 |  |  |  |  |  |  |  |

### **5.** Block diagram

Rev. 4 — 12 December 2012

© IDT 2012. All rights reserved. 3 of 78 Integrated Device Technology

DAC1617D1G0

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### 6. Pinning information

### 6.1 Pinning

### 6.2 Pin description

| Table 2. | Pin description | on                    |                                              |

|----------|-----------------|-----------------------|----------------------------------------------|

| Symbol   | Pin             | Type <mark>[1]</mark> | Description                                  |

| CLKP     | 1               | I                     | DAC clock positive input                     |

| CLKN     | 2               | I                     | DAC clock negative input                     |

| MDSP     | 3               | IO                    | multi-device synchronization positive signal |

| MDSN     | 4               | IO                    | multi-device synchronization negative signal |

| ТМ       | 5               | I                     | Test mode selection (connect to GND)         |

| ALIGNP   | 6               | I                     | positive input for data alignment            |

| ALIGNN   | 7               | I                     | negative input for data alignment            |

| LD[15]P  | 8               | I                     | LVDS positive input bit 15 <sup>[2]</sup>    |

| LD[15]N  | 9               | I                     | LVDS negative input bit 15 <sup>[2]</sup>    |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

| Table 2.         | Pin description continued |                     |                                           |  |  |

|------------------|---------------------------|---------------------|-------------------------------------------|--|--|

| Symbol           | Pin                       | Type <sup>[1]</sup> | Description                               |  |  |

| LD[14]P          | 10                        | I                   | LVDS positive input bit 14 <sup>[2]</sup> |  |  |

| LD[14]N          | 11                        | I                   | LVDS negative input bit 14 <sup>[2]</sup> |  |  |

| V <sub>DDD</sub> | 12                        | Р                   | digital power supply                      |  |  |

| LD[13]P          | 13                        | I                   | LVDS positive input bit 13 <sup>[2]</sup> |  |  |

| LD[13]N          | 14                        | I                   | LVDS negative input bit 13[2]             |  |  |

| LD[12]P          | 15                        | I                   | LVDS positive input bit 12 <sup>[2]</sup> |  |  |

| LD[12]N          | 16                        | I                   | LVDS negative input bit 12[2]             |  |  |

| LD[11]P          | 17                        | I                   | LVDS positive input bit 11 <sup>[2]</sup> |  |  |

| LD[11]N          | 18                        | I                   | LVDS negative input bit 11 <sup>[2]</sup> |  |  |

| V <sub>DDD</sub> | 19                        | Р                   | digital power supply                      |  |  |

| LD[10]P          | 20                        | I                   | LVDS positive input bit 10 <sup>[2]</sup> |  |  |

| LD[10]N          | 21                        | I                   | LVDS negative input bit 10 <sup>[2]</sup> |  |  |

| LD[9]P           | 22                        | I                   | LVDS positive input bit 9 <sup>[2]</sup>  |  |  |

| LD[9]N           | 23                        | I                   | LVDS negative input bit 9 <sup>[2]</sup>  |  |  |

| LD[8]P           | 24                        | I                   | LVDS positive input bit 8 <sup>[2]</sup>  |  |  |

| LD[8]N           | 25                        | I                   | LVDS negative input bit 8 <sup>[2]</sup>  |  |  |

| V <sub>DDD</sub> | 26                        | Р                   | digital power supply                      |  |  |

| LCKP             | 27                        | I                   | LVDS positive data clock input            |  |  |

| LCKN             | 28                        | I                   | LVDS negative data clock input            |  |  |

| n.c.             | 29                        | G                   | not connected                             |  |  |

| LD[7]P           | 30                        | I                   | LVDS positive input bit 7 <sup>[2]</sup>  |  |  |

| LD[7]N           | 31                        | I                   | LVDS negative input bit 7 <sup>[2]</sup>  |  |  |

| LD[6]P           | 32                        | I                   | LVDS positive input bit 6 <sup>[2]</sup>  |  |  |

| LD[6]N           | 33                        | I                   | LVDS negative input bit 6 <sup>[2]</sup>  |  |  |

| LD[5]P           | 34                        | I                   | LVDS positive input bit 5 <sup>[2]</sup>  |  |  |

| LD[5]N           | 35                        | I                   | LVDS negative input bit 5 <sup>[2]</sup>  |  |  |

| V <sub>DDD</sub> | 36                        | Р                   | digital power supply                      |  |  |

| LD[4]P           | 37                        | I                   | LVDS positive input bit 4 <sup>[2]</sup>  |  |  |

| LD[4]N           | 38                        | I                   | LVDS negative input bit 4 <sup>[2]</sup>  |  |  |

| LD[3]P           | 39                        | I                   | LVDS positive input bit 3 <sup>[2]</sup>  |  |  |

| LD[3]N           | 40                        | I                   | LVDS negative input bit 3 <sup>[2]</sup>  |  |  |

| LD[2]P           | 41                        | I                   | LVDS positive input bit 2 <sup>[2]</sup>  |  |  |

| LD[2]N           | 42                        | I                   | LVDS negative input bit 2 <sup>[2]</sup>  |  |  |

| V <sub>DDD</sub> | 43                        | Р                   | digital power supply                      |  |  |

| LD[1]P           | 44                        | I                   | LVDS positive input bit 1 <sup>[2]</sup>  |  |  |

| LD[1]N           | 45                        | I                   | LVDS negative input bit 1 <sup>[2]</sup>  |  |  |

| LD[0]P           | 46                        | I                   | LVDS positive input bit 0 <sup>[2]</sup>  |  |  |

| LD[0]N           | 47                        | I                   | LVDS negative input bit 0 <sup>[2]</sup>  |  |  |

| IO1              | 48                        | IO                  | IO port bit 1                             |  |  |

| IO0              | 49                        | IO                  | IO port bit 0                             |  |  |

| SDO              | 50                        | 0                   | SPI data output                           |  |  |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

| Symbol                    | Pin | Type <sup>[1]</sup> | Description                                  |

|---------------------------|-----|---------------------|----------------------------------------------|

| SDIO                      | 51  | IO                  | SPI data input/output                        |

| SCLK                      | 52  | I                   | SPI clock                                    |

| SCS_N                     | 53  | I                   | SPI chip select (active LOW)                 |

| RESET_N                   | 54  | I                   | general reset (active LOW)                   |

| V <sub>DDA(1V8)</sub> _D  | 55  | Р                   | 1.8 V analog power supply (DAC core)         |

| IOUTBN                    | 56  | 0                   | complementary DAC B output current           |

| IOUTBP                    | 57  | 0                   | DAC B output current                         |

| V <sub>DDA(1V8)</sub> _D  | 58  | Р                   | 1.8 V analog power supply (DAC core)         |

| V <sub>DDA(3V3)</sub>     | 59  | Р                   | 3.3 V analog power supply                    |

| AUXBP                     | 60  | 0                   | auxiliary DAC B output current               |

| AUXBN                     | 61  | 0                   | complementary auxiliary DAC B output current |

| V <sub>DDA(1V8)</sub> _P1 | 62  | Р                   | 1.8 V analog power supply (PLL)              |

| VIRES                     | 63  | IO                  | DAC biasing resistor                         |

| GAPOUT                    | 64  | IO                  | band gap input/output voltage                |

| V <sub>DDA(1V8)</sub> P2  | 65  | Р                   | 1.8 V analog power supply (PLL)              |

| AUXAN                     | 66  | 0                   | complementary auxiliary DAC A output current |

| AUXAP                     | 67  | 0                   | auxiliary DAC A output current               |

| V <sub>DDA(3V3)</sub>     | 68  | Р                   | 3.3 V analog power supply                    |

| V <sub>DDA1V8_D</sub>     | 69  | Р                   | 1.8 V analog power supply (DAC core)         |

| IOUTAP                    | 70  | 0                   | DAC A output current                         |

| IOUTAN                    | 71  | 0                   | complementary DAC A output current           |

| V <sub>DDA(1V8)_D</sub>   | 72  | Р                   | 1.8 V analog power supply (DAC core)         |

| GND                       | Н   | G                   | ground (exposed die pad)                     |

[1] P: power supply; G: ground; I: input; O: output.

[2] The LVDS input data bus order can be reversed and each element can be swapped between P and N using dedicated registers (see <u>Table 60</u>).

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### 7. Limiting values

| Table 3.<br>In accorda | Table 3.         Limiting values           In accordance with the Absolute Maximum Rating System (IEC 60134). |                                                                                               |          |      |      |  |  |  |  |  |

|------------------------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------|------|------|--|--|--|--|--|

| Symbol                 | Parameter                                                                                                     | Conditions                                                                                    | Min      | Max  | Unit |  |  |  |  |  |

| V <sub>DDA(3V3)</sub>  | analog supply voltage<br>(3.3 V)                                                                              |                                                                                               | -0.5     | +4.6 | V    |  |  |  |  |  |

| V <sub>DDD</sub>       | digital supply voltage                                                                                        |                                                                                               | -0.5     | +2.5 | V    |  |  |  |  |  |

| V <sub>DDA(1V8)</sub>  | analog supply voltage<br>(1.8 V)                                                                              | Ľ                                                                                             | <u> </u> | +2.5 | V    |  |  |  |  |  |

| VI                     | input voltage                                                                                                 | input pins referenced to GND                                                                  | -0.5     | +2.5 | V    |  |  |  |  |  |

| Vo                     | output voltage                                                                                                | pins IOUTAP, IOUTAN,<br>IOUTBP, IOUTBN, AUXAP,<br>AUXAN, AUXBP and AUXBN<br>referenced to GND | -0.5     | +4.6 | V    |  |  |  |  |  |

| T <sub>stg</sub>       | storage temperature                                                                                           |                                                                                               | -55      | +150 | °C   |  |  |  |  |  |

| T <sub>amb</sub>       | ambient temperature                                                                                           |                                                                                               | -40      | +85  | °C   |  |  |  |  |  |

| Tj                     | junction temperature                                                                                          |                                                                                               | -40      | +125 | °C   |  |  |  |  |  |

|                        |                                                                                                               |                                                                                               |          |      |      |  |  |  |  |  |

[1] Connect the analog 1.8 V power supply to pins VDDA1V8\_D, VDDA1V8\_P1, and VDDA1V8\_P2.

### 8. Thermal characteristics

| Table 4.             | Thermal characteristics                     |            |         |      |

|----------------------|---------------------------------------------|------------|---------|------|

| Symbol               | Parameter                                   | Conditions | Тур     | Unit |

| R <sub>th(j-a)</sub> | thermal resistance from junction to ambient |            | 16.2    | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | [1] 6.7 | K/W  |

[1] Value for six-layer board in still air with a minimum of 49 thermal vias.

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### 9. Characteristics

#### Table 5. Characteristics

| Symbol                 | Parameter                                  | Conditions                                                               | Test<br>[1] |     | Min         | Тур         | Max  | Unit |

|------------------------|--------------------------------------------|--------------------------------------------------------------------------|-------------|-----|-------------|-------------|------|------|

| V <sub>DDA(3V3)</sub>  | analog supply<br>voltage (3.3 V)           |                                                                          | С           |     | 3.15        | 3.3         | 3.45 | V    |

| V <sub>DDD</sub>       | digital supply<br>voltage                  |                                                                          | С           |     | 1.7         | 1.8         | 1.9  | V    |

| V <sub>DDA(1V8)</sub>  | analog supply<br>voltage (1.8 V)           |                                                                          | С           | [2] | 1.7         | 1.8         | 1.9  | V    |

| I <sub>DDA(3V3)</sub>  | analog supply current (3.3 V)              | Auxiliary DAC on                                                         | С           |     | 51          | 55          | 59   | mA   |

| I <sub>DDD</sub>       | digital supply current (1.8 V)             | f <sub>s</sub> = 983.04 67;<br>×4 interpolation; no NCO;<br>MDS off      | С           |     | 475         | 525         | 585  | mA   |

|                        |                                            | f <sub>s</sub> = 620 Msps;<br>×2 interpolation; NCO on;<br>no MDS        | С           |     | 400         | 450         | 500  | mA   |

| I <sub>DDA(1V8)</sub>  | analog supply                              | f <sub>s</sub> = 983.04 Msps; 1 V (p-p)                                  | С           | [2] | 207         | 218         | 230  | mA   |

|                        | current (1.8 V)                            | f <sub>s</sub> = 620 Msps; 1 V (p-p)                                     | С           |     | 207         | 218         | 230  | mA   |

| P <sub>tot</sub>       | total power<br>dissipation                 | f <sub>s</sub> = 983.04 Msps;<br>×4 interpolation; NCO off;<br>MDS off   | С           |     | -           | 1580        | -    | mW   |

|                        |                                            | f <sub>s</sub> = 983.04 Msps;<br>×4 interpolation;<br>5-bit NCO; MDS off | С           |     | -           | 1500        | -    | mW   |

|                        |                                            | f <sub>s</sub> = 620 Msps;<br>×2 interpolation; 5-bit<br>NCO; MDS off    |             |     | -           | 1370        | -    | mW   |

|                        |                                            | power-down using SPI<br>register                                         | С           |     | -           | 63          | -    | mW   |

| <b>Clock input</b>     | s (pins CLKP, CLK                          | N)                                                                       |             |     |             |             |      |      |

| V <sub>i(clk)dif</sub> | differential clock<br>input voltage        | peak-to-peak                                                             | С           |     | 150         | -           | 1000 | mV   |

| R <sub>i</sub>         | input resistance                           |                                                                          | D           |     | -           | 200         | -    | kΩ   |

| Ci                     | input<br>capacitance                       |                                                                          | D           |     | -           | 1           | -    | pF   |

| Digital inpu           | ts (pins LD[15]P to                        | LD[0]P, LD[15]N to LD[0]N                                                | , LCKP      | an  | d LCKN, ALI | GNP and ALI | GNN) |      |

| Vi                     | input voltage                              | V <sub>gpd</sub>   < 50 mV <mark>⊡</mark>                                | С           |     | 825         | -           | 1575 | mV   |

| V <sub>idth</sub>      | input differential<br>threshold<br>voltage | V <sub>gpd</sub>   < 50 mV <mark></mark> ⊡                               | С           |     | -100        | -           | +100 | mV   |

| R <sub>i</sub>         | input resistance                           |                                                                          | D           |     | -           | 100         | -    | Ω    |

| Ci                     | input                                      |                                                                          | D           |     | -           | 0.8         | -    | pF   |

|                        | capacitance                                | pins LCKP and LCKN                                                       | D           |     | -           | 0.9         | -    | pF   |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### Table 5. Characteristics ... continued

| Symbol                   | Parameter                                      | Conditions                                                           | Test<br>[1] | Min                      | Тур  | Max                      | Unit             |

|--------------------------|------------------------------------------------|----------------------------------------------------------------------|-------------|--------------------------|------|--------------------------|------------------|

| Digital inpu             | ts/outputs (pins M                             | DSN, MDSP)                                                           |             |                          |      |                          |                  |

| V <sub>o(dif)(p-p)</sub> | peak-to-peak<br>differential<br>output voltage |                                                                      | С           | -                        | 500  | -                        | mV               |

| Ci                       | input<br>capacitance                           | between GND and pin<br>MDSN or MDSP                                  | D           | -                        | 0.6  | -                        | pF               |

| R <sub>i</sub>           | input resistance                               |                                                                      | D           | -                        | 100  | -                        | Ω                |

| Vi                       | input voltage                                  | V <sub>gpd</sub>   < 50 mV <mark>⊡</mark>                            | С           | 825                      | -    | 1575                     | mV               |

| V <sub>idth</sub>        | input differential<br>threshold<br>voltage     | V <sub>gpd</sub>   < 50 mV <mark>③</mark>                            | С           | -100                     | -    | +100                     | mV               |

| Digital inpu             | ts/outputs (pins SI                            | DO, SDIO, SCLK, SCS_N, R                                             | ESET_N      | , IO0, IO1)              |      |                          |                  |

| V <sub>IL</sub>          | LOW-level input voltage                        |                                                                      | С           | GND                      | -    | 0.3V <sub>DDD(1V8)</sub> | V                |

| V <sub>IH</sub>          | HIGH-level<br>input voltage                    |                                                                      | С           | 0.7V <sub>DDD(1V8)</sub> | -    | V <sub>DDD(1V8)</sub>    | V                |

| V <sub>OL</sub>          | LOW-level output voltage                       | pins IO0, IO1, SDO and SDIO                                          | С           | GND                      | -    | 0.1V <sub>DDD(1V8)</sub> | V                |

| V <sub>ОН</sub>          | HIGH-level<br>output voltage                   | pins IO0, IO1, SDO and SDIO                                          | С           | 0.9V <sub>DDD(1V8)</sub> | -    | V <sub>DDD(1V8)</sub>    | V                |

| lıL                      | LOW-level input<br>current                     | maximum VIL                                                          | I           | -10                      | -    | +10                      | μA               |

| IIH                      | HIGH-level<br>input current                    | maximum VIL                                                          | I           | -10                      | -    | +10                      | μA               |

| Ci                       | input<br>capacitance                           |                                                                      | D           | -                        | 2.2  | -                        | pF               |

| Analog outp              | outs (pins IOUTAP,                             | IOUTAN, IOUTBP, IOUTBN                                               | )           |                          |      |                          |                  |

| I <sub>bias</sub>        | bias current                                   | DC current                                                           | D           | -                        | 2.5  | -                        | mA               |

| I <sub>O(fs)</sub>       | full-scale output<br>current                   | controlled by the analog<br>GAIN registers<br>(see <u>Table 32</u> ) | D           | 8.1                      | -    | 34                       | mA               |

|                          |                                                | default value                                                        | D           | -                        | 20   | -                        | mA               |

| Vo                       | output voltage                                 | compliance range                                                     | D           | 2.3                      | -    | V <sub>DDA(3V3)</sub>    | V                |

| V <sub>O(cm)</sub>       | common-mode                                    | 1 V (p-p) DAC output                                                 | D           | -                        | 3    | -                        | V                |

|                          | output voltage                                 | 2 V (p-p) DAC output                                                 |             | -                        | 2.8  | -                        | V                |

| R <sub>o</sub>           | output<br>resistance                           |                                                                      | D           | -                        | 250  | -                        | kΩ               |

| C <sub>o</sub>           | output<br>capacitance                          | between pins OUTAN and<br>OUTBN and pins OUTBN<br>and OUTBP          | D           | -                        | 5    | -                        | pF               |

| Reference v              | voltage output (pin                            | GAPOUT)                                                              |             |                          |      |                          |                  |

| V <sub>O(ref)</sub>      | reference output<br>voltage                    | $T_{amb} = +25 \text{ °C}$                                           | I           | -                        | 1.22 | -                        | V                |

| DAC1617D1G0              |                                                |                                                                      |             |                          |      | © IDT 2012               | . All rights res |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### Table 5. Characteristics ...continued

| Symbol                 | Parameter                    | Conditions                                                                                                                                                    | Test<br>[1] | Min   | Тур | Мах | Unit |

|------------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-----|-----|------|

| I <sub>O(ref)</sub>    | reference output<br>current  | 1.25 V external voltage                                                                                                                                       | D           | -     | 40  | -   | μA   |

| Analog au              | xiliary outputs (pins        | S AUXAP, AUXAN, AUXBP                                                                                                                                         | and AUX     | (BN)  |     |     |      |

| I <sub>O(fs)</sub>     | full-scale output<br>current | auxiliary DAC A;<br>differential outputs                                                                                                                      | I           | -     | 3.1 | -   | mA   |

|                        |                              | auxiliary DAC B;<br>differential outputs                                                                                                                      | I           | -     | 3.1 | -   | mA   |

| V <sub>O(aux)</sub>    | auxiliary output<br>voltage  | compliance range                                                                                                                                              | D           | 0     | -   | 2.3 | V    |

| LVDS inpu              | t timing                     |                                                                                                                                                               |             |       |     |     |      |

| f <sub>data</sub>      | data rate                    | $\begin{array}{l} f_{s(max)} \text{ specification must} \\ \text{be respected} \\ (f_s = f_{data} \times \text{ interpolation} \\ \text{factor}) \end{array}$ | С           | -     | -   | 370 | MHz  |

| t <sub>sk(clk-D)</sub> | skew time from               | $f_{DATA} = 184.32 \text{ Mhz}$                                                                                                                               | С           | 800   | -   | 830 | ps   |

|                        | clock to data<br>input       | f <sub>DATA</sub> = 245.76 MHz                                                                                                                                | С           | 500   | -   | 675 | ps   |

|                        | input                        | $f_{DATA} = 307.2 \text{ MHz}$                                                                                                                                | С           | 300   | -   | 520 | ps   |

|                        |                              | $f_{DATA} = 368.64 \text{ MHz}$                                                                                                                               | С           | 150   | -   | 500 | ps   |

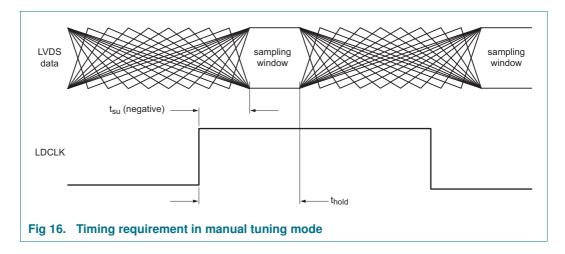

| t <sub>su</sub>        | set-up time                  | manual tuning mode<br>(see <u>Figure 16</u> ); depends<br>on LDCLK_DEL[3:0]                                                                                   |             |       |     |     |      |

|                        |                              | 0000                                                                                                                                                          | С           | -300  | -   | -   | ps   |

|                        |                              | 0001                                                                                                                                                          | С           | -365  | -   | -   | ps   |

|                        |                              | 0010                                                                                                                                                          | С           | -440  | -   | -   | ps   |

|                        |                              | 0011                                                                                                                                                          | С           | -520  | -   | -   | ps   |

|                        |                              | 0100                                                                                                                                                          | С           | -590  | -   | -   | ps   |

|                        |                              | 0101                                                                                                                                                          | С           | -675  | -   | -   | ps   |

|                        |                              | 0110                                                                                                                                                          | С           | -750  | -   | -   | ps   |

|                        |                              | 0111                                                                                                                                                          | С           | -830  | -   | -   | ps   |

|                        |                              | 1000                                                                                                                                                          | С           | -845  | -   | -   | ps   |

|                        |                              | 1001                                                                                                                                                          | С           | -845  | -   | -   | ps   |

|                        |                              | 1010                                                                                                                                                          | С           | -1000 | -   | -   | ps   |

|                        |                              | 1011                                                                                                                                                          | С           | -1100 | -   | -   | ps   |

|                        |                              | 1100                                                                                                                                                          | С           | -1220 | -   | -   | ps   |

|                        |                              | 1101                                                                                                                                                          | С           | -1290 | -   | -   | ps   |

|                        |                              | 1110                                                                                                                                                          | С           | -1360 | -   | -   | ps   |

|                        |                              | 1111                                                                                                                                                          | С           | -1450 | -   | -   | ps   |

|                        |                              |                                                                                                                                                               |             |       |     |     |      |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### Table 5. Characteristics ...continued

| Symbol              | Parameter          | Conditions                                                                   | Test<br>[1] | Min  | Тур        | Max  | Unit |

|---------------------|--------------------|------------------------------------------------------------------------------|-------------|------|------------|------|------|

| t <sub>hold</sub>   | hold time          | manual tuning mode<br>(see <u>Figure 15</u> ); depends<br>on LDCLK_DEL[3:0]: |             |      |            |      |      |

|                     |                    | 0000                                                                         | С           | 790  | -          | -    | ps   |

|                     |                    | 0001                                                                         | С           | 870  | -          | -    | ps   |

|                     |                    | 0010                                                                         | С           | 950  | -          | -    | ps   |

|                     |                    | 0011                                                                         | С           | 1055 | -          | -    | ps   |

|                     |                    | 0100                                                                         | С           | 1140 | -          | -    | ps   |

|                     |                    | 0101                                                                         | С           | 1230 | -          | -    | ps   |

|                     |                    | 0110                                                                         | С           | 1360 | -          | -    | ps   |

|                     |                    | 0111                                                                         | С           | 1460 | -          | -    | ps   |

|                     |                    | 1000                                                                         | С           | 1900 | -          | -    | ps   |

|                     |                    | 1001                                                                         | С           | 2075 | -          | -    | ps   |

|                     |                    | 1010                                                                         | С           | 2250 | -          | -    | ps   |

|                     |                    | 1011                                                                         | С           | 2400 | -          | -    | ps   |

|                     |                    | 1100                                                                         | С           | 2560 | -          | -    | ps   |

|                     |                    | 1101                                                                         | С           | 2740 | -          | -    | ps   |

|                     |                    | 1110                                                                         | С           | 2900 | -          | -    | ps   |

|                     |                    | 1111                                                                         | С           | 3000 | -          | -    | ps   |

| DAC outpo           | ut timing          |                                                                              |             |      |            |      |      |

| f <sub>s(max)</sub> | sampling rate      |                                                                              | С           | 1000 | -          | -    | Msps |

| t <sub>s</sub>      | settling time      | to $\pm$ 0.5 LSB                                                             | D           | -    | 20         | -    | ns   |

| Internal Pl         | L timing           |                                                                              |             |      |            |      |      |

| f <sub>s</sub>      | sampling rate      |                                                                              | D           | 50   | -          | 1000 | Msps |

| 40-bit NCC          | ) frequency range; | f <sub>s</sub> = 1000 Msps                                                   |             |      |            |      |      |

| f <sub>NCO</sub>    | NCO frequency      | two's complement coding                                                      |             |      |            |      |      |

|                     |                    | register value =<br>8000000000h                                              | D           | -    | -500       | -    | MHz  |

|                     |                    | register value =<br>FFFFFFFFFh                                               | D           | -    | -0.9095    | -    | mHz  |

|                     |                    | register value =<br>0000000000h                                              | D           | -    | 0          | -    | Hz   |

|                     |                    | register value =<br>0000000001h                                              | D           | -    | +0.9095    | -    | mHz  |

|                     |                    | register value =<br>7FFFFFFFFh                                               | D           | -    | +499.99909 | -    | MHz  |

| f <sub>step</sub>   | step frequency     |                                                                              | D           | -    | 0.9095     | -    | mHz  |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### Table 5. Characteristics ...continued

| Symbol              | Parameter                                    | Conditions                                                                                                                                                                                                                            | Test<br>[1] | Min | Тур     | Max | Unit |

|---------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|---------|-----|------|

| Low-power           | NCO frequency ra                             | nge; f <sub>s</sub> = 1000 MHz                                                                                                                                                                                                        |             |     |         |     |      |

| f <sub>NCO</sub>    | NCO frequency                                | two's complement coding                                                                                                                                                                                                               |             |     |         |     |      |

|                     |                                              | register value =<br>F8000000000h                                                                                                                                                                                                      | D           | -   | -500    | -   | MHz  |

|                     |                                              | register value =<br>F8000000000h                                                                                                                                                                                                      | D           | -   | -31.25  | -   | MHz  |

|                     |                                              | register value =<br>00000000000h                                                                                                                                                                                                      | D           | -   | 0       | -   | Hz   |

|                     |                                              | register value =<br>08000000000h                                                                                                                                                                                                      | D           | -   | +31.25  | -   | MHz  |

|                     |                                              | register value =<br>7FFFFFFFFh                                                                                                                                                                                                        | D           | -   | +468.75 | -   | MHz  |

| f <sub>step</sub>   | step frequency                               |                                                                                                                                                                                                                                       | D           | -   | 31.25   | -   | MHz  |

| Dynamic pe          | erformance                                   |                                                                                                                                                                                                                                       |             |     |         |     |      |

| SFDR                | spurious-free<br>dynamic range               | $f_{data} = 245.76 \text{ MHz};$<br>$f_s = 983.04 \text{ Msps};$<br>BW = $f_s / 2$                                                                                                                                                    |             |     |         |     |      |

|                     |                                              | $f_o = 20 \text{ MHz at} - 1 \text{ dBFS}$                                                                                                                                                                                            | I           | -   | 78      | -   | dBc  |

|                     |                                              | $f_{data} = 184.32 \text{ MHz};$<br>$f_{s} = 737.28 \text{ Msps};$<br>BW = $f_{s} / 2$                                                                                                                                                |             |     |         |     |      |

|                     |                                              | $f_0 = 20 \text{ MHz at} - 1 \text{ dBFS}$                                                                                                                                                                                            |             | -   | 78      | -   | dBc  |

| SFDR <sub>RBW</sub> | restricted<br>bandwidth<br>spurious-free     | $f_{data} = 245.76 \text{ MHz};$<br>$f_{s} = 983.04 \text{ Msps};$<br>$f_{o} = 150 \text{ MHz}$                                                                                                                                       |             | -   |         | -   | dBc  |

|                     | dynamic range                                | BW = 100 MHz                                                                                                                                                                                                                          |             | -   | 78      | -   | dBc  |

|                     |                                              | BW = 180 MHz                                                                                                                                                                                                                          |             | -   | 78      | -   | dBc  |

|                     | third-order<br>intermodulation<br>distortion | $\begin{array}{l} f_{data} = 245.76 \text{ MHz}; \\ f_{s} = 983.04 \text{ Msps}; \\ f_{o1} = 20 \text{ MHz}; \\ f_{o2} = 21 \text{ MHz}; \\ \times 4 \text{ interpolation}; \\ \text{output level} = -1 \text{ dBFS} \end{array}$     | С           | -   | 75      | -   | dBc  |

|                     |                                              | $\begin{array}{l} f_{data} = 245.76 \text{ MHz}; \\ f_{s} = 983.04 \text{ Msps}; \\ f_{o1} = 152 \text{ MHz}; \\ f_{o2} = 155.1 \text{ MHz}; \\ \times 4 \text{ interpolation}; \\ \text{output level} = -1 \text{ dBFS} \end{array}$ | I           | -   | 75      | -   | dBc  |

### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

#### Table 5. Characteristics ...continued

$V_{DDA(1V8)} = 1.8 \text{ V}; V_{DDD} = 1.8 \text{ V}; V_{DDA(3V3)} = 3.3 \text{ V};$  Typical values measured at  $T_{amb} = +25 \text{ °C}; R_L = 50 \Omega; I_{O(fs)} = 20 \text{ mA};$  maximum sample rate used; external PLL; no auxiliary DAC; no inverse sinus x/x; no output correction; output load condition defined in Figure 29; output level = 1 V (p-p).

| Symbol                 | Parameter                          | Conditions                                                                                                                                                                                                                                        | Test<br>[1] | Min | Тур  | Max | Unit   |

|------------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----|------|-----|--------|

| ACPR                   | adjacent<br>channel power<br>ratio | WCDMA pattern;<br>f <sub>s</sub> = 983.04 Msps;<br>×4 interpolation;<br>f <sub>NCO</sub> = 153.6 MHz                                                                                                                                              |             |     |      |     |        |

|                        |                                    | 1 carrier; BW = 5 MHz                                                                                                                                                                                                                             | С           | -   | 73   | -   | dBc    |

|                        |                                    | 2 carriers; BW = 10 MHz                                                                                                                                                                                                                           | С           | -   | 70   | -   | dBc    |

|                        |                                    | 4 carriers; BW = 20 MHz                                                                                                                                                                                                                           | С           | -   | 68   | -   | dBc    |

| $\alpha_{isol(ch-ch)}$ | isolation<br>between<br>channels   | $\begin{array}{l} f_{s} = 1228.8 \text{ Msps}; \\ \times 4 \text{ interpolation}; \\ f_{out} = 10 \text{ MHz}; \text{ NCO} = \text{off}; \\ \text{level} = 0.1 \text{ dBFS}; \text{ both} \\ \text{DAC channels enabled} \end{array}$             | С           | -   | 110  | -   | dBc    |

|                        |                                    | $\begin{array}{l} f_{s} = 1228.8 \mbox{ Msps}; \\ \times 4 \mbox{ interpolation}; \\ f_{out} = 83 \mbox{ MHz}; \mbox{ NCO} = off; \\ level = 0.1 \mbox{ dBFS}; \mbox{ both} \\ \mbox{ DAC channels enabled} \end{array}$                          | С           | -   | 95   | -   | dBc    |

|                        |                                    | $\begin{array}{l} f_s = 1228.8 \mbox{ Msps}; \\ \times 4 \mbox{ interpolation}; \\ f_{out} = 210 \mbox{ MHz}; \mbox{ NCO} = on; \\ level = 0.1 \mbox{ dBFS}; \mbox{ one DAC} \\ channel enabled; \mbox{ one DAC} \\ channel disabled \end{array}$ | С           | -   | 81   | -   | dBc    |

| NSD                    | noise spectral<br>density          | f <sub>s</sub> = 983.04 Msps;<br>×4 interpolation;<br>f <sub>o</sub> = 20 MHz at -1 dBFS                                                                                                                                                          | D           | -   | -158 | -   | dBm/Hz |

|                        |                                    | $f_s = 983.04 \text{ Msps};$<br>×4 interpolation;<br>$f_o = 153.6 \text{ MHz}$ at –1 dBFS                                                                                                                                                         | D           | -   | -155 | -   | dBm/Hz |

|                        |                                    |                                                                                                                                                                                                                                                   |             |     |      |     |        |

[1] D = guaranteed by design; C = guaranteed by characterization; I = 100 % industrially tested.

[2] Connect V<sub>DDA(1V8)\_D</sub>, V<sub>DDA(1V8)\_P1</sub> and V<sub>DDA(1V8)\_P2</sub> to the same 1.8 V analog power supply. Use dedicated filters for the three power pins.

[3] |V<sub>gpd</sub>| represents the ground potential difference voltage. This voltage is the result of current flowing through the finite resistance and the inductance between the receiver and the driver circuit ground voltages.

### **10. Application information**

### **10.1 General description**

The DAC1617D1G0 is a dual 16-bit DAC operating up to 1000 Msps. Each DAC consists of a segmented architecture, comprising a 6-bit thermometer subDAC and a 10-bit binary weighted subDAC.

A maximum input LVDS DDR data rate of up to 370 MHz and a maximum output sampling rate of 1000 Msps ensure more flexibility for wide bandwidth and multi-carrier systems. The internal 40-bit NCO of the DAC1617D1G0 simplifies the frequency selection of the system. The DAC1617D1G0 provides  $\times 2$ ,  $\times 4$  or  $\times 8$  interpolation filters that are useful for removing the undesired images.

Each DAC generates two complementary current outputs on pins IOUTAP and IOUTAN and pins IOUTBP and IOUTBN. These outputs provide a full-scale output current ( $I_{O(fs)}$ ) of up to 34 mA. An internal reference is available for the reference current which is externally adjustable using pin VIRES.

High resolution internal gain, phase and offset control provide outstanding image and Local Oscillator (LO) signal rejection at the system analog modulator output.

Multiple device synchronization enables synchronization of the outputs of multiple DAC devices. MDS guarantees a maximum skew of one output clock period between several devices.

All functions can be set using an SPI interface.

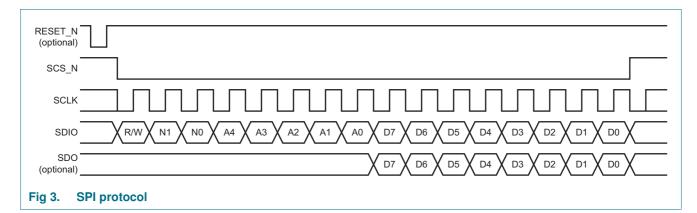

### 10.2 Serial Peripheral Interface (SPI)

### 10.2.1 Protocol description

The DAC1617D1G0 serial interface is a synchronous serial communication port ensures easy interface with many industry microprocessors. It provides access to the registers that define the operating modes of the chip in both write and read mode.

This interface can be configured as a 3-wire type (pin SDIO as bidirectional pin) or 4-wire type (pins SDIO and SDO as unidirectional pins, input and output port, respectively). In both configurations, SCLK acts as the serial clock and SCS\_N as the serial chip select.

<u>Figure 3</u> shows the SPI protocol. An SCS\_N signal follows each read/write operation. A LOW assertion enables it to drive the chip with 2 bytes to 5 bytes, depending on the content of the instruction byte (see <u>Table 7</u>).

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

R/W indicates the mode access (see Table 6)

| Table 6. | Read o | r Write | mode | access | description |

|----------|--------|---------|------|--------|-------------|

|----------|--------|---------|------|--------|-------------|

| R/W | Description          |

|-----|----------------------|

| 0   | Write mode operation |

| 1   | Read mode operation  |

<u>Table 7</u> shows the number of bytes to be transferred. N1 and N0 indicate the number of bytes transferred after the instruction byte.

| Table 7. | Number | of b | vtes | transferred |

|----------|--------|------|------|-------------|

|          |        |      | ,    |             |

| N1 | N0 | Number of bytes transferred |

|----|----|-----------------------------|

| 0  | 0  | 1 byte                      |

| 0  | 1  | 2 bytes                     |

| 1  | 0  | 3 bytes                     |

| 1  | 1  | 4 bytes                     |

|    |    |                             |

A[4:0] indicates which register is being addressed. If a multiple transfer occurs, this address concerns the first register. The other registers follow directly in a decreasing order (see <u>Table 21</u>, <u>Table 35</u> and <u>Table 53</u>).

The DAC1617D1G0 incorporates more than the 32 SPI registers allowed by the address value A[4:0]. It uses three SPI register pages (page\_00, page\_01, and page\_0A), each containing 32 registers. The 32<sup>nd</sup> register of each page indicates which page is currently addressed (00h, 01h or 0Ah).

#### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

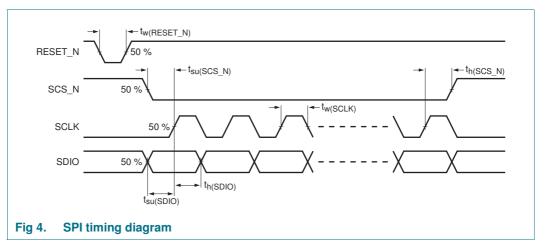

#### 10.2.2 SPI timing description

The SPI interface can operate at a frequency up to 25 MHz. The SPI timings are shown in Figure 4.

The SPI timing characteristics are given in Table 8.

#### Table 8. SPI timing characteristics

| Symbol                 | Parameter              | Min | Тур | Max | Unit |

|------------------------|------------------------|-----|-----|-----|------|

| f <sub>SCLK</sub>      | SCLK frequency         | -   | -   | 25  | MHz  |

| $t_{w(SCLK)}$          | SCLK pulse width       | 30  | -   | -   | ns   |

| t <sub>su(SCS_N)</sub> | SCS_N set-up time      | 20  | -   | -   | ns   |

| t <sub>h(SCS_N)</sub>  | SCS_N hold time        | 20  | -   | -   | ns   |

| t <sub>su(SDIO)</sub>  | SDIO set-up<br>time    | 10  | -   | -   | ns   |

| t <sub>h(SDIO)</sub>   | SDIO hold time         | 5   | -   | -   | ns   |

| $t_{w(RESET_N)}$       | RESET_N pulse<br>width | 30  | -   | -   | ns   |

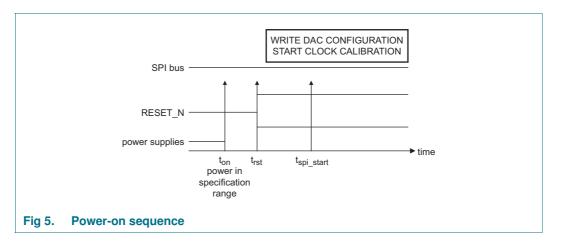

### **10.3 Power-on sequence**

There are three steps for the power-on sequence (see Figure 5):

- 1. The board is power-on. At the turn-on time, all DAC1617D1G0 supplies have reached their specification ranges.

- 2. At least 1 µs after the turn-on time pin RESET\_N must be released.

- When the DAC clock and LVDS clock are stable, the SPI configuration is sent to the DAC1617D1G0. Writing 0 in bits RST\_DCLK and RST\_LCLK of the register MAIN\_CNTRL (see <u>Table 54</u>) starts the automatic calibration. 30 μs after this calibration, the DAC1617D1G0 is operational.

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

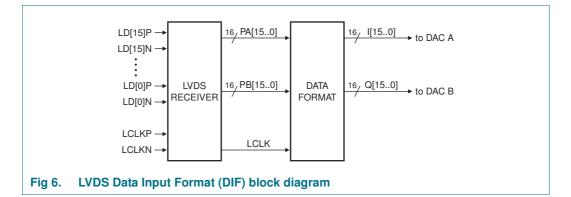

### 10.4 LVDS Data Input Format (DIF) block

The Data Input Formatting (DIF) block captures and resynchronizes data on the LVDS bus with its own LCLKP/LCLKN clock. Each LVDS input buffer has an internal resistance of 100  $\Omega$ , so an external resistor is not required. The DIF block includes two subblocks:

### • LVDS receiver:

Provides high flexibility for the LVDS interface, especially for the PCB layout and the control of the input port polarity and the input port mapping.

### Data format block:

Enables the adaptation, which ensures the support of several data encoding modes.

### **10.4.1** Input port polarity

The polarity of each individual LVDS input (LD[15]P to LD[0]P and LD[15]N to LD[0]N) can be changed. This ensures a much easier PCB layout design. The input polarity is controlled with bits LD\_POL[15:0] (see <u>Table 59</u>).

### 10.4.2 Input port mapping

Inverting the order of the LSB and the MSB of the LVDS bus using bit WORD\_SWAP in register LD\_CNTRL (see <u>Table 60</u>) also simplifies the design of the PCB (see <u>Table 9</u>).

#### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

| Table 9. Input LVDS bus swapping |                                      |                                      |  |  |  |  |  |

|----------------------------------|--------------------------------------|--------------------------------------|--|--|--|--|--|

| Internal LVDS bus                | External LVDS bus<br>(WORD_SWAP = 0) | External LVDS bus<br>(WORD_SWAP = 1) |  |  |  |  |  |

| LDI[15]P,N                       | LD[15]P,N                            | LD[0]P,N                             |  |  |  |  |  |

| LDI[14]P,N                       | LD[14]P,N                            | LD[1]P,N                             |  |  |  |  |  |

| LDI[13]P,N                       | LD[13]P,N                            | LD[2]P,N                             |  |  |  |  |  |

| LDI[12]P,N                       | LD[12]P,N                            | LD[3]P,N                             |  |  |  |  |  |

| LDI[11]P,N                       | LD[11]P,N                            | LD[4]P,N                             |  |  |  |  |  |

| LDI[10]P,N                       | LD[10]P,N                            | LD[5]P,N                             |  |  |  |  |  |

| LDI[9]P,N                        | LD[9]P,N                             | LD[6]P,N                             |  |  |  |  |  |

| LDI[8]P,N                        | LD[8]P,N                             | LD[7]P,N                             |  |  |  |  |  |

| LDI[7]P,N                        | LD[7]P,N                             | LD[8]P,N                             |  |  |  |  |  |

| LDI[6]P,N                        | LD[6]P,N                             | LD[9]P,N                             |  |  |  |  |  |

| LDI[5]P,N                        | LD[5]P,N                             | LD[10]P,N                            |  |  |  |  |  |

| LDI[4]P,N                        | LD[4]P,N                             | LD[11]P,N                            |  |  |  |  |  |

| LDI[3]P,N                        | LD[3]P,N                             | LD[12]P,N                            |  |  |  |  |  |

| LDI[2]P,N                        | LD[2]P,N                             | LD[13]P,N                            |  |  |  |  |  |

| LDI[1]P,N                        | LD[1]P,N                             | LD[14]P,N                            |  |  |  |  |  |

| LDI[0]P,N                        | LD[0]P,N                             | LD[15]P,N                            |  |  |  |  |  |

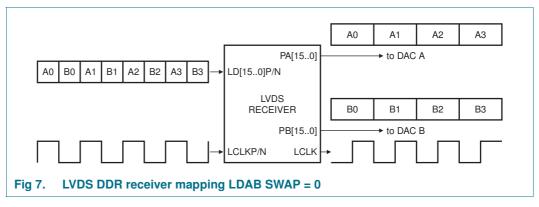

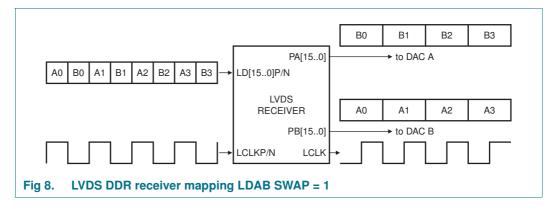

### 10.4.3 Input port swapping

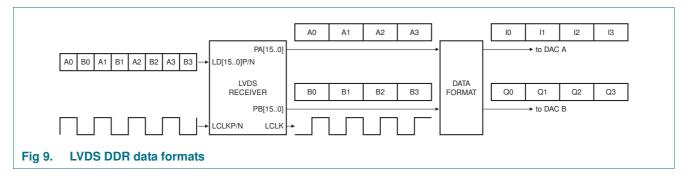

The LVDS DDR receiver block internally maps the incoming LVDS data bus into two buses with a single data rate (Figure 7).

These two buses can be swapped internally using bit LDAB\_SWAP of register LD\_CNTRL (see <u>Table 60</u> and <u>Figure 8</u>).

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### **10.4.4 Input port formatting**

The LVDS DDR input bus multiplexes two 16-bit streams. The LVDS receiver block demultiplexes these two streams.

The two streams can carry two data formats:

- Folded

- Interleaved

The data format block is in charge of the data format adaptation (see Figure 9).

The DAC1617D1G0 can correctly decode the input stream using bit IQ\_FORMAT of register LD\_CNTRL (see <u>Table 60</u>), because it can determine which format is used on the LVDS DDR bus.

<u>Table 10</u> shows the format mapping between the LVDS input data and the data sent to the two DAC channels depending on the data format selected.

#### Table 10. Folded and interleaved format mapping

| a bit mapping                                                     |

|-------------------------------------------------------------------|

| 50] = An[150]; Qn[150] = Bn[150]                                  |

| 58] = An[158]; In[70] = Bn[158]<br> 58] = An[70]; Qn[70] = Bn[70] |

|                                                                   |

#### 10.4.5 Data parity/data enable

The ALIGN pins can be used in several ways:

- As datastream start flag for Multiple Devices Synchronization (see Section 10.13).

- As LVDS data enable which can be used to insert a DC level into the datastream. The SEL\_EN bits in register LD\_CNTRL (see <u>Table 60</u>) enable the programming of this mode. The DC level for both channels is selected using registers I\_DC\_LVL and Q\_DC\_LVL (see <u>Table 62</u>)

- As parity bit for the LD[15:0] to detect disruptions at the LVDS-input port bit PARITYC in register LD\_CNTRL (see <u>Table 60</u>) enabling the control of this mode. A Parity error can generate an interrupt (INTR) reported on either IO0 or IO1 pin

### **10.5 Interrupt controller**

The DAC1617D1G0 incorporates an interrupt controller that makes notifying a host-controller in case of an internal event. The INTR-signal can be made available on one of the IO pins. The polarity on the IO pins is programmable.

The internal event that must be tracked and generates an interrupt can be selected using the INTR\_EN register (see <u>Table 45</u>). Two types of interrupt sources are considered:

- The ready-indicators (MAQ\_RDY\_B, MAQ\_RDY\_A, AUTO\_CAL\_RDY, and AUTO\_DL\_RDY; register INTR\_FLAGS; see Table <u>Table 47</u>) notify the host-interface that the corresponding process (invoked by the host interface) has been finalized

- The error flags indicate that a failure has been detected. For example, on the LVDS-interface it is possible to check for parity errors and/or to monitor if the internal timing of the LVDS clock delay has changed since the calibration. Errors like these can result in critical timings within the Clock Domain Interface (CDI) which transfers the data from the LCLK to the DCLK domain

The selected event that has invoked the interrupt can be determined using the INTR\_FLAGS register (see <u>Table 47</u>). The flags and the INTR signal are reinitialized by setting the INTR\_CLEAR control bit in register INTR\_CTRL (see <u>Table 45</u>).

### 10.6 General-purpose IO pins

The DAC1617D1G0 provides two general-purpose pins, IO0 and IO1. These pins can be used to observe the interrupt signal (INTR) or other internal signals (internal clocks, LVDS data, etc.). These pins can also be used as generic outputs to control external devices.

The internal signals that must be observed on these pins are selected using registers IO\_MUX0, IO\_MUX1, and IO\_MUX2 (see <u>Table 63</u> and <u>Table 64</u>).

### 10.7 Input clock

The DAC1617D1G0 operates with two clocks, one for the LVDS DDR interface and one for the DAC core.

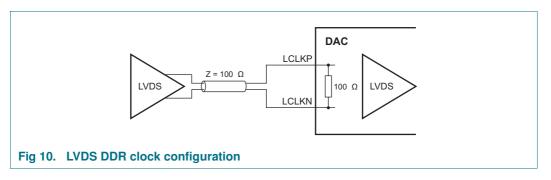

#### 10.7.1 LVDS DDR clock

The LVDS DDR clock can be interfaced as shown in Figure 10 because the clock buffer contains a 100  $\Omega$  internal resistor.

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

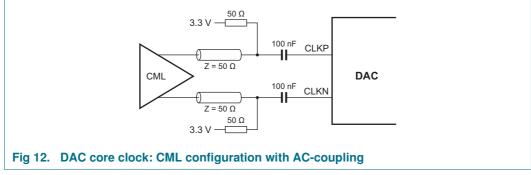

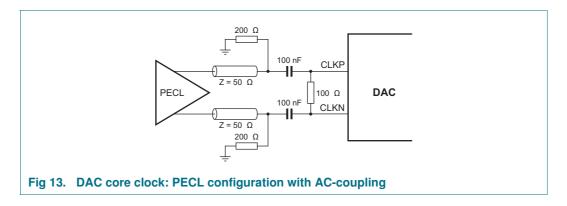

### 10.7.2 DAC core clock

The DAC core clock can achieve a frequency of up to 1 Gsps. It includes internal biasing to support both AC-coupling and DC-coupling. The clock can be easily connected to any LVDS, CML or PECL clock sources.

Depending on the interface selected, the hardware configuration varies (see <u>Figure 11</u> to <u>Figure 13</u>).

Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### 10.8 Timing

The DAC1617D1G0 can operate at an update rate ( $f_s$ ) of up to 1 Gsps and with an input data rate ( $f_{data}$ ) of up to 370 MHz.

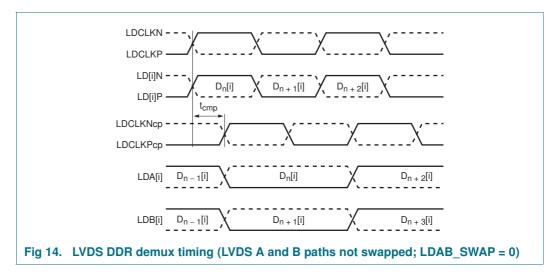

The sampling position of the LVDS data can be tuned using a 16-step compensation delay clock. An internal clock is generated to define the exact sampling position of the LVDS data (see Figure 14, signals LDCLKPcp and LDCLKNcp) which depends on the compensation delay.

Figure 14 shows how the compensation delay helps to recover the LVDS DDR data on both the A and B paths.

The compensation delay time ( $t_{cmp}$  in Figure 14) can be tuned automatically or manually. Bit CAL\_CNTRL of the MAIN\_CNTRL register (see Table 54) enables the switching between automatic tuning and manual tuning.

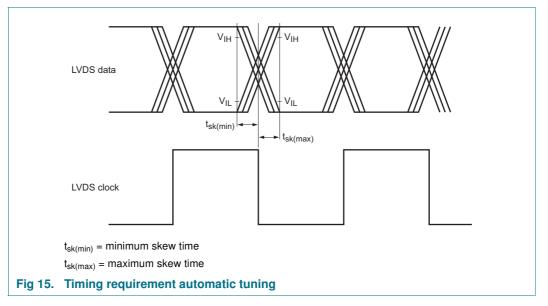

In Automatic tuning mode, the external LVDS data and clock signals are generated using the same reference clock (inside the FPGA). The LDCLK clock is similar to a data bit that toggles each time (the rising edge and falling edge of the LDCLK and LVDS data occur at the same time). In automatic tuning, the internal compensation delay time ( $t_{cmp}$ ) is defined automatically to compensate the internal DAC1617D1G0 delay time optimally.

The timing requirement in automatic tuning mode is defined in Figure 15 and in Table 5.

#### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

Use manual tuning mode if the LVDS data and the LDCLK clock signals provided to the DAC1617D1G0 device have a systematic delay. The compensation delay time can be adjusted to compensate for the systematic delay. The compensation delay time ( $t_{cmp}$  in Figure 14), can be defined using bits LDCLK\_DEL[3:0] of register MAN\_LDCLKDEL (see Table 55).

The timing requirement in manual tuning mode is defined in Figure 16 and in Table 5.

### 10.9 Operating modes

The DAC1617D1G0 requires two differential clocks:

- The LVDS clock (LDCLKP, LDCLKN) for the LVDS DDR interface

- The data clock (CLKP, CLKN) for the internal PLL and the dual DAC core

In Normal mode, provide both the DAC clock and the LVDS clock to the DAC1617D1G0. Align the ratio frequency between these two clocks needs with selected  $\times 2$ ,  $\times 4$  or  $\times 8$  interpolation filters. The clocks provided to the DAC1617D1G0 must respect the LVDS input timing and the DAC output timing specifications as defined in <u>Table 5</u>.

#### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

In PLL mode, provide the LVDS clock to pins LDCLKP/LDCLKN and pins CLKP/CLKN. Depending on selected interpolation filter, the internal PLL can be set to generate the right DAC core clock frequency internally. The clocks provided to the DAC1617D1G0 pins must respect the LVDS input timing and the DAC output timing specifications as defined in Table 5. The PLL settings must also respect the maximum sampling rate of the PLL (see the sampling rate ( $f_s$ ) in subsection Internal PLL timing of Table 5).

The main function of the Clock Domain Interface (CDI) is to resynchronize the input data streams to the internal clock the digital processing uses. The CDI also performs the required reformatting of the input datastreams. Set PLL, CDI, and the interpolation filters, which depend on the targeted application accordingly. <u>Section 10.9.1</u> (×2), <u>Section 10.9.2</u> (×4), and <u>Section 10.9.3</u> (×8) explain how to set the DAC1617D1G0 to support the different upsampling modes.

### 10.9.1 CDI mode 0 (x2 interpolation)

CDI mode 0 ( $\times$ 2 interpolation) is required when the value of the LVDS DDR clock is twice the internal maximum CDI frequency. <u>Table 11</u> shows examples of applications using an internal PLL or an external clock for the DAC core.

| LVDS DDR<br>rate (MHz) | l rate;<br>Q rate | CDI<br>mode[1] | FIR mode <sup>[2]</sup> | SSBM<br>rate <sup>[3]</sup> |         | PL                                         |                              |                               |

|------------------------|-------------------|----------------|-------------------------|-----------------------------|---------|--------------------------------------------|------------------------------|-------------------------------|

|                        | (Msps)            | mode           |                         | (Msps)                      | (10342) | DAC input<br>clock <sup>[4]</sup><br>(MHz) | PLL<br>status <sup>[5]</sup> | PLL<br>divider <sup>[6]</sup> |

| 320                    | 320               | 0              | ×2                      | 640                         | 640     | 320                                        | enabled                      | 2                             |

| 320                    | 320               | 0              | ×2                      | 640                         | 640     | 640                                        | disabled                     | n.a.                          |

#### Table 11. CDI mode 0: operating modes examples

[1] Bits CDI\_MODE[1:0] of register MISC\_CNTRL (see <u>Table 61</u>).

[2] Bits INTERPOLATION[1:0] of register TXCFG (see <u>Table 23</u>).

[3] If a Single Sideband Modulator (SSBM) is used, see bits NCO\_ON and MODULATION[2:0] of register TXCFG (see Table 23).

[4] Pins CLKP and CLKN (see Figure 2).

[5] Bit PLL\_PD of register PLLCFG (see Table 24).

[6] Bits PLL\_DIV[1:0] of register PLLCFG (see <u>Table 24</u>).

#### Dual 16-bit DAC: up to 1 Gsps; x2, x4 and x8 interpolating

### 10.9.2 CDI mode 1 (x4 interpolation)

CDI mode 1 (×4 interpolation) is required when the values of the LVDS DDR clock and the internal CDI frequency are equal. <u>Table 12</u> shows examples of applications using an internal PLL or an external clock for the DAC core.

#### Table 12. CDI mode 1: operating modes examples

| ,          | CDI              |                     | SSBM DAC rate |                                            | PLL configuration |                                            |                              |                               |

|------------|------------------|---------------------|---------------|--------------------------------------------|-------------------|--------------------------------------------|------------------------------|-------------------------------|