Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

Home > Products > Intellectual Property > Lattice IP Cores > Distributed Arithmetic FIR (DA-FIR)

# Distributed Arithmetic FIR (DA-FIR) Filter Generator

## Overview

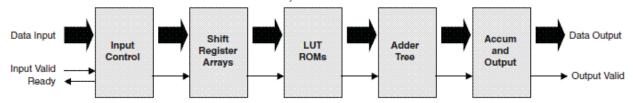

The Lattice Distributed Arithmetic Finite Impulse Response (DA-FIR) Filter Generator IP implements a highly configurable, multi-channel DA-FIR filter, using distributed arithmetic algorithms implemented in FPGA Look Up Table (LUT) or Embedded Block Memory (EBR) to efficiently support the sum-of-product calculations required to perform the filter function. These techniques generate very area-efficient utilization of the FPGA

LUTs while enabling savings of multiply-accumulate blocks (sysDSP) for other design logic. As a result, the DA-FIR Filter Generator IP core is extremely useful for implementing custom DSP blocks in Lattice FPGAs. Please refer to the user's guide to determine which cores are available for each device family.

## **Features**

Variable number of taps up to 1024

Multi-channel support (up to 32 channels)

Polyphase interpolation/decimation filters

Halfband filters

Interpolation and Decimation ratios from 2 to 32

Input data widths from 4 to 32 bits

Coefficient widths from 4 to 32 bits

Signed or unsigned data and coefficients

Selectable rounding: truncation, rounding away from zero, convergent rounding

Optional saturation logic for overflow handling

Full precision arithmetic

Specification of fractional inputs and outputs

Support for both serial and parallel filters, with user specified degree of parallelism.

Configurable pipelining to increase performance

Optimizations based on filter characteristics (symmetry and halfband).

Handshake signals to facilitate smooth interfacing

#### **Performance and Resource Utilization**

## Lattice ECP3<sup>1</sup>

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 290     | 348  | -    | 476       | 318  |

| 1        | 9    | Disable       | 8      | TRUN  | 512     | 611  | -    | 877       | 279  |

| 1        | 36   | Enable        | 12     | TRUN  | 600     | 709  | -    | 883       | 308  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFE3-70E-7FN484CES device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeECP3 family.

# Lattice ECP2 M/S1

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 317     | 378  | -    | 481       | 343  |

| 1        | 9    | Disable       | 8      | TRUN  | 550     | 655  | -    | 887       | 310  |

| Channe | ls Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|--------|---------|---------------|--------|-------|---------|------|------|-----------|------|

| 1      | 36      | Enable        | 12     | TRUN  | 625     | 743  | -    | 899       | 291  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFE2M20E-6F256C device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeECP2M family.

#### Lattice ECP2/S1

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 317     | 378  | -    | 481       | 341  |

| 1        | 9    | Disable       | 8      | TRUN  | 550     | 655  | -    | 887       | 321  |

| 1        | 36   | Enable        | 12     | TRUN  | 625     | 743  | -    | 899       | 320  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFE2-20E-6F256C device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeECP2 family.

## Lattice ECP/ EC1

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 296     | 340  | -    | 481       | 192  |

| 1        | 9    | Disable       | 8      | TRUN  | 521     | 594  | -    | 887       | 180  |

| 1        | 36   | Enable        | 12     | TRUN  | 590     | 689  | -    | 899       | 174  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFECP15E-4F256C device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeECP family.

# LatticeSC/ M<sup>1</sup>

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 278     | 343  | -    | 481       | 372  |

| 1        | 9    | Disable       | 8      | TRUN  | 564     | 759  | -    | 895       | 338  |

| 1        | 36   | Enable        | 12     | TRUN  | 568     | 668  | -    | 934       | 390  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFSC3GA15E-6F256C device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeSC/M family.

# Lattice XP2<sup>1</sup>

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 317     | 378  | -    | 481       | 274  |

| 1        | 9    | Disable       | 8      | TRUN  | 550     | 655  | -    | 887       | 251  |

| 1        | 36   | Enable        | 12     | TRUN  | 625     | 743  | -    | 899       | 270  |

2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeXP2 family.

## Lattice XP1

| Channels | Taps | Interpolation | DWidth | Round | SLI CEs | LUTs | EBRs | Registers | Fmax |

|----------|------|---------------|--------|-------|---------|------|------|-----------|------|

| 1        | 16   | Disable       | 16     | TRUN  | 296     | 340  | -    | 481       | 186  |

| 1        | 9    | Disable       | 8      | TRUN  | 521     | 594  | -    | 887       | 178  |

| 1        | 36   | Enable        | 12     | TRUN  | 590     | 689  | -    | 899       | 168  |

<sup>1.</sup> Performance and utilization data are generated targeting a LFXP10E-4F256C device using Lattice Diamond 1.0 and Synplify Pro D-2009.12L-1 software. Performance may vary when using a different software version or targeting a different device density or speed grade within the LatticeXP family.

# **Ordering Information**

**Family** Part Number LatticeECP3 DAFIR-GEN-E3-U2 DAFIR-GEN-PM-U2 LatticeECP2M LatticeECP2 DAFIR-GEN-P2-U2 LatticeECP/EC DAFIR-GEN-E2-U2 LatticeSC DAFIR-GEN-SC-U2 LatticeXP2 DAFIR-GEN-X2-U2 LatticeXP DAFIR-GEN-XM-U2

IP Version: 2.2

Evaluate: To download a full evaluation version of this IP, go to the IPexpress tool and click the IP Server button in the toolbar. All LatticeCORE IP cores and modules available for download will be visible. For more information on viewing/downloading IP please read the IP Express Quick Start Guide.

Purchase: To find out how to purchase the IP Core, please contact your local Lattice Sales Office.