Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

## Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

## LTC6951 Multichannel JESD204B ADC with Clocking

### DESCRIPTION

Demonstration Circuit 2226A-A is a reference design for a four-channel, 250Msps ADC system consisting of two LTC®2123, dual 14-bit 250Msps ADCs and a JESD204B Subclass 1 clocking solution based on the LTC6951 Clock Synthesizer with Integrated VCO. Other dash options reserved for future use. No external clock source is required to operate the board; however, the onboard 100MHz reference oscillator may be bypassed, allowing synchronization to other equipment.

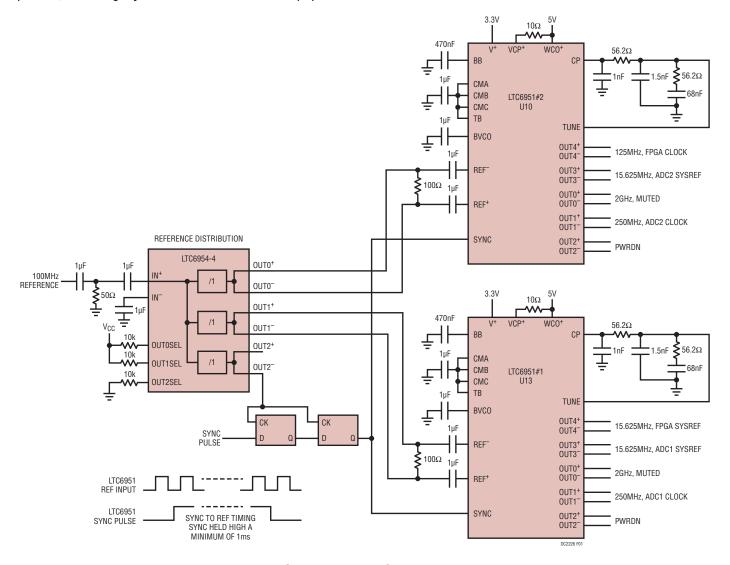

Figure 1 is a block diagram of the DC2226A clock configuration, consisting of two LTC6951s in a JESD204B subclass 1, ParallelSync<sup>™</sup> configuration. More detailed information is available on the LTC6951 product page.

# Design files for this circuit board are available at http://www.linear.com/demo/DC2226A

7, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and ParallelSync and PScope are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

Figure 1. Subclass 1 ParallelSync Design Example

## **QUICK START PROCEDURE**

- Install PScope<sup>™</sup> from http://www.linear.com/solutions/PScope. This step will also install the USB drivers required to communicate with the DC2226A demo system. Quit PScope after the installation is finished. Note that PScope does not directly support the DC2226A demo system, however the Matlab and Python scripts can export data files that may be opened in PScope for analysis.

- 2) Install LinearLabTools from <a href="http://www.linear.com/solutions/linearlabtools">http://www.linear.com/solutions/linearlabtools</a>, following the procedure for either Matlab or Python. Both Matlab and Python code for DC2226A are included in the \matlab\DemoBoardExamples\LTC2123 and \python\demo\_board\_examples\ltc2123 directories, respectively. The main scripts run through a series of tests, concluding with capturing data from all four channels and displaying time and frequency domain plots.

- Do NOT plug the USB cable into the DC2159 FMC Communication Interface board before powering up the KC705 board.

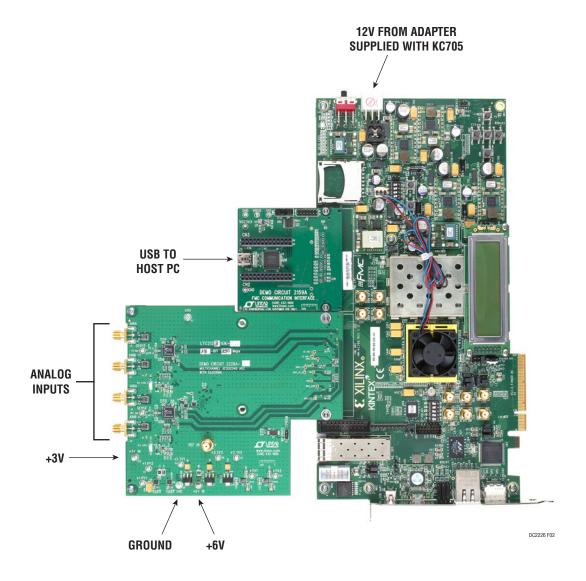

- 4) Refer to Figure 2. Power up the KC705 board using the adapter supplied with the KC705. If the board was obtained from Linear Technology as part of a kit, the correct bitfile was installed into the onboard configuration PROM.

- 5) If necessary, load the .bit file (included in the design files PDF subdirectory) into the KC705 board using the appropriate Xilinx tool (Impact, Vivado, or Vivado lab). Alternatively, create a .mcs file from the bitfile and load into the onboard configuration PROM. (See KC705 documentation for details.)

- 6) Connect the DC2159 FMC board to the host PC with a USB-A/Mini-B cable.

- 7) Apply 6V and 3V to the turret posts as shown in Figure 2. Both supplies should be low-noise benchtop supplies, with current limit set to 2A.

- 8) Apply analog input signals to J2, J3, J4, J5. The DC2226A is populated with an input network that has 50Ω characteristic impedance over a wide frequency range, refer to LTC2123 data sheet for details. A 70MHz, 1.5V<sub>P-P</sub> sine wave is a good starting point for testing DC2226A. If an RF generator is used, it should be followed by a bandpass filter to limit noise and harmonics. Alternatively, DC1164 High Speed ADC Signal Source may be used.

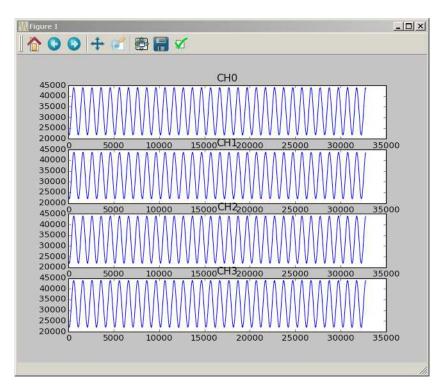

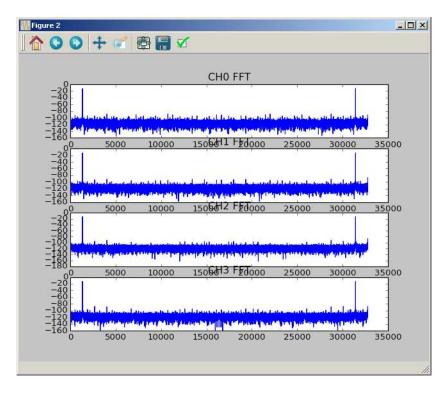

- 9) Run the appropriate test script (Ltc2123Dc2226Du-alClockingSolution.m for Matlab, Itc2123\_dc2226\_dual\_clocking\_solution.py for Python). Plots similar to Figures 3 and 4 should appear. At this point, data is stored in program variables for further manipulation and testing.

- 10) The default test scripts set the ADC sample rate to 250MSPS, with a SYSREF frequency of 15.625MHz (JESD204B K=16). Design examples on the LTC6951 product page detail the process for changing clock frequencies.

## **QUICK START PROCEDURE**

Figure 2. Basic Connections

## **QUICK START PROCEDURE**

Figure 3. Example Time Domain Plot

Figure 4. Example Frequency Domain Plot

### HARDWARE SETUP

#### DC2226A Power Connections

**E14:** +6V Power Input. Connect to a low-noise supply set to a current limit of 2A.

**E12:** +3V Power Input. Connect to a low-noise supply set to a current limit of 2A.

**E1**, **E9**: GND - Ground connections for power supplies.

**E5, E8:** 1.8V test points. Measure 1.8V supply voltages at these points. (Measurement only, do not apply power.)

**E4, E6, E11:** 3V3\_1, 3V3\_2, 3V3\_3 test points. Measure 3.3V supply voltages at these points. (Measurement only, do not apply power.)

**E7**, **E13**: 5V\_1, 5V\_2 test points. Measure 5V supply voltages at these points. (Measurement only, do not apply power.)

#### **DC2226A Signal Connections**

**J2**, **J3**: Analog inputs for U1,  $50\Omega$  impedance. Maximum signal level is  $1.5V_{P-P}$ .

**J4, J5:** Analog inputs for U3,  $50\Omega$  impedance. Maximum signal level is  $1.5V_{P-P}$ .

**J1:** External Reference Clock Input. Not connected, requires component changes, refer to schematic.

**J6:** FMC HPC interface to FPGA carrier board.

### APPENDIX A

### Xilinx KC705 Based Evaluation System

The DC2226A system consists of the DC2226A itself, a Xilinx KC705 FPGA evaluation board, a DC2159 USB communication board, and a host PC running the various test programs. Complete systems that ship from Linear Technology will have the KC705 board configured to automatically load the default FPGA image for DC2226A from the onboard configuration EEPROM. The procedure for bringing up the system is as follows:

- If the boards were obtained separately, assemble them as shown in Figure 1 (FMC connectors are fragile, make sure they are properly aligned before seating.)

- Connect power supply to the KC705 board and turn on the power switch. If the assembled system was obtained from Linear Technology, the FPGA bitstream will load automatically from the onboard configuration memory.

- Boards not obtained from Linear Technology will need to be configured as described in the Alternate FPGA Configuration section.

- 4) Apply power and analog input signals to the DC2226A board.

5) Verify that PScope software is installed. Connect DC2159 to the host PC with a USB-mini cable. Driver installation will start automatically and PScope will recognize the system when installation finishes. Quit PScope and run Matlab/Python test scripts.

**Note:** Power must be applied to the KC705 board when the USB cable is connected or the driver installation will not complete properly.

## Alternate FPGA Configuration

KC705 boards not obtained from Linear Technology will need to be configured via JTAG. FPGA images are located in the PScope installation directory in the FPGA\_images folder. Connect a USB micro cable to the JTAG USB connector on the KC705 board and use a Xilinx tool such as Impact or Vivado Lab Edition to load the bitfile. Once the FPGA is configured, remove the USB cable and exit the software. (The onboard JTAG adapter and the DC2159 USB communication board use the same USB controller and they may interfere with one another.)

## DEMO MANUAL DC2226

#### DEMONSTRATION BOARD IMPORTANT NOTICE

Linear Technology Corporation (LTC) provides the enclosed product(s) under the following AS IS conditions:

This demonstration board (DEMO BOARD) kit being sold or provided by Linear Technology is intended for use for **ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY** and is not provided by LTC for commercial use. As such, the DEMO BOARD herein may not be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety measures typically found in finished commercial goods. As a prototype, this product does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may or may not meet the technical requirements of the directive, or other regulations.

If this evaluation kit does not meet the specifications recited in the DEMO BOARD manual the kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user releases LTC from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. Also be aware that the products herein may not be regulatory compliant or agency certified (FCC, UL, CE, etc.).

No License is granted under any patent right or other intellectual property whatsoever. LTC assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.

LTC currently services a variety of customers for products around the world, and therefore this transaction is not exclusive.

**Please read the DEMO BOARD manual prior to handling the product**. Persons handling this product must have electronics training and observe good laboratory practice standards. **Common sense is encouraged**.

This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a LTC application engineer.

Mailing Address:

Linear Technology 1630 McCarthy Blvd. Milpitas, CA 95035

Copyright © 2004, Linear Technology Corporation