Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# Lattice **CORE**

# DDR & DDR2 SDRAM Controller for MachXO2 PLD Family IP Cores User Guide

(Piplelined Versions)

# **Table of Contents**

| Chapter 1. Introduction                                   |    |

|-----------------------------------------------------------|----|

| Quick Facts                                               |    |

| Features                                                  |    |

| Chapter 2. Functional Description                         |    |

| Command Decode Logic                                      |    |

| Configuration Interface                                   |    |

| sysCLOCK PLL                                              |    |

| Data Path Logic                                           |    |

| Initialization State Machine                              |    |

| Command Application Logic                                 |    |

| DDR I/O Modules                                           |    |

| Signal Descriptions                                       | 8  |

| Using the Local User Interface                            |    |

| Initialization and Auto-Refresh Control                   |    |

| Command and Address                                       | 11 |

| Data Write                                                | 12 |

| Data Read                                                 | 13 |

| Read/Write with Auto Precharge                            |    |

| Local-to-Memory Address Mapping                           |    |

| Mode Register Programming                                 |    |

| Memory Interface                                          |    |

| Chapter 3. Parameter Settings                             |    |

| Mode Tab                                                  |    |

| Type Tab                                                  |    |

| Select Memory                                             |    |

| Clock                                                     |    |

| Memory Data Bus Size                                      |    |

| Configuration                                             |    |

| Data_rdy to Write Data Delay                              |    |

| Clock Width                                               |    |

| CKE Width                                                 |    |

| Fixed Memory Timing                                       |    |

| Setting Tab                                               |    |

| Row Size                                                  |    |

| Column Size                                               |    |

| Bank Size                                                 |    |

| Chip Select Width.                                        | 22 |

| User Slot Size                                            |    |

| EMR Prog During Init                                      |    |

|                                                           |    |

| Auto Refresh Burst Count                                  |    |

| External Auto Refresh Port                                |    |

| Mode Register Initial Setting                             |    |

| Timing Tab                                                |    |

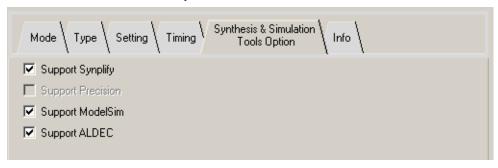

| Synthesis & Simulation Tools Option Tab                   |    |

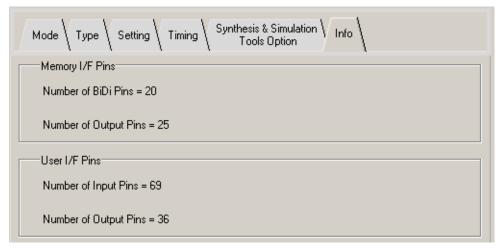

| Info Tab                                                  |    |

| Chapter 4. IP Core Generation                             |    |

| Licensing the IP Core                                     |    |

| Getting Started                                           |    |

| IPexpress-Created Files and Top Level Directory Structure |    |

| Generated Files                                           | 27 |

| DDR Memory Controller Core Structure           |    |

|------------------------------------------------|----|

| Top-level Wrapper                              | 29 |

| Encrypted Netlist                              | 29 |

| I/O Modules                                    | 29 |

| Clock Generator                                | 29 |

| Parameter File                                 | 29 |

| Core Header File                               | 29 |

| Preference Files                               |    |

| Evaluation Project Files                       |    |

| Simulation Files for Core Evaluation           |    |

| Testbench Top                                  |    |

| Obfuscated Core Simulation Model               |    |

| Command Generator                              |    |

| Monitor                                        |    |

| TB Configuration Parameter                     |    |

| Memory Model                                   |    |

| Memory Model Parameter                         |    |

| Evaluation Script File                         |    |

| Hardware Evaluation                            |    |

| Enabling Hardware Evaluation in Diamond        |    |

| Enabling Hardware Evaluation in ispLEVER       |    |

| Updating/Regenerating the IP Core              |    |

| Regenerating an IP Core in Diamond             |    |

|                                                |    |

| Regenerating an IP Core in ispLEVER            |    |

| Chapter 5. Application Support                 |    |

| Core Implementation Understanding Preferences  |    |

|                                                |    |

| Preference Localization                        |    |

| VREF Assignments                               |    |

| DLL Allocation                                 |    |

| I/O Types for DDR                              |    |

| Skew Treatment                                 |    |

| Dummy Logic Removal                            |    |

| Read Data Auto-Alignment Logic                 |    |

| PCB Routing Delay Compensation                 |    |

| DQS_PIO_READ Locate Constraints                |    |

| Obtaining Location Values in Diamond Software  |    |

| Obtaining Location Values in ispLEVER Software |    |

| Troubleshooting                                |    |

| Chapter 6. Core Verification                   |    |

| Chapter 7. Support Resources                   |    |

| Lattice Technical Support                      |    |

| Online Forums                                  |    |

| Telephone Support Hotline                      | 41 |

| E-mail Support                                 | 41 |

| Local Support                                  | 41 |

| Internet                                       | 41 |

| References                                     | 41 |

| MachXO2                                        | 41 |

| JEDEC Website                                  | 41 |

| Micron Technology, Inc., Website               | 41 |

| Revision History                               |    |

| Appendix A. Resource Utilization               |    |

|                                                |    |

| MachXO2 Devices      | 4 | 43 |

|----------------------|---|----|

| Ordering Part Number | _ | 1. |

# Introduction

The Double Data Rate (DDR) Synchronous Dynamic Random Access Memory (SDRAM) Controller is a general-purpose memory controller that interfaces with industry standard DDR/DDR2 memory devices/modules and provides a generic command interface to user applications. This core reduces the efforts required to integrate the DDR/DDR2 memory controller with the remainder of the application and minimizes the need to deal with the DDR/DDR2 memory interface. This core utilizes dedicated DDR input and output registers in the Lattice devices to meet the requirements for high-speed double data rate transfers. The timing parameters for a memory device or module can be set through the signals that are input to the core as a part of the configuration interface. This capability enables effortless switching among different memory devices by updating the timing parameters to suit the application without generating a new core configuration.

Throughout this user's guide, the term 'DDR' is used to represent the first-generation DDR memory. Since this document covers both the Lattice DDR and DDR2 memory controller IP cores, use of the term 'DDR' indicates both DDR and DDR2.

#### **Quick Facts**

Table 1-1 gives quick facts about the DDR IP core for MachXO2™ devices.

Table 1-1. DDR IP Core Quick Facts

|                        |                        | DDR IP Configuration                               |                   |                              |  |  |

|------------------------|------------------------|----------------------------------------------------|-------------------|------------------------------|--|--|

|                        |                        | x16 1cs                                            | x16 1cs           | x16 1cs                      |  |  |

| Device Family supporte |                        |                                                    | MachXO2           |                              |  |  |

| Core Requirements      | Minimal Device needed  | LC                                                 | MXO2-2000HC-6FTG2 | 256CES                       |  |  |

|                        | Targeted Device        | LCMXO2-2000HC-<br>6FTG256CES                       |                   | LCMXO2-7000HC-<br>6FTG256CES |  |  |

|                        | Data Path Width        | 16                                                 |                   |                              |  |  |

| Resource Utilization   | LUTs                   | 1200                                               |                   |                              |  |  |

|                        | sysMEM EBRs            | 0                                                  |                   |                              |  |  |

|                        | Registers              | 1150                                               |                   |                              |  |  |

|                        | Lattice Implementation | n Lattice Diamond™ 1.0 or ispLEVER® 8.1            |                   |                              |  |  |

| Design Tool Compant    | Synthesis              | Synopsys® Synplify™ Pro for Lattice D-2009.12L-1   |                   |                              |  |  |

| Design Tool Support    | Circulation            | Aldec <sup>®</sup> Active-HDL™ 8.2 Lattice Edition |                   |                              |  |  |

|                        | Simulation             | Mentor Graphics® ModelSim™ SE 6.3F                 |                   |                              |  |  |

Table 1-2 gives quick facts about the DDR2 IP core for MachXO2 devices.

#### Table 1-2. DDR2 IP Core Quick Facts

|                         |                        | DDR2 IP Configuration                 |                                                 |                              |  |  |

|-------------------------|------------------------|---------------------------------------|-------------------------------------------------|------------------------------|--|--|

|                         |                        | x16 1cs                               | x16 1cs                                         | x16 1cs                      |  |  |

| Device Family supported |                        |                                       | MachXO2                                         |                              |  |  |

| Core Requirements       | Minimal Device needed  | LC                                    | MXO2-2000HC-6FTG                                | 256CES                       |  |  |

|                         | Targeted Device        | LCMXO2-2000HC-<br>6FTG256CES          | LCMXO2-4000HC-<br>6FTG256CES                    | LCMXO2-7000HC-<br>6FTG256CES |  |  |

|                         | Data Path Width        | 16                                    |                                                 |                              |  |  |

| Resource Utilization    | LUTs                   | 1325                                  |                                                 |                              |  |  |

|                         | sysMEM EBRs            | ysMEM EBRs 0                          |                                                 |                              |  |  |

|                         | Registers              | 1200                                  |                                                 |                              |  |  |

|                         | Lattice Implementation | Latti                                 | ce Diamond 1.0 or ispl                          | LEVE® 8.1                    |  |  |

| Design Tool Support     | Synthesis              |                                       | Synopsys® Synplify Pro for Lattice D-2009.12L-1 |                              |  |  |

| Design 1001 Support     | Simulation             | Aldec® Active-HDL 8.2 Lattice Edition |                                                 |                              |  |  |

|                         | Simulation             | Mentor Graphics ModelSim™ SE 6.3F     |                                                 |                              |  |  |

#### **Features**

- Interfaces to industry standard DDR/DDR2 SDRAM devices and modules

- MachXO2 devices support DDR2 performance upto 266 Mbps. Although DDR2 SDRAM standard (JESD79-2F, www.jedec.org/standards-documents/docs/jesd-79-2-e) supports 400 Mbps and higher speeds, Micron Technology, Inc. (and possibly others) support operation below 400 Mbps.

- Programmable burst lengths of 2, 4 or 8 for DDR and 4 or 8 for DDR2

- Programmable CAS latency of 2 or 3 cycles for DDR and 3, 4, 5 or 6 cycles for DDR2

- Intelligent bank management to optimize performance by minimizing ACTIVE commands

- Supports all JEDEC standard DDR commands

- Two-stage command pipeline to improve throughput

- Supports unbuffered DIMM

- · Supports all common memory configurations

- SDRAM data path width of 16 bits max.

- Variable address widths for different memory devices

- Up to 8 (DDR) or 4 (DDR2) chip selects for multiple SO/DIMM support

- Programmable memory timing parameters

- Byte-level writing through data mask signals

# **Functional Description**

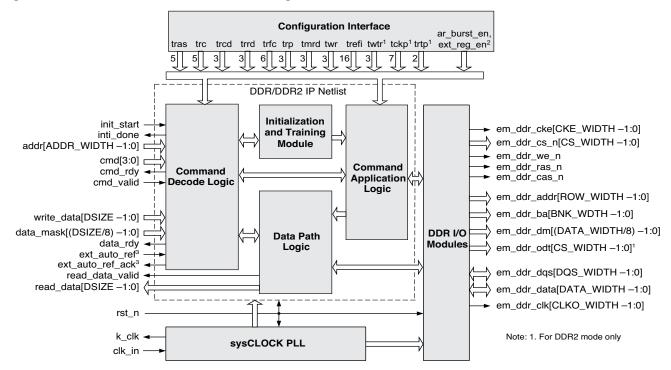

The DDR memory controller consists of two major parts, the encrypted netlist and I/O modules. The encrypted netlist comprises several internal blocks, as shown in Figure 2-1. The device architecture-dependent I/O modules are provided in RTL form. This section briefly describes the operation of each of these blocks.

Figure 2-1. DDR SDRAM Controller Block Diagram

## **Command Decode Logic**

The Command Decode Logic (CDL) block accepts the user commands from the local interface. The accepted command is decoded to determine how the core will act to access the memory. When an accepted command is decoded as a write command, the CDL block asks the user logic to provide the write data. Once it receives the write data from the user logic, the CDL block delivers a write command to the Command Application Logic (CAL) block and the data is sent to the Data Path Logic (DPL) block. Similarly, when the accepted command is a read command, the CDL block sends a read command to the DPL block to generate a read command on the memory interface. The data read from memory is presented to the local user interface.

Intelligent bank management logic tracks the open/close status of every bank and stores the row address of every open bank. This information is used to reduce the number of PRECHARGE and ACTIVE commands issued to the memory. The controller also utilizes two pipelines to improve throughput. One command in the queue is decoded while another is presented at the memory interface.

## **Configuration Interface**

The Configuration Interface (CI) block provides the DDR memory controller with the core reconfiguration capability for the memory timing parameters and other core configuration inputs. The configuration interface for the memory timing parameters can be enabled or disabled via a user parameter. When enabled, the DDR memory controller core can be reconfigured with an updated set of the memory timing parameters in the parameter file without generating a new IP core. When disabled, the reconfiguration logic is permanently removed from the core. It is generally expected that the IP core performance will be improved due to a lower utilization.

## sysCLOCK PLL

The sysCLOCK<sup>™</sup> PLL block generates the clocks used in all blocks in the memory controller core. If an external clock generator is to be used, it is possible to remove this block from the IP core structure.

## **Data Path Logic**

The DPL block interfaces with the DDR I/O modules and is responsible for generation of the read data and read data valid signal in the read operation mode. This block implements the logic to ensure that the data read from the memory is transferred to the local user interface in a deterministic and coherent manner. The write data does not go through the DPL block; it is directly transferred to the Command Application Logic (CAL) block for the write operation mode. The implementation of the DPL block is also device dependent.

#### **Initialization State Machine**

The Initialization State Machine (ISM) block performs the DDR memory initialization sequence defined by JEDEC. Although the memory initialization must be done after the power-up, it is the user's responsibility to provide a user input to the block to start the memory initialization sequence. The ISM block provides an output that indicates the completion of the sequence to the local user interface.

## **Command Application Logic**

The CAL block accepts the decoded commands from the Command Decode Logic on two separate queues. These commands are translated to the memory commands in a way that meets the timing requirements of the memory device. The CI block provides the memory timing parameters to the CAL block so that the timing requirements are satisfied during the command translations. Commands in the two stage queues are pipelined to maximize the throughput on the memory interface. The CDL and the CAL blocks work in parallel to fill and empty the queues respectively.

#### **DDR I/O Modules**

The DDR I/O modules are directly connected to the memory interface providing all required DDR ports for memory access. They convert the single data rate (SDR) data to DDR data for write operations and perform the DDR to SDR conversion for read operations. The I/O modules utilize the dedicated DDR I/O logic and are designed to reliably drive and capture the data on the memory interface.

# **Signal Descriptions**

Table 2-1 describes the user interface and memory interface signals at the top level.

Table 2-1. DDR SDRAM Memory Controller Top-Level I/O List

| Port Name                 | Active<br>State | I/O   | Description                                                                                                                 |  |

|---------------------------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Local User Interface      |                 | •     |                                                                                                                             |  |

| clk_in                    | N/A             | Input | Reference clock. It is connected to the PLL input.                                                                          |  |

| rst_n                     | Low             | Input | Asynchronous reset. It resets the entire core when asserted.                                                                |  |

| init_start                | High            | Input | Initialization start. It should be asserted at least 200 µs after the power-on reset to initiate the memory initialization. |  |

| cmd[3:0]                  | N/A             | Input | User command input to the memory controller.                                                                                |  |

| cmd_valid                 | High            | Input | Command and address valid input. When asserted, the addr and cmd inputs are validated.                                      |  |

| addr[ADDR_WIDTH -1:0]     | N/A             | Input | User address input to the memory controller.                                                                                |  |

| write_data[DSIZE -1:0]    | N/A             | Input | Write data input from user logic to the memory controller.                                                                  |  |

| data_mask[(DSIZE/8) -1:0] | High            | Input | Data mask input for write_data. Each bit masks the corresponding byte on the write_data bus, in order                       |  |

| ext_auto_ref              | High            | Input | User auto-refresh control input. This port is enabled when EXT_AUTO_REF is defined.                                         |  |

Table 2-1. DDR SDRAM Memory Controller Top-Level I/O List (Continued)

| Port Name                      | Active<br>State | I/O    | Description                                                                                                               |

|--------------------------------|-----------------|--------|---------------------------------------------------------------------------------------------------------------------------|

| k_clk                          | N/A             | Output | System clock output. The user logic uses this as a system clock unless an external clock generator is used.               |

| init_done                      | High            | Output | Initialization done output. It is asserted for one clock cycle when the core completes the memory initialization routine. |

| ext_auto_ref_ack               | High            | Output | User auto-refresh control acknowledge output. This port is enabled when EXT_AUTO_REF is defined.                          |

| cmd_rdy                        | High            | Output | Command ready output. When asserted, it indicates the core is ready to accept the next command and address.               |

| data_rdy                       | High            | Output | Data ready output. When asserted, it indicates the core is ready to receive the write data.                               |

| read_data[DSIZE -1:0]          | N/A             | Output | Read data output from the memory to the user logic.                                                                       |

| read_data_valid                | High            | Output | Read data valid output. When asserted, it indicates the data on the read_data bus is valid.                               |

| DDR SDRAM Memory Interface     |                 |        |                                                                                                                           |

| em_ddr_clk[CLKO_WIDTH -1:0]    | N/A             | Output | DDR memory clock generated by the memory controller.                                                                      |

| em_ddr_cke[CKE_WIDTH -1:0]     | High            | Output | DDR memory clock enable generated by the memory controller.                                                               |

| em_ddr_addr[ROW_WIDTH -1:0]    | N/A             | Output | DDR memory address. It has the multiplexed row and column address for the memory.                                         |

| em_ddr_ba[BNK_WDTH -1:0]       | N/A             | Output | DDR memory bank address.                                                                                                  |

| em_ddr_data[DATA_WIDTH -1:0]   | N/A             | In/Out | DDR memory bi-directional data bus.                                                                                       |

| em_ddr_dm[(DATA_WIDTH/8) -1:0] | High            | Output | DDR memory write data mask. It is used to mask the byte lanes for byte level write control.                               |

| em_ddr_dqs[(DQS_WIDTH -1:0]    | N/A             | In/Out | DDR memory bi-directional data strobe. This strobe signal is associated with either 4 or 8 data pads.                     |

| em_ddr_cs_n[CS_WIDTH -1:0]     | Low             | Output | DDR memory chip select.                                                                                                   |

| em_ddr_cas_n                   | Low             | Output | DDR memory column address strobe.                                                                                         |

| em_ddr_ras_n                   | Low             | Output | DDR memory row address strobe.                                                                                            |

| em_ddr_we_n                    | Low             | Output | DDR memory write enable.                                                                                                  |

| em_ddr_odt[CS_WIDTH -1:0]      | High            | Output | DDR memory on-die termination control. This output is present only in the DDR2 mode.                                      |

# **Using the Local User Interface**

The local user interface of the DDR memory controller IP core consists of four independent functional groups:

- Initialization and Auto-Refresh Control

- · Command and Address

- Data Write

- Data Read

Each functional group and its associated local interface signals are listed in Table 2-2.

Table 2-2. Local User Interface Functional Groups

| Functional Group                        | Signals                                               |

|-----------------------------------------|-------------------------------------------------------|

| Initialization and Auto-Refresh Control | init_start, init_done, ext_auto_ref, ext_auto_ref_ack |

| Command and Address                     | addr, cmd, cmd_rdy, cmd_valid                         |

| Data Write                              | data_rdy, write_data, data_mask                       |

| Data Read                               | read_data, read_data_valid                            |

#### **Initialization and Auto-Refresh Control**

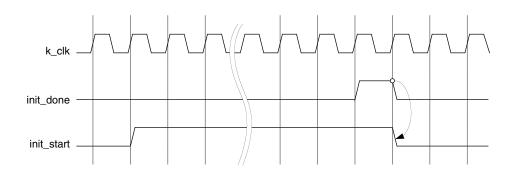

The DDR memory devices must be initialized before the memory controller can access them. The memory controller starts the memory initialization sequence when the init\_start signal is asserted by the user interface. The user must wait at least 200 µs after the power-up cycle is completed and the system clock is stabilized, and then generate the initialization start input to the core. Once asserted, the init\_start signal needs to be held high until the initialization process is completed. The init\_done signal is asserted high for one clock cycle when the core has completed the initialization and training sequence and is now ready to access the memory. The init\_start signal must be deasserted as soon as init\_done is asserted. The memory initialization is required only once after the system reset. Note that the core will operate with the default memory configuration initialized in this process if the user does not program the MR and/or EMR registers. Figure 2-2 shows the timing diagram of the initialization control signals.

Figure 2-2. Timing of Memory Initialization Control

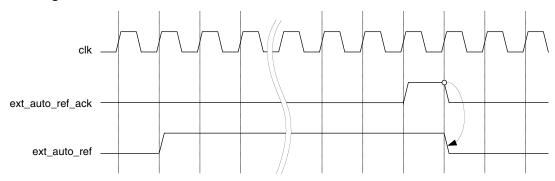

The memory controller core provides the user auto-refresh control feature. This feature can be enabled by the External Auto Refresh Port option. It is a useful function for applications that need to have a complete control on the DDR interface in order to avoid unwanted intervention caused by the memory refresh operations. Once enabled, ext\_auto\_ref is asserted by a user to force the core to generate a set of Refresh commands in a burst. The number of Refresh commands in a burst is defined by the Auto Refresh Burst Count option. The ext\_auto\_ref\_ack signal is asserted high for one clock cycle to indicate that the core has generated the Refresh commands. The ext\_auto\_ref signal can be deasserted once the acknowledge signal is detected as shown in Figure 2-3.

Figure 2-3. Timing of External Auto Refresh Control

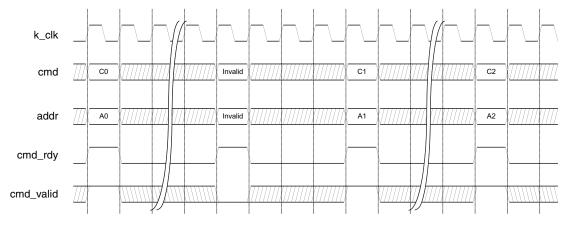

#### **Command and Address**

Once the memory initialization is done, the core waits for user commands that will access the memory. The user logic needs to provide the command and address to the core along with the control signals. The commands and addresses are delivered to the core using the procedure described below:

- 1. The memory controller core tells the user logic that it is ready to receive a command by asserting the cmd\_rdy signal for one clock cycle.

- 2. If the core finds the cmd\_valid signal asserted by the user logic while it is asserting cmd\_rdy, it takes the cmd input as a valid user command. The core also accepts the addr input as a valid start address or mode register programming data depending on the command type. If cmd\_valid is not asserted, the cmd and addr inputs become invalid and the core ignores them.

- 3. The cmd, addr and cmd\_valid inputs become "don't care" while cmd\_rdy is deasserted.

- The cmd\_rdy signal is asserted again to take the next command.

The timing of the command and address group is shown in Figure 2-4. The core will prevent cmd\_rdy from being asserted when two queues in CDL are both occupied, if any queue in CDL is empty, the cmd\_rdy will be asserted.

Figure 2-4. Timing of Command and Address

Each command on the cmd bus must be a valid command. Lattice defines the valid memory commands as shown in Table 2-3. All other values are reserved and considered invalid.

Table 2-3. Defined User Commands

| Command                   | Mnemonic | cmd[3:0] |

|---------------------------|----------|----------|

| Read                      | READ     | 0001     |

| Write                     | WRITE    | 0010     |

| Read with Auto Precharge  | READA    | 0011     |

| Write with Auto Precharge | WRITEA   | 0100     |

| Powerdown                 | PDOWN    | 0101     |

| Load Mode Register        | LOAD_MR  | 0110     |

| Self Refresh              | SELF_REF | 0111     |

#### **Data Write**

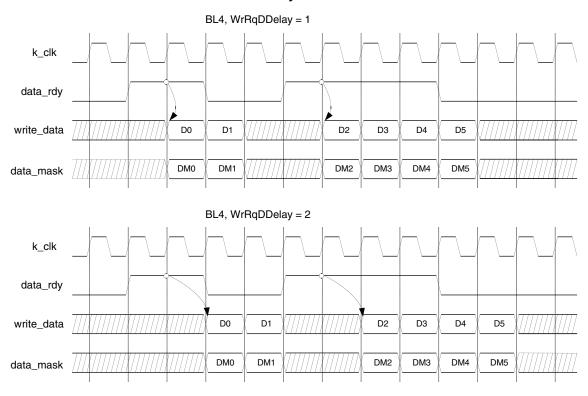

After the WRITE command is accepted, the memory controller core asserts the data\_rdy signal when it is ready to receive the write data from the user logic to be written into the memory. Since the duration from the time a write command is accepted to the time the data\_rdy signal is asserted is not fixed, the user logic needs to monitor the data\_rdy signal to detect when it is asserted. Once data\_rdy is asserted, the core expects valid data on the write\_data bus one or two clock cycles after the data\_rdy signal is asserted. The write data delay is programmable by the user parameter, WrRqDDelay, providing flexible back-end application support. For example, setting WrRqDDelay = 2 ensures that the core takes the write data out in proper time when the local user interface of the core is connected to a synchronous FIFO module inside the user logic. Figure 2-5 shows two examples of the local user interface data write timing. Both cases are in the BL4 mode. The upper diagram shows the case of one clock cycle delay of write data, while the lower one displays a two clock-cycle delay case. The memory controller considers D0, DM0 through D5, DM5 valid write data.

Figure 2-5. One-Clock vs. Two-Clock Write Data Delay

#### **Data Read**

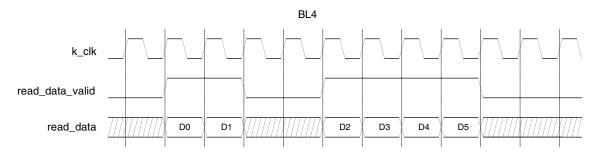

When the READ command is accepted, the memory controller core accesses the memory to read the addressed data and brings it back to the local user interface. Once the read data is available on the local user interface, the memory controller core asserts the read\_data\_valid signal to tell the user logic that the valid read data is on the read\_data bus. The read data timing on the local user interface is shown in Figure 2-6.

Figure 2-6. Read Data Timing on Local User Interface

## Read/Write with Auto Precharge

The DDR2 IP core automatically closes (precharges) and opens rows according to the user memory address accesses. Therefore, the READA and WRITEA commands are not used for most applications. The commands are provided to comply to the JEDEC DDR2 specification.

## **Local-to-Memory Address Mapping**

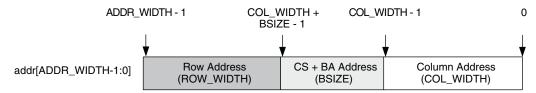

Mapping local addresses to memory addresses is an important part of a system design when a memory controller function is implemented. Users must know how the local address lines from the memory controller connect to those address lines from the memory because proper local-to-memory address mapping is crucial to meet the system requirements in applications such as a video frame buffer controller. Even for other applications, careful address mapping is generally necessary to optimize the system performance. On the memory side, the address (A), bank address (BA) and chip select (CS) inputs are used for addressing a memory device. Users can obtain this information from the memory device data sheet. Figure 2-7 shows the local-to-memory address mapping of the Lattice DDR memory controller cores.

Figure 2-7. Local-to-Memory Address Mapping for Memory Access

ADDR\_WIDTH is calculated by the sum of COL\_WIDTH, ROW\_WIDTH and BSIZE. BSIZE is determined by the sum of the bank address size and chip select address size. For 4- or 8-Bank DDR2 devices, the bank address size is 2 or 3, respectively. When the number of chip select is 1, 2 or 4, the chip select address size becomes 0, 1, or 2, respectively. An example of the address mapping is shown in Table 2-4 and Figure 2-8.

Table 2-4. An Example of Address Mapping

| User Selection Name        | User Value | Parameter Name | Parameter Value | Actual Line Size | Local Address Map |

|----------------------------|------------|----------------|-----------------|------------------|-------------------|

| Row Size                   | 14         | ROW_WIDTH      | 14              | 14               | addr[28:15]       |

| Column Size                | 11         | COL_WIDTH      | 11              | 11               | addr[10:0]        |

| Bank Size                  | 8          | BNK_WDTH       | 3               | 3                | addr[13:11]       |

| Chip Select Width          | 2          | CS_WIDTH       | 2               | 1                | addr[14]          |

| Total Local Address Line S | Size       | ADDR_WIDTH     | 29              | 29               | addr[28:0]        |

Figure 2-8. Mapped Address for the Example

|    |                  | 14             |                | 10 |                     | 0 |

|----|------------------|----------------|----------------|----|---------------------|---|

|    | Row Address (14) | CS Addr<br>(1) | BA Addr<br>(3) |    | Column Address (11) |   |

| 28 | 15               |                | 13 1           | 1  |                     |   |

## **Mode Register Programming**

The DDR SDRAM memory devices are programmed using the mode register (MR) and extended mode registers (EMR). The bank address bus (em\_ddr\_ba) is used for choosing one of the MR or EMR registers, while the programming data is delivered through the address bus (em\_ddr\_addr). The memory data bus cannot be used for the MR/EMR programming.

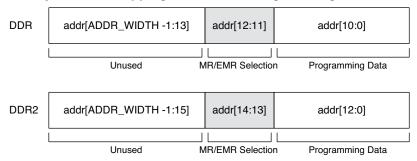

The Lattice DDR memory controller core uses the local address bus, addr, to program these registers. It uses different address mapping from the address mapping for memory accesses. The core accepts a user command, LOAD\_MR, to initiate the programming of MR/EMR registers. When LOAD\_MR is applied on the cmd bus, the user logic must provide the information for a target mode register and the programming data on the addr bus. When the target mode register is programmed, the memory controller core is also configured to support the new memory setting. Figure 2-9 shows how the local address lines are allocated for the programming of memory registers.

Figure 2-9. Local-to-Memory Address Mapping for MR/EMR Programming

The register programming data is provided through the lower side of the addr bus starting from the bit 0 for LSB. The programming data requires eleven (DDR mode) or thirteen (DDR2 mode) bits of the local address lines. Two more bits are needed to choose a target register as listed in Table 2-5. All other upper address lines are unused during the command patch cycle for the LOAD\_MR command.

Table 2-5. Mode Register Selection Using Bank Address

|                   | Local Address     |                    |  |  |  |

|-------------------|-------------------|--------------------|--|--|--|

| Mode Register     | DDR (addr[12:11]) | DDR2 (addr[14:13]) |  |  |  |

| MR                | 00                | 00                 |  |  |  |

| EMR               | 01                | 01                 |  |  |  |

| EMR2 <sup>1</sup> | _                 | 10                 |  |  |  |

| EMR3 <sup>1</sup> | _                 | 11                 |  |  |  |

<sup>1.</sup> DDR2 mode only

Figure 2-10 shows the use of local address for typical DDR2 memory configurations. The DDR memory configuration is accomplished the same way, except that it accesses only two registers, MR and EMR. Starting from DDR/DDR2 version 6.7, some of the registers such as Burst Type, Burst Length, CAS Latency and others can be configured directly from the IPexpress™ GUI for custom initialization.

The initialization default values for all mode registers are listed in Table 2-6.

Table 2-6. Initialization Default Values for DDR/DDR2 Mode Registers

| Туре                                       | Registers                     | Value  | Description           | Local address        |

|--------------------------------------------|-------------------------------|--------|-----------------------|----------------------|

| DDD MD (DAI1:01 00)                        | Burst Length <sup>1</sup>     | 3'b010 | BL = 4                | addr[2:0]            |

|                                            | Burst Type <sup>1</sup>       | 1'b0   | Sequential            | addr[3]              |

|                                            | Cas Latency <sup>1</sup>      | 3'b010 | CL = 2 Cycles         | addr[6:4]            |

| DDR MR (BA[1:0] = 00)                      | Test Mode                     | 1'b0   | Normal                | addr[7]              |

|                                            | DLL Reset                     | 1'b1   | DLL Reset = Yes       | addr[8]              |

|                                            | All Others                    | 0      |                       | addr[ROW_WIDTH-1:8]  |

|                                            | DLL                           | 1'b0   | DLL Enable            | addr[0]              |

| DDR EMR (BA[1:0] = 01)                     | Drive Strength                | 1'b0   | Normal                | addr[1]              |

|                                            | All Others                    | 0      |                       | addr[ROW_WIDTH-1:2]  |

|                                            | Burst Length <sup>1</sup>     | 3'b010 | BL = 4                | addr[2:0]            |

|                                            | Burst Type <sup>1</sup>       | 1'b0   | Sequential            | addr[3]              |

|                                            | Cas Latency <sup>1</sup>      | 3'b100 | CL = 4 Cycles         | addr[6:4]            |

| DDR2 MR (BA[1:0] = 00 or                   | Test Mode                     | 1'b0   | Normal                | addr[7]              |

| BA[2:0]=000)                               | DLL Reset                     | 1'b1   | DLL Reset = Yes       | addr[8]              |

|                                            | WR Recovery <sup>1</sup>      | 3'b010 | 3 Cycles              | addr[11:9]           |

|                                            | Power Down Exit <sup>1</sup>  | 1'b0   | Fast                  | addr[12]             |

|                                            | All Others                    | 0      |                       | addr[ROW_WIDTH-1:13] |

|                                            | DLL                           | 1'b0   | DLL Enable            | addr[0]              |

|                                            | Drive Strength                | 1'b0   | Normal                | addr[1]              |

|                                            | RTT0 <sup>1</sup>             | 1'b0   | Disabled with RTT1=0  | addr[2]              |

|                                            | Additive Latency <sup>1</sup> | 3'b011 | 3 Cycles              | addr[5:3]            |

| DDR2 EMR (BA[1:0] = 01 or                  | RTT1 <sup>1</sup>             | 1'b0   | Disabled with RTT0=0  | addr[6]              |

| BA[2:0]=001)                               | OCD                           | 3'b000 | OCD Not Applicable    | addr[9:7]            |

|                                            | DQS Mode                      | 1'b1   | Differential Disabled | addr[10]             |

|                                            | RDQS                          | 1'b0   | Disable               | addr[11]             |

|                                            | Outputs                       | 1'b0   | Enable                | addr[12]             |

|                                            | All Others                    |        |                       | addr[ROW_WIDTH-1:13] |

| DDR2 EMR2 (BA[1:0] = 10 or<br>BA[2:0]=010) | All                           | 0      |                       | addr[ROW_WIDTH-1:0]  |

#### Table 2-6. Initialization Default Values for DDR/DDR2 Mode Registers (Continued)

| Туре                                       | Registers | Value | Description | Local address       |

|--------------------------------------------|-----------|-------|-------------|---------------------|

| DDR2 EMR3 (BA[1:0] = 11 or<br>BA[2:0]=011) | All       | 0     |             | addr[ROW_WIDTH-1:0] |

<sup>1.</sup> This register can be initialized with a custom value through the IPexpress GUI.

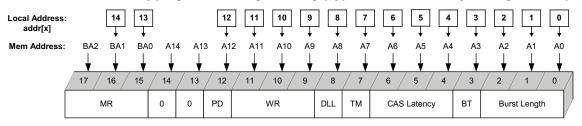

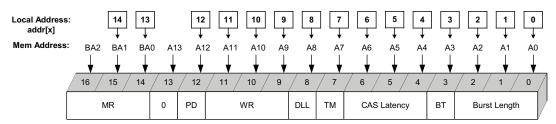

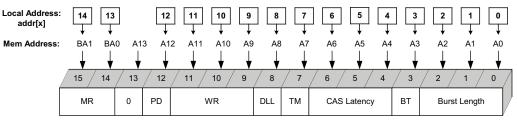

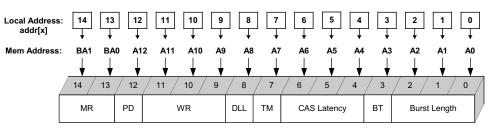

## Figure 2-10. Local Address Mapping for MR Programming (Typical DDR2 Memory Configurations)

Row Size = 15, Bank Size = 8 (2Gb)

Row Size = 14, Bank Size = 8 (1Gb)

Row Size = 14, Bank Size = 4 (512Mb)

Row Size = 13, Bank Size = 4 (256Mb)

## **Memory Interface**

Table 2-7 lists the connections of the DDR interface between the Lattice DDR memory controller core and memory.

Table 2-7. DDR Interface Signal Connections to DDR Memory

|                         |                               | VREF <sup>2</sup> |        | I/O Type                   |           |                                    |

|-------------------------|-------------------------------|-------------------|--------|----------------------------|-----------|------------------------------------|

| Core Port Name          | Memory Port Name <sup>1</sup> | Width             | DDR    | DDR2                       | DDR       | DDR2                               |

| em_ddr_clk <sup>3</sup> | CK, CK#                       | CLKO_WIDTH        | _      | _                          | SSTL25D_I | SSTL18D_I                          |

| em_ddr_cke              | CKE                           | CKE_WIDTH         | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_odt <sup>4</sup> | ODT                           | CS_WIDTH          | _      | _                          | N/A       | SSTL18_I                           |

| em_ddr_cs_n             | CS#                           | CS_WIDTH          | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_ras_n            | RAS#                          | 1                 |        | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_cas_n            | CAS#                          | 1                 | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_we_n             | WE#                           | 1                 | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_addr             | A                             | ROW_WIDTH         | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_ba               | BA                            | BNK_WDTH          | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_data             | DQ                            | DATA_WIDTH        | 1.25 V | 0.9 V                      | SSTL25_I  | SSTL18_I                           |

| em_ddr_dm               | DM                            | DATA_WIDTH/8      | _      | _                          | SSTL25_I  | SSTL18_I                           |

| em_ddr_dqs              | DQS                           | DQS_WIDTH         | 1.25 V | 0.9 V or none <sup>5</sup> | SSTL25_I  | SSTL18_I or SSTL18D_I <sup>6</sup> |

<sup>1.</sup> The listed DDR memory port names are from the Micron DDR memory data sheet.

<sup>2.</sup> In the banks with multiple VREFs, only VREF1 is used for DDR memory applications. VREF = VCCIO/2.

<sup>3.</sup> Lattice DDR memory controller core defines only the positive-end signal for the memory clock. The negative-end pad is allocated by the implementation software when a differential I/O type is assigned.

<sup>4.</sup> The ODT ports are available only in the DDR2 mode.

<sup>5.</sup> If DQS uses a differential pair, VREF is not required. However, VREF1 is still used for the DQS preamble detection.

<sup>6.</sup> In the DDR2 mode, either single-ended or differential type of DQS can be selected.

# **Parameter Settings**

The IPexpress tool is used to create IP and architectural modules in the Diamond and ispLEVER software. Refer to the IP Core Generation section for a description on how to generate the IP.

Table 3-1 provides the list of user configurable parameters for the DDR/DDR2 IP core. The parameter settings are specified using the DDR/DDR2 IP core Configuration GUI in IPexpress. The numerous IPexpress parameter options are partitioned across multiple GUI tabs as shown in this chapter.

Table 3-1. DDR SDRAM Memory Controller Parameters

| ect Memory - DDR2 ect Memory - DDR | Micron DDR2 512 Mb -5E<br>Custom  Micron DDR 512 Mb -5E<br>Micron DDR 512 Mb -6E<br>Micron DDR 512 Mb -75E<br>Custom | Custom  Micron DDR 512Mb -75E |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------|

| ·                                  | Custom  Micron DDR 512 Mb -5E  Micron DDR 512 Mb -6E  Micron DDR 512 Mb -75E  Custom                                 |                               |

| ect Memory - DDR                   | Micron DDR 512 Mb -6E<br>Micron DDR 512 Mb -75E<br>Custom                                                            | Micron DDR 512Mb -75E         |

|                                    | DDD 400.000                                                                                                          |                               |

| ck                                 | DDR - 133-200<br>DDR2 - 166 -333                                                                                     | 133.333                       |

| mory Data Bus size                 | 16                                                                                                                   | 16                            |

| figuration                         | x8, x16                                                                                                              | x8                            |

| a_rdy to Write Data Delay          | 1, 2                                                                                                                 | 1                             |

| ck Width                           | 1, 2                                                                                                                 | 1                             |

| E Width                            | 1, 2                                                                                                                 | 1                             |

| ed Memory Timing                   | Disable, Enable                                                                                                      | Disable                       |

| Differential DQS1                  | Disable, Enable                                                                                                      | Enable                        |

| ting                               |                                                                                                                      |                               |

| Iress                              |                                                                                                                      |                               |

| v Size                             | 13 - 16                                                                                                              | 13                            |

| umn Size                           | 9 - 11                                                                                                               | 10                            |

| k Size                             | 4, 8 <sup>2</sup>                                                                                                    | 4                             |

| Select width                       | 1, 2, 4                                                                                                              | 1                             |

| r Slot Size                        | 1, 2                                                                                                                 | 1                             |

| R Prog During Init <sup>3</sup>    | Disable, Enable                                                                                                      | Enable                        |

| o Refresh Control                  |                                                                                                                      |                               |

| Refresh Burst Count                | 2-8                                                                                                                  | 8                             |

| ernal Auto Refresh Port            | Disable, Enable                                                                                                      | Disable                       |

| de Register Initial Setting - DDR2 |                                                                                                                      |                               |

| st Length                          | 4, 8                                                                                                                 | 4                             |

| S Latency                          | 2 - 6                                                                                                                | 4                             |

| litive Latency                     | 0 - 4                                                                                                                | 3                             |

| te Recovery                        | 2 - 6                                                                                                                | 3                             |

| _Nom (Ohm)                         | 50 Ohm, 75 Ohm, 150 Ohm,<br>Disable                                                                                  | Disable                       |

| st Type                            | Sequential, Interleaved                                                                                              | Sequential                    |

| . Control for PD                   | Fast End, Slow Exit                                                                                                  | Fast Exit                     |

| erential DQS                       | Enable, Disable                                                                                                      | Enable                        |

| Parameters                                        | Range/Options           | Default Value       |

|---------------------------------------------------|-------------------------|---------------------|

| Mode Register Initial Setting - DDR               |                         |                     |

| Burst Length                                      | 2, 4, 8                 | 4                   |

| CAS Latency                                       | 2, 3                    | 2                   |

| Burst Type                                        | Sequential, Interleaved | Sequential          |

| Timing                                            |                         |                     |

| TRCD                                              | 1 - 7                   | 3                   |

| TRAS                                              | 1 - 31                  | 8                   |

| TRFC                                              | 1 - 63                  | DDR: 14<br>DDR2: 21 |

| TMRD                                              | 1 - 7                   | 2                   |

| TRP                                               | 1 - 7                   | 3                   |

| TRRD                                              | 1 - 7                   | 2                   |

| TRC                                               | 1 - 31                  | 11                  |

| TREFI                                             | 1 - 65536               | 1563                |

| TWTR                                              | 1 - 7                   | 2                   |

| TRTP                                              | 1 - 4                   | 2                   |

| Synthesis & Simulation Tools Option               |                         |                     |

| Support Synplify, Support ModelSim, Support ALDEC | Enable, Disable         | Enable              |

<sup>1.</sup> DDR2 only.

## **Mode Tab**

The Memory Type Selection field is not a user option but is selected by IPexpress when a DDR memory controller core is selected from the IPexpress IP core list. Figure 3-1 shows the contents of the Mode tab.

Figure 3-1. Mode Tab

<sup>2.</sup> DDR has 4 only.

<sup>3.</sup> The EXT\_REG\_EN parameter is effective only in the DDR mode.

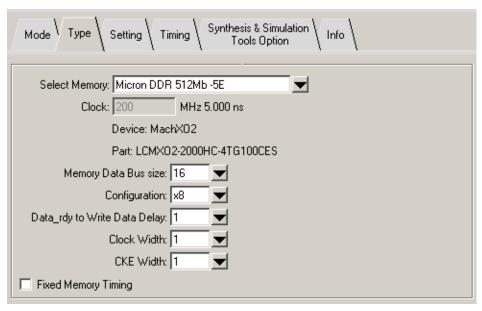

## Type Tab

The Type tab enables users to select various configuration options for the target memory device/ module and the core functional features. Figure 3-2 shows the contents of the Type tab.

Figure 3-2. Type Tab

## **Select Memory**

A predefined DDR memory device is selected by default. The timing parameters for the selected memory are listed in the Timing tab. One or more different speed grade memory devices are also available for easy selection. If the desired memory device requires different timing parameters from the pre-defined ones, the Custom option should be selected.

#### Clock

When a predefined memory is selected, the Clock field displays the corresponding clock speed, and it cannot be modified. With the Custom option selected, a user target speed must be provided.

## **Memory Data Bus Size**

This option means the memory data bus width to which the memory controller core is connected. If a memory module that has a wider data bus than required is to be used, only the required data width has to be selected.

## Configuration

This option is used to select the device configuration of the DIMM. Device configurations x4, x8, and x16 are supported.

## Data\_rdy to Write Data Delay

This option is selected according to the user local back-end application's requirement. The user logic can send the write data to the core with either one-clock cycle or two-clock cycle delay.

#### **Clock Width**

This option sets the number of clocks with which the memory controller drives the memory. The IPexpress tool can generate either one or two memory clocks. Once a DDR memory controller core is generated, more memory clocks can be manually instantiated for those applications that need more than two memory clocks.

#### **CKE Width**

The number of memory clock enable signals is configured using this option. More clock enable signals can also be instantiated by the user.

## **Fixed Memory Timing**

This option disables the memory timing reconfiguration feature for a generated core. When disabled, the IP core only supports the timing parameter set applied at the time of the core generation. This option may provide somewhat improved performance with lower resource utilization by removing the reconfiguration logic from the core. This option should not be selected if it is necessary to support different memory timing parameters without regenerating the core. This option is unchecked by default.

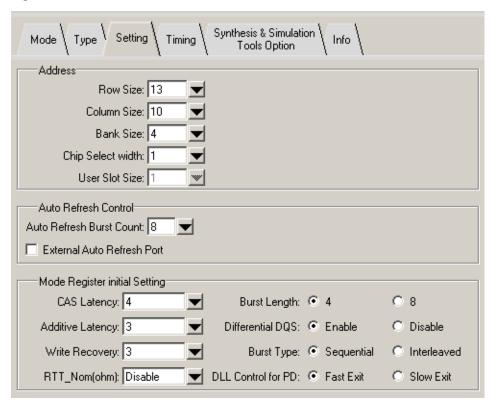

## **Setting Tab**

The target memory size and addressing scheme are determined in the Setting tab. The memory initialization and auto-refresh configurations are also covered in this tab. Figure 3-3 shows the contents of the Setting tab.

Figure 3-3. Setting Tab

#### **Row Size**

This option indicates the row address size for the memory ranging from 13 to 16, which is found in the memory data sheet.

#### Column Size

This option indicates the column address size for the memory ranging from 9 to 11, which is found in the memory data sheet.

#### **Bank Size**

This option indicates the bank address size for the memory. Either 4 or 8 is selected depending on the size and type of the memory to be used with the core.

## **Chip Select Width**

The Lattice memory controller cores follow the JEDEC specifications for DDR/DDR2 SDRAM memories supporting two different sets of chip select signaling. The DDR mode provides up to eight chip selects supporting up to four memory modules. The DDR2 mode provides up to four chip selects supporting up to two DDR2 memory modules. Note that this option does not indicate the number of memory modules but the number of actual chip select signals.

#### **User Slot Size**

This option indicates the number of physical DIMM or SODIMM slots. The information of user slot number is used for the memory controller core to properly drive the ODT (On-Die Termination) signals to the DDR2 memory modules. Since DDR memory does not have ODT, this option is available only to the DDR2 mode with a choice of one or two slots.

## **EMR Prog During Init**

Once disabled, the core does not program the EMR during the initialization; it can then be programmed after the initialization process is done. This option is required only in the DDR mode because the core must program the EMR during the initialization in the DDR2 mode. The default value for this option is Program. Keep the default for the DDR2 mode core configurations.

#### **Auto Refresh Burst Count**

This option indicates the number of Refresh commands that the memory controller core generates at once. DDR memories have at least an 8-deep Refresh command queue following the JEDEC specification and Lattice DDR memory controller cores support up to eight Refresh commands in one burst. It is recommended that the maximum number be used if the DDR interface throughput is a major concern of the system. If it is set to 8, for example, the core will send a set of eight consecutive Refresh commands to the memory at once when it reaches the time period of the eight refresh intervals (t<sub>REFI</sub> x 8). Bursting refresh cycles increases the DDR bus throughput because it helps keep core intervention to a minimum.

#### **External Auto Refresh Port**

This option provides users with the capability of controlling the memory refresh command generation. If this option is disabled, the core takes control of the Refresh command generation according to the memory timing parameter, TREFI. Once enabled, the core adds the external auto refresh control ports to the local user interface with which users can take full control of the Refresh command generation.

## **Mode Register Initial Setting**

This option allows the user to program the mode registers during the core initialization process. Not all mode register bits are initialized from this option. Only the mode register configuration bits that are used for normal DDR operations are programmed using this setting. See Table 3-1 for the list of the covered mode register settings. The user does not need to program the mode registers after the core initialization is finished if the mode register is properly configured as desired.

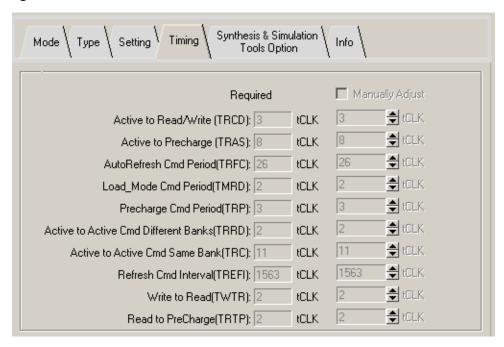

# **Timing Tab**

Lattice DDR memory controller core allows users to customize the memory timing parameters. This can be done when the Custom memory type is selected in the Type tab of the IPexpress GUI. The Manually Adjust box in the Timing tab must also be checked to adjust the parameters. Two timing parameters, TWTR and TRTP, are for the DDR2 mode only while all others are common to both modes. The numbers in the parameter boxes are decimal values indicating the number of clock cycles (t<sub>CLK</sub>). Since the timing numbers available in the memory vendors' data sheets usually are actual time based, conversions from time numbers to clock numbers should be properly made. The conversion is easily made by dividing the time number by the clock period. When a timing parameter is

found to be a minimum value in the data sheet, the calculated number, if not a whole integer, should be the next whole integer to be safe. If it is a maximum value, then only the whole part is taken, and the decimal part is discarded. Figure 3-4 shows the contents of the Timing tab.

Figure 3-4. Timing Tab

The memory timing parameters are listed in Table 3-2.

Note: There is a timing parameter that is not shown in the Timing tab. The TCKP parameter is not a memory timing parameter but a memory controller core parameter used only in the DDR2 mode. It provides the wait cycles during the DDR2 memory initialization. The DDR2 specification requires a minimum of 400 ns wait before the PRE-CHARGE ALL command is executed. This parameter is found in the core parameter file with the default number 'd107, which ensures 400 ns of wait up to 266 MHz speed. Although the wait time can be increased or decreased by adjusting the TCKP parameter, it may not be necessary to modify this parameter in most applications.

Table 3-2. Memory Timing Parameters for DDR Memory Controller

| Signal Name            | Description                                                     |

|------------------------|-----------------------------------------------------------------|

| tras[4:0]              | ACTIVE to PRECHARGE command delay in clock cycles               |

| trc[4:0]               | ACTIVE to ACTIVE/AUTO REFRESH delay in clock cycles             |

| trcd[2:0]              | ACTIVE to READ/WRITE delay in clock cycles                      |

| trrd[2:0]              | ACTIVE bank A to ACTIVE bank B delay in clock cycles            |

| trfc[5:0]              | REFRESH command period in clock cycles                          |

| trp[2:0]               | PRECHARGE command period in clock cycles                        |

| tmrd[2:0]              | LOAD MODE REGISTER command period in clock cycles               |

| trefi[15:0]            | Refresh Interval in clock cycles                                |

| trtp[1:0]              | READ to PRECHARGE delay, DDR2 mode only                         |

| twtr[2:0]              | WRITE to READ delay, DDR2 mode only                             |

| tckp[6:0] <sup>1</sup> | Wait before PRECHARGE ALL during initialization, DDR2 mode only |

<sup>1.</sup> Not available in the IPexpress GUI.

## **Synthesis & Simulation Tools Option Tab**

The Lattice DDR memory controller cores support multiple synthesis and simulation tool flows. This tab allows users to deselect the unwanted flow supports. Figure 3-5 shows the contents of the Synthesis & Simulation Tools Option tab.

Figure 3-5. Synthesis & Simulation Tools Option Tab

#### Info Tab

The number of pins required on the DDR bus and the local user interface are reported in the Info tab. Figure 3-6 shows the contents of the Info tab.

Figure 3-6. Info Tab

#### **Memory I/F Pins**

The numbers displayed indicate the total required number of DDR bus I/O pads.

#### **User I/F Pins**

The numbers displayed indicate the total required number of local user interface signals. Although these signals usually do not use I/O pads in user applications, this information can indicate whether or not the evaluation project will insert the dummy logic. Note that all local user interface signals also use I/O pads in the core evaluation project.

# **IP Core Generation**

This chapter provides information on licensing the DDR/DDR2 IP core, generating the core using the Diamond or ispLEVER software IPexpress tool, running functional simulation, and including the core in a top-level design. The Lattice DDR/DDR2 IP core can be used in MachXO2 PLDs.

## Licensing the IP Core

An IP license is required to enable full, unrestricted use of the DDR/DDR2 IP core in a complete, top-level design. An IP license that specifies the IP core (DDR/DDR2) and device family (MachXO2) is required to enable full use of the DDR/DDR2 IP core in MachXO2 devices Instructions on how to obtain licenses for Lattice IP cores are given at:

http://www.latticesemi.com/products/intellectualproperty/aboutip/isplevercoreonlinepurchas.cfm

Users may download and generate the DDR/DDR2 IP core and fully evaluate the core through functional simulation and implementation (synthesis, map, place and route) without an IP license. The DDR/DDR2 IP core also supports Lattice's IP hardware evaluation capability, which makes it possible to create versions of the IP core that operate in hardware for a limited time (approximately four hours) without requiring an IP license. See the Hardware Evaluation section for further details. However, a license is required to enable timing simulation, to open the design in the Diamond or ispLEVER EPIC tool, and to generate bitstreams that do not include the hardware evaluation timeout limitation.

## **Getting Started**

The DDR/DDR2 IP core is available for download from the Lattice IP Server using the IPexpress tool. The IP files are automatically installed using ispUPDATE technology in any customer-specified directory. After the IP core has been installed, the IP core will be available in the IPexpress GUI dialog box shown in Figure 4-1.

The IPexpress tool GUI dialog box for the DDR/DDR2 SDRAM IP core is shown in Figure 4-1. To generate a specific IP core configuration the user specifies:

- Project Path Path to the directory where the generated IP files will be loaded.

- File Name "username" designation given to the generated IP core and corresponding folders and files.

- (Diamond) Module Output Verilog or VHDL.

- (ispLEVER) Design Entry Type Verilog HDL or VHDL

- **Device Family** Device family to which IP is to be targeted (e.g. LatticeSCM, Lattice ECP2M, LatticeECP3, etc.). Only families that support the particular IP core are listed.

- Part Name Specific targeted part within the selected device family.