Chipsmall Limited consists of a professional team with an average of over 10 year of expertise in the distribution of electronic components. Based in Hongkong, we have already established firm and mutual-benefit business relationships with customers from, Europe, America and south Asia, supplying obsolete and hard-to-find components to meet their specific needs.

With the principle of "Quality Parts, Customers Priority, Honest Operation, and Considerate Service", our business mainly focus on the distribution of electronic components. Line cards we deal with include Microchip, ALPS, ROHM, Xilinx, Pulse, ON, Everlight and Freescale. Main products comprise IC, Modules, Potentiometer, IC Socket, Relay, Connector. Our parts cover such applications as commercial, industrial, and automotives areas.

We are looking forward to setting up business relationship with you and hope to provide you with the best service and solution. Let us make a better world for our industry!

# Contact us

Tel: +86-755-8981 8866 Fax: +86-755-8427 6832

Email & Skype: info@chipsmall.com Web: www.chipsmall.com

Address: A1208, Overseas Decoration Building, #122 Zhenhua RD., Futian, Shenzhen, China

# WT32i BLUETOOTH AUDIO MODULE

**DATA SHEET**

Tuesday, 22 July 2014

Version 1.21

# Copyright © 2000-2014 Bluegiga Technologies All rights reserved. Bluegiga Technologies assumes no responsibility for any errors which may appear in this manual. Furthermore, Bluegiga Technologies reserves the right to alter the hardware, software, and/or specifications detailed here at any time without notice and does not make any commitment to update the information contained here. Bluegiga's products are not authorized for use as critical components in life support devices or systems. The WRAP is a registered trademark of Bluegiga Technologies

The Bluetooth trademark is owned by the Bluetooth SIG Inc., USA and is licensed to Bluegiga Technologies.

All other trademarks listed herein are owned by their respective owners.

# **VERSION HISTORY**

| VERSION | COMMENT                                                                                           |

|---------|---------------------------------------------------------------------------------------------------|

| 1.0     | First version                                                                                     |

| 1.1     | Added example how to protect the battery by shutting down the regulators at certain voltage level |

| 1.2     | Fixed PCM pin numbering                                                                           |

| 1.21    | Design check list added                                                                           |

# **TABLE OF CONTENTS**

| 1 D | esign (   | Check List                                                                   | 7  |

|-----|-----------|------------------------------------------------------------------------------|----|

| 2 V | VT32i F   | Product Numbering                                                            | 8  |

| 3 B | Block di  | agram                                                                        | 9  |

| 4 P | inout a   | nd Terminal Description                                                      | 10 |

| 5 E | Electrica | al Characteristics                                                           | 13 |

| 5.1 | Abs       | olute Maximum Ratings                                                        | 13 |

| 5.2 | Red       | commended Operating Conditions                                               | 13 |

| 5.3 | Dig       | ital Terminals                                                               | 13 |

| 5.4 | Auc       | lio Characteristics                                                          | 14 |

| 5   | .4.1      | ADC                                                                          | 14 |

| 5   | .4.2      | DAC                                                                          | 15 |

| 5   | .4.3      | A2DP Codecs                                                                  | 15 |

| 5.5 | RF        | Characteristics                                                              | 17 |

| 5   | .5.1      | RF Transceiver                                                               | 17 |

| 5   | .5.2      | Antenna Characteristics                                                      | 18 |

| 5.6 | Cur       | rent Consumption                                                             | 21 |

| 6 P | ower C    | Control and Regulation                                                       | 22 |

| 6.1 | Pro       | tecting the Battery by Configuring the Module to Turn Off at Certain Voltage | 24 |

| 6.2 | Res       | set                                                                          | 25 |

| 6   | .2.1      | Internal POR                                                                 | 25 |

| 7 B | Battery ( | Charger                                                                      | 27 |

| 8 G | PIO ar    | nd AIO Functions                                                             | 28 |

| 8.1 | iWF       | RAP supported GPIO Functions                                                 | 28 |

| 8.2 | Out       | putting Internal Clocks                                                      | 28 |

| 8.3 | Aux       | iliary ADC                                                                   | 29 |

| 8.4 | Sof       | tware I2C Interface                                                          | 29 |

| 9 S | Serial In | terfaces                                                                     | 30 |

| 9.1 | UAI       | RT Interface                                                                 | 30 |

| 9   | .1.1      | Resetting Through UART Break Signal                                          | 31 |

| 9   | .1.2      | UART Configuration While Reset is Active                                     | 31 |

| 9   | .1.3      | UART Bypass Mode                                                             | 31 |

| 9.2 | USI       | 3 Interface                                                                  | 32 |

| 9.3 | Pro       | gramming and Debug Interface (SPI)                                           | 33 |

| 10  | Audio     | Interfaces                                                                   | 34 |

| 10. | 1         | Stereo Audio Codec Interface                                                 | 34 |

| 1   | 0.1.1     | ADC                                                                          | 34 |

| 1   | 012       | DAC                                                                          | 36 |

| 10   | 0.1.3   | Microphone Input                               | 37 |

|------|---------|------------------------------------------------|----|

| 1    | 0.1.4   | Line Input                                     | 38 |

| 10   | 0.1.5   | Output Stage                                   | 39 |

| 10   | 0.1.6   | Mono Operation                                 | 41 |

| 10   | 0.1.7   | Side Tone                                      | 41 |

| 10.2 | 2       | PCM Interface                                  | 41 |

| 10.3 | 3       | I2S Interface                                  | 41 |

| 10.4 | 1       | IEC 60958 Interface                            | 43 |

| 11   | Desig   | n Guidelines                                   | 45 |

| 11.1 | 1       | Audio Layout Guide                             | 45 |

| 1    | 1.1.1   | EMC Considerations                             | 45 |

| 1    | 1.1.2   | Choosing Capacitors and Resistors              | 45 |

| 11.2 | 2       | RF Layout Guide                                | 46 |

| 11.3 | 3       | Example Application Schematics                 | 49 |

| 12   | Physic  | cal Dimensions                                 | 53 |

| 13   | Solde   | ring Recommendations                           | 55 |

| 14   | Packa   | ge                                             | 56 |

| 15   | Certifi | cation Guidance for an End Product Using WT32i | 58 |

| 15.1 | 1       | Bluetooth End Product Listing                  | 58 |

| 15.2 | 2       | CE Approval of an End-Product                  | 58 |

| 15.3 | 3       | FCC Certification of an End Product            | 59 |

| 1    | 5.3.1   | Co-location with Other Transmitters            | 60 |

| 15.4 | 4       | IC Certification of an End Product             | 60 |

| 15.5 | 5       | MIC Japan Certification of an End Product      | 60 |

| 16   | WT32    | i Certifications                               | 60 |

| 16.1 | 1       | Bluetooth                                      | 60 |

| 16.2 | 2       | CE                                             | 60 |

| 16.3 | 3       | FCC                                            | 61 |

| 16.4 | 4       | IC                                             | 62 |

| 10   | 6.4.1   | IC                                             | 62 |

| 16.5 | 5       | MIC Japan                                      | 63 |

| 16.6 | 6       | KCC (South-Korea)                              | 63 |

| 16.7 | 7       | Qualified Antenna Types for WT32i-E            | 63 |

| 47   | Conto   | at Information                                 | 64 |

#### WT32i Bluetooth® Audio Module

#### **DESCRIPTION**

WT32i is an audio specific Bluetooth 3.0 module with excellent radio frequency performance and enhanced audio features. enabling a best in class Bluetooth audio addition experience. In to certified Bluetooth radio and software stack, WT32i also contains a DSP, stereo audio codec, and battery charger making it ideal for fixed and portable audio applications. WT32i includes Bluegiga's iWRAP6 Bluetooth stack software which implements A2DP, AVRCP v.1.5 profiles and supports  $\text{aptX}^{\text{\tiny{(B)}}}$  and AAC audio codecs for stereo audio applications. For hands-free iWRAP6 applications software supports HFP v.1.6, HSP, MAP PBAP and CVC® echo cancellation software. For data communications to Android and iWRAP6 iOS applications also implements *Bluetooth* Serial Port Profile (SPP) and Apple iAP profiles. WT32i is an ideal solution for developers who want to quickly integrate the latest Bluetooth audio technologies without the time and costs typically involved with a Bluetooth audio chipset design.

#### **APPLICATIONS:**

- Stereo speakers and sound bars

- Hi-Fi devices

- Hands-free kits

- Stereo headsets

Figure 1: WT32i Bluetooth Audio Module

#### **KEY FEATURES:**

- Bluetooth 3.0 compliant

- Excellent Radio Performance

- o Transmit power: +6.5 dBm

- o Receiver sensitivity: -90 dBm

- o Link budget: 96.5 dB

- Integrated chip antenna or U.FL antenna connector

- Audio features

- o Integrated DSP

- o 16-bit stereo codec

- o 44.1kHz ADC, 48kHz DAC

- Analog, I2S, PCM, SPDIF, and microphone interfaces

- Optional aptX<sup>®</sup> and AAC stereo audio codecs

- Optional CVC<sup>®</sup> echo cancellation

- Wide Band Speech

- Built-in battery charger

- UART host interface

- 802.11 co-existence interface

- 10 software programmable IO pins

- Operating voltage: 1.8V to 3.6V

- Temperature range: -40C to +85C

- Bluetooth, CE, FCC, IC, Korea and Japan qualified

- Integrated iWRAP6 Bluetooth stack

- o 13 Bluetooth profiles

- Apple iAP1 and iAP2 compatibility

# 1 Design Check List

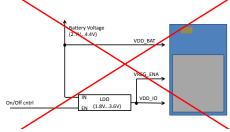

# POWERING THE MODULE

- > Make sure that VRE\_ENA is connected correctly

- Use iWRAP command SET CONTROL VREGEN command to configure the VREG\_ENA pin according to the HW

- Reserve test points for SPI interface for debugging and FW updates

- The internal power on reset does not work properly if the host pulls the reset line low during boot. To prevent this, place a diode to the reset input.

# On/Off cntrl Battery Voltage (2.7V...4.4V) VDD\_BAT VREG\_ENA VREG\_ENA VRD\_IO EN (1.8V...3.6V)

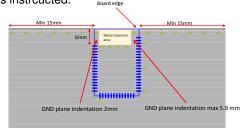

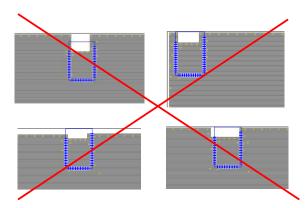

# **RF LAYOUT**

Make sure that the layout for the antenna is done as instrcucted.

Board edge

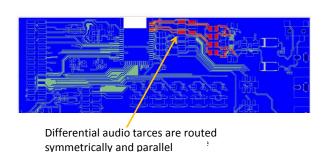

# **AUDIO DESIGN AND LAYOUT**

- > See the example schematics on pages 49 -52

- Avoid using single ended audio traces. Always use differential audio signaling when possible

- Use solid GND plane and make sure that all the GND pins are connected to it by placing a GND via right next to any GND pins.

- When routing single ended audio traces, make sure that the return current (i.e. GND) follows the traces all the way from start to the end

- > DO NOT COMPROMISE AUDIO ROUTING

# 2 WT32i Product Numbering

| Product code     | Description                                                                                                                                                                                       |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WT32i-A-Al6      | WT32i Bluetooth Module with internal chip antenna and iWRAP6 <i>Bluetooth</i> software                                                                                                            |

| WT32i-A-AI6-APTX | WT32i Bluetooth Module with internal chip antenna and aptX® audio codec capable iWRAP6 <i>Bluetooth</i> software.                                                                                 |

| WT32i-A-Al6IAP   | WT32i Bluetooth Module with internal chip antenna and Apple iAP capable iWRAP6 <i>Bluetooth</i> software. Available only to Apple MFI licensees. Contact sales@bluegiga.com for more information. |

| WT32i-E-Al6      | WT32i Bluetooth Module with U.FL connector and iWRAP6 Bluetooth software                                                                                                                          |

| WT32i-E-Al6-APTX | WT32i Bluetooth Module with U.FL connector and aptX® audio codec capable iWRAP6 <i>Bluetooth</i> software.                                                                                        |

| WT32i-E-Al6IAP   | WT32i Bluetooth Module with U.FL connector and Apple iAP capable iWRAP6 <i>Bluetooth</i> software. Available only to Apple MFI licensees. Contact sales@bluegiga.com for more information.        |

| DKWT32i-A        | WT32i development kit                                                                                                                                                                             |

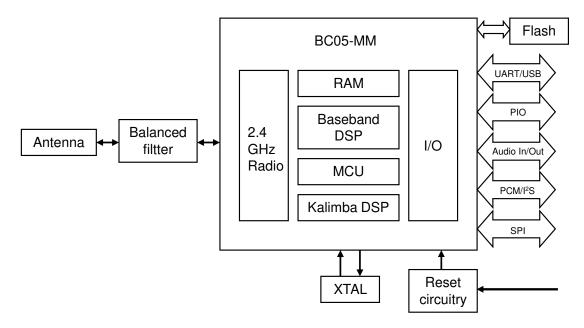

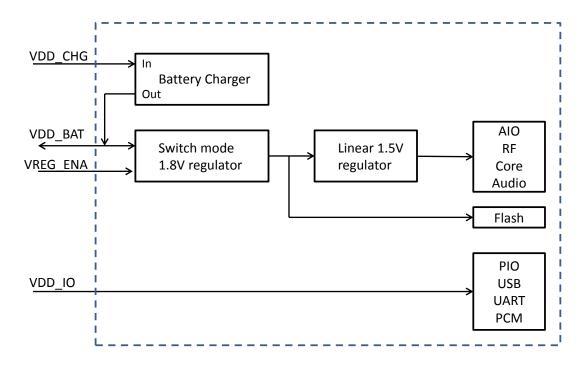

# 3 Block diagram

Figure 2: Block Diagram of WT32i

#### BC05-MM

The BlueCore®5-Multimedia External is a single-chip radio and baseband IC for Bluetooth 2.4GHz systems. It provides a fully compliant Bluetooth v3.0 specification system for data and voice. BlueCore5-Multimedia External contains the Kalimba DSP coprocessor with double the MIPS of BlueCore3-Multimedia External, supporting enhanced audio applications.

#### **XTAL**

Ther reference clock of WT32i is generated with 26 MHz crystal. All BC05-MM internal digital clocks are generated using a phase locked loop, which is locked to the frequency of either the 26 MHz crystal or an internally generated watchdog clock frequency of 1kHz.

#### **RESET CIRCUITRY**

The internal reset circuitry keeps BC05-MM in reset during boot in order for the supply voltages to stabilize. This is to prevent corruption of the flash memory during booting. Please see chapter 6.1 for more detailed description.

#### **BALANCED FILTER**

The internal balanced filter provides optimal impedance matching and band pass filtering in order to achieve lowest possible in-band and out-of-band emissions.

#### **ANTENNA**

The antenna is a ceramic chip antenna with high efficiency. The antenna is insensitive to surrounding dielectric materials and requires only a small clearance underneath which makes it compatible with previous WT32I designs and well suitable for designs with high density.

#### **FLASH**

16 Mbit flash memory is used for storing the Bluetooth protocol stack and Virtual Machine applications. It can also be used as an optional external RAM for memory-intensive applications.

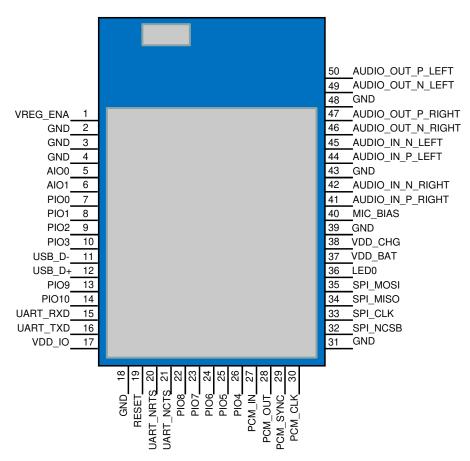

# 4 Pinout and Terminal Description

Figure 3: WT32i

| Pin Number                 | Pin Name | Pad Type                      | Description                                                                              |

|----------------------------|----------|-------------------------------|------------------------------------------------------------------------------------------|

| 1                          | VREG_ENA | Input                         | SW configurable enable pin for the internal regulators                                   |

| 2-4, 18, 31,<br>39, 43, 48 | GND GND  |                               | GND                                                                                      |

| 17                         | VDD_IO   | Power supply                  | 1.7V - 3.6V power supply for the serial interfaces and GPIOs                             |

| 37                         | VDD_BAT  | Power supply / Charger output | 2.7V - 4.4V supply voltage for the internal regulators and output of the battery charger |

| 38                         | VDD_CHG  | Power supply                  | Nominal 5V supply voltage for the battery charger                                        |

**Table 1: Supply Terminal Descriptions**

| Pin<br>Number | Pin Name  | Pin Type                                        | Description                                                                                                                                                                                                                                                                       |  |  |  |

|---------------|-----------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 19            | RESET     | RESET                                           | Active high reset. If not used, leave floating. When connected, make sure that the reset is either pulled high or floating (connected to high impedance) during boot.                                                                                                             |  |  |  |

| 5             | AIO0      |                                                 | AlO0 and AlO1 can be used to read the voltage level through the internal ADC (refer to iWRAP User Guide for details). AlO pins can also be                                                                                                                                        |  |  |  |

| 6             | AIO1      | Configurable I/O                                | configured to be used as general digital IO pins through PS settings. Internal clocks can be routed out through AIO pins by setting corresponding PS settings. Note that the AIO pins are powered from internal 1.5V supply so the maximum voltage level of the AIO pins is 1.5V. |  |  |  |

|               |           |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 7             | PIO0      |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 8             | PIO1      |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 9             | PIO2      |                                                 | General purpose IO's can be configured with                                                                                                                                                                                                                                       |  |  |  |

| 10            | PIO3      |                                                 | iWRAP for various functions. Each IO can be configured individually as output or input with                                                                                                                                                                                       |  |  |  |

| 13            | PIO9      |                                                 | strong or weak pull-up/-down. Using particular PS                                                                                                                                                                                                                                 |  |  |  |

| 14            | PIO10     | Configurable CMOS I/O                           | setting GPIO pins can be used to implement WiFi                                                                                                                                                                                                                                   |  |  |  |

| 22            | PIO8      | -                                               | co-existence signaling between WT32i and a WiFi radio. Software I2C interface can be implemented                                                                                                                                                                                  |  |  |  |

| 23            | PIO7      |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 24            | PIO6      |                                                 | for slow I2C functions such as configuring external                                                                                                                                                                                                                               |  |  |  |

| 25            | PIO5      |                                                 | audio codec or display.                                                                                                                                                                                                                                                           |  |  |  |

| 26            | PIO4      |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

|               |           |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 11            | USB_D-    | I/O                                             | USB data minus                                                                                                                                                                                                                                                                    |  |  |  |

| 12            | USB_D+    | I/O                                             | USB data plus with selectable internal 1.5k pull-up resistor                                                                                                                                                                                                                      |  |  |  |

|               |           |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 15            | UART_RXD  | CMOS Input, weak internal pull-down             | UART data input                                                                                                                                                                                                                                                                   |  |  |  |

| 16            | UART_TXD  | CMOS output, tristate,<br>weak internal pull-up | UART data output                                                                                                                                                                                                                                                                  |  |  |  |

| 20            | UART_NRTS | CMOS output, tristate,<br>weak internal pull-up | UART request to send, active low                                                                                                                                                                                                                                                  |  |  |  |

| 21            | UART_NCTS | CMOS Input, weak internal pull-down             | UART clear to send, active low                                                                                                                                                                                                                                                    |  |  |  |

|               |           |                                                 |                                                                                                                                                                                                                                                                                   |  |  |  |

| 32            | SPI_NCSB  | CMOS Input, weak internal pull-down             | SPI chip select                                                                                                                                                                                                                                                                   |  |  |  |

| 33            | SPI_CLK   | CMOS Input, weak internal pull-down             | SPI clock                                                                                                                                                                                                                                                                         |  |  |  |

| 34 | SPI_MISO | CMOS Input, weak internal pull-down            | SPI data input  |

|----|----------|------------------------------------------------|-----------------|

| 35 | SPI_MOSI | CMOS output, tristate, weak internal pull-down | SPI data output |

|    |          |                                                |                 |

| 36 | LED0     | Open drain output                              | LED driver      |

**Table 2: Terminal Descriptions**

| Pin<br>Number | Pin Name          | Pin Type                                       | Description                                                                                                            |

|---------------|-------------------|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| 40            | MIC_BIAS          | Analog                                         |                                                                                                                        |

| 41            | AUDIO_IN_P_RIGHT  | Analog                                         |                                                                                                                        |

| 42            | AUDIO_IN_N_RIGHT  | Analog                                         |                                                                                                                        |

| 44            | AUDIO_IN_P_LEFT   | Analog                                         |                                                                                                                        |

| 45            | AUDIO_IN_N_LEFT   | Analog                                         |                                                                                                                        |

| 46            | AUDIO_OUT_N_RIGHT | Analog                                         |                                                                                                                        |

| 47            | AUDIO_OUT_P_RIGHT | Analog                                         |                                                                                                                        |

| 49            | AUDIO_OUT_N_LEFT  | Analog                                         |                                                                                                                        |

| 50            | AUDIO_OUT_P_LEFT  | Analog                                         |                                                                                                                        |

|               |                   |                                                |                                                                                                                        |

| 27            | PCM_IN / I2S IN   | CMOS input, weak internal pull-down            | PCM or I2S data input                                                                                                  |

| 28            | PCM_OUT / I2S_OUT | CMOS outptu, tristate, weak internal pull-down | PCM or I2S data output                                                                                                 |

| 29            | PCM_SYNC / I2S_WS | Bidirectional, weak internal down              | PCM sync or I2S word select. WT32i can operate as a PCM/I2S master providing the sync or as a slave receiving the sync |

| 30            | PCM_CLK / I2S_SCK | Bidirectional, weak<br>internal down           | PCM or I2S clock. WT32i can operate as a PCM/I2S master providing the clock or as a slave receiving the clock.         |

**Table 3: Audio Terminal Descriptions**

# 5 Electrical Characteristics

# 5.1 Absolute Maximum Ratings

|                             | Min        | Max        | Unit |

|-----------------------------|------------|------------|------|

| Storage temperature range   | -40        | +85        | °C   |

| Operating temperature range | -40        | +85        | °C   |

| VDD_IO                      | -0.4       | 3.6        | V    |

| VDD_BAT                     | -0.4       | 4.4        | V    |

| VDD_CHG                     | -0.4       | 6.5        | V    |

| Digital Terminal voltages   | VSS - 0.4V | VDD + 0.4V | V    |

| AIO voltages                | VSS - 0.4V | 1.9V       | V    |

**Table 4: Absolute Maximum Ratings**

# 5.2 Recommended Operating Conditions

|                             | Min | Max  | Unit |

|-----------------------------|-----|------|------|

| Storage temperature range   | -40 | +85  | °C   |

| Operating temperature range | -40 | +85  | °C   |

| VDD_IO                      | 1.7 | 3.6  | V    |

| VDD_BAT                     | 2.7 | 4.4  | V    |

| VDD_CHG                     | 0   | 6.5  | V    |

| Digital Terminal voltages   | 0   | VDD  | V    |

| AIO voltages                | 0   | 1.5V | V    |

**Table 5: Recommended Operating Conditions**

# 5.3 Digital Terminals

| Input/Output Characteristic                                       | Min         | Max        | Unit |

|-------------------------------------------------------------------|-------------|------------|------|

| V <sub>IL</sub> input logic level low                             | -0.3        | 0.25 x VDD | V    |

| V <sub>IL</sub> input logic level high                            | 0.625 x VDD | VDD + 0.3  | V    |

| V <sub>OL</sub> output logic level low, I <sub>OL</sub> = 4.0mA   | 0           | 0.125      | V    |

| V <sub>OL</sub> output logic level high, I <sub>OL</sub> = -4.0mA | 0.75 x VDD  | VDD        | V    |

| Strong pull-up                                                    | -100        | -10        | μΑ   |

| Strong pull-down                                                  | 10          | 100        | μΑ   |

| Weak pull-up                                                      | -5          | -0.2       | μΑ   |

| Weak pull-down                                                    | 0.2         | 5          | μΑ   |

**Table 6: Digital Terminal Characteristics**

# 5.4 Audio Characteristics

# 5.4.1 ADC

| Parameter                                       | Conditions        |                     | Min | Тур  | Max  | Unit   |

|-------------------------------------------------|-------------------|---------------------|-----|------|------|--------|

| Resolution                                      | -                 |                     | -   | -    | 16   | Bits   |

| Input Sample<br>Rate, F <sub>sample</sub>       | -                 |                     | 8   | -    | 44.1 | kHz    |

|                                                 |                   | F <sub>sample</sub> |     |      |      |        |

|                                                 |                   | 8kHz                | -   | 79   | -    | dB     |

| Signal to Noise                                 |                   | 11.025kHz           | -   | 77   | -    | dB     |

| Ratio, SNR                                      |                   | 16kHz               | -   | 76   | -    | dB     |

|                                                 |                   | 22.050kHz           | -   | 76   | -    | dB     |

|                                                 |                   | 32kHz               | -   | 75   | -    | dB     |

|                                                 |                   | 44.1kHz             | -   | 75   | -    | dB     |

| Input full scale a                              | at maximum gain ( | differential)       | -   | 4    | -    | mV rms |

| Input full scale at minimum gain (differential) |                   |                     | -   | 800  | -    | mV rms |

| 3dB Bandwidth                                   |                   |                     | -   | 20   | -    | kHz    |

| Microphone mode input impedance                 |                   |                     | -   | 6.0  | -    | kHz    |

| THD+N @ 30mV rms input                          |                   |                     | -   | 0.04 | -    | %      |

**Table 7: ADC characteristics**

#### 5.4.2 DAC

| Parameter                                  | Conditions   |           | ons                 | Min | Тур  | Max    | Unit |

|--------------------------------------------|--------------|-----------|---------------------|-----|------|--------|------|

| Resolution                                 | -            |           |                     | -   | -    | 16     | Bits |

| Output Sample<br>Rate, F <sub>sample</sub> |              | -         |                     | 8   | -    | 48     | kHz  |

|                                            |              |           | F <sub>sample</sub> |     |      |        |      |

|                                            |              |           | 8kHz                | -   | 95   | -      | dB   |

| Signal to Noise                            |              |           | 11.025kHz           | -   | 95   | -      | dB   |

| Ratio, SNR                                 |              |           | 16kHz               | -   | 95   | -      | dB   |

|                                            |              |           | 22.050kHz           | -   | 95   | -      | dB   |

|                                            |              |           | 32kHz               | -   | 95   | -      | dB   |

|                                            |              |           | 44.1kHz             | -   | 95   | -      | dB   |

| Output Full Voltage Swing (differential)   |              |           | -                   | 750 | -    | mV rms |      |

| Alle ed Leed                               |              | Resistive |                     | 16  | -    | O.C.   | Ω    |

| Allowed Loa                                | Allowed Load |           | Capacitive          |     | -    | 500    | pF   |

| THD+N 16Ω Load                             |              | -         | -                   | 0.1 | %    |        |      |

| THD+N 100Ω Load                            |              |           | -                   | -   | 0.01 | %      |      |

**Table 8: DAC Characteristics**

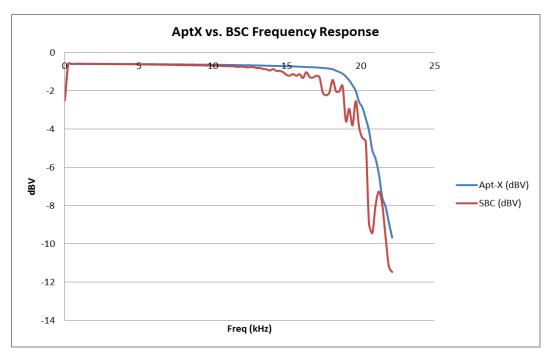

#### 5.4.3 A2DP Codecs

#### 5.4.3.1 SBC

SBC codec is the default codec used for Bluetooth A2DP connections. Any Bluetooth device supporting A2DP audio profile supports SBC codec. SBC was originally design to provide reasonable good audio quality while keeping low computational complexity. SBC does not require high bit rates. Thus it works sufficiently with Bluetooth where the bandwidth and the processing power are limited.

#### 5.4.3.2 aptX®

The aptX is widely used in high quality audio devices. aptX can provide dynamic range up to 120 dB and it has the shortest coding delay (<2ms) than other coding algorithms. Using aptX<sup>®</sup> the whole system latency can be reduced significantly because unlike SBC, it does not require buffering the audio. SBC reproduces a limited audio band width whereas aptX<sup>®</sup> encode the entire frequency range of audio.

aptX<sup>®</sup> is more robust and resilient coding scheme than SBC and thus re-transmits does not occur as with SBC.

Both SBC and aptX<sup>®</sup> have flat frequency response up to 14 kHz. Up to 14 kHz both algorithms produce good quality audio with very little distortion. At frequencies higher than 14 kHz the benefit of aptX<sup>®</sup> becomes obvious. SBC exhibits increasing attenuation with increasing frequency but aptX<sup>®</sup> retains high reproduction quality.

aptX<sup>®</sup> requires purchasing a license for each Bluetooth address and the license agreement must be done with CSR. The combination of aptX<sup>®</sup> license and the Bluetooth address is programmed into the module in the module production line.

Figure 4: Frequency response of aptX and SBC codecs

#### 5.4.3.3 AAC

AAC (Advanced Audio Coding) achieves better sound quality than MP3 and it is the default audio format for YouTube and iPhone among others. AAC has long latency (>100ms) compared to aptX<sup>®</sup>. Because of high processing capacity requirement for encoding, WT32i does not support AAC as A2DP source. Thus WT32i can be used for receiving (A2DP sink) AAC (from iPhone for example) but it cannot transmit AAC coded audio.

# 5.5 RF Characteristics

# 5.5.1 RF Transceiver

| Transceiver characteristi                | Min  | Тур     | Max | Unit |     |

|------------------------------------------|------|---------|-----|------|-----|

| Maximum transmit power                   | 5    | 6.5     | 8   | dBm  |     |

| Minimum transmit power                   |      | -17     |     | dBm  |     |

| Transmit power stability over the temper |      | +/- 0.5 |     | dB   |     |

| Transmit power variation within the      |      |         | 1   | dB   |     |

|                                          | RT   |         | -90 |      | dBm |

| Sensitivity DH1                          | -40C |         | -91 |      | dBm |

|                                          | +85C |         | -86 |      | dBm |

|                                          | RT   |         | -83 |      | dBm |

| Sensitivity 3DH5                         | -40C |         | -84 |      | dBm |

|                                          | +85C |         | -80 |      | dBm |

**Table 9: Transceiver characteristics**

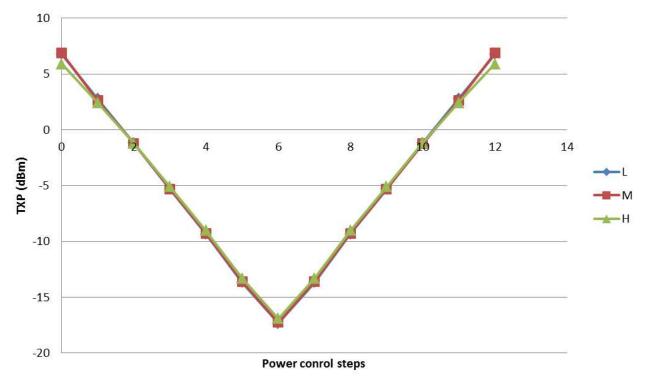

Table 10: Power control of WT32i

| Standard                                             | Band /<br>Frequency                   | Min<br>(AVG /<br>PEAK) | Typ<br>(AVG /<br>PEAK) | Max<br>(AVG /<br>PEAK) | Limit by the Standard<br>(AVG / PEAK) | Unit   |

|------------------------------------------------------|---------------------------------------|------------------------|------------------------|------------------------|---------------------------------------|--------|

|                                                      | 2nd harmonic                          |                        | 50 / 61                |                        | 54 / 74                               | dBuV/m |

|                                                      | 3rd harmonic                          |                        | < 40 /<br>50           |                        | 54 / 74                               | dBuV/m |

|                                                      | Band edge<br>2390MHz                  |                        |                        |                        | 54 / 74                               | dBuV/m |

| FCC part 15 transmitter                              | Band edge<br>2483.5MHz                |                        |                        |                        | 54 / 74                               | dBuV/m |

| spurious<br>emissions                                | Band edge<br>2400MHz<br>(conducted)   |                        |                        |                        | -20                                   | dBc    |

|                                                      | Band edge<br>2483.5MHz<br>(conducted) |                        |                        |                        | -20                                   | dBc    |

| ETSI EN 300<br>328 transmitter                       | Band edge<br>2400MHz                  |                        |                        |                        | -30                                   | dBm    |

| spurious                                             | 2nd harmonic                          |                        | -35                    |                        | -30                                   | dBm    |

| emissions                                            | 3rd harmonic                          |                        | <-40                   |                        | -30                                   | dBm    |

| ETSI EN 300<br>328 receiver<br>spurious<br>emissions | (2400 - 2479)<br>MHz                  |                        |                        |                        | -47                                   | dBm    |

|                                                      | (1600 - 1653)<br>MHz                  |                        |                        |                        | -47                                   | dBm    |

Table 11: WT32i-A spurious emissions

Note: All the emissions tested with maximum 8 dBm TX power

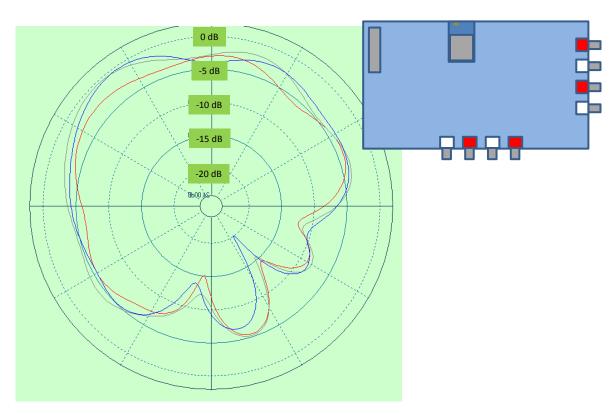

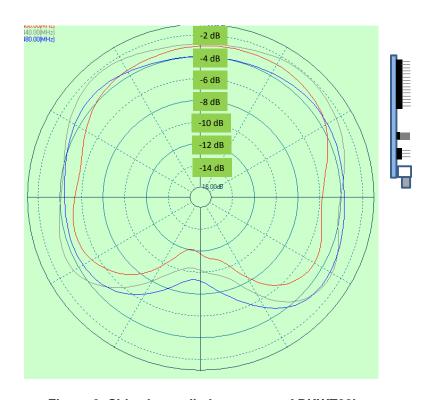

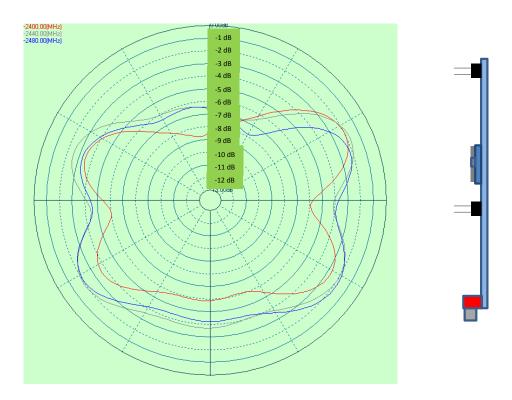

# 5.5.2 Antenna Characteristics

Note: Antenna characteristics may vary depending on the mother board layout. Following characteristics have been measured using DKWT32i

- Antenna efficiency -3.5 dB (45%)

- Peak gain 0 dBi

Figure 5: Top view radiation pattern of DKWT32i

Figure 6: Side view radiation pattern of DKWT32i

Figure 7: Front view radiation pattern

# 5.6 Current Consumption

| Орег                      | ation Mode                  | Peak | Average | Unit |

|---------------------------|-----------------------------|------|---------|------|

|                           | SET BT PAGEMODE 0 2000 0    |      | 2.0     |      |

|                           | SET BT PAGEMODE 0 2000 1    | 12   | 2.0     |      |

|                           | SET BT PAGEMODE 0 2000 2    |      | 2.0     |      |

|                           | SET BT PAGEMODE 1 2000 0    |      | 2.0     |      |

|                           | SET BT PAGEMODE 1 2000 1    |      | 2.1     | mA   |

|                           | SET BT PAGEMODE 1 2000 2    |      | 2.1     |      |

|                           | SET BT PAGEMODE 2 2000 0    |      | 23      |      |

| Idle                      | SET BT PAGEMODE 2 2000 1    |      | 2.2     |      |

|                           | SET BT PAGEMODE 2 2000 2    | 00   | 2.1     |      |

|                           | SET BT PAGEMODE 3 2000 0    | 32   | 23      |      |

|                           | SET BT PAGEMODE 3 2000 1    |      | 2.3     |      |

|                           | SET BT PAGEMODE 3 2000 2    |      | 2.2     |      |

|                           | SET BT PAGEMODE 4 2000 0    |      | 23      |      |

|                           | SET BT PAGEMODE 4 2000 1    |      | 2.3     |      |

|                           | SET BT PAGEMODE 4 2000 2    |      | 2.2     |      |

|                           | SET BT PAGEMODE 0 2000 0    |      | 0.08    |      |

|                           | SET BT PAGEMODE 0 2000 1    | 12   | 0.08    |      |

|                           | SET BT PAGEMODE 0 2000 2    |      | 0.08    |      |

|                           | SET BT PAGEMODE 1 2000 0    |      | 0.18    |      |

|                           | SET BT PAGEMODE 1 2000 1    |      | 0.18    |      |

|                           | SET BT PAGEMODE 1 2000 2    |      | 0.18    |      |

|                           | SET BT PAGEMODE 2 2000 0    |      | 23.5    |      |

| Sleep                     | SET BT PAGEMODE 2 2000 1    |      | 0.31    |      |

|                           | SET BT PAGEMODE 2 2000 2    |      | 0.19    |      |

|                           | SET BT PAGEMODE 3 2000 0    |      | 23      | ^    |

|                           | SET BT PAGEMODE 3 2000 1    |      | 0.4     | mA   |

|                           | SET BT PAGEMODE 3 2000 2    | 32   | 0.29    | -    |

|                           | SET BT PAGEMODE 4 2000 0    |      | 23      |      |

|                           | SET BT PAGEMODE 4 2000 1    |      | 0.4     |      |

|                           | SET BT PAGEMODE 4 2000 2    |      | 0.29    |      |

| Connected, Sniff disabled | SET BT SNIFF 0 20 1 8       |      | 4.7     |      |

| Connected + Sniff, Master | SET BT SNIFF 40 20 1 8      |      | 3.9     |      |

| Connected + Sniff, Master | SET BT SNIFF 1000 20 1 8    |      | 2.5     |      |

| Connected + Sniff, Slave  | SET BT SNIFF 40 20 1 8      |      | 3.6     |      |

| Connected + Sniff, Slave  | SET BT SNIFF 1000 20 1 8    |      | 2.5     |      |

| A2DP Audio Streaming      | A2DP SINK, INTERNAL CODEC   | 75   | 28      |      |

| A2DP Audio Streaming      | A2DP SOURCE, INTERNAL CODEC | 70   | 23      | mA   |

Table 12: Current consumption of WT32i

# 6 Power Control and Regulation

WT32i contains an internal battery charger and a switch mode regulator that is mainly used for internal blocks of the module. The module can be powered from a single 3.3 V supply provided that VDD\_CHG is floating. Alternatively the module can be powered from a battery connected to VDD\_BAT and using an external regulator for VDD\_IO. 1.8 V to 3.3 V supply voltage for VDD\_IO can be used to give desired signal levels for the digital interfaces of the module. USB, however, requires 3.3 V for proper operation and thus, when USB is in use, 3.3 V for VDD\_IO is required.

Figure 8: Power supply configuration of WT32i

VDD\_ENA is software configurable enable pin for the internal regulators. Using iWRAP the enable pin can be configured to

- 1. Latch on the internal regulators at the rising edge

- 2. Turn the regulators on at rising edge and turn off the regulators at falling edge

- 3. Latch the regulators on at the rising edge and turn off the regulators at the following rising edge

GPIO can be configured to control an external regulator.

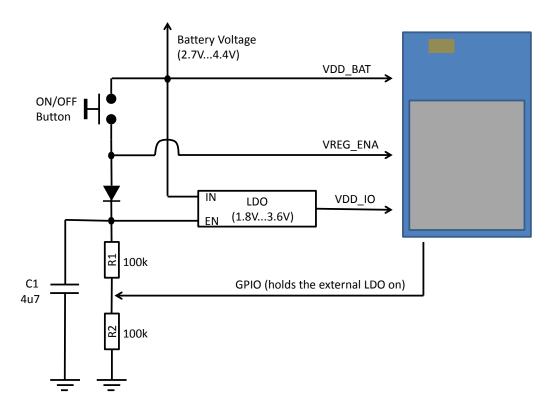

Figure 9: Example of making a power on/off button using the latch feature of the internal regulators

iWRAP Example: Creating an on/off button with PIO2 holding the external regulator on "SET CONTROL VREGEN 2 4"

(PIO is defined with a bit mask. 4 in hexadecimal is 100 in binary corresponding to PIO2)

**NOTE:** With the configuration shown above, when doing a SW reset for the module C1 will hold the enable pin of the external regulator high until iWRAP has booted. This will prevent the module from turning off during reset. When resetting through the reset pin one has to make sure that the enable pin is held high as long as the reset pin is held active.

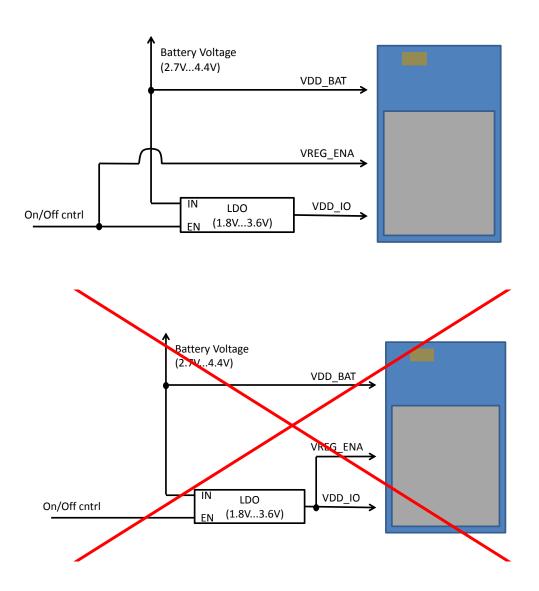

Figure 10 shows an example how to arrange power control when on/off button is not implemented. VREG\_ENA pin must not be connected to VDD\_IO because leakage from VDD\_BAT to VDD\_IO will prevent VREG\_ENA to fall low enough to turn off the internal regulators.

Figure 10: Correct and wrong connection for the power on/off control

# 6.1 Protecting the Battery by Configuring the Module to Turn Off at Certain Voltage

It is important not to let the battery be drained to voltages below 2.8V. In iWRAP it is possible to define certain level when the module turns off the regulators.

iWRAP Example: Configure WT32i to start sending low battery warning at 3.4V, turn off at 3.3V and cease the low battery warning at 4.0V. Set PIO0 to indicate low batter

"SET CONTROL BATTERY 3400 3300 4000 10"

#### 6.2 Reset

WT32i may be reset from several sources: reset pin, power on reset, a UART break character or through software configured watchdog timer.

At reset, the digital I/O pins are set to inputs for bi-directional pins and outputs are tri-state.

The chip status after a reset is as follows:

- Warm Reset: data rate and RAM data remain available

- Cold Reset: data rate and RAM data are not available

Table 13 shows the pin states of WT32i on reset. Pull-up (PU) and pull-down (PD) default to weak values unless specified otherwise.

| Pin Name / Group | I/O Type                          | No Core Voltage<br>Reset | Full Chip Reset |  |

|------------------|-----------------------------------|--------------------------|-----------------|--|

| USB              | Digital bi-directional            | N/A                      | N/A             |  |

| UART_RX          | Digital input with PD             | PD                       | PD              |  |

| UART_CTS         | Digital input with 1 D            | 10                       | 10              |  |

| UART_TX          | Digital output with PU            | PU                       | PU              |  |

| UART_RTS         | Digital output with 1 o           | 10                       |                 |  |

| SPI_MOSI         | Digital input with PD             |                          | PD              |  |

| SPI_CLK          | Digital input with 1 D            | PD                       |                 |  |

| SPI_MISO         | Digital tristate output with PD   |                          |                 |  |

| SPI_CS           | Digital input with PU             | PU                       | PU              |  |

| PCM_IN           | Digital input with PD             |                          | PD              |  |

| PCM_CLK          | Digital bi-directional with PD    |                          |                 |  |

| PCM_SYNC         | Digital bi-directional with 1 D   | PD                       |                 |  |

| PCM_OUT          | Digital tri-state output with PD  |                          |                 |  |

| GPIO             | Digital bi-directional with PU/PD | PD                       | PD              |  |

Table 13: Pin states on reset

### 6.2.1 Internal POR

WT32i has two internal POR circuits. One is internally to the BC5 chip. In BC5 the power on reset occurs when the core supply voltage (output of the internal 1.5V regulator) falls below typically 1.26V and is released when VDD\_CORE rises above typically 1.31V.

Another POR circuit is embedded to the module and it keeps the module in reset until supply voltages have stabilized. This is to prevent corruption of the internal flash memory during boot. The embedded POR is shown in the figure Figure 2Figure 11.

Because the POR is based on a simple RC time constant it will not work if the supply voltage ramps very slowly or if the reset pin is not connected to high impedance. It is recommended that the power ramp will not take more than 10 msec. If the reset pin is connected to a host it is good to place a diode between the host and the module as shown in Figure 12. A diode will prevent the host from pulling the reset low before the internal flash has its supply stabilized.